# Reliability Report SN54SC4T32-SEP Production Flow and Reliability Report

#### ABSTRACT

This report presents the reliability and qualification results for the Texas Instruments SN54SC4T32-SEP - quadruple 2-input positive OR gates with integrated translation in Space Enhanced Plastic (SEP). The SN54SC4T32-SEP is manufactured with a controlled baseline that has the following:

- An extended product life cycle

- One assembly and test site

- Product traceability

## **Table of Contents**

| 1 Texas Instruments Enhanced Product Qualification and Reliability Report |     |

|---------------------------------------------------------------------------|-----|

| 2 Space Enhanced Plastic Production Flow                                  |     |

| 2.1 Device Introduction                                                   | . 3 |

| 2.2 SN54SC4T32-SEP Space Enhanced Plastic Production Flow                 | 3   |

| 3 Device Qualification                                                    |     |

| 4 Outgas Test Report                                                      |     |

### **List of Figures**

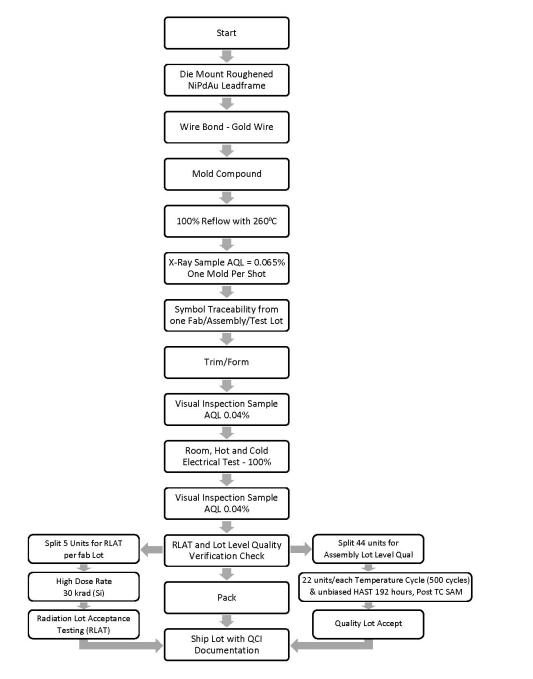

| Figure 2-1. SN54SC4T32-SEP S | Space Enhanced Plastic Production Flow Chart | 3 |

|------------------------------|----------------------------------------------|---|

#### List of Tables

| Table 3-1. Space Enhanced Products New Device Qualification Matrix | 4 |

|--------------------------------------------------------------------|---|

| Table 4-1. Outgas Test Results                                     | 5 |

#### Trademarks

All trademarks are the property of their respective owners.

1

## 1 Texas Instruments Enhanced Product Qualification and Reliability Report

TI qualification testing is a risk mitigation process that is engineered to assure device longevity in customer applications. Wafer fabrication process and package level reliability are evaluated in a variety of ways that may include accelerated environmental test conditions with subsequent derating to actual use conditions. Manufacturability of the device is evaluated to verify a robust assembly flow and assure continuity of supply to customers. TI Enhanced Products are qualified with industry standard test methodologies performed to the intent of Joint Electron Device Engineering Council (JEDEC) standards and procedures. Texas Instruments Enhanced Products are certified to meet GEIA-STD-0002-1 Aerospace Qualified Electronic Components.

# 2 Space Enhanced Plastic Production Flow

## 2.1 Device Introduction

SN54SC4T32-SEP is a radiation hardened device in a plastic package which allows this device to be used in space applications. The device was verified immune to 43 MeV ×  $cm^2$  / mg at 125°C for single event latch-up (SEL). Each fabrication lot was tested according to MIL-STD-883 for Radiation Lot Acceptance Tested (RLAT) up to 30 krad(Si) and each assembly and test lot follows the process flow shown in Figure 2-1. To maintain the quality of SN54SC4T32-SEP, the device is qualified with Space EP requirements. See Section 3 for further details.

## 2.2 SN54SC4T32-SEP Space Enhanced Plastic Production Flow

3

# **3 Device Qualification**

The following is the device qualification summary.

#### **Qualification by Similarity (Qualification Family)**

A new device can be qualified either by performing full scale quality and reliability tests on the actual device or using previously qualified devices through "Qualification by Similarity" (QBS) rules. By establishing similarity between the new device and those qualified previously, repetitive tests are eliminated, allowing for timely production release. When adopting QBS methodology, the emphasis is on qualifying the differences between a previously qualified product and the new product under consideration.

The QBS rules for a technology, product, test parameters, or package shall define which attributes are required to remain fixed for the QBS rules to apply. The attributes which are expected and allowed to vary is reviewed and a QBS plan is developed, based on the reliability impact assessment above, specifying what subset of the full complement of environmental stresses is required to evaluate the reliability impact of those variations. Each new device is reviewed for conformance to the QBS rule sets applicable to that device. See JEDEC JESD47 for more information.

| Note                                | Note that qualification by similarity ("qualification family") per JEDEC JESD47 is allowed. |                                 |               |                            |  |

|-------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------|---------------|----------------------------|--|

| Description                         | Condition                                                                                   | Sample Size Used<br>and Rejects | Lots Required | Test Method                |  |

| Electromigration                    | Maximum recommended operating conditions                                                    | N/A                             | N/A           | Per TI Design rules        |  |

| Wire bond life                      | Maximum recommended operating conditions                                                    | N/A                             | N/A           | Per TI Design rules        |  |

| Electrical characterization         | TI data sheet                                                                               | 10                              | 3             | N/A                        |  |

| Electrostatic discharge             | НВМ                                                                                         | - 3 units/voltage               | 1             | EIA/JESD22-A114            |  |

| sensitivity                         | CDM                                                                                         |                                 | I             | EIA/JESD22-C101            |  |

| Latch-up                            | Per technology                                                                              | 3/0                             | 1             | EIA/JESD78                 |  |

| Physical dimensions                 | TI data sheet                                                                               | 5/0                             | 1             | EIA/JESD22- B100           |  |

| Thermal impedance                   | Theta-JA on board                                                                           | Per pin-package                 | N/A           | EIA/JESD51                 |  |

| Bias life test                      | 125°C / 1000 hours or equivalent                                                            | 77/0                            | 3             | JESD22-A108*               |  |

| Biased HAST                         | 130°C / 85% / 96 hours                                                                      | 77/0                            | 3             | JESD22-A110*               |  |

| Extended biased HAST                | 130°C / 85% / 250 hours (for reference)                                                     | 77/0                            | 1             | JESD22-A110*               |  |

| Unbiased HAST                       | 130°C / 85% / 192 hours                                                                     | 77/0                            | 3             | JESD22-A118*               |  |

| Temperature cycle                   | -65°C to +150°C non-biased for 500 cycles                                                   | 77/0                            | 3             | JESD22-A104*               |  |

| Solder heat                         | 260°C for 10 seconds                                                                        | 22/0                            | 1             | JESD22-B106                |  |

| Resistance to solvents              | Ink symbol only                                                                             | 12/0                            | 1             | JESD22-B107                |  |

| Solderability                       | Condition A (steam age for 8 hours)                                                         | 22/0                            | 1             | ANSI/J-STD-002-92          |  |

| Flammability                        | Method A or Method B                                                                        | 5/0                             | 1             | UL-1964                    |  |

| Bond shear                          | Per wire size                                                                               | 5 units × 30/0 bonds            | 3             | JESD22-B116                |  |

| Bond pull strength                  | Per wire size                                                                               | 5 units × 30/0 bonds            | 3             | ASTM F-459                 |  |

| Die shear                           | Per die size                                                                                | 5/0                             | 3             | TM 2019                    |  |

| High Temp storage                   | 150 °C / 1000 hours                                                                         | 15/0                            | 3             | JESD22-A103-A*             |  |

| Moisture sensitivity                | Surface mount only                                                                          | 12                              | 1             | J-STD-020-A*               |  |

| Radiation response characterization | Total ionization dose, single-event latch-<br>up                                            | 5 units / dose level            | 1             | MIL-STD-883/Method<br>1019 |  |

| Outgassing characterization         | TML (Total Mass Lost), CVCM<br>(Collected Volatile Condensable<br>material)                 | 5                               | 1             | ASTM E595                  |  |

#### Table 3-1. Space Enhanced Products New Device Qualification Matrix

1. \*Precondition performed per JEDEC Std. 22, Method A112/A113.

4

**IEXAS**

**ISTRUMENTS**

www.ti.com

# 4 Outgas Test Report

Outgassing test was performed on Die attach and Mold compound used for the SN54SC4T32-SEP. A total mass loss (TML) of 1.00% and collected volatile condensable material (CVCM) of 0.10% were used as screening levels for rejection of spacecraft materials. The outgas test was performed in a vacuum environment of less than  $5 \times 10^{-5}$  Torr according to ASTM E 595, for a duration of 24 hours, at 125°C. The TML and CVCM were measured after the test.

#### Table 4-1. Outgas Test Results

| Device            | TML<br>< 1.0% | CVCM<br>< 0.1% |

|-------------------|---------------|----------------|

| SN54SC4T32MPWTSEP | Pass          | Pass           |

5

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated