Application Report SCPA056-April 2019

# Steps to Configure TIC12400-Q1 Multiple Switch Detection Interface (MSDI)

Helen Wanchie Sun

### ABSTRACT

This application report explains the procedures to configure the TIC12400-Q1 using two examples including a set of digital and analog switches.

| Contents |

|----------|

|----------|

| 1 | Automotive Body Control Module                                   | 2  |

|---|------------------------------------------------------------------|----|

| 2 | TIC12400-Q1 device 101                                           | 3  |

| 3 | How to configure TIC12400-Q1                                     | 4  |

| 4 | Interrupt configuration                                          | 5  |

| 5 | Digital switch-using comparator to detect switch states          | 5  |

|   | Analog (Resistor-coded) switch-using ADC to detect switch states |    |

| 7 | References                                                       | 11 |

#### List of Figures

| 1 | Typical switch detection | 2 |

|---|--------------------------|---|

| 2 | Simplified block diagram | 3 |

| 3 | Flow chart               | 4 |

| 4 | Digital switch           | 5 |

| 5 | Analog switch            | 7 |

|   | THRES_CFG0 Register      |   |

### List of Tables

| 1 | V <sub>s</sub> required for proper detection                          | 6  |

|---|-----------------------------------------------------------------------|----|

| 2 | Comparator threshold                                                  | 6  |

| 3 | TIC12400-Q1 IN12-15 pin Wetting Current and Threshold Setting Details | 8  |

| 4 | Equivalent switch resistance                                          | 8  |

| 5 | Wetting current accuracy for analog switches                          | 9  |

| 6 | Equivalent Voltage at INx                                             | 9  |

| 7 | Equivalent ADC code                                                   | 9  |

| 8 | Proper Threshold Configuration For ADC Inputs                         | 10 |

| 9 | THRESMAP_CFG1 Register Field Descriptions                             | 10 |

|   |                                                                       |    |

### Trademarks

All trademarks are the property of their respective owners.

1

### 1 Automotive Body Control Module

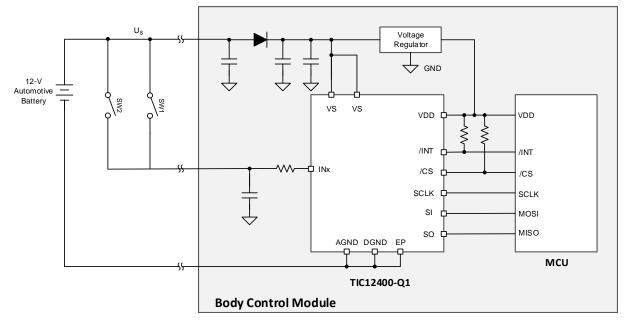

The body control module (BCM) is an electronic control unit responsible for monitoring and controlling electronic accessories in a vehicle body. Detecting mechanical switch status in a vehicle is an important task handled by the BCM. The automotive body has on-and-off type of switch (digital switch) such as door locks and resistor coded switch (analog switch) with three or more states used in wiper speed control. A typical switch detection implementation with a MSDI device is shown in Figure 1.

Figure 1. Typical switch detection

### 2 TIC12400-Q1 device 101

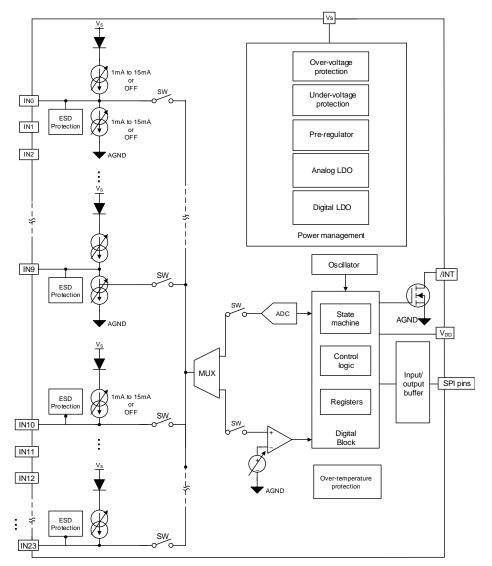

The TIC12400-Q1 is an integrated multiple switch detection interface (MSDI) designed to detect external switch status in a 12-V automotive system. The TIC12400-Q1 features an integrated 10-bit ADC that saturates at 6V to monitor analog switches and a comparator with four thresholds( 2-V, 2.7-V, 3-V, 4-V) to monitor digital switches. The ADC and the comparator threshold can be programmed to support a wide variety of switch types. The TIC12400-Q1 has 24 direct switch inputs, 10 inputs (IN0-IN9) are configurable to monitor switches connected to either ground or battery and 14 inputs (IN10-IN23) are for general use. Each input can be easily programmed through SPI interface to support different application scenarios. The TIC12400-Q1 input can also be programmed to monitor more than 24 switches. The ability to monitor more than 24 switches with the same number of inputs reduces the overall system cost. (See: *Input Sharing with the TIC12400-Q1*) A simplified block diagram of TIC12400-Q1 is shown in Figure 2.

Figure 2. Simplified block diagram

3

How to configure TIC12400-Q1

### 3 How to configure TIC12400-Q1

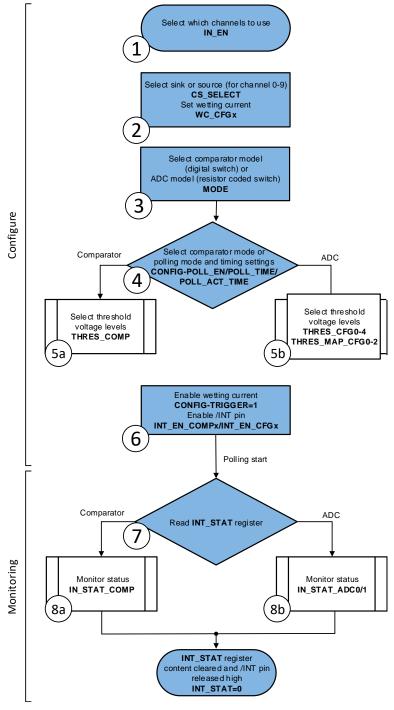

There are only a handful of registers to configure to start monitoring switch status. Follow the steps in Figure 3 to configure the TIC12400-Q1 registers:

Figure 3. Flow chart

After polling and wetting current have been activated, the monitored digital switch status is stored in IN\_STAT\_COMP register for comparator inputs and the monitored analog switch status is stored in IN\_STAT\_ADC0/1 for ADC inputs. Once wetting current has been enabled, the TRIGGER bit (CONFIG register) must be set to "0" to apply changes to the register settings.

### 4 Interrupt configuration

The INT pin is used to monitor events detected by the TIC12400-Q1. Example of monitored events include: switch state change, temperature warning, over-voltage shutdown, and so on. These events are communicated to the micro-controller by the INT pin output asserting logic low. To configure INT pin, select static or dynamic assertion scheme (selected in INT\_CONFIG bit in the CONFIG register). Each switch input (IN0-IN23) can be programmed to have the event interrupt enabled or disabled by configuring registers INT\_EN\_COMP1 to INT\_EN\_COMP2 (for comparator assigned inputs) and INT\_EN\_CFG1 to INT\_EN\_CFG4 (for ADC assigned inputs). After the end of the first polling cycle, the INT pin asserts logic low to notify the micro-controller that the default switch status is ready to be read. It is essential to read and clear the INT pin after the first polling cycle is completed and read the corresponding the switch position in the INT\_STAT\_COMP and INT\_STAT\_ADC registers. INT pin can also be used to wake up a micro-controller in sleep mode which provides significant system-level power savings.

### 5 Digital switch-using comparator to detect switch states

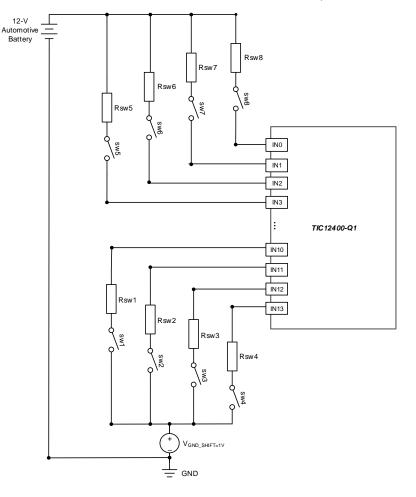

Digital switch is defined to have two states, typically switch closed resistance less than  $100-\Omega$ , and switch open resistance larger than  $5000-\Omega$ . Figure 4 is an example of how to configure MSDI to monitor digital switch with  $50-\Omega$  resistance in closed state and  $5000-\Omega$  resistance in open state:

#### Notes

- Digital switches: four battery-connected, four ground-connected

- State 1: switch is opened > 5000-Ω

- State 2: switch is closed: 50-Ω

- Minimum Vs = 6-V (lowest battery voltage during cranking), grounded shift = 1-V

### Figure 4. Digital switch

### 5.1 Configure channels

Enable channel used by setting IN\_EN\_x bit to 1 in the IN\_EN register (*Flow chart step 1*). For batteryconnected switches, only inputs IN0-IN9 of TIC12400-Q1 may be enabled. In this example, inputs IN0-IN3 are configured for battery-connected switches, and inputs IN4-IN7 are configured for ground-connected switches.

Select source/sink mode and program the wetting current:

- For ground-connected switches, program the wetting current to source mode by setting CS\_INx bits to 0 in the CS\_SELECT register. For battery-connected switches, program the wetting current to sink mode by setting CS\_INx bits to 1. The wetting current magnitude can be programmed from 0 to 15-mA by configuring WC\_CFG0 and WC\_CFG1 registers (*Step 2*). Since we are using the comparator in this case, assign 0 to bit 0-3 (IN0-IN3) of MODE register (*Step 3*).

- In CONFIG register, program the POLL\_EN bit to enable continuous mode or polling mode, then select total period time in POLL\_TIME bits and the active polling time is programmed in the POLL\_ACT\_TIME bits (*Step 4*).

## 5.2 Program threshold voltage of comparator

Four thresholds can be selected for the comparator: 2-V, 2.7-V, 3-V and 4-V. There are several factors involved to determine which threshold of the comparator should be picked:

Using Equation 1 calculate the voltage drop when the switch is closed. The switch closed resistance is 50-Ω, assuming the worst case for digital switches of 100-Ω. With I<sub>WETT</sub> set at 10-mA, V<sub>INX</sub> is calculated to be 1-V.

$V_{INX} = R_{EQ} \times I_{WETT}$

(1)

- Ground shift and other non- ideal situation should be considered. With 1-V ground shift adding onto the

previously calculated V<sub>INX</sub>, the total voltage change is 1.5-V when switch is closed.

- Minimum V<sub>s</sub> requested for correct detection is specified in Table 1. In this example, the minimum V<sub>s</sub> = 6-V, so 3-V is the highest threshold that can be selected.

| PARAMETER           |                                           | TEST CONDITIONS    | MIN | TYP | MAX | UNIT |

|---------------------|-------------------------------------------|--------------------|-----|-----|-----|------|

|                     |                                           | THRES_COMP = 2 V   | 4.5 |     |     |      |

| V                   | Minimum V <sub>s</sub><br>requirement for | THRES_COMP = 2.7 V | 5   |     |     | V    |

| V <sub>S_COMP</sub> | proper detection                          | THRES_COMP = 3 V   | 5.5 |     |     | v    |

|                     |                                           | THRES_COMP = 4 V   | 6.5 |     |     |      |

### Table 1. V<sub>s</sub> required for proper detection

- If ground-connected switch is used, the threshold voltage should be as high as possible so switch status would not be misread. For our ground-connected switches example (IN0-IN3), considering detection range of the threshold (Table 2), the highest threshold we pick is 3-V due to minimum Vs.

- If battery-connected switch is used, the threshold voltage should be as low as possible so switch status would not be misread. For our battery-connected switches example (IN12-IN15), considering detection range of the threshold (Table 2), the lowest threshold we can pick is 2.7-V due to maximum switch closed voltage of 2-V.

| I                          | PARAMETER                      | TEST CONDITIONS    | MIN  | TYP MAX | UNIT |

|----------------------------|--------------------------------|--------------------|------|---------|------|

| V <sub>TH_ COMP_2V</sub>   | Comparator threshold for 2 V   | THRES_COMP = 2 V   | 1.85 | 2.25    | V    |

| V <sub>TH_ COMP_2p7V</sub> | Comparator threshold for 2.7 V | THRES_COMP = 2.7 V | 2.4  | 2.9     | V    |

| V <sub>TH_ COMP_3V</sub>   | Comparator threshold for 3 V   | THRES_COMP = 3 V   | 2.85 | 3.3     | V    |

| V <sub>TH_ COMP_4V</sub>   | Comparator threshold for 4 V   | THRES_COMP = 4 V   | 3.7  | 4.35    | V    |

#### Table 2. Comparator threshold

To program the comparator threshold, set the THRES\_COMP\_IN0\_IN3 to 10 (threshold = 3-V) and THRES\_COMP\_IN4\_IN7 (IN4-IN7) bits to 00 (threshold = 2-V) in the THRES\_COMP register (*Step* 5a).

### 5.3 Interrupt enable and start monitoring

After the voltage thresholds had been set, the interrupt needs to be set properly for TIC12400-Q1 to start the switch monitoring process.

- The Switch Status Change (SSC) interrupt need to be enabled so when switch state had changed, interrupt will be generated and alert the micro-controller. SSC interrupt can be enabled by setting the SSC bit to 1 in the INT\_EN\_CFG0 register. Start TIC12400-Q1 operation by setting the TRIGGER bit in CONFIG register to 1 and read the INT\_STAT register to clear the baseline SSC interrupt (*Step 6*).

- Start monitoring by reading the interrupt status register INT\_STAT when /INT pin is asserted and then read the IN\_STAT\_COMP for comparator status (*Step 8a*).

### 6 Analog (Resistor-coded) switch-using ADC to detect switch states

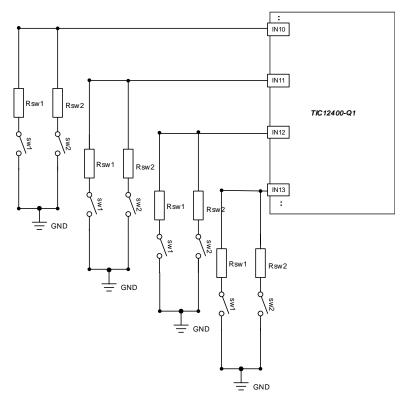

Using analog switches combining with an ADC decoding scheme in TIC12400-Q1, implementations such as wiper speed setting and sign control arms in a vehicle can be monitored. With a given set of resistor coded switches, the ADC in TIC12400-Q1 (saturates at 6-V) is able to detect statuses of the switches. The Figure 5 shows a typical connection between a BCM and a resistor coded switch with three states. A real life example of a three state switch is the power window switch in a vehicle where you can pull up, pull down or leave the window stationary.

The example of how to set the ADC for a given set of resistor coded switches with three states is shown in Figure 5:

#### Notes

- Analog switches: four ground-connected

- Rsw1 =  $100-\Omega \pm 10\%$

- Rsw2 =  $470 \cdot \Omega \pm 10\%$

- State 1: No switch is closed

- State 2: SW1 is closed

- State 3: SW2 is closed

- Minimum V<sub>s</sub> = 6-V (lowest battery voltage during cranking)

### Figure 5. Analog switch

In Figure 5,  $R_{SW1}$  and  $R_{SW2}$  are given and there are three different states that need to be detected by TIC12400-Q1. The following steps can be implemented to determine the threshold of the ADC values.

### 6.1 Configure channels

Enable channel used by setting IN\_EN\_x bit to 1 in the IN\_EN register. In this example since IN0-IN7 is already used for digital switches and two thresholds are needed (Table 3), IN12-IN15 is enabled for analog switches (*Step 1*).

THRESHOLD SWITCH POSITION WETTING CURRENT INPUT **COMPARATOR INPUT** CURRENT SOURCE/SINK DETECTION ADC INPUT MODE MODE THRES2A IN12 THRES2B WC\_IN12\_13 CSO Switch to GND THRES2A IN13 THRES2B THRES\_COMP\_IN12\_IN15 THRES2A IN14 THRES2B CSO WC\_IN14\_15 Switch to GND THRES2A IN15 THRES2B

Table 3. TIC12400-Q1 IN12-15 pin Wetting Current and Threshold Setting Details

Program the wetting current and select source/sink mode:

- For ground-connected switches, program the wetting current to source by setting CS\_INx bits to 0 in the CS\_SELECT register. The wetting current magnitude can be programmed from 0 to 15-mA by configuring WC\_CFG0 and WC\_CFG1 registers (*Step 2*). Since we are using the ADC in this case, assign 1 to bits 12-15 (IN12- IN15) of MODE register (*Step 3*).

- In CONFIG register, program the POLL\_EN bit to enable continuous mode or polling mode, then select total period time in POLL\_TIME bits and the active polling time is programmed in the POLL\_ACT\_TIME bits (*Step 4*).

### 6.2 Calculate the minimum and maximum resistance values in each state

In each state, the maximum resistance is calculated based on the resistance variation.

|         | Switch status        | Equivalent min/ max resistance          |

|---------|----------------------|-----------------------------------------|

| State 1 | No switch closed     | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

| State 2 | SW2 closed, SW1 open | 423~517Ω                                |

| State 3 | SW1 closed, SW2 open | 90~110Ω                                 |

#### Table 4. Equivalent switch resistance

### 6.3 Calculate the voltage depending on which wetting current setting is selected

Using Equation 2 calculate the input voltage. Wetting current can be programmed from 0 to 15-mA. In this example wetting current is set to 2-mA by configuring WC\_CFG0 and WC\_CFG1 registers. The wetting current accuracy needs to be considered as well. For accurate wetting current to be applied, the V<sub>s</sub> and V<sub>INX</sub> conditions need to fulfill the following conditions:

$V_{INX} = R_{EQ} \times I_{WETT}$

(2)

8

Analog (Resistor-coded) switch-using ADC to detect switch states

| PARA          | METER           |               | TEST CONDITIONS                                                                                                           | MIN  | TYP | MAX  | UNIT |

|---------------|-----------------|---------------|---------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| WETTING CURRE |                 |               |                                                                                                                           |      |     |      |      |

|               |                 | 1 mA setting  |                                                                                                                           | 0.88 | 1   | 1.13 |      |

|               |                 | 2 mA setting  | -4.5 V ≤ V <sub>S</sub> ≤ 35 V, V <sub>S</sub> $-$ V <sub>INX</sub> ≥ 2.5 V                                               | 1.8  | 2   | 2.25 |      |

| 1             | Wetting current | 5 mA setting  | $5.5 \text{ V} \le \text{V}_{\text{S}} \le 35 \text{ V}, \text{V}_{\text{S}} - \text{V}_{\text{INX}} \ge 2.5 \text{ V}$   | 4.3  | 5   | 5.5  | A    |

| IWETT         | accuracy        |               | 5.5 V $\leq$ V <sub>S</sub> $\leq$ 35 V, V <sub>S</sub> - V <sub>INX</sub> $\geq$ 3 V                                     | 4.5  | 5   | 5.5  | mA   |

|               |                 | 10 mA setting | $6 \text{ V} \le \text{V}_{\text{S}} \le 35 \text{ V}, \text{V}_{\text{S}} - \text{V}_{\text{INX}} \ge 4 \text{ V}$       | 9    | 10  | 11   |      |

|               |                 | 15 mA setting | $6.5 \text{ V} \leq \text{V}_{\text{S}} \leq 35 \text{ V}, \text{ V}_{\text{S}} - \text{V}_{\text{INX}} \geq 5 \text{ V}$ | 12.5 | 15  | 16.5 |      |

#### Table 5. Wetting current accuracy for analog switches

In this example minimum V<sub>S</sub> = 6-V. If 2-mA wetting current is selected, the highest voltage seen at V<sub>INX</sub> is at the highest resistance value (517- $\Omega$ ) multiply by the highest wetting current of 2-mA (2.25-mA) where maximum V<sub>INX</sub> = 1.16-V, which fulfills the V<sub>S</sub> - V<sub>INX</sub> ≥ 2.5-V requirement for 2-mA wetting current setting. Table 6 values are calculated:

### Table 6. Equivalent Voltage at INx

|         | Switch status        | VINx       |

|---------|----------------------|------------|

| State 1 | No switch closed     | 6V(max)    |

| State 2 | SW2 closed, SW1 open | 0.76~1.16V |

| State 3 | SW1 closed, SW2 open | 0.16~0.25V |

### 6.4 Convert the voltage established on the INx pin into equivalent ADC code

The integrated 10-bit ADC range of TIC12400-Q1 is from 0-V to 6-V, with 6-V corresponding to the full scale maximum code of 1023. Therefore, the ADC code for each of the three different states can be calculated with equation .

$ADC_{code} = V_{INX} \times 1024 \div 6$

The calculated ADC codes are listed in Table 7:

### Table 7. Equivalent ADC code

|         | Switch status        | Code    |

|---------|----------------------|---------|

| State 1 | No switch closed     | 1023    |

| State 2 | SW2 closed, SW1 open | 130~198 |

| State 3 | SW1 closed, SW2 open | 27~43   |

After the ADC code spread for each switch state is calculated, the detection can be set at the mid-point between the max code of one state and min code for the next state. For example, to select the threshold between state 2 and state 3, take the mid-point between the highest code of state 2 and lowest code of state 3 (code 87) to be the threshold code between state 2 and 3. For state 1 and state 2, the mid-point between state 1 and lowest code of state 2 (code 611) is selected to be the threshold code between state 1 and 2.

(3)

Analog (Resistor-coded) switch-using ADC to detect switch states

### 6.5 Set the threshold of the ADC and start monitoring

An additional register mapping step need to be done with ADC switch monitoring containing more than 2 states. Proper threshold configuration rules specified in Table 8 have to be followed for ADC inputs threshold adjustments (*Step 5b*).

### **Table 8. Proper Threshold Configuration For ADC Inputs**

| INPUT        | PROPER THRESHOLD CONFIGURATION                |

|--------------|-----------------------------------------------|

| IN12 to IN17 | THRES2B ≥ THRES2A                             |

| IN18 to IN22 | THRES3C ≥ THRES3B ≥ THRES3A                   |

| IN23         | THRES9 ≥ THRES8 ≥ THRES3C ≥ THRES3B ≥ THRES3A |

Two thresholds are set with THRES2B = code 611 and THRES2A = code 87. These 2 values can be set in THRES\_CFG0 register . THRES\_CFG0 is selected in this case with THRES1= 611 and THRES0 = 87.

### Figure 6. THRES\_CFG0 Register

|                 |    |    |    |    |    |      |    |        |    |    |    | _  | -    |   | • |   |   |   |   |   |   |   |   |

|-----------------|----|----|----|----|----|------|----|--------|----|----|----|----|------|---|---|---|---|---|---|---|---|---|---|

| 23              | 22 | 21 | 20 | 19 | 18 | 17   | 16 | 15     | 14 | 13 | 12 | 11 | 10   | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RESERVED THRES1 |    |    |    |    |    |      |    | THRES0 |    |    |    |    |      |   |   |   |   |   |   |   |   |   |   |

| R-0h            |    |    |    |    |    | R-0h |    |        |    |    |    |    | R-0h |   |   |   |   |   |   |   |   |   |   |

LEGEND: R/W = Read/Write; R = Read only

THRESMAP\_CFG1 need to be set to map the THRES01 and THRES1 values the designated input pin thresholds. In this example, two thresholds need to be set and mapped.

THRES1 need to be map to THRES2B: THRESMAP\_IN12\_IN17\_THRES2B is set to 1h (Table 9).

THRES0 need to be map to THRES2A: THRESMAP\_IN12\_IN17\_THRES2A is set to 0h (Table 9).

| Bit   | Field                          | Туре | Reset | Description                                                                                                          |

|-------|--------------------------------|------|-------|----------------------------------------------------------------------------------------------------------------------|

| 23-18 | RESERVED                       | R    | 0h    | Reserved                                                                                                             |

| 17-15 | THRESMAP_IN12_IN17_THR<br>ES2B | R/W  | Oh    | 0h = THRES0<br>1h = THRES1<br>2h = THRES2<br>3h = THRES3<br>4h = THRES4<br>5h = THRES5<br>6h = THRES6<br>7h = THRES7 |

| 14-12 | THRESMAP_IN12_IN17_THR<br>ES2A | R/W  | Oh    | 0h = THRES0<br>1h = THRES1<br>2h = THRES2<br>3h = THRES3<br>4h = THRES4<br>5h = THRES5<br>6h = THRES6<br>7h = THRES7 |

#### Table 9. THRESMAP\_CFG1 Register Field Descriptions

### 6.6 Interrupt enable and start monitoring

After the thresholds had been set, the interrupt needs to be set properly for TIC12400-Q1 to start the switch monitoring process.

- The Switch Status Change (SSC) interrupt need to be enabled so when switch state had changed, interrupt is generated and alert the micro-controller. SSC interrupt can be enabled by setting the SSC bit to 1 in the INT\_EN\_CFG0 register and enable the desired channels by setting INT\_EN\_CFG1 to INT\_EN\_CFG4. Start TIC12400-Q1 operation by setting the TRIGGER bit in CONFIG register to 1 and read the INT\_STAT register to clear the baseline SSC interrupt (*Step 6*).

- Start monitoring by reading the interrupt status register INT\_STAT when INT pin is asserted and then read the IN\_STAT\_ADC0/ IN\_STAT\_ADC1 for switch status (*Step 8b*). The raw code can also be retrieved in ANA\_STATx registers.

### 7 References

### TIC12400-Q1 24-Input Multiple-Switch Detection Interface (MSDI), data sheet

To further training on the advantages of using TIC12400-Q1, please see TIC12400-Q1 training.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated