# Errata

# MSP430F5517 Microcontroller

### **ABSTRACT**

This document describes the known exceptions to the functional specifications (advisories).

# **Table of Contents**

| 1 Functional Advisories                                            | 2 |

|--------------------------------------------------------------------|---|

| 2 Preprogrammed Software Advisories                                | 3 |

| 3 Debug Only Advisories                                            |   |

| 4 Fixed by Compiler Advisories                                     | 3 |

| 5 Nomenclature, Package Symbolization, and Revision Identification | 5 |

| 5.1 Device Nomenclature                                            | 5 |

| 5.2 Package Markings                                               | 5 |

| 5.3 Memory-Mapped Hardware Revision (TLV Structure)                |   |

| 6 Advisory Descriptions                                            | 7 |

| 7 Revision History                                                 |   |

# 1 Functional Advisories

Advisories that affect the device's operation, function, or parametrics.

$\checkmark$  The check mark indicates that the issue is present in the specified revision.

| V THE CHECK HIS |       |     |       |       |       |       |       |       |

|-----------------|-------|-----|-------|-------|-------|-------|-------|-------|

| Errata Number   | Rev K | Rev | Rev H | Rev G | Rev F | Rev E | Rev D | Rev C |

| COMP10          | 1     | 1   | 1     | 1     | 1     | 1     | 1     | 1     |

| CPU37           | 1     | 1   | 1     | 1     | 1     | 1     | 1     | 1     |

| CPU47           | 1     | 1   | 1     | 1     | 1     | 1     | 1     | 1     |

| DMA4            | 1     | 1   | 1     | 1     | 1     | 1     | 1     | 1     |

| DMA7            | 1     | 1   | 1     | 1     | 1     | 1     | 1     | ✓     |

| DMA8            | 1     | 1   | 1     | 1     | 1     | 1     | 1     | 1     |

| DMA10           | ✓     | ✓   | ✓     | ✓     | ✓     | ✓     | ✓     | 1     |

| FLASH33         | 1     | 1   | 1     | 1     | 1     | 1     | 1     | ✓     |

| FLASH34         | 1     | 1   | 1     | 1     | 1     | 1     | 1     | ✓     |

| FLASH35         |       |     |       |       |       |       | 1     | ✓     |

| FLASH37         |       |     |       |       |       | 1     | 1     | ✓     |

| MPY1            | ✓     | ✓   | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

| PMAP1           | 1     | 1   | 1     | 1     | 1     | 1     | 1     | ✓     |

| РММ9            | 1     | ✓   | ✓     | ✓     | ✓     | ✓     | 1     | ✓     |

| PMM10           |       |     |       |       |       | ✓     | 1     | ✓     |

| PMM11           | ✓     | 1   | 1     | 1     | 1     | 1     | ✓     | 1     |

| PMM12           | ✓     | ✓   | ✓     | ✓     | ✓     | ✓     | ✓     | 1     |

| PMM14           | 1     | 1   | 1     | 1     | 1     | 1     | 1     | 1     |

| PMM15           | ✓     | 1   | 1     | 1     | 1     | 1     | ✓     | 1     |

| PMM17           |       |     |       |       |       | 1     | 1     | 1     |

| PMM18           | 1     | 1   | 1     | 1     | 1     | 1     | 1     | 1     |

| PMM20           | 1     | 1   | 1     | 1     | 1     | 1     | 1     | ✓     |

| PORT15          | 1     | 1   | 1     | 1     | 1     | 1     | 1     | 1     |

| PORT16          | 1     | 1   | 1     | 1     | 1     | 1     | 1     | 1     |

| PORT19          | ✓     | 1   | 1     | 1     | 1     | 1     | ✓     | 1     |

| PORT24          | 1     | 1   | 1     | 1     | 1     | 1     | 1     | ✓     |

| RTC3            | 1     | 1   | 1     | 1     | 1     | 1     | 1     | ✓     |

| RTC6            | ✓     | ✓   | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

| SYS10           |       |     |       |       |       | ✓     | 1     | ✓     |

| SYS12           |       |     |       |       |       | ✓     | 1     | ✓     |

| SYS14           |       |     |       |       |       | 1     | 1     | ✓     |

| SYS16           | ✓     | ✓   | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

| SYS18           | ✓     | ✓   | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

| TAB23           | 1     | 1   | 1     | 1     | 1     | 1     | 1     | ✓     |

| USB4            |       |     |       |       |       | 1     | 1     | ✓     |

| USB6            |       |     |       |       |       | ✓     | ✓     | ✓     |

| USB8            |       |     |       |       |       | 1     | 1     | ✓     |

| USB9            |       |     |       | ✓     | ✓     | ✓     | ✓     | ✓     |

| USB10           | 1     | 1   | 1     | 1     | 1     | 1     | 1     | ✓     |

| USB11           |       | 1   |       |       |       |       |       |       |

| USB12           | 1     | 1   | 1     | 1     | 1     | 1     | 1     | ✓     |

| USB13           |       | ✓   |       |       |       |       |       |       |

| Errata Number | Rev K | Rev I | Rev H | Rev G | Rev F | Rev E | Rev D | Rev C |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| USCI26        | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

| USCI30        | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

| USCI31        | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

| USCI34        | 1     | 1     | 1     | ✓     | ✓     | ✓     | ✓     | ✓     |

| USCI35        | 1     | 1     | 1     | ✓     | ✓     | ✓     | ✓     | ✓     |

| USCI39        | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| USCI40        | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| WDG4          | 1     | 1     | 1     | ✓     | ✓     | ✓     | ✓     | ✓     |

# 2 Preprogrammed Software Advisories

Advisories that affect factory-programmed software.

✓ The check mark indicates that the issue is present in the specified revision.

| Errata Number | Rev K | Rev I | Rev H | Rev G | Rev F | Rev E | Rev D | Rev C |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| BSL6          |       |       | ✓     | ✓     | ✓     |       |       |       |

| BSL7          |       | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

| JTAG20        | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

# 3 Debug Only Advisories

Advisories that affect only debug operation.

✓ The check mark indicates that the issue is present in the specified revision.

| Errata Number | Rev K | Rev I | Rev H | Rev G | Rev F | Rev E | Rev D | Rev C |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| EEM9          | ✓     | ✓     | ✓     | ✓     | 1     | 1     | ✓     | ✓     |

| EEM11         | ✓     | ✓     | ✓     | ✓     | 1     | 1     | ✓     | ✓     |

| EEM13         | ✓     | ✓     | ✓     | 1     | 1     | 1     | 1     | ✓     |

| EEM14         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

| EEM15         | ✓     | ✓     | ✓     | ✓     | 1     | 1     | ✓     | ✓     |

| EEM16         | ✓     | ✓     | ✓     | ✓     | 1     | 1     | ✓     | ✓     |

| EEM17         | ✓     | ✓     | ✓     | ✓     | 1     | 1     | ✓     | ✓     |

| EEM19         | ✓     | ✓     | ✓     | 1     | 1     | 1     | 1     | ✓     |

| EEM21         | ✓     | ✓     | ✓     | 1     | 1     | 1     | 1     | ✓     |

| EEM23         | ✓     | ✓     | ✓     | ✓     | 1     | 1     | ✓     | ✓     |

| JTAG26        | ✓     | ✓     | ✓     | 1     | 1     | 1     | 1     | ✓     |

| JTAG27        | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

# 4 Fixed by Compiler Advisories

Advisories that are resolved by compiler workaround. Refer to each advisory for the IDE and compiler versions with a workaround.

✓ The check mark indicates that the issue is present in the specified revision.

| Errata Number | Rev K | Rev I | Rev H | Rev G | Rev F | Rev E | Rev D | Rev C |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| CPU21         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     |

| CPU22         | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

|               | V     |       | I     | O     | ш     | ш     | ۵     | O        |

|---------------|-------|-------|-------|-------|-------|-------|-------|----------|

| Errata Number | Rev K | Rev I | Rev F | Rev ( | Rev F | Rev F | Rev I | Rev (    |

| Errata Number | œ     | œ     | œ     | œ     | œ     | œ     | œ     | <b>E</b> |

| CPU23         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓        |

| CPU26         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓        |

| CPU27         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓        |

| CPU28         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓        |

| CPU29         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓        |

| CPU30         | 1     | 1     | ✓     | ✓     | 1     | ✓     | 1     | ✓        |

| CPU31         | 1     | 1     | ✓     | ✓     | 1     | ✓     | 1     | ✓        |

| CPU32         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓        |

| CPU33         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓        |

| CPU34         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓        |

| CPU35         | 1     | 1     | ✓     | ✓     | 1     | ✓     | 1     | ✓        |

| CPU39         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓        |

| CPU40         | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓     | ✓        |

Refer to the following MSP430 compiler documentation for more details about the CPU bugs workarounds.

# TI MSP430 Compiler Tools (Code Composer Studio IDE)

- MSP430 Optimizing C/C++ Compiler: Check the --silicon\_errata option

- MSP430 Assembly Language Tools

### MSP430 GNU Compiler (MSP430-GCC)

- MSP430 GCC Options: Check -msilicon-errata= and -msilicon-errata-warn= options

- MSP430 GCC User's Guide

# IAR Embedded Workbench

• IAR workarounds for msp430 hardware issues

# 5 Nomenclature, Package Symbolization, and Revision Identification

The revision of the device can be identified by the revision letter on the Package Markings or by the HW\_ID located inside the TLV structure of the device.

### 5.1 Device Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all MSP MCU devices. Each MSP MCU commercial family member has one of two prefixes: MSP or XMS. These prefixes represent evolutionary stages of product development from engineering prototypes (XMS) through fully qualified production devices (MSP).

**XMS** – Experimental device that is not necessarily representative of the final device's electrical specifications

MSP - Fully qualified production device

Support tool naming prefixes:

X: Development-support product that has not yet completed Texas Instruments internal qualification testing.

null: Fully-qualified development-support product.

XMS devices and X development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

MSP devices have been characterized fully, and the quality and reliability of the device have been demonstrated fully. Tl's standard warranty applies.

Predictions show that prototype devices (XMS) have a greater failure rate than the standard production devices. TI recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

TI device nomenclature also includes a suffix with the device family name. This suffix indicates the temperature range, package type, and distribution format.

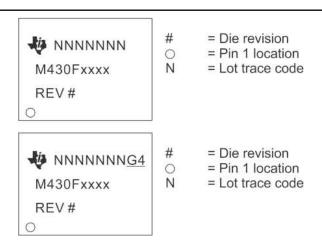

### 5.2 Package Markings

#### **PN80**

#### LQFP (PN), 80 Pin

### 5.3 Memory-Mapped Hardware Revision (TLV Structure)

| Die Revision | TLV Hardware Revision |

|--------------|-----------------------|

| Rev K        | 19h                   |

| Rev I        | 18h                   |

| Rev H        | 17h                   |

| Rev G        | 16h                   |

| Die Revision | TLV Hardware Revision |

|--------------|-----------------------|

| Rev F        | 15h                   |

| Rev E        | 14h                   |

| Rev D        | 13h                   |

| Rev C        | 12h                   |

Further guidance on how to locate the TLV structure and read out the HW\_ID can be found in the device User's Guide.

# **6 Advisory Descriptions**

BSL6 BSL Module

**Category** Software in ROM

**Function** USB BSL does not respond properly to suspend/reset events from the USB host

**Description** The USB BSL in affected revisions contains an improper configuration of the USB

module. As a result, errors might occur in response to suspend/reset events from the USB host. (Since enumeration of the USB device often involves suspend and/or reset events, an enumeration might trigger the failure.) If the failure occurs, the device becomes

unresponsive to the USB host.

If the failure occurs, and if application code exists in main flash, a reset (BOR/POR/PUC) can be issued to switch execution away from the BSL, to the application. Given the same USB host/setup circumstances, the problem is likely to occur again on subsequent attempts.

Applications that do not use the USB BSL are unaffected.

-

1. The BSL can be updated via JTAG with a version that does not contain this bug. Use the code published in BSL documentation starting with version 00.07.85.36.

BSL7 BSL Module

Workaround

**Category** Software in ROM

**Function** BSL does not start after waking up from LPMx.5

**Description** When waking up from LPMx.5 mode, the BSL does not start as it does not clear the Lock

I/O bit (LOCKLPM5 bit in PM5CTL0 register) on start-up.

Workaround 1. Upgrade the device BSL to the latest version (see Creating a Custom Flash-Based

Bootstrap Loader (BSL) Application Note - SLAA450 for more details)

OR

2. Do not use LOCKLPM5 bit (LPMx.5) if the BSL is used but cannot be upgraded.

COMP10 COMP Module

Category Functional

**Function** Comparator port output toggles when entering or leaving LPM3/LPM4

**Description** The comparator port pin output (CECTL1.CEOUT) erroneously toggles when device

enters or leaves LPM3/LPM4 modes under the following conditions:

1) Comparator is disabled (CECTL1.CEON = 0)

AND

2) Output polarity is enabled (CECTL1.CEOUTPOL = 1)

**AND**

3) The port pin is configured to have CEOUT functionality.

For example, if the CEOUT pin is high when the device is in Active Mode, CEOUT pin becomes low when the device enters LPM3/LPM4 modes.

#### Workaround

When the comparator is disabled, ensure at least one of the following:

1) Output inversion is disabled (CECTL.CEOUTPOL = 0)

OR

2) Change pin configuration from CEOUT to GPIO with output low.

### CPU21

#### **CPU Module**

Category

Compiler-Fixed

**Function**

Using POPM instruction on Status register may result in device hang up

**Description**

When an active interrupt service request is pending and the POPM instruction is used to set the Status Register (SR) and initiate entry into a low power mode, the device may hang up.

Workaround

None. It is recommended not to use POPM instruction on the Status Register.

Refer to the table below for compiler-specific fix implementation information.

| IDE/Compiler                                       | Version Number                    | Notes                                                                                    |

|----------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------|

| IAR Embedded Workbench                             | Not affected                      |                                                                                          |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | v4.0.x or later                   | User is required to add the compiler or assembler flag option below silicon_errata=CPU21 |

| MSP430 GNU Compiler (MSP430-GCC)                   | MSP430-GCC 4.9 build 167 or later |                                                                                          |

### CPU22

### CPU Module

Category

Compiler-Fixed

**Function**

Indirect addressing mode with the Program Counter as the source register may produce unexpected results

Description

When using the indirect addressing mode in an instruction with the Program Counter (PC) as the source operand, the instruction that follows immediately does not get executed. For example in the code below, the ADD instruction does not get executed.

mov @PC, R7 add #1h, R4

### Workaround

Refer to the table below for compiler-specific fix implementation information.

| IDE/Compiler           | Version Number | Notes |

|------------------------|----------------|-------|

| IAR Embedded Workbench | Not affected   |       |

| IDE/Compiler                                       | Version Number                    | Notes                                                                                    |

|----------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------|

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | v4.0.x or later                   | User is required to add the compiler or assembler flag option below silicon_errata=CPU22 |

| MSP430 GNU Compiler (MSP430-GCC)                   | MSP430-GCC 4.9 build 167 or later |                                                                                          |

CPU23 CPU Module

Category Compiler-Fixed

**Function** Rotate instruction does not function as expected

**Description** When repeated rotate instructions (rrcm, rram, rrum and rlam) are applied on the Program

Counter(PC), unexpected instruction execution may occur.

**Workaround** Insert a NOP instruction between sequential rotate instructions performed on the PC

register.

Refer to the table below for compiler-specific fix implementation information.

| IDE/Compiler                                       | Version Number                    | Notes                                                                                    |

|----------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------|

| IAR Embedded Workbench                             | Not affected                      |                                                                                          |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | v4.0.x or later                   | User is required to add the compiler or assembler flag option below silicon_errata=CPU23 |

| MSP430 GNU Compiler (MSP430-GCC)                   | MSP430-GCC 4.9 build 167 or later |                                                                                          |

CPU26 CPU Module

Category Compiler-Fixed

Function CALL SP instruction does not behave as expected

**Description** The intention of the CALL SP instruction is to execute code from the stack, instead it skips

the first piece of data (instruction) on the stack. The second piece of data at SP+2 is used

as the first executable instruction.

Workaround Write the op code for a NOP as the first instruction on the stack. Begin the intended

subroutine at address SP + 2.

Refer to the table below for compiler-specific fix implementation information.

| IDE/Compiler                                       | Version Number  | Notes |

|----------------------------------------------------|-----------------|-------|

| IAR Embedded Workbench                             | Not affected    |       |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | v4.1.3 or later |       |

| MSP430 GNU Compiler (MSP430-GCC)                   | Not affected    |       |

CPU27 CPU Module

Category Compiler-Fixed

**Function** Program Counter (PC) is corrupted during the context save of a nested interrupt

**Description** When a low power mode is entered within an interrupt service routine that has enabled

nested interrupts (by setting the GIE bit), and the instruction that sets the low power mode is directly followed by a RETI instruction, an incorrect value of PC + 2 is pushed to the stack during the context save. Hence, the RETI instruction is not executed on return from

the nested interrupt and the PC becomes corrupted.

**Workaround** Insert a NOP or \_\_no\_operation() intrinsic function between the instruction that sets the lower power mode and the RETI instruction.

Refer to the table below for compiler-specific fix implementation information.

| IDE/Compiler                                       | Version Number              | Notes                                                                                           |

|----------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------|

| IAR Embedded Workbench                             | IAR EW430 v6.20 until v6.40 | User is required to add the compiler or assembler flag option below hw_workaround=nop_after_lpm |

| IAR Embedded Workbench                             | IAR EW430 v6.40 or later    | Workaround is automatically enabled                                                             |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | v4.1.3 or later             |                                                                                                 |

| MSP430 GNU Compiler (MSP430-GCC)                   | MSP430-GCC 4.9 build 167    |                                                                                                 |

CPU28 CPU Module

Category Compiler-Fixed

**Function** PC is corrupted when using certain extended addressing mode combinations

**Description**An extended memory instruction that modifies the program counter executes incorrectly when preceded by an extended memory write-back instruction under the following

conditions:

First instruction:

2-operand instruction, extended mode using (register,index), (register,absolute), OR

(register,symbolic) addressing modes

Second instruction:

2-operand instruction, extended mode using the (indirect,PC), (indirect auto-increment,PC), OR (indexed [with ind 0], PC) addressing modes

morement, O, Or (indexed [with ind o], 1 O) addressing modes

Example:

BISX.A R6,&AABCD ANDX.A @R4+,PC

Workaround 1. Insert a NOP or a no operation() intrinsic function between the two instructions

Or

2. Do not use an extended memory instruction to modify the PC

Refer to the table below for compiler-specific fix implementation information.

| IDE/Compiler                                       | Version Number  | Notes |

|----------------------------------------------------|-----------------|-------|

| IAR Embedded Workbench                             | Not affected    |       |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | v4.1.3 or later |       |

| MSP430 GNU Compiler (MSP430-GCC)                   | Not affected    |       |

CPU29

#### **CPU Module**

Category

Compiler-Fixed

**Function**

Using a certain instruction sequence to enter low power mode(s) affects the instruction width of the first instruction in an NMI ISR

**Description**

If there is a pending NMI request when the CPU enters a low power mode (LPMx) using an instruction of Indexed source addressing mode, and that instruction is followed by a 20-bit wide instruction of Register source and destination addressing modes, the first instruction of the ISR is executed as a 20-bit wide instruction.

Example:

main:

...

MOV.W [indexed],SR; Enter LPMx

MOVX.A [register], [register]; 20-bit wide instruction

...

ISR\_start:

MOV.B [indexed], [register]; ERROR - Executed as a 20-bit instruction!

Note: [] indicates addressing mode

### Workaround

1. Insert a NOP or a \_\_no\_operation() intrinsic function following the instruction that enters the LPMx using indexed addressing mode

OR

2. Use a NOP or a no operation() intrinsic function as first instruction in the ISR

OR

3. Do not use the indexed mode to enter LPMx

Refer to the table below for compiler-specific fix implementation information.

| IDE/Compiler           | Version Number              | Notes                                |

|------------------------|-----------------------------|--------------------------------------|

|                        |                             | User is required to add the compiler |

| IAR Embedded Workbench | IAR EW430 v6.20 until v6.40 | or assembler flag option below       |

|                        |                             | hw_workaround=nop_after_lpm          |

| IDE/Compiler                                       | Version Number           | Notes                               |

|----------------------------------------------------|--------------------------|-------------------------------------|

| IAR Embedded Workbench                             | IAR EW430 v6.40 or later | Workaround is automatically enabled |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | v4.1.3 or later          |                                     |

| MSP430 GNU Compiler (MSP430-GCC)                   | MSP430-GCC 4.9 build 167 |                                     |

CPU<sub>30</sub>

**CPU Module**

Category

Compiler-Fixed

**Function**

ADDA, SUBA, CMPA [immediate],PC behave as if immediate value were offset by -2

**Description**

The extended address instructions ADDA, SUBA, CMPA in immediate addressing mode are represented by 4-bytes of opcode (see the MSP430F5xx Family User's Guide MSP430F5xx Family User's Guide for more details). In cases where the program counter (PC) is used as the destination register only 2 bytes of the current instruction's 4-byte opcode are accounted for in the PC value. The resulting operation executes as if the immediate value were offset by a value of -2.

Ideal: ADDA #Immediate-4, PC

...is equivalent to...

Actual: ADDA #Immediate-2, PC

\*\* NOTE: The MOV instruction is not affected \*\*

Workaround

1) Modify immediate value in software to account for the offset of 2.

OR

2) Use extended 20-bit instructions (addx.a, subx.a, cmpx.a).

Refer to the table below for compiler-specific fix implementation information.

| IDE/Compiler                                       | Version Number           | Notes                                                                                                                                                  |

|----------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| IAR Embedded Workbench                             | IAR EW430 v5.30 or later | IDE-based usage enables the workaround automatically. When using the command line, user is required to add the option below: Linker: -D?CPU30_OFFSET=2 |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | v4.0 or later            |                                                                                                                                                        |

| MSP430 GNU Compiler (MSP430-GCC)                   | Not affected             |                                                                                                                                                        |

CPU31

**CPU Module**

Category

Compiler-Fixed

www.ti.com Advisory Descriptions

**Function** SP corruption

**Description** When the instruction PUSHX.A is executed using the indirect auto-increment mode with

the stack pointer (SP) as the source register [PUSHX.A @SP+] the SP is consequently corrupted. Instead of decrementing the value of the SP by four, the value of the SP is replaced with the data pointed to by the SP previous to the PUSHX.A instruction

execution.

**Workaround** None. Note that compilers will not generate a PUSHX.A instruction that involves the SP.

Refer to the table below for compiler-specific information.

| IDE/Compiler                                       | Version Number | Notes                                                                                    |

|----------------------------------------------------|----------------|------------------------------------------------------------------------------------------|

| IAR Embedded Workbench                             | Not affected   |                                                                                          |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | Not affected   | User is required to add the compiler or assembler flag option below silicon_errata=CPU18 |

| MSP430 GNU Compiler (MSP430-GCC)                   | Not affected   |                                                                                          |

CPU32 CPU Module

Category Compiler-Fixed

**Function** CALLA PC executes incorrectly

**Description** When the instruction CALLA PC is executed, the program counter (PC) that is pushed

onto the stack during the context save is incorrectly offset by a value of -2.

**Workaround** None. Note that compilers will not generate a CALLA PC instruction.

Refer to the table below for compiler-specific information.

| IDE/Compiler                                       | Version Number | Notes |

|----------------------------------------------------|----------------|-------|

| IAR Embedded Workbench                             | Not affected   |       |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | Not affected   |       |

| MSP430 GNU Compiler (MSP430-GCC)                   | Not affected   |       |

CPU33 CPU Module

Category Compiler-Fixed

**Function** CALLA [indexed] may corrupt the program counter

**Description** When the Stack Pointer (SP) is used as the destination register in the CALLA

index(Rdst) instruction and is preceded by a PUSH or PUSHX instruction in any of the following addressing modes: Absolute, Symbolic, Indexed, Indirect register or Indirect auto increment, the "index" of the CALLA instruction is not sign extended to 20-bits and is always treated as a positive value. This causes the Program Counter to be set to a wrong address location when the index of the CALLA instruction represents a negative offset.

### NOTE:

- 1. This erratum only applies when the instruction sequence is: PUSH or PUSHX followed by CALLA index(SP)

- 2. This erratum does not apply if the PUSH or PUSHX instruction is used in the Register or Immediate addressing mode

- 3. This erratum only applies when SP is used as the destination register in the CALLA index(Rdst) instruction

#### Workaround

Place a "NOP" instruction in between the PUSH or PUSHX and the CALLA index(SP) instructions.

NOTE: This bug has no compiler impact as the compiler will not generate a CALLA instruction that uses indexed addressing mode with the SP.

Refer to the table below for compiler-specific information.

| IDE/Compiler                                       | Version Number | Notes |

|----------------------------------------------------|----------------|-------|

| IAR Embedded Workbench                             | Not affected   |       |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | Not affected   |       |

| MSP430 GNU Compiler (MSP430-GCC)                   | Not affected   |       |

CPU34 CPU Module

Category Compiler-Fixed

**Function** CPU may be halted if a conditional jump is followed by a rotate PC instruction

**Description** If a conditional jump instruction (JZ, JNZ, JC, JNC, JN, JGE, JL) is followed by an

Address Rotate instruction on the PC (RRCM, RRAM, RLAM, RRUM) and the jump is not

performed, the CPU is halted.

**Workaround** Insert a NOP between the conditional jump and the rotate PC instructions.

Refer to the table below for compiler-specific information.

| IDE/Compiler                                       | Version Number | Notes |

|----------------------------------------------------|----------------|-------|

| IAR Embedded Workbench                             | Not affected   |       |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | Not affected   |       |

| MSP430 GNU Compiler (MSP430-GCC)                   | Not affected   |       |

CPU35 CPU Module

Category Compiler-Fixed

**Function** Instruction BIT.B @Rx,PC uses the wrong PC value

www.ti.com Advisory Descriptions

### Description

The BIT(.B/.W) instruction in indirect register addressing mode uses the wrong PC value. This instruction is represented by 2 bytes of opcode. If the Program Counter (PC) is used as the destination register, the 2 opcode bytes of the current BIT instruction are not accounted for. The resulting operation executes the instruction using the wrong PC value and this affects the results in the Status Register (SR).

#### Workaround

None. Note that compilers will not generate a BIT instruction that uses the PC as an operand.

Refer to the table below for compiler-specific information.

| IDE/Compiler                                       | Version Number | Notes |

|----------------------------------------------------|----------------|-------|

| IAR Embedded Workbench                             | Not affected   |       |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | Not affected   |       |

| MSP430 GNU Compiler (MSP430-GCC)                   | Not affected   |       |

CPU37 CPU Module

Category

**Functional**

**Function**

Wrong program trace display in the debugger while using conditional jump instructions

Description

The state storage window displays an incorrect sequence of instructions when:

1. Conditional jump instructions are used to form a software loop

AND

2. A false condition on the jump breaks out of the loop

In such cases the trace buffer incorrectly displays the first instruction of the loop as the instruction that is executed immediately after exiting the loop.

Example:

Actual Code:

mov #4,R4

LABEL mov #1,R5

dec R4

jnz LABEL

mov #2,R6

nop

State Storage Window Displays:

LABEL mov #1,R5

dec R4

inz LABEL

mov #1,R5

nop

Workaround None

Note: This erratum affects the trace buffer display only. It does not affect code execution in debugger or free run mode

CPU Module **CPU39**

Compiler-Fixed Category

**Function** PC is corrupted when single-stepping through an instruction that clears the GIE bit

Description Single-stepping over an instruction that clears the General Interrupt Enable bit (for example DINT or BIC #GIE,SR) when the GIE bit was previously set may corrupt the PC. For example, the DINT or BIC #GIE,SR is a 2-byte instruction. Single stepping through

value.

Note: This erratum applies to debug mode only.

Workaround Insert a NOP or no operation() intrinsic immediately after the line of code that clears the GIE bit.

OR

Refer to the table below for compiler-specific fix implementation information. Note that compilers implementing the fix may lead to double stack usage when RET/ RETA follows the compiler-inserted NOP.

this instruction increments the PC by a value of 4 instead of 2 thus corrupting the next PC

| IDE/Compiler                                       | Version Number                    | Notes                                                                                                                                                                  |

|----------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IAR Embedded Workbench                             | IAR EW430 v5.60 until v6.20       | User is required to add the compiler flag option below hw_workaround=CPU39 For the command line version add the following information Compiler: core=430 Assembler:-v1 |

| IAR Embedded Workbench                             | IAR EW430 v6.20 or later          | Workaround is automatically enabled                                                                                                                                    |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | v4.1.3 or later                   |                                                                                                                                                                        |

| MSP430 GNU Compiler (MSP430-GCC)                   | MSP430-GCC 4.9 build 167 or later |                                                                                                                                                                        |

**CPU Module** CPU40

Category Compiler-Fixed

**Function** PC is corrupted when executing jump/conditional jump instruction that is followed by

instruction with PC as destination register or a data section

If the value at the memory location immediately following a jump/conditional jump instruction is 0X40h or 0X50h (where X = don't care), which could either be an instruction opcode (for instructions like RRCM, RRAM, RLAM, RRUM) with PC as destination register or a data section (const data in flash memory or data variable in RAM), then the PC value is auto-incremented by 2 after the jump instruction is executed;

therefore, branching to a wrong address location in code and leading to wrong program execution.

For example, a conditional jump instruction followed by data section (0140h).

**Description**

@0x8012 Loop DEC.W R6 @0x8014 DEC.W R7 @0x8016 JNZ Loop @0x8018 Value1 DW 0140h

### Workaround

In assembly, insert a NOP between the jump/conditional jump instruction and program code with instruction that contains PC as destination register or the data section.

Refer to the table below for compiler-specific fix implementation information.

| IDE/Compiler                                       | Version Number           | Notes                                                                                                 |

|----------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------|

| IAR Embedded Workbench                             | IAR EW430 v5.51 or later | For the command line version add the following information Compiler:hw_workaround=CPU40 Assembler:-v1 |

| TI MSP430 Compiler Tools (Code<br>Composer Studio) | v4.0.x or later          | User is required to add the compiler or assembler flag option below silicon_errata=CPU40              |

| MSP430 GNU Compiler (MSP430-GCC)                   | Not affected             |                                                                                                       |

| CPH47  | CPU Module  |

|--------|-------------|

| (:PH4/ | or o module |

**Category** Functional

Function An unexpected Vacant Memory Access Flag (VMAIFG) can be triggered

**Description** An unexpected Vacant Memory Access Flag (VMAIFG) can be triggered, if a PC-

modifying instruction (e.g. - ret, push, call, pop, jmp, br) is fetched from the last addresses (last 4 or 8 byte) of a memory (e.g.- FLASH, RAM, FRAM) that is not contiguous to a

higher, valid section on the memory map.

In debug mode using breakpoints the last 8 bytes are affected.

In free running mode the last 4 bytes are affected.

**Workaround** Edit the linker command file to make the last 4 or 8 bytes of affected memory sections

unavailable, to avoid PC-modifying instructions on these locations. Remaining instructions or data can still be stored on these locations.

DMA4 DMA Module

Category Functional

Function Corrupted write access to 20-bit DMA registers

**Description** When a 20-bit wide write to a DMA address register (DMAxSA or DMAxDA) is interrupted

by a DMA transfer, the register contents may be unpredictable.

Workaround

1. Design the application to guarantee that no DMA access interrupts 20-bit wide

accesses to the DMA address registers.

OR

2. When accessing the DMA address registers, enable the Read Modify Write disable bit (DMARMWDIS = 1) or temporarily disable all active DMA channels (DMAEN = 0).

OR

3. Use word access for accessing the DMA address registers. Note that this limits the values that can be written to the address registers to 16-bit values (lower 64K of Flash).

DMA7 DMA Module

**Category** Functional

**Function** DMA request may cause the loss of interrupts

**Description** If a DMA request starts executing during the time when a module register containing an

interrupt flags is accessed with a read-modify-write instruction, a newly arriving interrupt from the same module can get lost. An interrupt flag set prior to DMA execution would not

be affected and remain set.

Workaround 1. Use a read of Interrupt Vector registers to clear interrupt flags and do not use read-

modify-write instruction.

OR

2. Disable all DMA channels during read-modify-write instruction of specific module

registers containing interrupts flags while these interrupts are activated.

DMA8 DMA Module

**Category** Functional

**Function** DMA can corrupt values on write-access to program stack

**Description** If the DMA controller makes a write access to the stack while executing one of the

following instructions, the data that is written may be corrupted.

CALLA [REG | IDX | SYM | ABS | IND | INA | IMM] PUSHX.A [IDX | SYM | ABS | IND | IMM | INA]

PUSHX.A [REG] PUSHM.A [REG] POPM.A [REG]

Note: [ ... ] denotes an addressing mode

Workaround Do not declare function-scope variables. Declare all variables that are intended to be

modified by the DMA as global- or file-scope such that they are allocated in the data

section of RAM and not on the program stack.

DMA10 DMA Module

**Category** Functional

**Function** DMA access may cause invalid module operation

**Description** The peripheral modules MPY, CRC, USB, RF1A and FRAM controller in manual mode

can stall the CPU by issuing wait states while in operation. If a DMA access to the

module occurs while that module is issuing a wait state, the module may exhibit undefined

behavior.

www.ti.com Advisory Descriptions

Workaround Ensure that DMA accesses to the affected modules occur only when the modules are

not in operation. For example with the MPY module, ensure that the MPY operation is

completed before triggering a DMA access to the MPY module.

EEM9 EEM Module

Category Debug

**Function** Combined triggers on the PUSH instruction may be missed

**Description** When the PUSH instruction is used in any addressing mode except register or immediate

modes, a combined trigger may be missed when its conditions are defined by a PUSH

instruction fetch and a successful match of the value being pushed onto stack.

Workaround None

EEM11 EEM Module

**Category** Debug

**Function** Conditional register write trigger fails while executing rotate instructions

**Description** A conditional register write trigger will fail to generate the expected breakpoint if

the trigger condition is a result of executing one of the following rotate instructions:

RRUM, RRCM, RRAM and RLAM.

Workaround None

Note

This erratum applies to debug mode only.

EEM13 EEM Module

Category Debug

Function Halting the debugger does not return correct PC value when in LPM

**Description** When debugging, if the device is in any low power mode and the debugger is halted, the

program counter update by the debugger is corrupted. The debugger is unable to halt at

the correct location.

Workaround None.

Note

This erratum applies to debug mode only.

EEM14 EEM Module

Category Debug

**Function** Single-step or breakpoint on module registers with WAIT capability may not work

**Description** In debug mode, the CPU clock is driven independently from the wait inputs of device

modules (i.e., MULT, USB, RF1A, CRC). As a result, an EEM halt on an access to

the module data registers (breakpoint or single-step) may show incorrect results due to incomplete execution.

#### Workaround

Do not single-step through a data register access that holds the CPU to provide a valid result. Place breakpoints after the affected register is accessed and sufficient clock cycles have been provided.

Note

This erratum applies to debug mode only.

EEM15 EEM Module

**Category** Debug

Function Read or write to RF1A, CRC, MULT and USB RAM may be corrupted when debugging

**Description** When performing read or write operations on modules that require CPU wait cycles (i.e.

when accessing CRC, RF1A, MULT and USB RAM) setting a breakpoint on or single

stepping through the operation could corrupt the result.

Workaround None

Note

This erratum applies to debug mode only.

EEM16 EEM Module

Category Debug

**Function** The state storage display does not work reliably when used on instructions with CPU Wait

cycles.

**Description** When executing instructions that require wait states; the state storage window updates

incorrectly. For example a flash erase instruction causes the CPU to be held until the erase is completed i.e. the flash puts the CPU in a wait state. During this time if the state storage window is enabled it may incorrectly display any previously executed instruction

multiple times.

Workaround Do not enable the state storage display when executing instructions that require wait

states. Instead set a breakpoint after the instruction is completed to view the state storage

display.

Note

This erratum affects debug mode only.

EEM17 EEM Module

Category Debug

**Function** Wrong Breakpoint halt after executing Flash Erase/Write instructions

www.ti.com Advisory Descriptions

**Description**

Hardware breakpoints or Conditional Address triggered breakpoints on instructions that follow Flash Erase/Write instructions, stops the debugger at the actual Flash Erase/Write instruction even though the flash erase/write operation has already been executed. The hardware/conditional address triggered breakpoints that are placed on either the next two single opcode instructions OR the next double opcode instruction that follows the Flash Erase/Write instruction are affected by this erratum.

Workaround

None. Use other conditional/advanced triggered breakpoints to halt the debugger right after Flash erase/write instructions.

Note

This erratum affects debug mode only.

EEM19 EEM Module

**Category** Debug

**Function** DMA may corrupt data in debug mode

**Description** When the DMA is enabled and the device is in debug mode, the data written by the DMA

may be corrupted when a breakpoint is hit or when the debug session is halted.

Workaround This erratum has been addressed in MSPDebugStack version 3.5.0.1. It is also available

in released IDE EW430 IAR version 6.30.3 and CCS version 6.1.1 or newer.

If using an earlier version of either IDE or MSPDebugStack, do not halt or use breakpoints

during a DMA transfer.

Note

This erratum applies to debug mode only.

EEM21 EEM Module

Category Debug

**Function** LPMx.5 debug limitations

**Description** Debugging the device in LPMx.5 mode might wake the device up from LPMx.5 mode

inadvertently, and it is possible that the device enters a lock-up condition; that is, the

device cannot be accessed by the debugger any more.

Workaround Follow the debugging steps in Debugging MSP430 LPM4.5 SLAA424.

EEM23 EEM Module

**Category** Debug

Function EEM triggers incorrectly when modules using wait states are enabled

**Description** When modules using wait states (USB, MPY, CRC and FRAM controller in manual mode)

are enabled, the EEM may trigger incorrectly. This can lead to an incorrect profile counter value or cause issues with the EEMs data watch point, state storage, and breakpoint

functionality.

Workaround None.

#### Note

This erratum affects debug mode only.

FLASH33 FLASH Module

**Category** Functional

Function Flash erase/program with fsystem <160kHz causes code execution to fail

**Description** A flash erase or flash program operation with the system frequency (fsystem) <160kHz

causes the program execution (executing out of main or info memory) that follows to fail.

**Workaround** Make sure the fsystem >160kHz before doing a flash erase or program operation.

FLASH34 FLASH Module

**Category** Functional

**Function** Concurrent flash read during bank erase fails

**Description** Code residing in flash cannot be executed during a bank erase.

**Workaround** Place the code to be executed during bank erase in RAM.

FLASH35 FLASH Module

**Category** Functional

Function Flash read error may cause invalid memory access

**Description** Flash memory accesses are always 32-bit wide and performed on 32-bit boundaries. A read error when accessing flash may corrupt the second most significant bit (MSB-1) in a

32-bit access when programmed as a logic 0.

When affected flash is idle, the read disturb may occur on the first flash access that

follows any of the listed events:

- On reset issued at RST input pin

- On wakeup from low-power modes when executing interrupt service routines located at

addresses <0xC400

- When moving program execution from unaffected to affected areas of flash

- When accessing affected flash after execution from RAM

Workaround See Flash Read Error and Susceptibility for MSP430F55xx (SLAA471) for detailed

background information and possible workaround(s).

FLASH37 FLASH Module

Category Functional

**Function** Corrupted flash read when SVM low-side flag is triggered

**Description** If the SVM low side is enabled, a change in the VCORE voltage level (an increase in the

VCORE level) may cause the currently executed read operation from flash to be incorrect and may lead to unexpected code execution or incorrect data. This can happen under any

one of the following conditions:

- When the VCORE is changed in application, the SVM low side is used to indicate if the core voltage has settled by using the SVMDLYIFG flag. The failure occurs only when a flash access is concurrent to the expiration of the settling time delay.

- Unexpected changes in the VCORE voltage level

For code examples and detailed guidance on the PMM operation and software APIs for PMM configuration see the driverlib APIs from 430Ware (MSP430Ware).

#### Workaround

- Execute the procedure to change the VCORE level from RAM.

or

- If executing from flash, follow the procedure below when increasing the VCORE level. Note: To apply this workaround, the SVM low-side comparator must operate in normal mode (SVMLFP = 0 in SVMLCTL).

```

// Set SVM highside to new level and check if a VCore increase is possible

SVSMHCTL = SVMHE | SVSHE | (SVSMHRRL0 * level);

// Wait until SVM highside is settled

while ((PMMIFG & SVSMHDLYIFG) == 0);

// Clear flag

PMMIFG &= ~SVSMHDLYIFG;

// Set also SVS highside to new level

// Vcc is high enough for a Vcore increase

SVSMHCTL |= (SVSHRVL0 * level);

// Wait until SVM highside is settled

while ((PMMIFG & SVSMHDLYIFG) == 0);

// Clear flag

PMMIFG &= ~SVSMHDLYIFG;

//******flow change for errata workaround *********

// Set VCore to new level

PMMCTL0 L = PMMCOREV0 * level;

// Set SVM, SVS low side to new level

SVSMLCTL = SVMLE | (SVSMLRRL0 * level)| SVSLE | (SVSLRVL0 * level);

// Wait until SVM, SVS low side is settled

while ((PMMIFG & SVSMLDLYIFG) == 0);

// Clear flag

PMMIFG &= ~SVSMLDLYIFG;

//******flow change for errata workaround ********

```

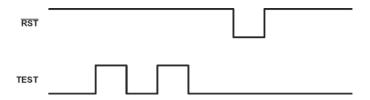

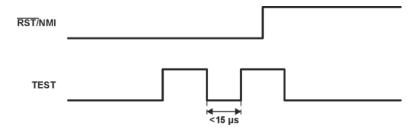

# JTAG20 JTAG Module

Category Software in ROM

**Function** BSL does not exit to application code

**Description** The methods used to exit the BSL per MSP430 Programming Via the Bootstrap Loader

(SLAU319) are invalid.

#### Workaround

To exit the BSL one of the following methods must be used.

- A Power cycle

or

- Toggle the TEST pin twice when nRST is high and after 50us pull nRST low.

Note: This toggling of TEST pins is not subject to timing constraints. The appropriate level transitions on TEST pin, followed by a RST pulse after 50us, are sufficient to trigger an exit from BSL mode.

### JTAG26

#### JTAG Module

### Category

Debug

#### **Function**

LPMx.5 Debug Support Limitations

#### **Description**

The JTAG connection to the device might fail at device-dependent low or high supply voltage levels if the LPMx.5 debug support feature is enabled. To avoid a potentially unreliable debug session or general issues with JTAG device connectivity and the resulting bad customer experience Texas Instruments has chosen to remove the LPMx.5 debug support feature from common MSP430 IDEs including TIs Code Composer Studio 6.1.0 with msp430.emu updated to version 6.1.0.7 and IARs Embedded Workbench 6.30.2, which are based on the MSP430 debug stack MSP430.DLL 3.5.0.1 http://www.ti.com/tool/MSPDS

TI plans to re-introduce this feature in limited capacity in a future release of the debug stack by providing an IDE override option for customers to selectively re-activate LPMx.5 debug support if needed. Note that the limitations and supply voltage dependencies outlined in this erratum will continue to apply.

For additional information on how the LPMx.5 debug support is handled within the MSP430 IDEs including possible workarounds on how to debug applications using LPMx.5 without toolchain support refer to Code Composer Studio User's Guide for MSP430 chapter F.4 and IAR Embedded Workbench User's Guide for MSP430 chapter 2.2.5.

### Workaround

- 1. If LPMx.5 debug support is deemed functional and required in a given scenario:

- a) Do not update the IDE to continue using a previous version of the debug stack such as MSP430.DLL v3.4.3.4.

OR

b) Roll back the debug stack by either performing a clean re-installation of a previous version of the IDE or by manually replacing the debug stack with a prior version such as MSP430.DLL v3.4.3.4 that can be obtained from http://www.ti.com/tool/MSPDS.

2. In case JTAG connectivity fails during the LPMx.5 debug mode, the device supply voltage level needs to be raised or lowered until the connection is working.

Do not enable the LPMx.5 debug support feature during production programming.

JTAG27 JTAG Module

**Category** Debug

Workaround

Function Unintentional code execution after programming via JTAG/SBW

**Description**The device can unintentionally start executing code from uninitialized RAM addresses 0x0006 or 0x0008 after being programming via the JTAG or SBW interface. This can result in unpredictable behavior depending on the contents of the address location.

1. If using programming tools purchased from TI (MSP-FET, LaunchPad), update to CCS version 6.1.3 later or IAR version 6.30 or later to resolve the issue.

2. If using the MSP-GANG Production Programmer, use v1.2.3.0 or later.

3. For custom programming solutions refer to the specification on MSP430 Programming Via the JTAG Interface User's Guide (SLAU320) revision V or newer and use MSPDebugStack v3.7.0.12 or later.

For MSPDebugStack (MSP430.DLL) in CCS or IAR, download the latest version of the development environment or the latest version of the MSPDebugStack

NOTE: This only affects debug mode.'

MPY1 MPY Module

Category Functional

**Function** Save and Restore feature on MPY32 not functional

**Description**The MPY32 module uses the Save and Restore method which involves saving the multiplier state by pushing the MPY configuration/operand values to the stack before using the multiplier inside an Interrupt Service Routine (ISR) and then restoring the state

by popping the configuration/operand values back to the MPY registers at the end of the ISR. However due to the erratum the Save and Restore operation fails causing the write operation to the OP2H register right after the restore operation to be ignored as it is not

preceded by a write to OP2L register resulting in an invalid multiply operation.

**Workaround** None. Disable interrupts when writing to OP2L and OP2H registers.

Note: When using the C-compiler, the interrupts are automatically disabled while using the

MPY32

PMAP1 PMAP Module

Category Functional

**Function** Port Mapping Controller does not clear unselected inputs to mapped module.

**Description**The Port Mapping Controller provides the logical OR of all port mapped inputs to a

module (Timer, USCI, etc). If the PSEL bit (PxSEL.y) of a port mapped input is cleared, then the logic level of that port mapped input is latched to the current logic level of the

input. If the input is in a logical high state, then this high state is latched into the input of the logical OR. In this case, the input to the module is always a logical 1 regardless of the state of the selected input.

### Workaround

1. Drive input to the low state before clearing the PSEL bit of that input and switching to another input source.

or

2. Use the Port Mapping Controller reconfiguration feature, PMAPRECFG, to select inputs to a module and map only one input at a time.

### **PMM9**

#### PMM Module

### Category

**Functional**

#### **Function**

False SVSxIFG events

### Description

The comparators of the SVS require a certain amount of time to stabilize and output a correct result once re-enabled; this time is different for the Full Performance versus the Normal mode. The time to stabilize the SVS comparators is intended to be accounted for by a built-in event-masking delay of 2 us when Full Performance mode is enabled. However, the comparators of the SVS in Full Performance mode take longer than 2 us to stabilize so the possibility exists that a false positive will be triggered on the SVSH or SVSL. This results in the SVSxIFG flags being set and depending on the configuration of SVSxPE bit a POR can also be triggered.

Additionally when the SVSxIFGs are set, all GPIOs are tri-stated i.e. floating until the SVSx comparators are settled.

The SVS IFG's are falsely set under the following conditions:

- 1. Wakeup from LPM2/3/4 when SVSxMD = 0 (default setting) && SVSxFP=1. The SVSx comparators are disabled automatically in LPM2/3/4 and are then re-enabled on return to active mode.

- 2. SVSx is turned on in full performance mode (SVSxFP=1).

- 3. A PUC/POR occurs after SVSx is disabled. After a PUC or POR the SVSx are enabled automatically but the settling delay does not get triggered. Based on SVSxPE bit this may lead to POR events until the SVS comparator is fully settled.

### Workaround

For each of the above listed conditions the following workarounds apply:

- 1. If the Full Performance mode is to be enabled for either the high- or low-side SVS comparators, the respective SVSxMD bits must be set (SVSxMD = 1) such that the SVS comparators are not temporarily shut off in LPM2/3/4. Note that this is equivalent to a 2 uA (typical) adder to the low power mode current, per the device-specific datasheet, for each SVSx that remains enabled.

- 2. The SVSx must be turned on in normal mode (SVSxFP=0). It can be reconfigured to use full performance mode once the SVSx/SVMx delay has expired.

- 3. Ensure that SVSH and SVSL are always enabled.

### **PMM10**

## PMM Module

#### Category

**Functional**

www.ti.com Advisory Descriptions

**Function** SVS/SVM flags disabled after Power Up Clear reset

**Description** SVS/SVM interrupt flag functionality is disabled after a Power Up Clear (PUC) Reset if the

SVS was disabled before the PUC reset was applied.

Workaround A write access to the intended SVSx register after PUC re-enables the SVS & SVM

interrupt flags.

PMM11 PMM Module

**Category** Functional

**Function** MCLK comes up fast on exit from LPM3 and LPM4

**Description** The DCO exceeds the programmed frequency of operation on exit from LPM3 and

LPM4 for up to 6 us. This behavior is masked from affecting code execution by default: SVSL and SVML run in normal-performance mode and mask CPU execution for 150 us on wakeup from LPM3 and LPM4. However ,when the low-side SVS and the SVM are disabled or are operating in full-performance mode (SVMLE= 0 and SVSLE= 0, or SVMLFP= 1 and SVSLFP= 1) AND MCLK is sourced from the internal DCO running over 4 MHz, 7 MHz,11 MHz,or 14 MHz at core voltage levels 0, 1, 2, and 3, respectively, the

mask lasts only 2 us. MCLK is, therefore, susceptible to run out of spec for 4 us.

Set the MCLK divide bits in the Unified Clock System Control 5 Register (UCSCTL5) to divide MCLK by two prior to entering LPM3 or LPM4 (set DIVMx= 001). This prevents

MCLK from running out of spec when the CPU wakes from the low-power mode. Following the wakeup from the low-power mode, wait 32, 48, 80, or 100 cycles for core voltage levels 0, 1, 2, and 3, respectively, before resetting DIVM xto zero and running

MCLK at full speed [for example, \_\_delay\_cycles(100)]

PMM12 PMM Module

Category Functional

Workaround

**Function** SMCLK comesup fast on exit from LPM3 and LPM4

**Description** The DCO exceeds the programmed frequency of operationon exit from LPM3 and LPM4

for up to 6 us. When SMCLK is sourced by the DCO, it is not masked on exit from LPM3 or LPM4. Therefore, SMCLK exceeds the programmed frequency of operation on exit from LPM3 and LPM4 for up to 6 us. The increased frequency has the potential to change

the expected timing behavior of peripherals that select SMCLK as the clock source.

Use XT2 as the SMCLK oscillator source instead of the DCO

or

- Do not disable the clock request bit for SMCLKREQEN in the Unified Clock System Control 8 Register (UCSCTL8). This means that all modules that depend on SMCLK to operate successfully should be halted or disabled before entering LPM3 or LPM4. If the increased frequency prevents the proper function of an affected module, wait 32, 48, 80 or 100 cycles for core voltage levels 0, 1, 2, or 3, respectively, before re-enabling the

module. (for example, \_\_delay\_cycles(100)

PMM14 PMM Module

**Category** Functional

**Function**

Increasing the core level when SVS/SVM low side is configured in full-performance mode causes device reset

**Description**

When the SVS/SVM low side is configured in full performance mode (SVSMLCTL.SVSLFP = 1), the setting time delay for the SVS comparators is ~2us. When increasing the core level in full-performance mode; the core voltage does not settle to the new level before the settling time delay of the SVS/SVM comparator expires. This results in a device reset.

Workaround

When increasing the core level; enable the SVS/SVM low side in normal mode (SVSMLCTL.SVSLFP=0). This provides a settling time delay of approximately 150us allowing the core sufficient time to increase to the expected voltage before the delay expires.

**PMM15**

### **PMM Module**

Category

Functional

**Function**

Device may not wake up from LPM2, LPM3, or LPM4

Description

Device may not wake up from LPM2, LPM3 or LMP4 if an interrupt occurs within 1 us after the entry to the specified LPMx; entry can be caused either by user code or automatically (for example, after a previous ISR is completed). Device can be recovered with an external reset or a power cycle. Additionally, a PUC can also be used to reset the failing condition and bring the device back to normal operation (for example, a PUC caused by the WDT).

This effect is seen when:

- A write to the SVSMHCTL and SVSMLCTL registers is immediately followed by an LPM2, LPM3, LPM4 entry without waiting the requisite settling time ((PMMIFG.SVSMLDLYIFG = 0 and PMMIFG.SVSMHDLYIFG = 0)).

or

The following two conditions are met:

- The SVSL module is configured for a fast wake-up or when the SVSL/SVML module is turned off. The affected SVSMLCTL register settings are shaded in the following table.

|      | SVSLE | SVSLMD | SVSLFP | AM, LPM0/1<br>SVSL state | Manual<br>SVSMLACE = 0<br>LPM2/3/4<br>SVSL State | Automatic<br>SVSMLACE = 1<br>LPM2/3/4<br>SVSL State | Wakeup Time<br>LPM2/3/4 |

|------|-------|--------|--------|--------------------------|--------------------------------------------------|-----------------------------------------------------|-------------------------|

| SVSL | 0     | Х      | х      | OFF                      | OFF                                              | OFF                                                 | twake-up fast           |

|      | 1     | 0      | 0      | Normal                   | OFF                                              | OFF                                                 | twake-up slow           |

|      | 1     | 0      | 1      | Full Performance         | OFF                                              | OFF                                                 | twake-up fast           |

|      | 1     | 1      | 0      | Normal                   | Normal                                           | OFF                                                 | twake-up slow           |

|      | 1     | 1      | 1      | Full Performance         | Full Performance                                 | Nomal                                               | twake-up fast           |

|      | SVMLE | SVMLFP |        | AM, LPM0/1<br>SVML state | Manual<br>SVSMLACE = 0<br>LPM2/3/4               | Automatic<br>SVSMLACE = 1<br>LPM2/3/4               | Wakeup Time<br>LPM2/3/4 |

| SVML | •     |        |        | 055                      | SVML State                                       | SVML State                                          |                         |

|      | 0     | X      |        | OFF                      | OFF                                              | OFF                                                 | TWAKE-UP FAST           |

|      | 1     | 0      |        | Normal                   | Normal                                           | OFF                                                 | twake-up slow           |

|      | 1     | 1      |        | Full Performance         | Full Performance                                 | Nomal                                               | twake-up fast           |

and

-The SVSH/SVMH module is configured to transition from Normal mode to an OFF state when moving from Active/LPM0/LPM1 into LPM2/LPM3/LPM4 modes. The affected SVSMHCTL register settings are shaded in the following table.

|      | SVSHE                  | SVSHMD | SVSHFP    | AM, LPMO/1 SVSH<br>state | Manual<br>SVSMHACE = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Automatic<br>SVSMHACE = 1 |

|------|------------------------|--------|-----------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|      |                        |        |           |                          | State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | LPM2/3/4 SVSH<br>State    |

|      | 0                      | ×      | ×         | OFF                      | OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | OFF                       |

| SVSH | 1                      | 0      | 0         | Normal                   | M, LPMO/1 SVSH state         SVSMHACE = 0         LPM2/3/4 SVSH   LVSMHACE = 0         SVSMHACE = 0 | OFF                       |

|      | 1 0 1 Full Performance | OFF    | OFF       |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |