# Board Layout Adjustments Between the TNETE2201B and TLK2201/TLK1201

Lori Schnier; Falk Alicke, Thomas Neu

HPA Wizard Serial Links

#### ABSTRACT

This report explains the different features and pin assignments between the TNETE2201B and the TLK2201/TLK1201 serializer/deserializer (SERDES) devices from Texas Instruments. The differences in pin functions are described and guidelines are given to design a board that allows the use of either device.

The TNETE2201B is a 3.3-V device and can interface with optical modules such as the HFBR53D5.

The TLK2201/TLK1201 in contrast is a pure CMOS design with advanced features, lower cost, reduced board component count, and one-third the power of the TNETE2201B. The output PECL driver has been designed to be compatible with the TNETE2201B, allowing an easy replacement option. Differences between the TLK2201 and TLK1201 can be seen in their respective datasheets.

|   |     | Contents                                                                  |   |

|---|-----|---------------------------------------------------------------------------|---|

| 1 | TL  | K2201/TLK1201 New Feature Description                                     | 2 |

|   | 1.1 | Serial Pins                                                               | 2 |

|   | 1.2 | JTAG                                                                      | 2 |

|   | 1.3 | DDR (Double Data Rate)                                                    | 2 |

|   |     | PRBS (Pseudo Random Bit Stream) Generation and Verification               |   |

|   |     | TNETE2201B vs. TLK2201/TLK1201                                            |   |

|   | 1.6 | Status of the TNETE2201B and TLK2201/TLK1201                              | 3 |

| 2 | Pin | ו Comparison Table                                                        | 3 |

| 3 | Ho  | w to Design a TNETE2201B Board that can also House a TLK2201/TLK1201      | 4 |

|   | 3.1 | Power Supply Adjustment                                                   | 4 |

|   |     | Installing the PLL Filter Capacitors at Pins 48, 49, 16 and 17            |   |

|   | 3.3 | Installing the Resistors R(pd) on the Serial Output Line (Pins 61 and 62) | 6 |

| 4 | Su  | mmary                                                                     | 6 |

## 1 TLK2201/TLK1201 New Feature Description

#### 1.1 Serial Pins

The TNETE2201B and its pin-compatible devices use standard PECL drivers and receivers for the high-speed differential serial connections to copper and fiber media. A standard PECL driver requires a pull-down resistor of 150 to 200 ohms to ground. The TLK2201/TLK1201 driver differential pair, TxP and TxN (pin 62 and 61) are designed in such a way as to not require any external pull-down resistors. Therefore, you can simply de-install the external resistor when using the TLK2201/TLK1201.

#### 1.2 JTAG

In transitioning from theTNETE2201B to the TLK2201/TLK1201, pins that previously were used for transmit and receive PLL filter capacitors are no longer required since all filter components are now integrated. If a board has already been designed for the TNETE2201B, the filter capacitors can be left connected without affecting the functionality of the TLK2201/TLK1201. Support for board level testing via IEEE 11491. (JTAG) was added to the TLK2201/TLK1201 on these pins without compromising the present routing of existing board designs. Per the Pin Comparison Table in section 2.0, the JTAG port is on the following pins: TRSTN on pin 56, TMS on pin 55, TCK on pin 49, TDI on pin 48, and TDO on pin 27.

#### 1.3 DDR (Double Data Rate)

Most gigabit Ethernet transceivers have a ten-bit interface (TBI) when interfacing in each direction to the PCS layer of Ethernet ASICs. This large number of pins is becoming a limiting factor in Ethernet MAC/PCS integration. The TLK2201/TLK1201 has a reduced pin interface mode called Double Data Rate (DDR) that cuts the number of pins required to interface to the MAC/PCS device by 50%. During DDR mode (MODESEL = high), the transmit data sent from the MAC/PCS is latched on the rising and falling edge of REFCLK on TD0-TD4 (pins 2,3,4,6 and 7). The receive data sent to the MAC/PCS is output on both the rising and falling edge of RBC0 on RD0-TD4 (pins 45,44,43,41, and 40). RBC0 and REFCLK are source-centered in both cases.

#### 1.4 PRBS (Pseudo Random Bit Stream) Generation and Verification

The TLK2201/TLK1201 has integrated self-test features to test the part and the full link using its internal PRBS generation and pattern verification feature. Please refer to the data sheet for more details.

#### 1.5 TNETE2201B vs. TLK2201/TLK1201

The TLK2201/TLK1201 has additional features as JTAG, PRBS, and DDR. However, if you use the device in the same set-up as the TNETE2201B, both devices appear electrically and functionally equivalent. The TLK2201/TLK1201 meets the functional specification of the IEEE802.3 GbE standard.

#### 1.6 Status of the TNETE2201B and TLK2201/TLK1201

The TNETE2201B is available in production in a 64-pin VQFP. Orderable part numbers are TNETE2201BPHD and TNETE2201BPJD. The TLK2201 and TLK1201 are available in production in a 64-pin VQFP. The TLK2201 is also available in an 80-ball micro-star BGA package. Orderable part numbers are TLK2201RCP and TLK1201RCP (commercial temperature support, TLK2201IRCP and TLK1201IRCP (industrial temperature support) and TLK2201JRGQE (commercial temperature and BGA package).

### 2 Pin Comparison Table

| Pin          | TNETE2201 | TLK2201/TLK12 | Comment                                                                                                                                                                                                                                                                                                                                                 |  |  |

|--------------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| No.          | В         | 01            |                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 16           | TC1       | PRBSEN        | Transmit capacitor TC1 is not needed on<br>TLK2201/TLK1201; PRBS function can be used here or if<br>pin is left open, a internal pull down will force normal<br>operation                                                                                                                                                                               |  |  |

| 17           | тсо       | TESTEN        | Transmit capacitor TC1 is not needed on<br>TLK2201/TLK1201; just leave pin open (internal pull<br>down) or connect to GND will force normal operation.<br>TESTEN is used during manufacture only for functional<br>verification.                                                                                                                        |  |  |

| 26           | reserved  | LOS           | TLK2201/TLK1201 indicates LOS of signal on this output;<br>Make sure you do not connect this pin to GND if TNETE<br>& TLK will be used on the same board                                                                                                                                                                                                |  |  |

| 27           | LCKREFN   | JTDO          | for normal operation on TNETE this pin is set high;<br>internal pull-up ensures high on TLK2201/TLK1201 for<br>normal operation, if pulled low it is used for JTAG.<br>LCKREFN is not needed in the TLK2201/TLK1201<br>because it uses a single PLL and phase interpolator that<br>locks the PLL to the reference clock when a signal is not<br>present |  |  |

| 47           | SYNCH     | SYNCH/PASS    | in additional to the SYNCH functionality, the TLK output<br>provides the PRBS error flag during PRBS PRBS mode                                                                                                                                                                                                                                          |  |  |

| 48           | RC0       | JTDI          | the external cap is not required for TLK2201/TLK1201<br>(but can be left in the board if wanted), internal pull down<br>forces normal operation, if set to high, pin supports JTAG<br>interface                                                                                                                                                         |  |  |

| 49           | RC1       | TCK           | the external cap is not required for TLK2201/TLK1201<br>(but can be left in the board if wanted), internal pull down<br>forces normal operation, if set to high, pin supports JTAG<br>interface                                                                                                                                                         |  |  |

|              |           |               |                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 18           | Vcc_TX    | VDDPLL        | Analog transmitter power supply on TNETE2201B;<br>TLK2201/TLK1201 PLL supply; this power rail is the most<br>critical supply rail to ensure low noise/ripple                                                                                                                                                                                            |  |  |

| 50           | VCC_RX    | VDD           | VDD_RX is simplified to VDD on TLK2201/TLK1201                                                                                                                                                                                                                                                                                                          |  |  |

| 20,29,<br>63 | Vcc_A     | VDD           | Vcc_A is analog power for TNETE; the<br>TLK2201/TLK1201 treats this as a digital supply                                                                                                                                                                                                                                                                 |  |  |

| 28           | Vcc_A     | ENABLE        | TNETE analog power supply; on TLK if connected to                                                                                                                                                                                                                                                                                                       |  |  |

|       |         |         | power, the chip is enabled (normal operation)                                                                                                                                                                                                                         |

|-------|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55    | VCC_A   | JTMS    | TLK provides internal pull-up for normal operation (or can be connected to Vdd); set low for JTAG                                                                                                                                                                     |

|       |         |         |                                                                                                                                                                                                                                                                       |

| 15    | GND_TX  | MODESEL | MODESEL enables DDR (double data rate; If the pin is<br>shorted to GND or left open, the 10 bit standard interface<br>is used                                                                                                                                         |

| 51    | GND_RX  | GNDA    | GND_RX is simplified to GND on TLK2201/TLK1201                                                                                                                                                                                                                        |

| 21    | GND_A   | GND     | GND is simplified on TLK2201/TLK1201                                                                                                                                                                                                                                  |

| 32    | GND_A   | RBCMODE | if TLK pin is left open (internal pull-down) or connected to<br>GND, it forces RBC0 and RBC1 to output 1/20 baud rate<br>"ping pong' clocks compatible with the TNETE2201B;<br>else, if set high, a full baud rate clock is output on RBC0<br>and RBC1 is pulled low. |

| 56    | GND_A   | JTRSTN  | Pin is analog GND for the TNETE2201B; Pin is JTAG<br>reset for the TLK2201/TLK1201 with pull up. If pin is<br>grounded for the TLK2201/TLK1201, then JTAG is held<br>in reset.                                                                                        |

| 58    | GNDCMOS | GNDA    | Since most people use one GND plane for all different<br>GND supplies, GNDA is expected to connect directly to<br>the GND plane on the TLK2201/TLK1201 (use a common<br>GND plane)                                                                                    |

| 33,46 | GND_TTL | GND     | GND_TTL is simplified to GND on TLK2201/TLK1201                                                                                                                                                                                                                       |

| 37,42 | Vcc_TTL | VDD     | VDD_TTL is simplified to VDD on TLK2201/TLK1201                                                                                                                                                                                                                       |

# 3 Designing a TNETE2201B Board that can also House a TLK2201/TLK1201

Three adjustments need to be made in order to use the TLK2201/TLK1201 on an existing TNETE2201B design. For those needing a second source but do not want to loose the advantages of the TLK2201/TLK1201 over the TNETE2201B, this section explains how to design one common board that allows housing of either device. Please note that you will not be able to use any of the advanced features that the TLK2201/TLK1201 offers such as PRBS or JTAG.

#### 3.1 Power Supply Adjustment

The major difference between the TNETE2201B and the TLK2201/TLK1201 is the power supply of 3.3 V versus 2.5 V. The shape of the power planes itself can be kept identical for both devices (use of the same boards). We suggest in both cases a split Vcc plane and a common GND plane. The only user intervention is to select the appropriate voltage level for the supply. This could be done in several ways.

- If a 5-V supply is on the board and all power planes are feed from that supply, the simplest way would be to use a LDO (low dropout voltage regulator) or a switched power supply. Based on the transceiver in use, install the pin compatible 5V-to-3.3V converter or the 5 Vto-2.5 V converter.

- 2. If a 3.3-V supply plane is already on board, you may add a LDO or switched power supply when using the TLK2201/TLK1201 to provide the necessary 2.5 V. A simple two-pin jumper could be used to choose between one or the other solution. Please see following figure:

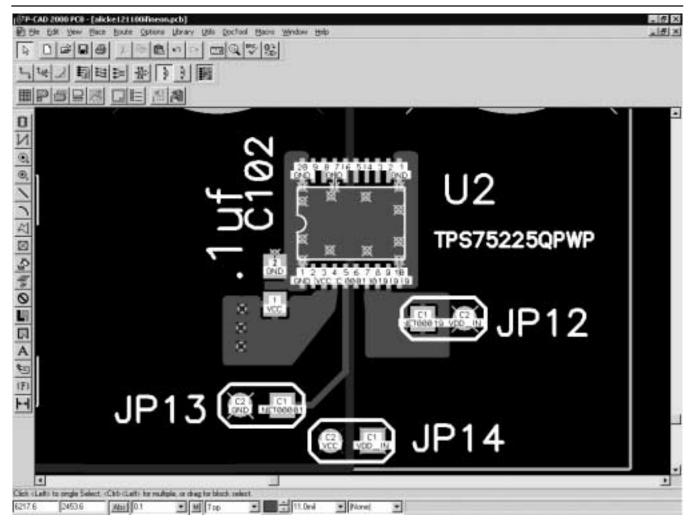

Figure 1: Power Supply Design Example

In the previous figure you find the LDO (**TPS75225QPWP**) that regulates power down to 2.5 V. The current drive of this part is up to 2 A, which is an overkill for the described application and might be replaced by a more cost effective LDO. The left board area (red) is basically the 2.5-V plane. The right board area (blue) is the 3.3-V supply plane. Jumper **JP14** connects both planes directly together when using the TNETE2201B. Another option would be to use a 0 Ohm resistor instead of JP14. **JP13** is the enable/disable pin for the TPS75225. This input is not required and therefore could be left open, which enables the TPS all the time. The **JP12** is allowed to cut off the 3.3-V power supply to the LDO which is an option. However, the TPS supply pins 7,8 and 9 could also connect straight to the 3.3-V power plane.

The only user intervention required when assembling boards would be to install JP14 and not install the TPS when using the TNETE2201B or install the TPS75225 but leave JP14 open.

#### 3.2 Installing the PLL Filter Capacitors at Pins 48, 49, 16 and 17

**TNETE2201B:** When using the TNETE2201B or similar devices, the PLL filter capacitors between pins 48 and 49 as well as the capacitor between pins 16 and 17 needs to be installed.

**TLK2201/TLK1201:** You can leave the capacitors connected without affecting the functionality of the TLK2201/TLK1201. For cost savings, you can also de-install the two capacitors.

#### 3.3 Installing the Resistors R(pd) on the Serial Output Line (Pins 61 and 62)

**TNETE2201B:** When using the TNETE2201B or similar devices, the 150 to 200 Ohm resistors on the differential output pins DOUT\_TXP and DOUT\_TXN have to be installed.

**TLK2201/TLK1201:** De-install this resistor since the TLK2201/TLK1201 has an output driver that does not need external current bias.

#### 4 Summary

It has been shown that is possible to design a PCB supporting both the TNETE2201B and the TLK2201/TLK1201. There is no major design issue involved and no trade-off performance wise. If one were planning to use the additional features that the TLK2201/TLK1201 can provide, the design would need further adjustments. This however is out of the scope of this report. For any new design, TI recommends using the TLK2201 or TLK1201 since they enable the lowest power and most cost effective solution.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated