# TUSB8040A Design Guide

Julie Nirchi Analog Motor Drives

### 1 Part Placement

- If possible, place all active components on the top layer of the board stack up.

- Place the crystal as close as possible to the TUSB8040A and on the top layer of the board stack up to avoid the use of any vias in the clock trace.

- Place the voltage regulators as far away as possible from the TUSB8040A, the crystal, and the differential pairs.

- Place the TUSB8040A apart from the USB connectors (if possible).

- Place the SuperSpeed transmit differential pair capacitors as close as possible to the USB connector pins. The ESD protection device (if used) should also be placed as close as possible to the USB connectors.

- In general, the bulk capacitors associated with each power rail should be placed as close as possible

to the voltage regulators.

## 2 Board Layout Considerations

### 2.1 RKM Package – QFN (Quad Flat No-Lead)

- The RKM package has 0.6 mm (~24 mil) pin pitch. The TUSB8040A EVM is routed on 4 layers: signal, power, ground, and signal. This 4 layer board still meets requirements of 0.062 thickness ±.010.

- The TUSB8040A has a thermal pad of 5.5 x 5.5 ±0.1 mm that must be connected to ground through a system of vias.

- All vias under the device should be solder masked to avoid any potential issues with thermal pad layouts.

## 2.2 Impedance

The differential pair traces for each USB port (USB\_DP\_XX/USB\_DM\_XX, USB\_SSTXP\_XX/USB\_SSTXM\_XX, USB\_SSRXP\_XX/USB\_SSRXM\_XX) must be designed with a characteristic impedance of 90  $\Omega$  ±10% between the complementary signals (i.e. + and -). The width and spacing of the differential pair traces can be modified to achieve the characteristic impedance of 90  $\Omega$  and may differ depending on the PCB stack up and materials used. The differential traces on the TUSB8040A EVM are 4.1 mils wide with 7.4 mil spacing from a pin pad that is approximately 9.5 mils wide.

The remaining traces should be as close as possible to  $50-\Omega$  characteristic impedance. To meet this impedance requirement the traces on the EVM are 6.0 mils wide. Due to constraints from routing the differential pairs, board stack up and board thickness requirements, the board fabricator may not be able to get to precisely exactly 50 ohms, in those cases maintaining impedances within  $\pm 20\%$  of  $50~\Omega$  is acceptable.

### 2.3 Critical Signals

- · Differential pair signals

- External crystal signals

- Power and ground signals (particularly VBUS and Earth GND)

Important rules for the routing of these critical signals are:

- Run all critical signals on a signal plane adjacent to a solid ground plane layer if possible.

- Never cross power and ground plane boundaries with critical signals, particularly at a 90 degree angle.

- Avoid 90 degree turns in traces, use 45 degree turns or use bevels instead.

- Keep digital signals away from the differential pairs and the crystal circuitry.

- See following sections for more information on the routing of critical signals.

### 2.4 Crystal

The XI terminal of the TUSB8040A requires a crystal input or an external clock source to the 1.8-V input. Since a 24-MHz crystal is used on the TUSB8040A EVM, the other side of the crystal is attached to the XO terminal and the ground connections of the load capacitors are attached to VSS\_OSC.

Care should be taken in the layout of the crystal to reduce noise and jitter. The crystal should be located as close as physically possible to the TUSB8040A XI and XO terminals. This connection should be short and direct.

### 2.5 USB Interface

The USB ports of the TUSB8040A are attached to USB 3.0 connectors. These port connectors allow the hub to communicate to downstream USB 3.0 devices in SuperSpeed or downstream USB 2.0 devices in High-speed or Full-speed or Low-speed. The upstream connection allows simultaneous SuperSpeed and High-speed connections. The connection speed determination is done automatically by the TUSB8040A.

### 2.6 Differential Pair Signals

Notes on routing differential pair signals:

- Minimize the trace lengths of the differential pair traces. The maximum recommended trace length for SS differential pair signals and USB 2.0 differential pair signals is eight inches. Longer trace lengths require very careful routing to assure proper signal integrity.

- Match the etch lengths of the differential pair traces (i.e. DP and DM or SSRXP and SSRXM or SSTXP and SSTXM). There should be less than 5 mils difference between a SS differential pair signal and its complement. The USB 2.0 differential pairs should not exceed 50 mils relative trace length difference.

- Route the differential pair traces parallel to one another and close together as much as possible. The traces should be symmetrical.

- The etch lengths of the differential pair groups do not need to match (i.e. the length of the SSRX pair to that of the SSTX pair), but all trace lengths should be minimized.

**NOTE:** To minimize crosstalk, it is recommended that the spacing between the TX and RX signal pairs for each interface be five times the width of the trace (5W rule). For instance, on the TUSB8040A EVM there are 27.5 mils of space between the TX and RX differential pairs.

If this 5W rule cannot be implemented, then the space between the TX and RX differential pairs should be maximized as much as possible and ground-fill should be placed between the two. In this case, it is better to route each differential pair on opposite sides of the board with a ground plane between them.

- There should be a general keep out region of at least 20 mils around the differential pairs so that signals, components or power/ground planes are not routed close to the differential pairs. The exception is at the TUSB8040A.

- Minimize the use of vias in the differential pair paths as much as possible. If this is not practical, make sure that the same via type and placement are used for both signals in a pair. Any vias used should be placed as close to the TUSB8040A as possible.

- Do not place power fuses across the differential pair traces.

- It is preferable to route the differential pair signals directly from the port to the via under the TUSB8040A. On the TUSB8040A EVM, the differential pair signals "fly-by" the ESD protection devices so that no stubs are created. Depending on board layout, this may not always be possible.

- The differential pairs should be routed over a solid ground plane. This ground plane should run under

the entire trace length from the TUSB8040A (or via) to the pins of the USB connectors and extend past the traces by 10 mils. Avoid routing differential pairs at 90 degrees angles over power plane edges.

- To ease routing, the polarity of the SS differential pairs can be swapped. This means that SSTXP can be routed to SSTXM or SSRXM can be routed to SSRXP.

- In order to route the differential pairs of the TUSB8040A to the USB connectors, it is necessary on the downstream ports to cross the SSTX pair and the SSRX pair. To avoid using multiple sets of vias, the vias were carefully placed on the TUSB8040A EVM so that the crossover was inherent in the board design and then both pairs of signals (along with the USB 2.0 differential pair) were routed on the bottom layer.

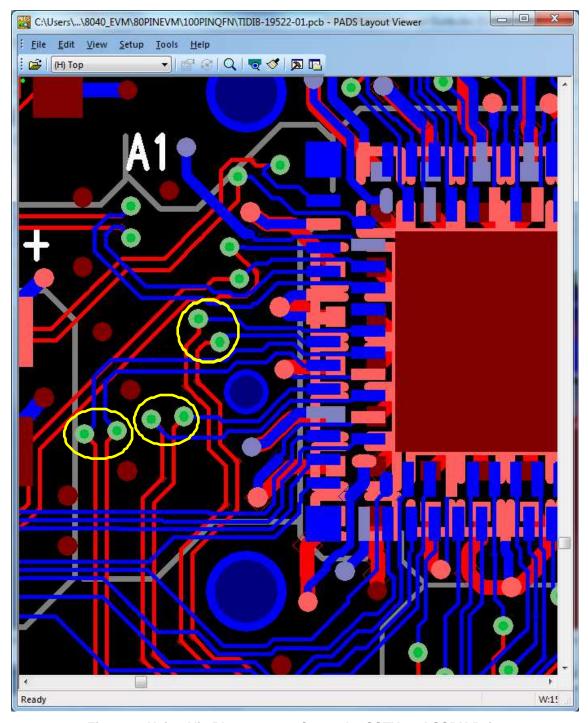

Figure 1. Using Via Placement to Cross the SSTX and SSRX Pairs

### 2.6.1 Internal Bond Wire Mismatch

The routing of the SS differential pairs must take into account the internal bond wire mismatch inherent in the dual row RKM package. Internal wire lengths (in mil) are below.

**Table 1. Internal Bond Wire Mismatch**

| USB_SSTXM_UP USB_SSTXP_UP USB_SSRXM_UP | A42<br>B39<br>B40 | 125<br>97 | 28 |  |

|----------------------------------------|-------------------|-----------|----|--|

|                                        |                   | 97        |    |  |

| USB_SSRXM_UP                           | B40               |           |    |  |

|                                        |                   | 89        | 20 |  |

| USB_SSRXP_UP                           | A44               | 109       |    |  |

| USB_DM_UP                              | B42               | 81        | 22 |  |

| USB_DP_UP                              | A46               | 103       |    |  |

| USB_DP_DN0                             | B1                | 102       | 34 |  |

| USB_DM_DN0                             | A1                | 136       |    |  |

| USB_SSRXP_DN0                          | В3                | 80        | 32 |  |

| USB_SSRXM_DN0                          | A3                | 112       |    |  |

| USB_SSTXP_DN0                          | B4                | 72        | 30 |  |

| USB_SSTXM_DN0                          | A4                | 102       |    |  |

| USB_SSRXP_DN2                          | B6                | 59        | 22 |  |

| USB_SSRXM_DN2                          | A7                | 81        |    |  |

| USB_SSTXP_DN2                          | В7                | 58        | 23 |  |

| USB_SSTXM_DN2                          | A8                | 81        |    |  |

| USB_DP_DN2                             | A9                | 82        | 20 |  |

| USB_DM_DN2                             | B9                | 62        |    |  |

| USB_DM_DN3                             | A31               | 87        | 26 |  |

| USB_DP_DN3                             | B29               | 61        |    |  |

| USB_SSRXP_DN3                          | B30               | 59        | 22 |  |

| USB_SSRXM_DN3                          | A33               | 81        |    |  |

| USB_SSTXP_DN3                          | B31               | 58        | 23 |  |

| USB_SSTXM_DN3                          | A34               | 81        |    |  |

| USB_SSRXP_DN1                          | B33               | 66        | 27 |  |

| USB_SSRXM_DN1                          | A36               | 93        |    |  |

| USB_SSTXP_DN1                          | B34               | 74        | 27 |  |

| USB_SSTXM_DN1                          | A37               | 101       |    |  |

| USB_DM_DN1                             | A39               | 126       | 34 |  |

| USB_DP_DN1                             | B36               | 92        |    |  |

### 2.7 Port Connectors

Most TUSB8040A customers will be using thru-hole USB 3.0 standard connectors with mounting pegs that are soldered into the board for more rigid connections. The thru-hole connectors allow differential pairs to be routed on the bottom layer of the EVM without requiring any vias to the top layer at the connector. Routing on the bottom layer of the EVM to the thru-hole connector can reduce the stub length caused by the thru hole pins.

The outside shield of the connector should be tied to chassis ground to provide a low impedance path to the chassis ground for ESD current. If galvanic isolation is required, the outside shield should be isolated from digital ground with a parallel combination of a 1-M $\Omega$  resistor and capacitors of 0.1  $\mu$ F and 0.001  $\mu$ F.

Pins 4 and 7 of the USB 3.0 connector should be connected to digital ground. Both of these pins should be connected directly to the board ground plane as close to the connector as possible.

### 2.8 Reset Terminals

Asserting the TUSB8040A GRSTZ pin low resets the TUSB8040A. The GRSTZ signal should be held low for a minimum of 3 ms from the time that the power supplies reach the minimum required supply voltage (90% of nominal) and the crystal is active to ensure a valid reset. An external delay capacitor of 1 µF along with the internal pull-up resistor can be used to generate the power on reset pulse; the voltage ramp of the implementation will dictate the capacitor value needed. An alternative to this passive reset is to actively drive GRSTZ low using external circuitry for the minimum reset time following power on.

### 2.9 Miscellaneous Terminals

The USB R1 and USBR1 RTN terminals require a precision resistor. A 9.09-k $\Omega$  ±1% resistor should be placed in parallel across these terminals, as close to the device as possible.

While the TUSB8040A EVM can utilize external pull up and pull down resistors on these terminals, there are inherent pull-ups and pull-downs implemented within the TUSB8040A.

NOTE: The internal pull up and pull down resistors of the TUSB8040A have a nominal value of 22 kΩ (150 μA at 3.3 V). If using an external pull up on a terminal that has an internal pull down resistor, TI recommends using a value of 7.5 k $\Omega$  or smaller. Or if using an external pull down on a terminal that has an internal pull-up resistor, TI recommends using a value of 7.5 k $\Omega$  or smaller.

- SMBUSz the I2C interface mode is enabled by default via the internal pull up resistor on this terminal. If a 4.7-k $\Omega$  pull-down is placed on this terminal and sampled at power-on reset, SMBUS mode is

- SDA SMBDAT and SCL SMBCLK serial EEPROM or SMBUS interface. On the EVM, these pins are routed to a serial EEPROM socket with 1-k $\Omega$  pull-up resistors installed on both signals. If the TUSB8040A is being used in SMBUS mode, then these signals become the data and clock signal respectively. The TUSB8040A has internal pull downs on these terminals. The SDA SMBDAT terminal is sampled at the deassertion of reset to determine if SuperSpeed low power states U1 and U2 are disabled. If SDA SMBDAT is high, U1 and U2 low power states are disabled. If SDA SMBDAT is low, U1 and U2 low power states are enabled. Disabling U1 and U2 allows the TUSB8040A to work with USB 3.0 devices that do not implement low power states per the USB 3.0 specification. If the EEPROM or SMBUS is implemented, the value of the u1u2Disable bit in the Device Configuration Register determines if the low power states U1 and U2 are disabled. The SCL SMBCLK terminal is sampled at the deassertion of reset to determine if SuperSpeed low power state (U1 and U2) initiation is disabled. If SCL\_SMBCLK is high, U1 and U2 low power state initiation is disabled. If SCL\_SMBCLK is low, U1 and U2 low power states are completely enabled. Disabling U1 and U2 initiation allows the TUSB8040ARKM to accept requests to enter low power states from the host or downstream devices, but it will not initiate the transitions. If the EEPROM or SMBUS is implemented, the value of the u1u2TimerOvr bit in the Device Configuration Register determines if the low power state initiation is disabled.

- HS\_SUSPEND\_POLARITY downstream port power switch enable polarity is set to active high if a pull up is placed on this terminal and sampled at power-on reset. The TUSB8040A has an internal pull down on this terminal to set the power enables to active low by default. Since this terminal also acts as a LED output, a pull-up value of 330  $\Omega$  is recommended if a LED wit series resistance of 1 k $\Omega$  is used for the status LED circuit.

- SS\_SUSPEND\_SSC spread spectrum clocking is disabled if a pull up is placed on this terminal and sampled at power-on reset. The TUSB8040A has an internal pull down on this terminal to enable SSC by default. Since this terminal also acts as a LED output, a pull up value of 330 ohm is recommended if a LED with series resistance of 1K is used for the status LED circuit.

### 2.10 Power Control and Battery Charging Terminals

- **FULLPWRMGMTZ\_SMBA1** full power management is enabled and reported in the USB descriptors when a 4.7-kΩ pull-down is placed on this terminal and sampled at power-on reset. The TUSB8040A has an internal pull up on this terminal, the TUSB8040A defaults to a non full power management state which is the lower cost implementation where no downstream port power control is implemented. This pin also acts as the interface for the SMBA1 signal when a SMBus host is connected to the TUSB8040A.

- **GANGED\_SMBA2** individual port power management is enabled and reported in the USB descriptors when a 4.7-kΩ pull-down is placed on this terminal and sampled at power-on reset. The TUSB8040A has an internal pull up on this terminal. The TUSB8040A defaults to a ganged power management state which is a lower cost implementation. This pin also acts as the interface for the SMBA2 signal when a SMBus host is connected to the TUSB8040A.

- **PWRON0Z\_BATEN0** battery charging on downstream port 0 is disabled by default via the internal pull down resistor on this terminal. If a 4.7-kΩ pull-up is placed on this terminal and sampled at power on reset, battery charging on the downstream port 0 is enabled. After reset, this signal acts at the active low power enable/disable for the downstream port power switch for port 0.

- OVERCUR0Z an over-current event on port 0 is reported to the TUSB8040A by the downstream port

power controller circuitry using this terminal. The TUSB8040A has an internal pull up on this terminal to

avoid any unexpected over-current reporting, but an external pull up resistor is recommended for noisy

applications.

- **PWRON1Z\_BATEN1** battery charging on downstream port 1 is disabled by default via the internal pull down resistor on this terminal. If a 4.7-kΩ pull-up is placed on this terminal and sampled at power on reset, battery charging on the downstream port 1 is enabled. After reset, this signal acts at the active low power enable/disable for the downstream port power switch for port 1.

- OVERCUR1Z an over-current event on port 1 is reported to the TUSB8040A by the downstream port

power controller circuitry using this terminal. The TUSB8040A has an internal pull up on this terminal to

avoid any unexpected over-current reporting, but an external pull up resistor is recommended for noisy

applications.

- **PWRON2Z\_BATEN2** battery charging on downstream port 2 is disabled by default via the internal pull down resistor on this terminal. If a 4.7-kΩ pull-up is placed on this terminal and sampled at power on reset, battery charging on the downstream port 2 is enabled. After reset, this signal acts at the active low power enable/disable for the downstream port power switch for port 2.

- OVERCUR2Z an over-current event on port 2 is reported to the TUSB8040A by the downstream port

power controller circuitry using this terminal. The TUSB8040A has an internal pull up on this terminal to

avoid any unexpected over-current reporting, but an external pull up resistor is recommended for noisy

applications.

- **PWRON3Z\_BATEN3** battery charging on downstream port 3 is disabled by default via the internal pull down resistor on this terminal. If a 4.7-kΩ pull-up is placed on this terminal and sampled at power on reset, battery charging on the downstream port 3 is enabled. After reset, this signal acts at the active low power enable/disable for the downstream port power switch for port 3.

- OVERCUR3Z an over-current event on port 3 is reported to the TUSB8040A by the downstream port

power controller circuitry using this terminal. The TUSB8040A has an internal pull up on this terminal to

avoid any unexpected over-current reporting, but an external pull up resistor is recommended for noisy

applications.

### 2.11 USB 2.0 Port Indicator LED Terminals

Table 2. Port State to Port Indicator Color Mapping

|                    | DOWNSTREAM FACING HUB PORT STATE |                                                            |                                  |                                    |  |

|--------------------|----------------------------------|------------------------------------------------------------|----------------------------------|------------------------------------|--|

| POWER<br>SWITCHING | POWERED-OFF                      | DISCONNECTED, DISABLED, NOT CONFIGURED, RESETTING, TESTING | ENABLED,<br>TRANSMIT,<br>RECEIVE | SUSPENDED,<br>RESUMING,<br>RESTART |  |

| WITH               | Off or amber if over-current     | Off                                                        | Green                            | Off                                |  |

| WITHOUT            | Off                              | Off or amber if over-current                               | Green                            | Off                                |  |

- **PORTINDZ\_SMBA3** individual USB 2.0 port indicator LEDs are enabled and reported in the USB descriptors when a 4.7-kΩ pull-down is placed on this terminal and sampled at power-on reset. The TUSB8040A has an internal pull up on this terminal. The TUSB8040A defaults to the lower cost implementation without the port LEDs. This pin also acts as the interface for the SMBA3 signal when a SMBus host is connected to the TUSB8040A.

- **LEDA0Z\_RMBL0** removable device mode on port 0 is enabled by default via the internal pull up resistor on this terminal. If a 4.7-kΩ pull-down is placed on this terminal and sampled at power on reset, port 0 will be reported in the USB descriptors as a non-removable port with a permanently attached device. After reset, this signal acts as the active low USB 2.0 port indicator status amber LED for port 0.

- LEDG0Z\_USED0 port 0 is enabled by default via the internal pull up resistor on this terminal. If a

4.7-kΩ pull-down is placed on this terminal and sampled at power on reset, port 0 will not be an active

port. After reset, this signal acts as the active low USB 2.0 port indicator status green LED for port 0.

- **LEDA1Z\_RMBL1** removable device mode on port 1 is enabled by default via the internal pull up resistor on this terminal. If a 4.7-kΩ pull-down is placed on this terminal and sampled at power on reset, port 1 will be reported in the USB descriptors as a non-removable port with a permanently attached device. After reset, this signal acts as the active low USB 2.0 port indicator status amber LED for port 1.

- LEDG1Z\_USED1 port 1 is enabled by default via the internal pull up resistor on this terminal. If a

4.7-kΩ pull-down is placed on this terminal and sampled at power on reset, port 1 will not be an active

port. After reset, this signal acts as the active low USB 2.0 port indicator status green LED for port 1.

- **LEDA2Z\_RMBL2** removable device mode on port 2 is enabled by default via the internal pull up resistor on this terminal. If a 4.7-kΩ pull-down is placed on this terminal and sampled at power on reset, port 2 will be reported in the USB descriptors as a non-removable port with a permanently attached device. After reset, this signal acts as the active low USB 2.0 port indicator status amber LED for port 2.

- LEDG2Z\_USED2 port 2 is enabled by default via the internal pull up resistor on this terminal. If a

4.7-kΩ pull-down is placed on this terminal and sampled at power on reset, port 2 will not be an active

port. After reset, this signal acts as the active low USB 2.0 port indicator status green LED for port 2.

- **LEDA3Z\_RMBL3** removable device mode on port 3 is enabled by default via the internal pull up resistor on this terminal. If a 4.7-kΩ pull-down is placed on this terminal and sampled at power on reset, port 3 will be reported in the USB descriptors as a non-removable port with a permanently attached device. After reset, this signal acts as the active low USB 2.0 port indicator status amber LED for port 3.

- LEDG3Z\_USED3 port 3 is enabled by default via the internal pull up resistor on this terminal. If a

4.7-kΩ pull-down is placed on this terminal and sampled at power on reset, port 3 will not be an active

port. After reset, this signal acts as the active low USB 2.0 port indicator status green LED for port 3.

Power www.ti.com

### 3 Power

### 3.1 Power

VDD11 and VDDA11 should be implemented as a single power plane, as should VDD33, VDDA33 and VDDA33 OSC.

- The VDD11 terminals supply 1.1-V power to the core of the TUSB8040A. This power rail can be isolated from all other power rails by a ferrite bead to reduce noise.

- The DC resistance of the ferrite bead on the 1.1-V power rail can affect the voltage provided to the device due to the high current draw on the power rail. The output of the 1.1-V votlage regulator may need to be adjusted to account for this or a ferrite bead with low DC resistance (less than 0.05  $\Omega$ ) can be selected.

- The VDD33 terminals supply 3.3-V power to the I/O of the TUSB8040A. This power rail can be isolated from all other power rails by a ferrite bead to reduce noise.

- All power rails require a 10-μF capacitor or 1-μF capacitors for stability and noise immunity. These bulk capacitors can be placed anywhere on the power rail. The smaller decoupling capacitors should be placed as close to the TUSB8040A power pins as possible with an optimal grouping of two of differing values per pin.

### 3.2 Downstream Port Power

- The downstream port power, VBUS, must be supplied by a source capable of supplying 5 V and up to 900 mA per port. Downstream port power switches can be controlled by the TUSB8040A signals. It is also possible to leave the downstream port power always enabled.

- A large bulk low-ESR capacitor of 22 μF or larger is required on each downstream port's VBUS to limit in-rush current.

- The ferrite beads on the VBUS pins of the downstream USB port connections are recommended for both ESD and EMI reasons. A 0.1-µF capacitor on the USB connector side of the ferrite provides a low impedance path to ground for fast rise time ESD current that might have coupled onto the VBUS trace from the cable.

### 3.3 Ground

It is recommended that only one board ground plane be used in the design. This provides the best image plane for signal traces running above the plane. The thermal pad of the TUSB8040A and any of the voltage regulators should be connected to this plane with vias. An earth or chassis ground is implemented only near the USB port connectors on a different plane for EMI and ESD purposes.

www.ti.com

# **Appendix A Schematics**

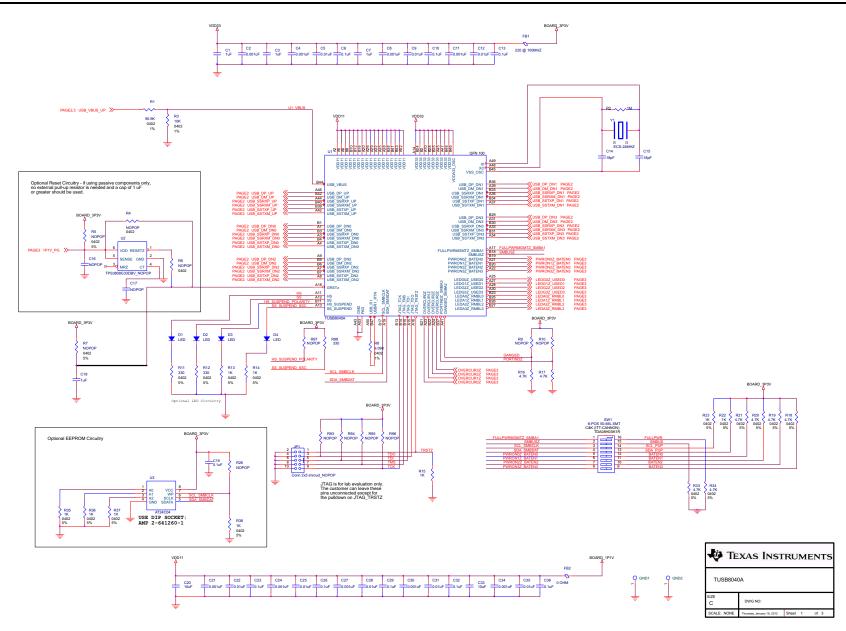

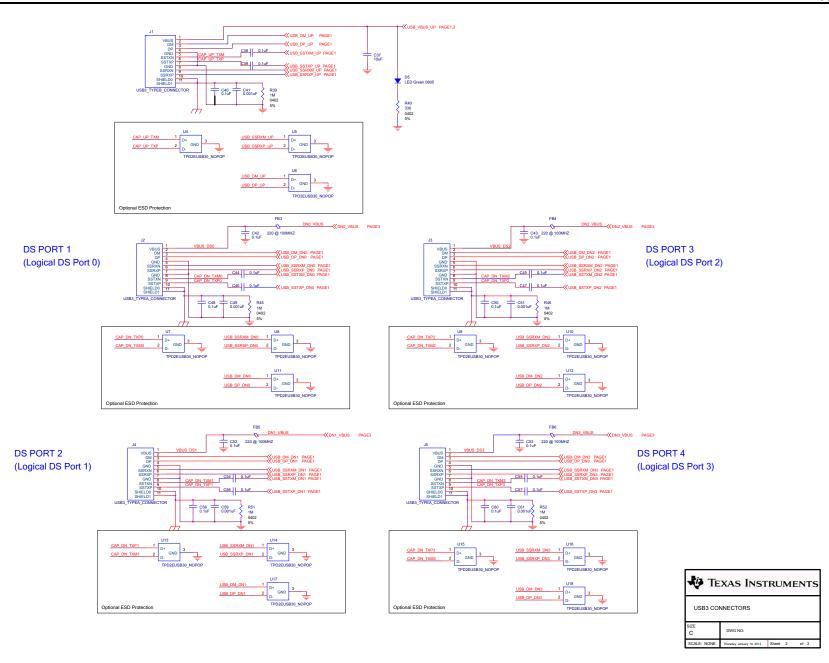

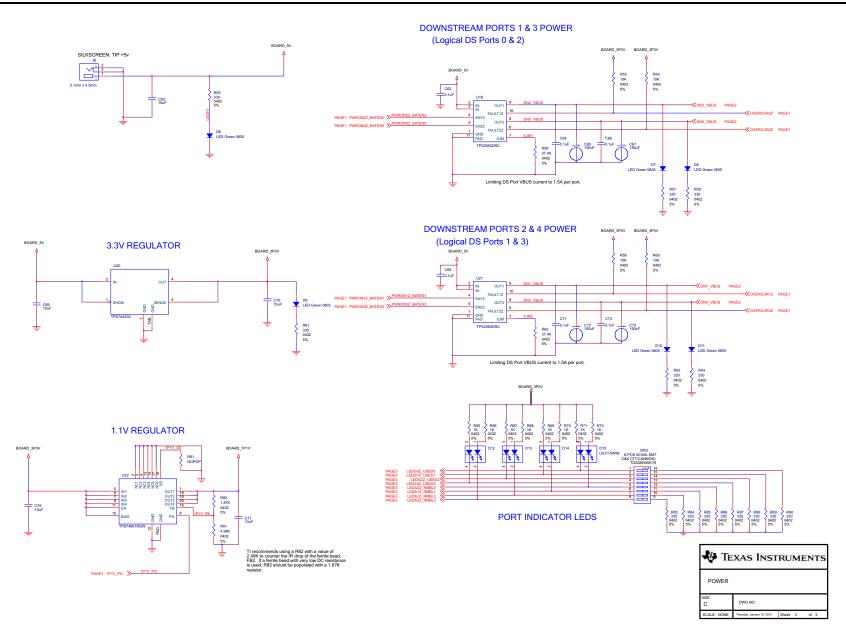

The following pages contain schematics for the TUSB8040A.

Appendix A www.ti.com

Appendix A www.ti.com

Appendix A www.ti.com

www.ti.com

# Appendix B TUSB8040AEVM Bill of Materials

The following pages contain the BOM for TUSB8040AEVM.

Appendix B www.ti.com

## Table 3. TUSB8040AEVM BOM

| Item | Quantity | Reference                                                                                                             | Part                        | Manufacturer       | Part Number                   | Package       |

|------|----------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|-------------------------------|---------------|

| 1    | 4        | C1,C3,C7,C18                                                                                                          | 1uF                         | TDK                | C2012X7R1A105K                | 805           |

| 2    | 14       | C2, C4, C8, C11, C21, C24, C27, C30, C34,C41, C49, C51, C59, C61                                                      | 0.001uF                     | TDK                | C1005X7R1H102K                | 402           |

| 3    | 8        | C5, C9, C12, C22, C25, C28, C31,<br>C35                                                                               | 0.01uF                      | AVX                | 0402YC103KAT2A                | 402           |

| 4    | 24       | C6, C10, C13, C19, C23, C26, C29, C32, C36, C40, C42, C43, C48, C50, C52, C53, C58, C60, C62, C64, C66, C68, C71, C73 | 0.1uF                       | Yageo              | CC0402KRX5R6BB104             | 402           |

| 5    | 10       | C38, C39, C44, C45, C46, C47, C54,<br>C55, C56, C57                                                                   | 0.1uF                       | TDK                | CC0402KRX5R6BB104             | 201           |

| 6    | 2        | C14, C15                                                                                                              | 18pF                        | AVX                | 04025A180JAT2A                | 402           |

| 7    | 8        | C20, C33, C37, C63, C69, C70, C76, C77                                                                                | 10uF                        | Murata Electronics | GRM31CR61C106KC31L            | 1206          |

| 8    | 4        | C65, C67, C72, C75                                                                                                    | 150uF                       | Kemet              | B45197A2157K409<br>(Tantalum) | 7343          |

| 9    | 14       | R4, R5, R6, R9, R10, C16, C17, R26,<br>R81, R93, R94, R95, R96, R97                                                   | NO POP                      |                    |                               | 402           |

| 10   | 11       | D1, D2, D3, D4, D5, D6, D7, D8, D9, D10, D11                                                                          | LED Green 0805              | Lite On            | LTST-C171GKT                  | 805           |

| 11   | 5        | FB1, FB3, FB4, FB5, FB6                                                                                               | 220 @ 100MHZ Ferrite Bead   | Murata Electronics | BLM18PG221SN1D                | 603           |

| 12   | 2        | SW1, SW2                                                                                                              | 8-POS 50-MIL SMT            | C&K Components     | SD08H0SBR                     |               |

| 13   | 1        | J1                                                                                                                    | USB3_TYPEB_CONNECTOR        | FoxConn            | UEB1112C-2AK1-4H              | 9_RA_TH_B     |

| 14   | 4        | J2, J3, J4, J5                                                                                                        | USB3_TYPEA_CONNECTOR        | FoxConn            | UEA1112C-4HK1-4H              | 9_RA_TH_A     |

| 15   | 1        | J6                                                                                                                    | 2.1mm x 5.5mm DC Power Jack | CUI Inc.           | PJ-202AH (PJ-002AH)           | 2.1mm x 5.5mm |

| 16   | 6        | R2, R39, R45, R46, R51, R52                                                                                           | 1M                          | Rohm Semiconductor | MCR01MZPJ105                  | 402           |

| 17   | 1        | R1                                                                                                                    | 90.9K 1%                    | Rohm Semiconductor | MCR01MZPF9092                 | 402           |

| 18   | 5        | R7, R53, R54, R59, R60                                                                                                | 10K                         | Rohm Semiconductor | MCR01MZPJ103                  | 402           |

| 19   | 1        | R3                                                                                                                    | 10K 1%                      | Rohm Semiconductor | MCR01MZPF1002                 | 402           |

| 20   | 8        | R16, R17, R18, R19, R20, R21, R33,<br>R34                                                                             | 4.7K                        | Rohm Semiconductor | MCR01MZPJ472                  | 402           |

| 21   | 17       | R15, R22, R23, R35, R36, R37, R38,<br>R65, R66, R67, R68, R69, R70, R71,<br>R72, R13, R14                             | 4.7K                        | Rohm Semiconductor | MCR01MZPJ102                  | 402           |

| 22   | 1        | R6                                                                                                                    | 0                           | Rohm Semiconductor | MCR01MZPJ000                  | 402           |

| 23   | 18       | R11, R12, R40, R55, R98, R57, R58,<br>R61, R63, R64, R83, R84, R85, R86,<br>R87, R88, R89, R90                        | 330                         | Rohm Semiconductor | MCR01MZPJ331                  | 402           |

| 24   | 2        | R56, R62                                                                                                              | 37.4K                       | Vishay / Dale      | CRCW040237K4FKED              | 402           |

| 25   | 1        | R82                                                                                                                   | 1.87K                       | Vishay / Dale      | CRCW04021K87FKED              | 402           |

| 26   | 1        | R91                                                                                                                   | 1.87K                       | Vishay / Dale      | CRCW04024K99FKED              | 402           |

| 27   | 1        | U1                                                                                                                    | TUSB8040A - USB 3.0 Hub     | Texas Instruments  | TUSB8040A                     | 100QFN        |

www.ti.com Appendix B

# Table 3. TUSB8040AEVM BOM (continued)

| Item | Quantity | Reference                                                           | Part                                 | Manufacturer      | Part Number                       | Package             |

|------|----------|---------------------------------------------------------------------|--------------------------------------|-------------------|-----------------------------------|---------------------|

| 28   | 1        | U2                                                                  | TPS3808G33DBV - Voltage Supervisor   | Texas Instruments | TPS3808G33DBV                     | 6DBV                |

| 29   | 1        | U3                                                                  | AT24C04 / SOCKET - I2C EEPROM        | Atmel / Tyco      | AT24C04A-10PU-1.8 /<br>2-641260-1 | 8DIP / 8SOIC SOCKET |

| 30   | 15       | U4, U5, U6, U7, U8, U9, U10, U11, U12, U13, U14, U15, U16, U17, U18 | TPD2EUSB30 - USB ESD Protection      | Texas Instruments | TPD2EUSB30                        | 3DRT                |

| 31   | 2        | U19, U21                                                            | TPS2560DRC - USB Power Switch        | Texas Instruments | TPS2560DRC                        | 10SON               |

| 32   | 1        | U20                                                                 | TPS7A4533 - 3.3V Voltage Regulator   | Texas Instruments | TPS7A4533KTT                      | DDPAK-5             |

| 33   | 1        | U22                                                                 | TPS74801RGW - 1.1V Voltage Regulator | Texas Instruments | TPS74801RGW                       | 20VQFN              |

| 34   | 1        | Y1                                                                  | ECS-24MHZ Crystal                    | ECS               | ECX-53B<br>(ECS-240-20-30B-TR)    | 5.0mm x 3.2mm       |

| 35   | 4        | D12, D13, D14, D15                                                  | Green Amber LED                      | Panasonic         | LNJ115W88                         | 603                 |

| 36   | 1        | JP1                                                                 | Conn 2x5 shroud                      | 3M                | LNJ115W88                         | HDR5X2 M 0.1" TH    |

| 37   | 1        | R8                                                                  | 9.09K 1%                             | Panasonic - ECG   | ERJ-2RKF9091X                     | 402                 |

| 38   | 1        | FB2                                                                 | 0 ohm                                |                   |                                   | 603                 |

| 39   | 1        | NO POP                                                              | NO POP AC Power Adapter              | CUI Inc           | ETSA050360UDC-P5P-SZ              | 2.1mm I.D. x 5.5mm  |

| 40   | 4        |                                                                     | PCB Feet                             | Richco Plastic Co | RBS-12 or RBS-32                  |                     |

### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

| Applications |

|--------------|

**Products** Audio www.ti.com/audio **Amplifiers** amplifier.ti.com **Data Converters** dataconverter.ti.com **DLP® Products** www.dlp.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com

www.ti-rfid.com **OMAP Mobile Processors** www.ti.com/omap

Wireless Connectivity www.ti.com/wirelessconnectivity Automotive and Transportation www.ti.com/automotive www.ti.com/communications Communications and Telecom Computers and Peripherals www.ti.com/computers Consumer Electronics www.ti.com/consumer-apps **Energy and Lighting** www.ti.com/energy Industrial www.ti.com/industrial Medical www.ti.com/medical Security www.ti.com/security

Space, Avionics and Defense www.ti.com/space-avionics-defense Video and Imaging www.ti.com/video

e2e.ti.com

**TI E2E Community**