# Application Note Using MOSFET Transient Thermal Impedance Curves In Your Design

John Wallace

#### ABSTRACT

Power MOSFET data sheets include a normalized transient thermal impedance graph: junction-to-case,  $Z_{\theta JC}$ , or junction-to-ambient,  $Z_{\theta JA}$ . For simplicity, this article uses the terminology " $Z_{\theta JC}$  graph" for either with the understanding that the same principles can be applied to the  $Z_{\theta JA}$  graph. These graphs are used to estimate the junction temperature rise due to single or repetitive power pulses. Alternatively, the  $Z_{\theta JC}$  graph can also be used to estimate the MOSFET peak current capability for single or periodic pulses of current as shown in *Understanding MOSFET Data Sheets, Part 4 - Pulsed Current Ratings*, technical article.

#### **Table of Contents**

| Introduction                                                                  | 2   |

|-------------------------------------------------------------------------------|-----|

| 2 Review the Z <sub>θJC</sub> Graph                                           | . 2 |

| B Using the Z <sub>BJC</sub> Graph to Estimate Junction Temperature Rise      | . 2 |

| Application Example                                                           |     |

| 5 Using the Z <sub>BJC</sub> Graph to Estimate MOSFET Peak Current Capability | .3  |

| Application Example                                                           |     |

| 7 Summary                                                                     | 5   |

| B References                                                                  | 6   |

|                                                                               |     |

## **List of Figures**

| Figure 2-1. CSD17579Q5A Ζ <sub>θJC</sub> Graph             | 2 |

|------------------------------------------------------------|---|

| Figure 4-1. TPS53819A Hiccup Mode Short Circuit Protection |   |

| Figure 6-1. CSD19532Q5B Z <sub>θJC</sub> Graph             |   |

|                                                            |   |

### Trademarks

All trademarks are the property of their respective owners.

## 1 Introduction

Introduction

The  $Z_{\theta,IC}$  graph includes a family of normalized thermal impedance curves at different values of duty cycle versus pulse width. Similar to the method shown in Understanding MOSFET Data Sheets, Part 6 - Thermal *Impedance*, the thermal resistance is measured on a standard 1.5 inches x 1.5 inches, FR4 PCB with the device mounted on a 1 inch<sup>2</sup>, 2 oz. Cu pad. However, instead of measuring thermal resistance with static power dissipation, the power pulse width and duty cycle are varied. The value of thermal resistance at each pulse width and duty cycle are then normalized to the static thermal resistance,  $R_{B,C}$ , specified in the data sheet to generate the curves.

## 2 Review the Z<sub>0JC</sub> Graph

10

Figure 2-1 shows the Z<sub>0JC</sub> graph from TI's CSD17579Q5A data sheet, a 30-V power MOSFET in a 5x6mm SON package. The y-axis is the Normalized Thermal Impedance,  $Z_{\theta,JC}$ , on a log scale and the x-axis is the pulse width, tp, in seconds on a log scale. Each curve represents a duty cycle value starting at 0% (for example, single pulse) at the bottom and ending at 50% duty cycle for the uppermost curve.

#### 50% 10% 2% Single Pulse 30% 5% - 1% Zeuc - Normalized Thermal Impedance Duty Cycle =t1/t2 0.1 Max $R_{BJC}$ = 4.3° C/W $\Delta T_i = P * Z_{\theta JC} * R_{\theta JC}$ 0.0 0.0001 0.01 1E-5 0.001 0.1 tp - Pulse Duration (s)

Figure 2-1. CSD17579Q5A Z<sub>0JC</sub> Graph

## 3 Using the $Z_{\theta JC}$ Graph to Estimate Junction Temperature Rise

Making use of the  $Z_{\theta,IC}$  graph is a relatively straight forward process. The operating conditions including gate drive voltage, V<sub>GS</sub>; drain current (DC or rms), I<sub>D</sub>; pulse width, t<sub>1</sub>; and duty cycle, D must be known. Use V<sub>GS</sub> to determine R<sub>DS(on)</sub> from the MOSFET data sheet and calculate the power dissipation.

On the

$$Z_{\theta JC}$$

graph, find the pulse width,  $t_1$  on the x-axis and draw a vertical line to the curve matching the duty cycle, D, of the power pulses. This is the normalized thermal impedance for those operating conditions. The estimated junction temperature rise can be calculated as shown below.

$\Delta T_{I} = P \times Z_{\theta IC} \times R_{\theta IC}$

Power MOSFETs are found in a wide variety of applications but typically fall into one of two categories: switch-mode and linear-mode. Some examples of switch-mode applications are DC-DC converters, class-D audio amplifiers and motor drives. Inrush control for hot-swap, load switching and as a pass element in a linear regulator are common linear-mode applications.

# $P = I_D^2 \times R_{DS(on)}$

2

SLUAAT8 - DECEMBER 2023 Submit Document Feedback

(1)

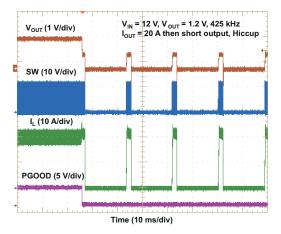

In most switch-mode applications, the MOSFET is selected and evaluated for a continuous output power level - thermal design power (TDP) - under steady state operating conditions. In this case, the power loss in the FET is constant and the junction temperature can be estimated using the thermal resistance,  $R_{\theta JC}$ , specified in the data sheet. However, during fault conditions such as an output short circuit, a DC-DC converter can go into hiccup mode current limiting. In this mode of operation, the controller stops the FET switching for a predefined time period before trying to restart. If the fault condition persists, the controller again stops switching and attempts to restart. This continues periodically until the fault condition is removed. An example for the TPS53819A in a synchronous buck converter is shown in Figure 4-1.

Figure 4-1. TPS53819A Hiccup Mode Short Circuit Protection

In this example, the pulse width,  $t_1$ , is approximately 2 ms and the period,  $t_2$ , is about 18 ms giving a duty cycle of 11%. Going back to the CSD17579Q5A  $Z_{\theta JC}$  graph, draw a vertical line from the x-axis at 2 ms up to the (closest) 10% duty cycle curve. From that intersection, draw a horizontal line to the y-axis which results in a  $Z_{\theta JC}$  value of approximately 0.52.

In linear mode applications, such as hot swap, the FET can be exposed to both single pulse events, such as inrush and overcurrent and periodic events such as retry mode which is similar to hiccup mode operation shown in the previous example.

## 5 Using the $Z_{\theta JC}$ Graph to Estimate MOSFET Peak Current Capability

The  $Z_{\theta JC}$  graph can also be useful during FET selection when the peak current requirement is known. As shown in this application brief, the FET maximum continuous drain current at  $T_C = 25^{\circ}C$  is calculated as follows:

$$Max I_{D} \left( T_{C} = 25^{\circ}C \right) = \sqrt{\frac{\left(\frac{Max T_{J} - 25^{\circ}C}{R_{\Theta JC}}\right)}{R_{DS(on)}@Max T_{J}}}$$

(3)

For single pulse or repetitive pulses, the thermal resistance is multiplied by the normalized transient thermal impedance value from the  $Z_{\theta,JC}$  graph. Now the calculation for peak drain current becomes:

$$\operatorname{Peak} I_{D}\left(T_{C} = 25^{\circ}C\right) = \sqrt{\frac{\left(\frac{\operatorname{Max} T_{J} - 25^{\circ}C}{Z_{\theta JC} \times R_{\theta JC}}\right)}{R_{DS(on)}@\operatorname{Max} T_{J}}}$$

(4)

## 6 Application Example

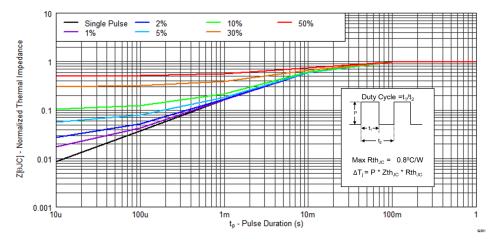

Using the CSD19532Q5B, what is the peak current for a 1-ms single pulse at  $T_C = 25^{\circ}C$ ? The  $Z_{\theta JC}$  graph from the CSD19532Q5B is shown below in Figure 6-1.

Figure 6-1. CSD19532Q5B  $Z_{\theta JC}$  Graph

The CSD19532Q5B maximum continuous drain current is calculated as follows:

$$Max P_{DISS} \left( T_{C} = 25^{\circ}C \right) = \frac{Max T_{J} - 25^{\circ}C}{R_{\theta JC}} = \frac{150^{\circ}C - 25^{\circ}C}{0.8^{\circ}C/W} = 156W$$

(5)

$$\operatorname{Max} I_{D} \left( T_{C} = 25^{\circ} C \right) = \sqrt{\frac{\operatorname{Max} P_{DISS}}{\operatorname{R}_{DS(on)} @\operatorname{Max} T_{J}}}$$

(6)

Maximum  $R_{DS(on)}$  at  $T_J = 150^{\circ}C$  can be calculated using the maximum specified  $R_{DS(on)} = 4.9 \text{ m}\Omega$  at  $V_{GS} = 10 \text{ V}$  and multiplying  $R_{DS(on)}$  by the normalizing factor shown in Figure 8 of the data sheet:

$$Max R_{DS(on)}@Max T_{J} = 4.9m\Omega \times 2.1 = 10.3m\Omega$$

(7)

Max

$$I_D(T_A = 25^{\circ}C) = \sqrt{\frac{156W}{10.3m\Omega}} = 123A$$

(8)

Draw a vertical line from 1 ms on the x-axis to the Single Pulse curve, and draw a horizontal line from there to the y-axis to get a value of  $Z_{\theta JC}$  = 0.17. The peak drain current is calculated as follows:

Peak

$$I_D \left( T_C = 25^{\circ}C, t_p = 1 \text{ms} \right) = \sqrt{\frac{\left( \frac{150^{\circ}C - 25^{\circ}C}{0.17 \times 0.8^{\circ}C/W} \right)}{10.3 \text{m}\Omega}} = 299 \text{A}$$

(9)

These calculations assume that the case temperature can be held indefinitely at  $T_C = 25^{\circ}C$ . In reality, this is impossible without using an infinite heat sink with zero thermal impedance. A more realistic approach is to assume the maximum case temperature is equal to the maximum allowable PCB temperature. For an FR4, a typical maximum temperature is 110°C and the peak drain current is reduced:

Peak I<sub>D</sub>

$$\left(T_{C} = 110^{\circ}C, t_{p} = 1 \text{ms}\right) = \sqrt{\frac{\left(\frac{150^{\circ}C - 110^{\circ}C}{0.17 \times 0.8^{\circ}C/W}\right)}{10.3 \text{m}\Omega}} = 169 \text{A}$$

(10)

What if the pulse width remains 1 ms but is repetitive with a duty cycle of 50%? From the  $Z_{\theta JC}$  graph, the value of  $Z_{\theta JC}$  = 0.56 for 1 ms, 50% duty cycle repetitive pulses. The peak repetitive drain current under these conditions is:

Peak repetitive

$$I_D \left( T_C = 110^{\circ}C, t_p = 1 \text{ms}, D = 50\% \right) = \sqrt{\frac{\left(\frac{150^{\circ}C - 110^{\circ}C}{0.56 \times 0.8^{\circ}C/W}\right)}{10.3 \text{m}\Omega}} = 93\text{A}$$

(11)

One last thing to note, for reliability purposes, most engineers typically derate the FET maximum operating junction temperature by 10°C to 25°C especially for repetitive pulses where the FET can operate for an extended period of time. For example, assume the derated maximum operating  $T_J = 130$ °C. Now, the peak repetitive drain current is:

Peak repetitive

$$I_D \left( T_C = 110^{\circ}C, t_p = 1 \text{ms}, D = 50\% \right) = \sqrt{\frac{\left(\frac{130^{\circ}C - 110^{\circ}C}{0.56 \times 0.8^{\circ}C/W}\right)}{10.3 \text{m}\Omega}} = 66A$$

(12)

### 7 Summary

This article explained how to use the  $Z_{\theta JC}$  graph from the MOSFET data sheet in a design and provided a few application examples. This is useful during FET selection and verification phases of a design.

## 8 References

- Texas Instruments, Understanding MOSFET Data Sheets, Part 4 Pulsed Current Ratings technical article.

- Texas Instruments, Understanding MOSFET Data Sheets, Part 6 Thermal Impedance technical article.

- Texas Instruments, CSD17579Q5A 30 V N-Channel NexFET™ Power MOSFETs data sheet.

- Texas Instruments, Power MOSFET Body Diode Continuous Current Carrying Capability application brief.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated