# High Power Factor Preregulator Using the SEPIC Converter

#### Lloyd Dixon

#### Summary:

The SEPIC converter combines the best features of the boost and flyback topologies, making it especially advantageous in high power factor preregulator applications.

In addition, ripple current can be steered away from the input, dramatically reducing input noise filtering requirements.

This paper discusses the design of the SEPIC converter, design of the coupled inductor to achieve ripple current steering, and Zero Voltage Transition circuitry to minimize switching losses.

#### The SEPIC Preregulator:

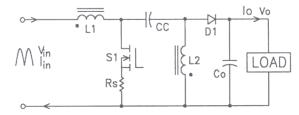

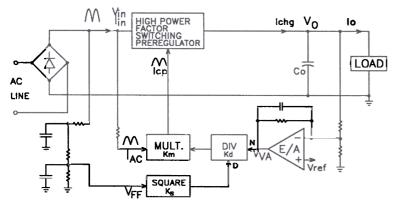

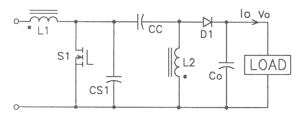

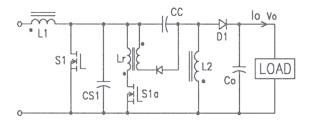

A Single-Ended Primary Inductance Converter (SEPIC) is shown in Fig. 1, configured as a nonisolated high power factor preregulator.

The SEPIC converter uses two inductances. The input inductor L1 together with the switch resembles a simple boost topology, whereas the shunt inductor L2 location is similar to a buck-boost, or flyback topology.

#### Fig 1. - SEPIC Power Circuit

In a conventional SEPIC converter, inductors L1and L2 are independent. This paper will show that improved dynamic performance is obtained by coupling these inductors. More importantly, if the coupled inductor is designed so that its leakage inductance (LL) is located in series with L1 in the input, the high frequency ripple current is steered *away* from L1 and into L2, thus greatly easing input noise filtering requirements.

The main advantages and disadvantages of the SEPIC high power factor preregulator are:

#### **PROs:**

- Single switch

- Continuous input current (like Boost)

- Any output voltage (like Flyback).

- Ripple current can be steered away from input, reducing the need for input noise filtering.

- Inrush/overload current limiting capability.

- Switch location facilitates MOSFET gate drive.

- Outer loop control scheme identical to Boost-UC3854 can be used in same manner.

- Possibility of isolation/step down using secondary inductor winding, if a way can be found to avoid leakage inductance problems.

#### CONs:

- Higher switch/diode peak voltages and currents compared to boost topology.

- Bulk capacitor size/cost will be greater if operated at lower voltage than boost.

#### **SEPIC Circuit Operation**

In most high power factor preregulator applications, the switching frequency is very much greater than the 50-60Hz line frequency. Except for the bulk filter capacitor, the inductor and capacitor values in the power circuit are based upon switching frequency (HF) considerations, Their impedances are negligible at line frequency (LF). Thus, instantaneous values along the rectified line waveform are regarded as "dc" values when analyzing HF operation.

Coupling capacitor Cc is an important element in the SEPIC topology. Its voltage offset allows the SEPIC's boost-like inductor input to coexist with an output voltage which may be less than  $V_{IN}$ .

The steady-state average voltage across Cc always equals VIN. To demonstrate this, look at the circuit mesh including VIN, Cc, and inductances LI and L2. Since the steady-state average voltage across all inductor windings must equal zero, Vcc(avg) must equal VIN. In a practical SEPIC preregulator, Cc is small (~0.5µF for 200W), so that Vcc(avg) tracks the rectified line voltage. A small triangular HF ripple voltage also appears across Cc.

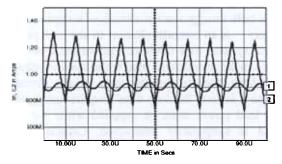

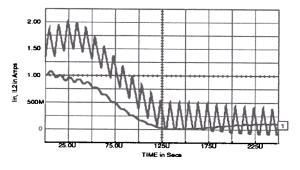

Fig. 2 shows the inductor currents in a conventional 200 Watt SEPIC converter operating at 100kHz with  $V_{IN}=220V$ ,  $I_{IN(\alpha\nu_g)}=0.9A$ , and  $V_{O}=200V$ . Inductors L1 and L2 are equal (4mH) and independent (not coupled). Input ripple is  $250mA_{P-P}$ .

**Circuit explanation:** Refer to the waveforms of Fig. 2 and the circuit of Fig. 1 with the inductors independent. When the switch is ON, the instantaneous rectified line voltage, VIN, is applied to L1, with its dotted end positive. At the same time, Vcc = VIN is applied to L2, with its dotted end also positive. Since L1 = L2, IL1 and IL2 ramp upward at the same rate: VIN/L. The switch current is the sum of IL1 (input current) and IL2. The rectifier reverse voltage equals VIN plus Vo.

When the switch is OFF, the currents flowing through L1 and L2 force their voltages to reverse until the output rectifier conducts current (IL1+IL2), previously conducted by the switch. L2 is clamped directly across Vo with its dotted end negative. VIN

- SEPIC Waveforms, Independent Inductors [1]-IIN, [2]-IL2

and Vcc cancel, so that Vo also appears across L1, with its dotted end also negative. ILI and IL2 both ramp downward at the same rate: Vo/L.

While the switch is OFF, IIN charges Cc. While the switch is ON, Cc is discharged by IL2. Although the steady-state average Vcc equals VIN, the nearly rectangular current waveform through Cc results in a triangular ripple voltage across Cc.

By inspection, note that although the switch and rectifier conduct alternately, both block ( $V_{IN}+V_O$ ), and both conduct ( $I_{IN}+I_{L2}$ ). Also, if D is the switch duty cycle,

$$I_{O} = (I_{IN} + I_{L2})(1 - D)$$

(1)

Since steady-state (and LF) Icc must equal zero,

$$I_O = I_{L2} \tag{2}$$

Obviously, by inspection,

$$I_{IN} = I_{LI} \tag{3}$$

Assuming 100% efficiency, Volo = VININ, and

$$I_{L2} = I_O = I_{IN}(V_{IN}/V_O)$$

(4)

Thus with  $V_{IN} = 220V$ ,  $V_O = 200V$  and 200W, Fig. 2 shows  $I_{O(avg)} = 1A$  and  $I_{IN(avg)} = 0.9A$ .

Since the steady-state (and LF) voltage across any inductor must equal zero, the volt-seconds applied to L2 (and L1) during the ON time must be opposed by equal volt-seconds during the off time. Thus:

$$V_{IN}D = V_O(1-D); \quad D = \frac{V_O}{(V_{IN}+V_O)}$$

(5)

Note that the duty cycle relationship above for the SEPIC converter is identical to the buck-boost (flyback) topology, even though the input current characteristic closely resembles a boost converter.

### **Ripple Current Steering**

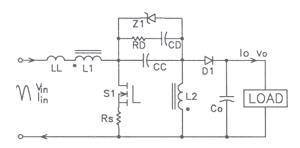

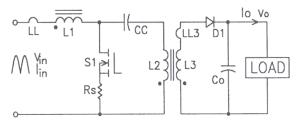

Identical voltages are applied to L1 and L2 at all times throughout the switching period. This permits the inductors to be coupled by winding them (with equal turns) on a single magnetic core. (In order to maintain the same total ripple current and same total inductive energy storage, the coupled inductance value is halved: 2mH.) Referring to Fig. 3,

# UNITRODE CORPORATION

#### Fig. 3 - SEPIC with Coupled Inductors

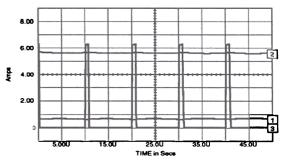

the coupled inductor is designed so that its leakage inductance, LL, is located in series with winding LIin the input. In this example, LL is 10% of the 2mH mutual inductance, or 0.2mH. The high impedance of LL in series with LI opposes the ripple current, forcing most of it into winding L2, which has only the relatively low impedance of Cc in opposition. As shown in Fig. 4, the triangular HF ripple current through L2 is increased to 500mA<sub>P-P</sub>. The input ripple is reduced to only 50mA<sub>P-P</sub> (mostly at the 100kHz fundamental), greatly diminishing the input noise filtering requirements.<sup>[1]</sup>

SEPIC Waveforms, Coupled Inductors [1]-IIN, [2]-IL2.

The design of the coupled inductor to achieve this important result is given in a separate paper.<sup>[2]</sup>

To summarize, the diversion of ac ripple from L1 to L2 occurs because (a) although the *total* current in coupled windings L1 and L2 is difficult to change, current can easily transfer from one winding to the other, and (b) the high impedance of LL opposes the ac ripple current in input winding L1 while the low impedance of Cc provides an easy path for the HF ripple current through winding L2.

The single coupled inductor is also smaller and costs less than two independent inductors with the same energy storage capability.

**Design Considerations:** The coupled inductance value L1 = L2 is made as small as possible to reduce cost/size and improve frequency response, limited by the amount of ripple current that can be tolerated. In this application, 2mH results in a worst-case ripple of  $0.65A_{PP}$  at highest  $V_{IN} =$  $365V_{pk}$ . This is best calculated during the OFF time when  $\Delta IL2/toFF = Vo/L$ . Max toFF can be calculated at max VIN using Eq. 5.

A large  $LL \cdot Cc$  product results in low input ripple, but impairs frequency response and increases cost. It is better to make Cc small to reduce inrush surge and cost. LL should be correspondingly large provided it can be integrated into the design of the coupled inductor to eliminate its size/cost.

Worst-case input ripple (and EMI) is at the low line peak and full load. A near-rectangular current waveform passes through Cc: IIN when the switch is OFF, and IL2 (=Io) in the other direction when the switch is ON. This current waveform produces a triangular ripple voltage across Cc. This is best calculated during the ON time when  $\Delta Vcc/ton=-Io/Cc$ . Io = 2A at 400W<sub>pk</sub>, 200V out. Max ton can be calculated from Eq. 5 at min VIN. In this application, a Cc of 0.5µF results in 25.6V<sub>PP</sub> worst-case at low-line VIN<sub>pk</sub> = 113V, and 400W.

The triangular ripple voltage across *Cc* appears directly across *LL*. *LL* integrates this triangular voltage into a quasi-sinusoidal waveform (which is the input ripple). The peak-peak fundamental is  $\sqrt{2}/\sqrt{3}$  of a peak-peak triangular waveform, or  $21V_{pp}$ in this application. Dividing by *XLL* =  $130\Omega$  (0.2mH at 100kHz) obtains 0.16A<sub>pp</sub> input ripple at 400Wpk and low-line *VINpk*. (Fig. 4 shows 50mA ripple at 220V input and 200W.)

**Resonance problems:** The coupled-inductor SEPIC topology has an unusual high-Q resonance effect involving leakage inductance LL and coupling capacitor Cc. In Fig. 3, examine the circuit mesh involving VIN, the inductances, and Cc. The ac impedance of VIN is quite low (an input noise filter capacitor). Inductors L1 and L2 are tightly coupled in opposition, so their impedances cancel. The only significant ac impedances in this loop are LL and

Cc. With  $0.5\mu$ F and 0.2mH used in this example, they will resonate with high Q at 16KHz. LL and Cc are tightly coupled to each other at all times during the switching period. Even when the switch is closed, LL and Cc are coupled through the tightly coupled L1 and L2 windings.

Unless damped, shock-excited oscillations will send considerable 16KHz ripple back through the input. Theoretically, damping would be achieved if the input current control loop had significant gain at the 16KHz resonant frequency. However, a crossover frequency well above 16 KHz is not practical, as will be explained later. So damping is accomplished by the "brute-force" method using damping network  $R_D$  and  $C_D$  in shunt with Cc. (Series damping is impractical because of high losses due to the high ac current through Cc.)

To achieve critical damping requires a shunt  $R_D$  equal to 1/2 of the resonant impedance. But this requires a large blocking capacitor  $C_D$ , increasing cost and reducing the resonant frequency. As a compromise in this application,  $R_D$  of 10 Ohms is in series with  $C_D$  of 2.5µF, resulting in Q  $\approx$  1, underdamped but adequate.  $C_D$  reduces the self-resonant frequency to 8KHz, but at the 100KHz switching frequency, the coupling network is still effectively 0.5µF. Normal operating loss in  $R_D$  is less than 2W, but may be 6W with output shorted.

# **Output Voltage Level**

In a boost preregulator, there is little choice — in order to function, the output voltage must be greater than the highest peak  $V_{IN}$ . Thus for a dual range (110/220V) input, the output voltage is normally 385V to 400V.

For the SEPIC converter, no such constraint exists. Theoretically, the output voltage can be any value — above or below the input voltage. However, there are several practical considerations.

Voltage and current ratings: In general, the SEPIC converter is "most comfortable" when Vo = VIN, and D = 0.5. When Vo is much greater or much smaller than VIN, peak voltages and peak currents become extreme. Peak switch and rectifier voltage is VIN+Vo. Peak current through these devices (neglecting HF ripple) is IIN+Io. Substituting Io from Eq. 4:

$$I_{IN} + I_O = I_{IN} \frac{V_{IN} + V_O}{V_O} = \frac{I_{IN}}{D}$$

(6)

From this viewpoint alone, Vo in the range of 100–150V is probably optimum for 120V line input, resulting in peak switch and rectifier voltages of 300–350V. For single range 220V, or for 120V/220V input, Vo of 200V results in peak voltages approaching 600V at high 220V line.

**Bulk capacitor size and cost:** For the same bulk energy storage capability, electrolytic capacitor size and cost tend to vary inversely with voltage rating (more about this later). This consideration alone favors a high Vo, limited by capacitor reliability considerations.

**Bus voltage requirements:** Power distribution bus voltage will probably *not* be a factor in this decision. This SEPIC converter does not provide the line isolation usually dictated by safety requirements. Because an additional stage is required to obtain isolation, the bulk energy can be stored at any voltage, based on the previous considerations.

### **Bulk Energy Storage Requirements:**

A bulk energy storage device - a capacitor or battery - is an essential element in any high power factor system. At a minimum, power must be provided to the downstream load while the line voltage waveform transits through zero. Many systems define a longer "hold-up time" requirement where full load power must be supplied while the line input is temporarily interrupted. Capacitors are normally used for bulk energy storage when holdup time requirements are in the tens or hundreds of milliseconds. For longer hold-up times, capacitor size and cost becomes prohibitive, so batteries are used.

When holdup requirements are minimal, a small bulk capacitor may provide the required energy storage, but other factors may then become dominant:

- 1. The trade-off between voltage control loop dynamics and input third harmonic distortion becomes severe with a small bulk capacitor.

- 2. The capacitor current rating (120Hz ripple current plus 100kHz switched current) can be

inadequate — this relates to its Equivalent Series Resistance.

3. 120Hz ripple voltage becomes large. These concerns are discussed in Ref. [3] and [4].

**Capacitor size and cost:** Electrolytic capacitors are "formed" by the manufacturer to various dielectric thicknesses. Thus several different voltage ratings and capacitance values are available in a single case size. The voltage rating is proportional to the dielectric thickness, but the capacitance value is inversely proportional. Therefore, for a given case size, C-V tends to be a constant value. A capacitor rated for 200V operation will have twice the capacitance as its 400V counterpart in the same case size.

However, at 200 Volts, 4 times the capacitance value is required as at 400V to achieve the same energy storage ( $\frac{1}{2}$ CV<sup>2</sup>) holdup capability, the same loop dynamics vs. harmonic distortion tradeoff, and the same percent 120Hz ripple. Thus, twice the physical volume (and cost) is required at 200V. For a given application, capacitor size and cost tends to vary inversely with voltage. Storing bulk energy at 48V vs. 385V can require 8 times the capacitor size, weight, and cost.

# **Current Control Loop Design**

The control characteristic of the SEPIC converter is complex. Fortunately, in a high power factor preregulator application, the current loop control characteristic is simplified because: (a) Input current, rather than output current, is controlled, (b)  $V_0$ is essentially constant because of the large output bulk capacitor which buffers the current control loop against rapid load changes, and (c) the outer voltage control loop requires very low bandwidth to minimize line current distortion and thus does not contribute to current loop instability.

Conventional (peak) current mode control depends upon a current waveform with a linearly increasing ramp. However in this SEPIC converter, ripple current is steered away from the input, leaving only the small amplitude quasi-sinusoidal waveform shown in Fig. 4. This waveform is totally unsuited for peak CMC of input current.

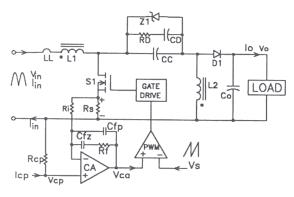

Average current mode control, using a current error amplifier as embodied in the UC3854A, could

handle this situation, but there is an additional serious complication: Resonance between LL and Cc puts two poles in the control-to-input-current characteristic. There is also a pole due to coupled inductor L1/L2, which varies with load. Thus there are three active poles (one variable) above the LL-Cc resonant frequency (10-15 kHz). This makes it impractical to achieve a crossover frequency, fc, above resonance. But with a lower crossover frequency there is insufficient loop gain to dampen the high Q LL-Cc resonant peak.

The solution to this problem is to use average CMC of the average switch current. The switch current waveform is chopped, whereas the input current is continuous with a very small ripple. Even though their waveshapes are radically different, average switch current equals average input current (at frequencies below LL-Cc resonance). The control-to-switch-current characteristic is identical to the control-to-input-current characteristic, except the switch current characteristic does not have the extra two resonant poles. Thus it is easy to control the switch current using average CMC. (Peak CMC won't do-the peak current is much greater than the average.) Since the LL-Cc resonant circuit is now outside the control loop, it would ring if not for the damping network, RD and CD.

An additional important benefit of controlling average switch current: Switch current is discontinuous, allowing the use of a current transformer (CT) for current sensing. This is not possible with input current, nor is there any apparent way to synthesize the input current waveform.

The optimized average CMC method is well suited to any high power factor preregulator topology. It provides input voltage feedforward to rapidly adapt to instantaneous line voltage changes. It eliminates the peak-to-average error which contributes to distortion with peak CMC. It provides sufficient gain and bandwidth in the discontinuous mode to adequately track the sudden reversal of current required at the cusp of the rectified voltage waveform.

Figure 5 shows the SEPIC preregulator with average CMC control loop. Optimization of the current control loop is covered in a separate Seminar topic<sup>[5]</sup>, which includes the derivation of a

Fig 5. - SEPIC with Average CMC

small-signal model of the coupled-inductor SEPIC converter.

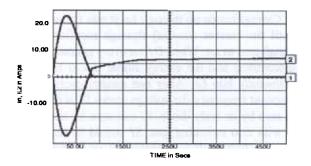

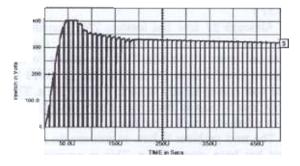

Figure 6 demonstrates the ability of the SEPIC power circuit with average CMC to track a change in input current demand from 1A to 50mA, and its stability. The max. rate of input current change is determined by LL and Cc, and is much faster than the most severe requirement of the actual application. Note that portions of the IL2 waveform go negative, yet operation is not discontinuous because total inductor current IL1+IL2 is not negative.

Fig 6. - Change in Current Demand

# **Input Current Sensing**

With most high power factor preregulator techniques, input current must be sensed in order to make it conform to the desired waveshape. It is more difficult to sense input current in the SEPIC converter than in most other topologies, because input current is continuous, ruling out current sense transformers, and because the resonant *LL-Cc*  characteristic is associated with the input current. However because of the unique identity between average switch current and input current, the discontinuous switch current can be used as a substitute, eliminating both problems.

A current sense resistor is certainly the easiest current sense method at the low end of the power range, where the sense resistor power loss is not too serious. At least 1 Volt sense voltage at full rated input current is required to achieve current loop optimization with low-bandwidth amplifiers such as in the UC3854. A smaller sense voltage reduces the sense resistor loss, but requires a higher amplifier bandwidth such as in the UC3854A. The switch current should be sensed. This enables the sense resistor to be located in series with the MOSFET source terminal which maintains the IC current amplifier input at positive potential, eliminating problems with substrate diode conduction.

A current sense transformer (CT) cannot be used to sense input current directly because the waveform is continuous, giving no opportunity to reset the core. Fortunately, it is better to sense switch current for reasons discussed earlier, thus facilitating the use of a CT. The current transformer can provide a relatively high sense voltage to the current amplifier, reducing its required bandwidth. The CT reduces the power loss involved in direct current sensing, and eliminates the cost and difficulty of using a low resistance value, high wattage precision resistor.

Locating the CT primary in series with the MOSFET drain may reduce current spikes through the CT when the switch turns on.

# Voltage Control Loop Design

Once the current loop has been optimized and properly closed, the specific power circuit topology is "buried" within the current loop. External to the closed current loop, the voltage control loop functions in exactly the same way, with the same design considerations whether the power circuit topology is boost, flyback, or SEPIC. The voltage loop establishes the desired amount of input current, but the current loop controls the specific power circuit topology to make it happen. Any HPF control circuit with a current amplifier can be used for

Fig 7. - HPF Preregulator Voltage Loop and Current Programming, any Topology, using the UC3854A

average CMC of the SEPIC preregulator. As shown in Figure 7, the UC3854A can be used, following the same procedure described in Reference [4] for a boost preregulator. (Reprinted in the back of this Seminar manual.)

#### **Overcurrent Limiting**

In normal operation, the outer voltage control loop programs an input current consistent with the power demand of the load, and sets an average input current *limit* consistent with the maximum power rating of the supply. However, when the output voltage is well below normal, either during the startup process or during severe overload, if the control circuit tries to maintain full rated power, an unacceptably high current level results.

For example, a 200 Watt preregulator must provide 400W at the line peak. Assume 100% efficiency, PIN = POUT. At VO = 200V and VIN =113V (peak input at 80V low line), IIN = 3.55A and IL2 = IO(avg) = 2A. Peak current through switch SI and rectifier D1 is 2A + 3.55A = 5.55A. But if VO is pulled down to 10V by a severe overload, 400W at the input is still 3.55A, but the same 400W delivered to the output is now 40A! Peak current through S1 and D1 is now an intolerable 43.55A. This same total current through the coupled inductor requires it to be grossly overdesigned to prevent saturation.

The solution to this problem, effective for startup or short-circuit conditions, is to incorporate in the control circuit an absolute limit on the peak *switch* current. This causes input current and power to be reduced in line with the reduced output power. In other words, the peak switch current limit translates into foldback input current limiting.

Peak switch current, peak rectifier current and total inductor current are the same: IIN + Io. So absolute current limiting is achieved by sensing the current through SI and shutting the switch off whenever the absolute limit is reached.

Switch current sensing already exists for use with the average cur-

rent mode control loop. This same sense voltage can rent mode control loop. This same sense voltage can be used for peak current limiting. The UC3854 HPF control IC has a peak current limit input, but it requires a negative-going signal, opposite to the polarity used for average CMC in this application. Both polarities can be easily obtained from one sense transformer by seriesing two resistors across the CT secondary, and ground referencing the junction of the two resistors.

Fig 8. - Overload [1]-IIN, [2]-IL2, [3]-ISW

Fig. 8 shows the SEPIC converter operating in equilibrium with ViN at 113V and Vo pulled down to only 10V. The normal control circuit would call for 400W, but the peak switch current limit takes over control. When S1 turns on, its current is the sum of IIN plus IL2. It does not take long for the current to ramp up to the 6.25A limit. When S1 turns off, the 6.25A transfers to the output through D1 (not shown) for the remainder of the switching period. Note that IL2 = Io(avg) = 5.65A, delivering 62.2W to the 10V output plus 1V diode drop. IIN is

only 0.6A, taking 67.8W from the 113V line. The 5.6W power difference is due to loss in the damping network (which is worst case under this condition). Without the absolute switch current limit, the 400W power limit would force  $I_{2}$  to 40A at 10V out, or even greater current with lower Vo.

Setting the current limit: The limit must be set high enough to provide full power at low line in normal operation with Vo=200V. For a 200W application, assume 80Vrms minimum, requiring 2.5Arms. Peak power is twice the average power at peak voltage and current — 400W at VIN=113V and IIN=3.55Apk. From Eq. 6:

$$I_{IN} + I_O = I_{IN} \frac{V_{IN} + V_O}{V_O} = 3.55 \frac{113 + 200}{200} = 5.55 \text{A}$$

Allowing for superimposed HF ripple current, a peak switch current limit of 7A would be appropriate. The inductor must be designed not to saturate at this current limit.

#### Start-up

Inrush surge: In normal operation, the voltage across coupling capacitor Cc is always equal to the instantaneous rectified line voltage. But at initial startup, Cc and the bulk output capacitor are both discharged. When the power supply is turned on, an inrush current surge charges Cc and Cb rapidly through the series inductor windings. This inrush surge is actually of little consequence because this capacitance is small ( $3\mu$ F in the 200W preregulator) and charges rapidly. The much larger bulk capacitor ( $800\mu$ F) is then charged slowly to Vo, under current limit control. This behavior of the SEPIC converter contrasts sharply with a boost converter, whose inrush surge charges is orders of magnitude greater because it charges the huge bulk capacitor directly.

Referring to Fig. 3 it can be seen that the inrush current flows *into* the dotted end of L1 but *out* of the dotted end of L2. Thus the ampere-turns of these coupled windings cancel. The core will not saturate no matter how large the inrush current is. Only the leakage inductance LL (in addition to the line impedance) limits the inrush surge. Since the leakage inductance flux is located in the non-magnetic region in and between windings L1 and L2, there is no danger of saturating LL.

There is one serious problem: *Cc resonantly* charges through *LL* to a voltage much higher than the instantaneous line voltage when the supply is turned on. Without damping, if the instantaneous line happens to be at the peak 220V high line condition (365V) when the supply is turned on, *Cc* would charge to nearly 730V, considerably more than 365 plus 200 = 565V worst case under normal operation. The damping network helps considerably, but because it is underdamped, the overshoot may still be excessive, increasing the voltage rating requirements of MOSFET *S1* and rectifier *D1*.

If the damping does not limit the overshoot sufficiently, Vcc can be limited with a 400V Zener diode – a little greater voltage than the maximum peak  $V_{IN}$  of 365V, so the Zener will not interfere with normal operation. In most cases, the Zener diode should not be needed.

Figure 9a shows the inrush surge current with  $V_{IN}$  at 300V when the supply is turned on, and Fig. 9b shows the voltage across switch SI as Vcc resonantly charges, clamping at 400V.

The inrush surge amplitude and pulse width can be estimated from the resonant frequency and resonant impedance of the inrush circuit (neglecting line and input rectifier impedance):

$$f_R = \frac{1}{2\pi\sqrt{L_L C_{eff}}} , \quad Z_R = \sqrt{\frac{L_L}{C_{eff}}}$$

With the circuit conditions of Fig. 9, LL = 0.2mH,  $Cc = 0.5\mu$ F,  $CD = 2.5\mu$ F and  $RD = 10\Omega$ . The effective capacitance at resonance is  $2\mu$ F, resulting in fR = 8kHz and  $ZR = 10\Omega$ . The peak undamped inrush current would be  $300V/10\Omega=30A$ , but damping reduces this to 25A peak. The half-cycle resonant pulse width is 60µsec, lengthened somewhat by the action of the 400V clamp. Compared to the startup surge to charge  $800\mu$ F directly, this surge is insignificant.

Fig. 9a shows that the inrush surge ends at 85 $\mu$ sec. During the surge, the switch turns on periodically, which applies Vcc momentarily across L2. Thus when IIN reaches zero at the end of the surge, IL2 is already at 3A in the positive direction.

Following the inrush surge: From 85 to 190  $\mu$ sec, each time the switch turns on, Cc gives up a

Fig. 9a - Startup [1]-IIN, [2]-ILI

Fig. 9b - Startup Vswitch

little of its energy into L2, causing Vcc (seen across the switch) to slowly fall towards VIN (300V), and IL2 to slowly rise. Most of the time, the switch is off, and IL2 is delivered through D1 to output capacitor Co. IIN remains at zero as long as Vcc is greater than VIN, because when the switch turns on, Vcc is applied to L2, inducing Vcc > VIN across L1 as well. Since VIN is still at 300V, the input rectifiers (not shown in Fig. 3) block all current flow.

At 190 $\mu$ sec, *IL2* reaches 6.5A and the switch current limit becomes effective. When the switch turns on, *Vcc* applied to *L1* causes *IL1* to rise rapidly until the 6.5A switch current limit is reached. When the switch turns off, *IL1* slowly discharges into *Co* (*Vco* is almost zero). The duty cycle thus is extremely short at the current limit.

With  $Co = 800\mu$ F, the output voltage rises at a rate less than 1V/100µsec!! So during the entire time shown in Fig. 8, the output is essentially shorted, and energy is being transferred from Cc (and CD) to Co, and IIN = 0.

At approximately 1000µsec, Vcc has decreased to equal ViN, which is still near 300V. (Vcc subse-

quently tracks  $V_{IN}$  along the rectified line waveform). Now, for the first time since the end of the surge, the input rectifiers can conduct and  $I_{IN}$  starts to rise. The rate of rise is not determined by winding  $L_1$ , but by leakage inductance  $L_L$ . Since  $L_1$  and  $L_2$  are coupled, whatever current is demanded by  $L_L$  is easily diverted away from winding  $L_2$  into winding  $L_1$ . As  $I_{IN}$  starts to rise,  $I_{L_2}$  falls in a complementary manner. The total current  $I_{IN+I_{L_2}}$ through the switch remains at the current limit.

During this last phase of the start-up process, when Vcc = VIN, current limited operation is identical to the situation described earlier with severe overload. The output will rise slowly as the bulk capacitor charges at the current limited level. When Vo rises to the point where Vo times the current limited charging current equals the power limit for normal operation, the current backs away from the current limit and normal power-limited operation takes over.

Note that the foldback limiting characteristic of the peak switch current limit requires that constant power loads (such as downstream switching power converters) be disabled when Vo is low, using undervoltage lockout. Otherwise, the reduced power input will not be able to pull up the preregulator output during start-up or after an overload has cleared. With resistive loads, this is not a problem, because load power is automatically reduced.

When Vo is at or very close to zero, the very small duty cycle required to maintain the current at the limit may require an ON time less than the system can provide, for various reasons including ZVT circuitry. To prevent loss of control, if the current is already over the current limit when the clock pulse occurs, the current limiting circuit should inhibit the ON pulse completely, skipping pulses until the current falls below the limit.

#### **ZVT Circuitry**

Zero Voltage Transition capability is an important addition to any high power factor preregulator. High voltage circuits store significant energy in circuit parasitic capacitances. High voltage rectifier recovery characteristics are far from ideal, especially at higher power levels. With "hard" switching, these characteristics translate into high losses, severe component stress, and radiated EMI. ZVT circuitry facilitates nearly lossless transitions and reduces noise.

Zero Voltage Transitions occur naturally whenever the power switch SI turns off. Current  $I_{IN+II2}$  transfers from the switch to the capacitance of the switch, rectifier, and circuit parasitics (lumped together as  $Cs_I$  in Fig. 10a) while the capacitance holds the voltage near zero. Then the capacitance charges as the voltage rises until clamped by the output rectifier conduction. Thus, turn-off loss is quite small without any special design effort.

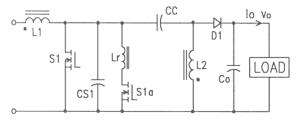

Fig 10a - Non-ZVT SEPIC Circuit

Turn-on is a different matter. SI is clamped at high voltage (VIN+Vo) while the current makes its transition, causing power loss in the switch. This loss is worsened by the high voltage rectifier's reverse recovery current, especially if the switch turn-on is fast to minimize the transition time. No matter how fast SI turns on, the very significant energy stored in CsI is translated into switch loss.

The first step in achieving turn-on ZVT is to connect a small inductor  $L_R$  in series with an auxiliary switch SIa across main power switch SI as shown in Fig. 10b.<sup>[6]</sup> SIa is a much smaller device than main power switch SI, with much lower *Coss*. When the control IC calls for switch turn-on, SIa is turned on first. SI turn-on is delayed.

Current ramps up through LR at rate (VIN+VO)/LRuntil the current (IIN+IL2) through rectifier DI is transferred to LR. When DI recovery is complete, it disconnects and the energy stored in  $Cs_I$  transfers resonantly into LR. After one quarter cycle at the resonant frequency the voltage across SI is clamped at zero by its body diode. SI can now be turned on - with zero switching loss. SI should be turned on and SIa turned off simultaneously, or as quickly as possible to transfer the current away from the much smaller SIa with its higher static losses. (As long as SIa remains on, LR will prevent the current transfer to SI.)

Although S1 now has lossless ZVT transitions, S1a clearly has turn-on losses. However, the big turn-on losses of the non-ZVT circuit due to the current transfer from D1 and the energy stored in  $Cs_1$  now end up mostly as energy stored in LR. The only loss in S1a is from the energy stored in its own relatively small capacitance.

The next problem is how to recover the energy that has been stored in  $L_R$ . This is accomplished with a second tightly coupled winding on  $L_R$ , as shown in Fig. 10c. The two windings have the same number of turns, bifilar wound. When *S1a* turns off, current transfers to the second winding and passes through the diode to any convenient voltage sink -- *Vcc* or *Vo*, where the energy stored in  $L_R$  is recovered.

#### Fig 10c - Energy Recovery

The ON time of the ZVT switch S1a becomes the minimum ON time of the SEPIC converter. In normal operation, this is not a problem. As shown by Eq. 5, the minimum duty cycle occurs at max VIN and never approaches zero with normal values of Vo. But D does approach zero when Vo is zero during start-up or short-circuit load conditions. The control circuit must then skip pulses to reduce the

# UNITRODE CORPORATION

duty cycle and retain control in spite of the fixed minimum ON time.

**Design Considerations:** Two things must be defined: (1) the inductor  $L_R$  value, and (2) the delay time for turning on S1 after S1a has been turned on (which will be the minimum ON time of the converter).

There are three sequential times involved:

1. The time for current to ramp up in LR and transfer away from D1:

tRAMP = Lr(IIN+IO)/(VIN+VO)

- 2. D1 recovery time

- 3. Resonant quarter cycle when energy transfers from Cs1 to LR:

tres =

$$\pi \sqrt{LrCs_1/2}$$

A small  $L_R$  value reduces tRAMP and tRES but worsens the diode recovery current and peak resonant current. One approach is to consider what would be a reasonable delay time (minimum ON time). A ramp time of 200ns is 2% of the 10µsec switching period. Worst case is at peak low line, full power. Applying the values developed earlier for this specific application to the tRAMP equation above:

$L_R = 200 \text{ns}(113\text{V}+200\text{V})/(3.55\text{A}+2\text{A})$  $L_R = 11.27 \mu\text{H}$

For  $LR = 10\mu$ H, tRAMPmax is 171nsec.

Assuming a total capacitance *Csi* of 500pF, the resonant frequency is 2.4 MHz, resulting in a time tRES of 104ns for 1/4 cycle. This time is independent of *ViN* or load. Resonant impedance  $ZR = (L/C)^{\frac{1}{2}} = 141\Omega$ . At high line peak of 365V, this results in a peak resonant current of (365+200)/141 = 4A (in addition to 3A *Io+IIN* at high line peak).

A total *S1a* ON time of 300nsec, resulting in a minimum duty cycle of .03 is reasonable and adequate for this application.

Switching losses in high power factor applications are especially severe because of the high voltages being switched. ZVT techniques are unusually advantageous. The biggest implementation problem at this date is that existing HPF control ICs do not provide the delayed driver function, forcing it to be accomplished with outboard components.

#### Line Isolation

It is theoretically possible to incorporate line isolation in the SEPIC converter by adding an additional winding L3, as shown in Fig. 11.

Insulation for 3750Vrms isolation must be incorporated between windings L2 and L3. Unfortunately, the high voltage insulation prevents close coupling between these windings. The resulting leakage inductance is large and its circuit location (directly in series with either L2 or L3) causes delays, voltage spikes and difficulty energy recovery problems.

Fig 11. - SEPIC Converter with Isolation

To date, there are no known practical solutions to this problem. If a way can be found, this would considerably enhance the usefulness of the SEPIC high power factor topology. Bear in mind that if an isolation technique is also used to step down to an isolated 48V bus, for example, there is a substantial penalty in bulk capacitor size and cost vs. energy storage at 200V.

A suggestion for anyone who would attempt to solve this problem: If L1 and L2 are also coupled to maintain ripple current steering as discussed earlier, it is important to use the following winding sequence, starting from the gapped core center leg: L3, HV insulation, L2, L1. Otherwise the leakage inductances LL in the input and LL3 in the output will be coupled to each other, with (probably) disastrous results.

# Conclusions

The SEPIC converter has many advantages for high power factor preregulator applications. Steering the high frequency ripple current away from the input can dramatically reduce the size and cost of th input noise filter. This advantage, the very small start-up surge, and the inherent current-limiting capability become more and more significant as the power level rises.

# **References:**

- [1] Paul Steffens, Personal Communication

- [2] L.H. Dixon, "Coupled Inductor Design," Unitrode Seminar SEM900, Topic 8, 1993

- [3] L.H. Dixon, "High Power Factor Preregulators for Off-Line Power Supplies," Unitrode Seminar SEM600, 1988 (Reprinted as Topic I2 in SEM800, SEM900)

- [4] L.H. Dixon, "High Power Factor Switching Preregulator Design Optimization," Unitrode Seminar SEM700, 1990 (Reprinted as Topic I3 in SEM800, SEM900)

- [5] L.H. Dixon, "Control Loop Design, SEPIC Preregulator Example," Unitrode Seminar SEM900, Topic 7, 1993

- [6] G.C.Hua, C.S.Leu, Y.M.Jiang, F.C.Lee "Novel Zero-Voltage Transition PWM Converters," VPEC Power Electronics Seminar Proceedings, p33, 1992

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated