# Optimize the Loop Compensation for Start-up Using TPS61178x

Yangwei Yu

#### ABSTRACT

The response time becomes increasingly important for the power supplies of some applications to minimize the overshoot/undershoot during load transient. To accomplish the stringent requirements, a very common method is to increase the system bandwidth. However, for a boost converter with load disconnect, there are two sets of output capacitors before and after the disconnect FET, so the output capacitor configuration is different for two phases of disconnect being FET on and off. This application note addresses the design of loop compensation of the boost converter with load disconnect to ensure the stable operation for both disconnect FET on and off. An example of TPS61178x is illustrated to show the design details together with the real bench measurements.

#### Contents

| 1 | Introduction                               | 1 |

|---|--------------------------------------------|---|

| 2 | Start-up                                   | 1 |

| 3 | Loop Compensation                          | 3 |

| 4 | Initial Inrush Current After EN ON         |   |

| 5 | References                                 | 4 |

|   | List of Figures                            |   |

| 1 | TPS61178x Start-up Behavior                | 2 |

| 2 | TPS61178x Control Loop of Normal Operation | 3 |

#### List of Tables

### Trademarks

All trademarks are the property of their respective owners.

### 1 Introduction

As a boost with load disconnect function, there is an additional FET serving as the disconnecting input from the output when the device is in shutdown or fault condition. Output capacitance is placed both before and after the disconnect FET, which caused the different output capacitor configuration with the disconnect FET turning on and off. However, the loop compensation usually just covers the case with the disconnect on. It might cause the unexpected performance for the case of disconnect FET in off status. This application note illustrates the details of the loop compensation design to cover both the disconnect on and off using the TPS61178x as an example.

### 2 Start-up

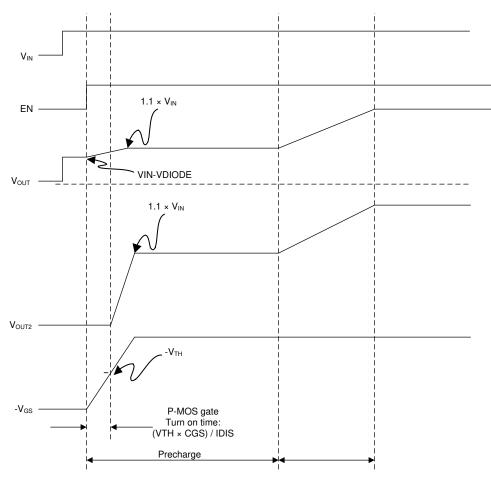

Figure 1 shows the start-up behavior where VOUT2 is the output voltage after the disconnect FET, VOUT is the output voltage before the disconnect FET, and -VGS is the gate voltage between gate and source of the disconnect FET. IDIS is the gate discharge current of the disconnect FET.

Start-up

Figure 1. TPS61178x Start-up Behavior

When the input voltage to the device exceeds the UVLO threshold and EN pin pulled to high, the TPS61178x starts to ramp up the output voltage. There is a switching pre-charge phase and the output voltage is charged up to 10% higher than the input voltage (1.1 x VIN). The switching frequency is a fixed 500 kHz at the pre-charge phase. After the pre-charge phase ends (typical 2.6 ms), The TPS61178x regulates the FB pin to the internal soft-start voltage and results in a gradual rise of the output voltage starting from the input voltage level to the target output voltage. The soft-start time is typical 3.2 ms, which helps the regulator to gradually reach the steady state setting point, thus reducing the start-up stresses and surges.

2

www.ti.com

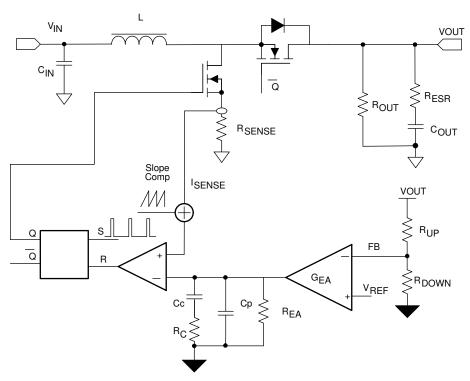

Figure 2. TPS61178x Control Loop of Normal Operation

## 3 Loop Compensation

The loop compensation with the normal control is illustrated in the *Loop Stability and Compensation* section *TPS61178x 20-V, 10-A Fully-Integrated Synchronous Boost with Load Disconnect Control Data Sheet.* The transfer function of the pre-charge phase is different from the one at steady state, including the following:

- Output capacitor

- COUT1, only if the disconnect FET is OFF

- COUT1 and COUT2 if the disconnect is ON (the same as steady state)

- The feedback network

- The gain of the feedback loop is 1.1 x (VOUT / VIN) while the gain is RDOWN / (RDOWN + RUP) at steady state.

There are two different configurations for pre-charge and steady state. If the loop compensation is characterized at normal steady operation, there is an extra step that checks the stability at the pre-charge phase as well. Make sure the loop is stable for both pre-charge and steady state.

To check the stability for the pre-charge phase, set the output voltage to  $1.1 \times VIN$  (the gain of the loop is close to  $1.1 \times Vin$ ), and measure the bode plot to check the stability.

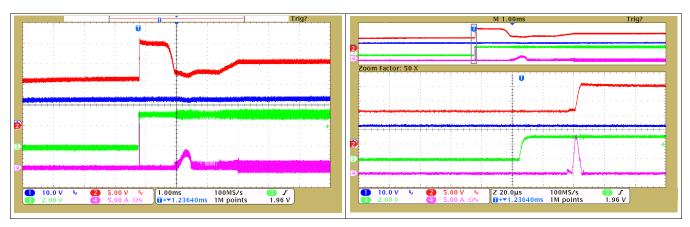

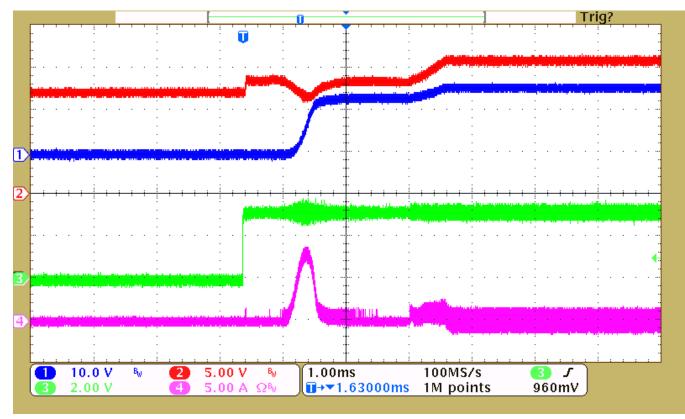

## 4 Initial Inrush Current After EN ON

For the initial cycles after EN is on (within 10  $\mu$ s after EN is on), the output of the operation amplifier is charged to a high voltage, depending on the compensation resistor. With this, the inrush current of the initial cycle is caused by the high comp pin voltage due to the large compensation resistor. The voltage of the comp pin for the initial cycle equals the current times the Rcomp. The on-time of the switching is extended if the comp voltage is high, so the inductor peak current is very high if the on-time is long. The COMP voltage of the output of the error amplifier is Rcomp × Icomp = 2.4 V with 120 k $\Omega$  Rcomp and 20  $\mu$ A sink current. It is suggested that make the comp voltage below 1.25 V to limit the for which the Rcomp = 1.25 / 20  $\mu$ A = 62.5 k $\Omega$ .

3

www.ti.com

Test condition: Vin = 12 V, Vout = 16 V

Test Condition: Cout is  $4 \times 22 \ \mu$ F (two in parallel and two in series) Rc = 39.2 K, Cc = 1.5 nFm, Rg = 120 k, Cg = 10 nF before disconnect FET

CH1 VIN, CH2 VOUT (before the disconnected FET), CH3 EN, CH4 ICOIL

Test condition: Cout before ISO FET is 4 × 22  $\mu$ F (two in parallel and two in series), Rc = 39.2 K, Cc = 1.5 nF, Rg = 39.2 k, Cg = 10 nF

Usually, these loop compensation components are chosen based on the stability in normal operation, but for this device, the components also affect inrush current during start-up. With a lower resistor (from COMP pin to GND), the inrush current of the initial cycles during start-up can be lowered.

## 5 References

4

Texas Instruments, TPS61178x 20-V, 10-A Fully-Integrated Synchronous Boost with Load Disconnect Control Data Sheet

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated