# Minimizing System Down-time with Smart eFuses

Abhinay Patil

# 1 Trademarks

All trademarks are the property of their respective owners.

## 2 Introduction

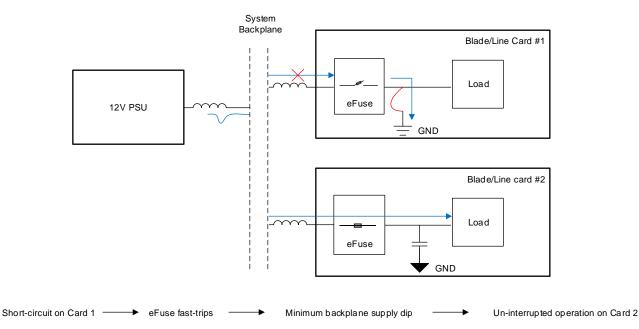

Safety and reliability comes first in most systems and eFuses/Hotswap controllers are often used to provide swift and robust response to power supply faults. An *eFuse* is an integrated power path protection device which is placed between the power source and load to protect the system from various power related fault conditions. Figure 1 shows an example of a typical system where multiple hot-pluggable cards are powered from a common supply backplane.

### Figure 1. eFuse Fast-trip Response to Short-circuit Faults Protects Backplane Power Supply

An eFuse is placed at the input of each card to protect the card from power supply related faults such as overvoltage. At the same time, it protects the backplane supply and connector from excess inrush current drawn by the card during startup or hot-plug. One of the most important protections offered by eFuse is against overcurrent faults on the load side. The eFuse either limits the current or breaks the circuit in case of any faults during steady state which results in excess current draw from the power supply. This prevents the power supply from getting stressed. The most severe form of overcurrent fault occurs during a short-circuit event. In this condition, the eFuse is expected to react swiftly to cut off the power before the current builds up too high, thereby protecting the card from damage and at the same time, preventing the backplane power supply from drooping to a level where the other cards stop functioning properly. The speed of the protection response to short-circuits is considered to be a key figure of merit when selecting an eFuse.

#### Introduction

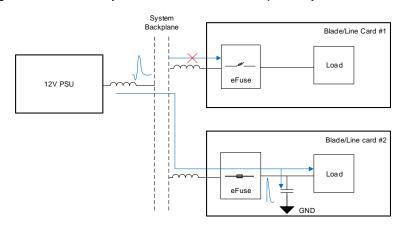

However, certain high-availability systems, such as servers, routers, and switches place a large value on maximizing up-time and un-interrupted operation. Conventional eFuse/Hotswap solutions are prone to nuisance tripping in practical system operating conditions where transient voltages and currents are commonplace. A typical example is large rack-based systems which have multiple high current cards that can be hot-plugged in and out of a common backplane. During a hot-plug event or during fast interruption of power to a card carrying high power, there can be large voltage and current transients experienced by adjacent cards. Also, some of the loads such as fans, processors, ASICs, and so forth, can draw large currents in bursts, exceeding the overcurrent protection limit momentarily. The speed of an eFuse overcurrent protection response during real faults and its sensitivity to transient events go hand-in-hand. A power path protection circuit designed to respond quickly to faults is also overly sensitive to load and line transients and could perform a "false trip" as it cannot distinguish between actual faults and transients. Figure 2 shows the sequence of events in a system where the power to one of the cards is turned off in response to a short-circuit event. The large current built up in the backplane inductance before the fast-trip event causes the backplane supply voltage to spike and induces a large transient current on the adjacent card. The eFuse of the adjacent card treats this as a fault and swiftly reacts to turns off the power to the load, resulting in an unnecessary shutdown or restart of a perfectly functional card.

Hot-unplug or fast-trip on Card #1 carrying large current 🔶 Transient on supply line due to large backplane inductance 🔶 High current injection into Card #2 🔶 False trip on eFuse of Card #2

#### Figure 2. Supply Transients Leading to Unexpected System Shutdown/Restart Due to False Trip of eFuse

To avoid such nuisance tripping, system designers are forced to make a conscious trade-off between protection robustness and transient immunity in their conventional powerpath protection circuits. These systems would benefit from an ideal eFuse solution which exhibits the following attributes.

- The eFuse provides swift response to load fault conditions. In case of soft overload conditions, the eFuse accurately limits the current to prevent any stress on the power supply beyond its rated capability. The current limit response is typically in the order of 10 s of microseconds. In case of severe faults such as short-circuit, the eFuse quickly cuts off the power to the output, thereby preventing damage to the circuits due to excessive current and at the same time, preventing the power supply from drooping excessively or collapsing completely. The fast-trip response is typically in the order of 100 s of nanoseconds.

- 2. The eFuse allows load transients to pass through without tripping. Momentary peak current demands of certain loads such as processors, fans, memory modules, or ASICs, do not trigger the overcurrent response of the eFuse. These peaks can last anywhere between a few microseconds to a few milliseconds but eventually the load current returns to the nominal level. These momentary overcurrent pulses do not pose any threat to the system and do not warrant any response from the eFuse. The eFuse should be capable of passing overcurrent pulses up to a certain threshold for short durations, but at the same time ensures that the eFuse responds only to real and persistent faults.

- 3. The eFuse is immune to input supply line transients. It does not perform false ("nuisance") trips when subjected to transients induced by high current loads switching on the backplane supply.

An eFuse which meets these requirements offers the following system level benefits.

· Ensures uncompromised system safety and reliability

- Isolates any faults from rest of the system

- Minimizes stress on power supply

- Avoids unexpected brown-out conditions

- Facilitates power supply design optimization

- Guarantees maximum system uptime

# 3 System Level Workarounds

Historically, power path protection solutions rely on the following workarounds to deal with transient events:

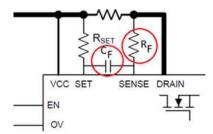

1. Place a low-pass filter on the current sense signal to de-sensitize the protection circuit from transients. This can be implemented on hotswap controllers or eFuses which use an external current sense resistor (Rsense) as shown in Figure 3. The RC time constant of the low-pass filter determines the minimum duration for a peak current pulse to last before it can trigger the overcurrent response of the hotswap controller. This results in short transient current pulses being filtered out of the overcurrent response of the circuit, thereby improving the immunity of the circuit to line and load transient events. On the downside, it increases the overcurrent protection response time in case of actual faults such as overloads or short-circuits. This could have an adverse impact on the system performance and reliability. During a short-circuit fault, the delayed response of the circuit leads to extended stress on the power supply and may cause the supply to droop (depending on the amount of hold-up capacitance). There is also an increased risk of overheating and damage to backplane connector and downstream circuit components.

Figure 3. Low-Pass Filter in Current Sense Circuit

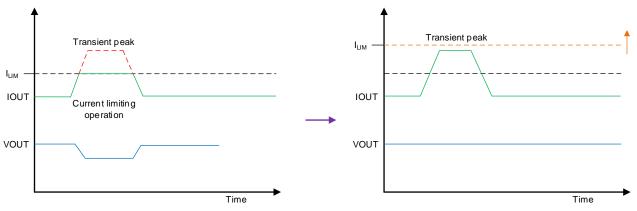

2. Employ a higher DC current limit threshold. The threshold is increased to a level above the highest peak current expected in the system as shown in Figure 4. This ensures that the load transients pass through without triggering the overcurrent response. On the downside, the eFuse now allows higher DC currents to flow in case of actual faults. The power supply size/rating needs to be increased accordingly to handle peak current demand continuously until the current limit takes action. It also leads to higher stress and overheating in the downstream circuits in case of real faults.

# Figure 4. Higher DC Current Limit to Avoid False Trip During Transients

3. Choose a device with a very high fixed fast-trip threshold. The threshold is higher than any transients

expected in the system during normal operation. This ensures that the threshold is exceeded only in case of very severe faults and the fast-trip response is not triggered by transients. On the downside, the fixed fast-trip threshold may be too high as compared to the power supply rating which is optimized for the nominal load current level. This results in a lot of stress on the power supply in case of a real fault, unless the power supply rating is increased accordingly to handle the excess current.

Each of the above mentioned system level workarounds have their pros and cons and the system designer needs to make the right trade-offs in the context of their system.

#### 4 TPS25982 eFuse with Integrated Transient Fault Managament

The Texas Instruments *TPS25982* eFuse integrates a unique combination of features in the device architecture to address this system challenge without any of the aforementioned limitations. These features help system designers to build a power path protection circuit which strikes the right balance between safety and functionality without having to compromise on either.

## 4.1 Adjustable Overcurrent Blanking Timer (ITIMER)

The TPS25982 can be configured to perform a current limit or circuit breaker action once the load current exceeds a certain threshold. The overcurrent threshold is set using a single resistor (RILIM) whose value can be calculated using Equation 1.

$$\mathsf{RILIM}(\Omega) = \frac{1460}{\mathsf{ILIM}(\mathsf{A}) - 0.11}$$

(1)

(2)

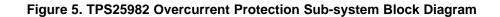

Once the load current exceeds the ILIM threshold, the overcurrent blanking timer is engaged as shown in Figure 5. If the current stays above the ILIM threshold, but lower than the fast-trip threshold (2.1xILIM) for the duration of the ITIMER interval, the gate control circuit is engaged to regulate the current (current limit action) or cut-off the current completely (circuit breaker action) depending on the variant chosen. The ITIMER interval can be set using a single capacitor whose value can be calculated using Equation 2.

tITIMER (ms) =

$$\frac{\text{CITIMER (nF)} \times \Delta \text{VITIMER (V)}}{\text{IITIMER (\muA)}}$$

where

4

•

$$\Delta VITIMER = 0.98 V$$

(typical)

VIN Gate Control ITRIP OCP Ix VIN Control ITRIP Cort Control C

Figure 6 shows a practical scenario where the TPS25982 circuit breaker variant is subjected to two overcurrent events of varying duration. The first event is a transient which lasts shorter than the set ITIMER interval of ~2.2 ms (based on a CITIMER of 4.7 nF) and does not invoke any response from the eFuse. The second event is a persistent overload condition which lasts longer than 2.2 ms and the eFuse performs a circuit breaker action.

Figure 6. Overcurrent Response (Circuit Breaker) After User-defined Blanking Interval

# 4.2 Scalable Fast-trip with Input Supply Transient Detection Logic

During severe output faults such as short-circuit, the current through the eFuse rises very rapidly. The TPS25982 responds to such events by cutting off the power in the fastest possible time. The fast-trip response time is of the order of ~400 ns typically. The fast-trip threshold scales in proportion (2.1x) to the current limit threshold (ILIM) as shown in Figure 5. Both the current limit and fast-trip threshold can be set using a single resistor (RILIM) whose value can be calculated using Equation 3.

$$\mathsf{RILIM}(\Omega) = \frac{1460}{\mathsf{ILIM}(\mathsf{A}) - 0.11}$$

(3)

5

This allows the system designer to set the fast-trip threshold at an appropriate level as per the system current needs and power supply capabilities, rather than use a fixed high threshold which may not be suitable for low current systems. Figure 7 shows the fast-trip response of a TPS25982 whose current limit is set to ~15 A using a RILIM of 100  $\Omega$ . Once the output current exceeds 2.1 x 15 A, the TPS25982 detects a short-circuit condition and performs a fast-trip within 500 ns. This protects the downstream circuit from damage to the excess current and also prevents the input supply from collapsing completely.

Short-circuit event Current exceeds fast trip threshold FET turns off in <500ns PGOOD C10 5.0V/div <sup>в</sup>w:20.0M A' \_\_\_\_\_ \ 7.4V 5.0µs/div 20.0MS/ 50.0ns/pt 5.0V/div Bw:20.0M Normal Preview Single Seq 1 2.0V/div Bw:20.0M 0 acos RL:1.0k a 10.0A/div 1MΩ Bw:20.0M Auto

Figure 7. Fast-trip Response to Output Short-circuit

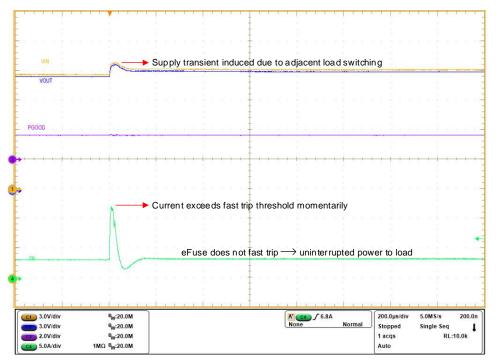

There are certain other system conditions which induce supply line transient currents through the eFuse which can be large enough to trigger the fast-trip response and cause power interruption to the load. However, the TPS25982 uses a proprietary algorithm to detect if the severe overcurrent was triggered by an actual output short-circuit event or an input line transient. This enables the TPS25982 to take swift action in case of an actual short-circuit, but also avoids false tripping in case of a line transient. Here are a couple of examples:

• If there is a step change in the system bus voltage during a switch-over from primary supply to back-up supply, there is a large inrush current spike through the eFuse as the output capacitors get charged up quickly. The TPS25982 does not fast-trip in this condition as shown in Figure 8.

|                                              |                                                                                                  | <ul> <li>Step voltage applied on VIN</li> </ul>                                                          |

|----------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| VIN                                          |                                                                                                  |                                                                                                          |

| VOUT                                         |                                                                                                  |                                                                                                          |

|                                              |                                                                                                  |                                                                                                          |

| PGOOD                                        | <u>a na Na na n</u><br>P                                                                         |                                                                                                          |

| •                                            | 1-1-1-1-1-1-1                                                                                    |                                                                                                          |

| <b>1</b> .                                   |                                                                                                  | Current exceeds fast trip threshold momentarily                                                          |

|                                              | a                                                                                                |                                                                                                          |

|                                              |                                                                                                  |                                                                                                          |

| IIN                                          |                                                                                                  | eFuse does not fast trip $\longrightarrow$ uninterrupted power to load                                   |

| É                                            |                                                                                                  |                                                                                                          |

| 3.0V/div<br>3.0V/div<br>2.0V/div<br>4.00/div | <sup>B</sup> w:20.0M<br><sup>B</sup> w:20.0M<br><sup>B</sup> w:20.0M<br>1MΩ <sup>B</sup> w:20.0M | None ♪ 7.8A<br>None Normal 200.0µs/div 5.0MS/s 200.0n<br>Preview Single Seq ↓<br>0 acqs RL:10.0k<br>Auto |

Figure 8. No Fast-trip in Case of Input Supply Voltage Step

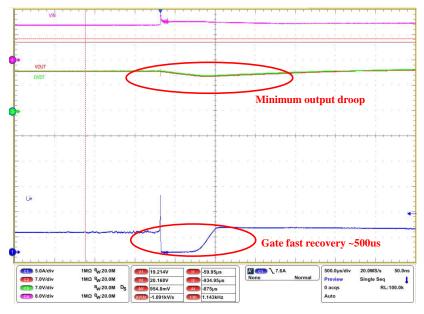

In a system housing multiple cards plugged into a common supply backplane, if one of the cards carrying high current is suddenly hot-plugged out or undergoes a fast trip, the inductive energy built up in the backplane gets discharged through adjacent cards, resulting in a current spike. This current when superimposed on top of the existing steady state load current carried by the eFuse on the adjacent card can easily exceed the fast-trip threshold. The TPS25982 does not fast-trip in this condition as shown in Figure 9.

Figure 9. No Fast-trip in Case of Line Transient Due to Adjacent Load Interruption or Hot Un-plug

### 4.3 Fast Recovery

After a fast-trip event, the TPS25982 attempts to perform a quick recovery to try and restore power to the load as soon as possible. If the fast-trip was the result of an accidental or temporary fault which is immediately cleared, the fast recovery mechanism ensures that the output supply does not droop significantly and the load continues to operate in an un-interrupted manner as shown in Figure 10.

Figure 10. Fast Recovery After Fast-trip

### 5 Conclusion

- Historically, hotswap controller/eFuse-based power path protection solutions that have been primarily

designed for fast response to faults are prone to nuisance tripping during load and line transients.

Transient immunity is usually an afterthought.

- Circuit workarounds are available to improve the transient immunity of these solutions, often at the expense of the protection response time or solution size. System designers need to perform a trade-off between transient immunity and protection robustness.

- eFuse devices that incorporate transient fault management, such as the *TPS25982*, address this key system requirement right at the device architecture level and allow the system designer to build a robust power path protection solution which is also inherently immune to transients.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated