# Application Note Low EMI Design Considerations for TLC6C5748-Q1

Roy Chou, Jin Lin, Gracie Guo, and Michael Yeh

#### ABSTRACT

Local dimming backlight is getting more and more popular in automotive display as it enables higher image contrast. TLC6C5748-Q1 is an LED driver designed for automotive local dimming applications. Due to the system level architecture of local dimming, sometimes there are challenges on EMC performance, including both low EMI and robust EMS. This application note covers several important considerations to achieve good EMC performance with TLC6C5748-Q1. Test results are also provided to prove the effectiveness. All the discussions are based on a demo design for 336 zones panel local dimming backlight module.

# **Table of Contents**

| 1 Introduction                      | 2   |

|-------------------------------------|-----|

| 2 Design Considerations for Low EMI | . 3 |

| 2.1 Design Considerations Overview  |     |

| 2.2 Considerations in Detail        | . 4 |

| 3 Summary                           |     |

| 4 References                        | 12  |

# List of Figures

| Figure 1-1. Typical Local Dimming System                                                                                                     | 2  |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-1. Typical Local Dimming System<br>Figure 2-1. PWM Signal Diagram                                                                   | 4  |

| Figure 2-2. Fourier Series in Frequency Domain                                                                                               | 4  |

| Figure 2-3. Test Results of Original Setup (Vertical Direction) from 45 MHz to 439 MHz                                                       | 5  |

| Figure 2-4. Test Results of Using 3.3 V IO Voltage Setup(Vertical Direction) from 45 MHz to 439 MHz                                          |    |

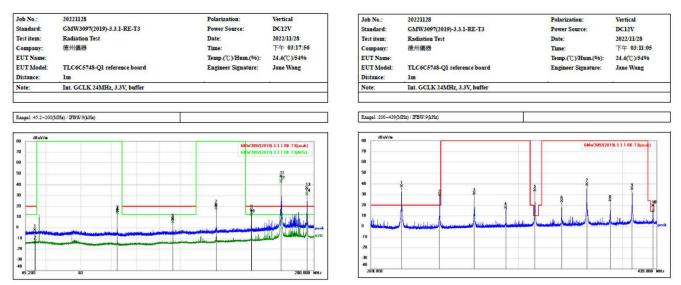

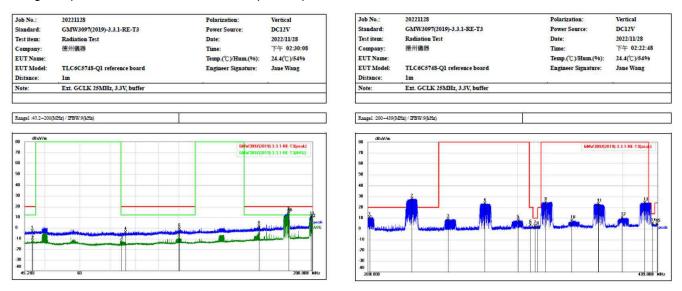

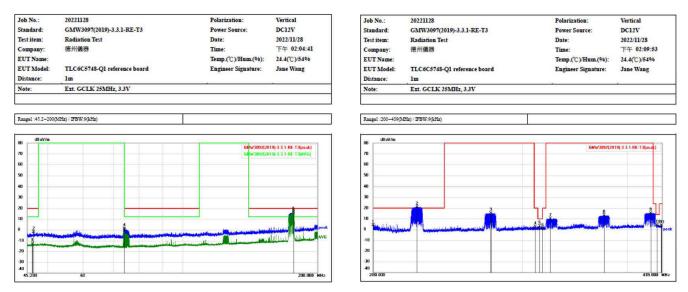

| Figure 2-5. Test Results of Using 3.3 V IO Voltage Setup, GSCLK with SSC and Remove Buffer (Vertical Direction) from 45 MHz to 439 MHz.      | 6  |

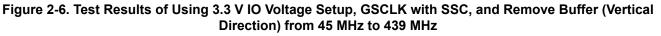

| Figure 2-6. Test Results of Using 3.3 V IO Voltage Setup, GSCLK with SSC, and Remove Buffer (Vertical Direction)<br>from 45 MHz to 439 MHz   | 6  |

| Figure 2-7. Test Results of Using 3.3V IO Voltage Setup, GSCLK with SSC and Add Snubber on GCLK (Vertical<br>Direction) from 45MHz to 439MHz | 7  |

| Figure 2-8. Near Field Test Results of Original Setup from 100kHz to 150kHz                                                                  | 8  |

| Figure 2-9. Near Field Test Results of Optimized Setup from 100kHz to 150kHz                                                                 |    |

| Figure 2-10. Bottom Layer of PCB Layout                                                                                                      | 9  |

| Figure 2-11. Top laver of PCB Lavout                                                                                                         | 9  |

| Figure 2-12. Test Setup                                                                                                                      | 10 |

| Figure 2-13. First TLC6C5748-Q1 GSCLK Waveform                                                                                               | 11 |

| Figure 2-14. Last TLC6C5748-Q1 GSCLK Waveform                                                                                                |    |

# List of Tables

| Table 2-1. Low EMI Design Considerations for TLC6C5748-Q1 | 3  |

|-----------------------------------------------------------|----|

| Table 2-2. Basic Parameters                               | 10 |

# Trademarks

All trademarks are the property of their respective owners.

1

# 1 Introduction

Image contrast has been a limitation for further improvement of automotive LCD displays. Meanwhile, as the display panel size in cars is getting larger and larger, the light leakage from the LCD panel, which makes the black area not true black, could lead to degraded viewing experience, especially when driving in the dark. To solve these problems, the local dimming LCD backlight technology has been introduced to the market. In a local dimming system, a LED matrix is used to replace the LED strings in global dimming LCD backlight. Each LED covers a small backlighting zone. The brightness of each zone can be adjusted independently based on the image content.

Compared with traditional global dimming backlight for LCD panels, the local dimming backlight could significantly improve the image contrast, and also eliminate the LCD light leakage by turning off the backlighting LEDs under the black display area.

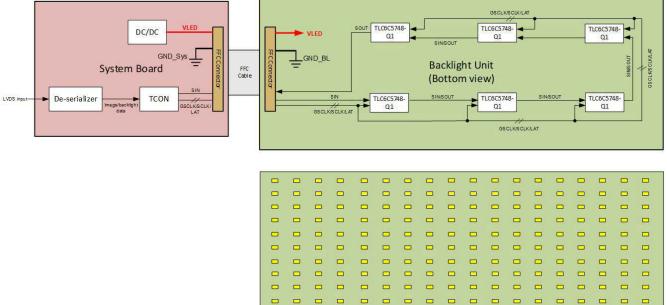

As shown in Figure 1-1, a typical local dimming system consists of a system board and an LED board.

# Figure 1-1. Typical Local Dimming System

The system board usually has a timing-controller (TCON) and some power supply circuits. The TCON accepts the image data stream for display, as well as calculating and outputting the brightness data for each backlight zone. The LED board usually has the LED matrix and the LED drivers. Connections between system board and LED board are off-board using FFC cables.

From EMC design perspective, this architecture results in below challenges,

- High frequency interface with off-board connection,

- High frequency signal routing on two-layer LED board,

Power integrity and signal integrity on LED board.

# 2 Design Considerations for Low EMI

# 2.1 Design Considerations Overview

As the general approach of dealing with EMC problems, the noise source and coupling path (or antenna for radiated emission) need to be identified first.

In a local dimming system, the noise mainly comes from four sources:

- 1. The clock and data signals in the interface. TLC6C5748-Q1 supports up to 25-MHz SCLK/SIN/SOUT frequency, and up to 33MHz GSCLK frequency. These pulses contain high order harmonics that need to be handled carefully.

- 2. The switching noise from dc/dc converters and the PWM dimming. This kind of noise has relatively lower range frequency spectrum but higher energy.

- 3. The LED PWM dimming frequency. Compare to previous two sources, this frequency is around kHz level. The calculation formula of the frequency about TLC6C5748-Q1 is shown in Equation 1

- 4. The impedance of the board interconnections, such as the parasitic inductance of the connector metal contacts, can result in a high frequency AC voltage source when the signal current pass through

$$f_{LED} = \frac{GSCLK}{2^{16}}$$

(1)

In many local dimming designs, the LED board is large size two-layer PCB. The routing on LED board can be quite complex and not able to maintain a good "return path" for the traces carrying high frequency signals. This results in an enlarged high di/dt loop area, which contributes to the radiated emission. The long traces carrying high frequency signals can also be equivalent antenna.

The low EMI design considerations for TLC6C5748-Q1 are summarized in Table 2-1.

| Item                                                                                                                   | Methods                                                                                                                            | Purpose                                        |  |  |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|

| Top-level architecture                                                                                                 | Shield cable or connector; minimized PCB numbers; minimize cable length.                                                           | Reduce high frequency noise and antenna        |  |  |

| High-frequency signals                                                                                                 | Use 3.3V I/O voltage.                                                                                                              | Decrease or attenuate high<br>frequency energy |  |  |

|                                                                                                                        | Select <i>just enough</i> interface frequency to reduce harmonic energy in high frequency range.                                   |                                                |  |  |

|                                                                                                                        | Decrease the driving strength of the data and clock signals;<br>Add R-C filter or ferrite beads to smooth the rising/falling edge. |                                                |  |  |

|                                                                                                                        | Spread spectrum                                                                                                                    | Suppress the peak in spectrum                  |  |  |

|                                                                                                                        | Optimization on GSCLK                                                                                                              | Decrease or attenuate high<br>frequency energy |  |  |

| PCB layout Provide low impedance return path for high frequency signals; along the high frequency signal routing, etc. |                                                                                                                                    | Reduce high frequency noise and antenna        |  |  |

#### Table 2-1. Low EMI Design Considerations for TLC6C5748-Q1

# 2.2 Considerations in Detail

#### 2.2.1 Top-Level Architecture

In most cases, a local dimming system consists of at least two PCB boards, one is the system board and the other is LED board for backlight. Some designs even have more PCB counts. This architecture could lead to long cables (mostly FPC or FFC) and multiple connector contacts, which introduces relatively high parasitic inductance along the signal path. When the driving current of the high frequency communication signals flowing through, the parasitic inductance could be equalized as an AC noise source. This is one of the dominant reasons of excessive radiated emission.

Minimized PCB counts and connector counts should be considered during the top-level architecture floor planning. Besides, cables and connectors with shield are also recommended to decrease the radiated emission.

#### 2.2.2 High Frequency Signals

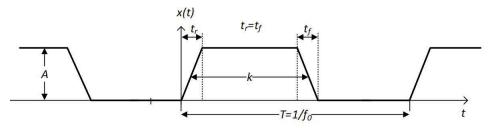

As discussed in previous sections, the pulse signals on the interface could be a noise source of EMI. Theoretically, a PWM signal with limited slew rate (shown as Figure 2-1) could be written into Fourier series format as,

Figure 2-1. PWM Signal Diagram

$$x(t) = A\frac{k}{T} + 2A\frac{k}{T} \sum_{n=1}^{\infty} \left( \frac{\sin(n\pi f_0 k)}{n\pi f_0 k} + \frac{\sin(n\pi f_0 t_r)}{n\pi f_0 t_r} \right) \cos[2\pi n f_0 t - \pi n f_0 (k - t_r)\theta]$$

(2)

To mitigate the EMI problem from noise source, E.Q 2 indicates several approaches to lower the energy in high frequency range. Figure 2-2 shows the spectrum in frequency domain.

Figure 2-2. Fourier Series in Frequency Domain

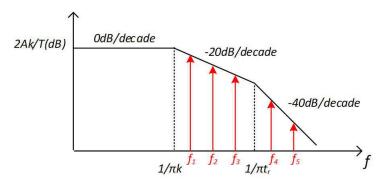

# 2.2.2.1 Original Setup

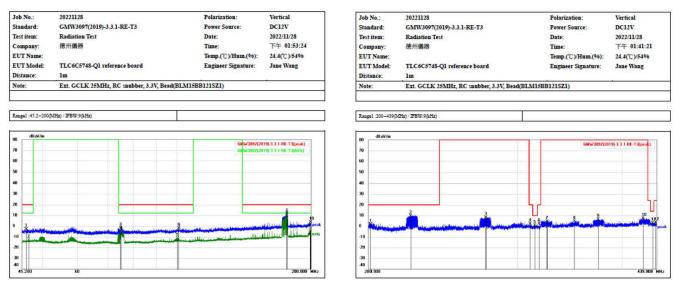

Without using any EMC countermeasures, board design usually uses micro-controller to provide the TLC6C5748-Q1 desired signal, 5 V I/O voltage level and used buffer without RC snubber. Figure 2-3 shows above setups test results in vertical direction from 45 MHz to 400 MHz with GMW3097 specification. In following test, we will measure the same frequency band to do the comparison

#### Figure 2-3. Test Results of Original Setup (Vertical Direction) from 45 MHz to 439 MHz

#### 2.2.2.2 3.3 V I/O Voltage Instead of 5 V

Although TLC6C5748-Q1 is compatible with either 3.3 V or 5 V I/O voltage on the interface (LAT, SIN, SCLK, GSCLK), 3.3V I/O voltage leads to lower energy in full frequency range. Figure 2-4 shows the 3.3 V I/O test results.

Figure 2-4. Test Results of Using 3.3 V IO Voltage Setup(Vertical Direction) from 45 MHz to 439 MHz

#### 2.2.2.3 Use Independent OSC for GSCLK With Spread Spectrum

Figure 2-4 shows the high EMI noise peak generating from GSCLK. To avoid EMI noise peak, using spectrum independent OSC is the common method. Generally, micro-controller can generate the spread spectrum clock signal, but comparing with oscillator, it has high EMI noise commonly. Using The independent OSC can be placed nearest close to the first LED driver which means lower shorter signal path. Figure 2-5 shows test results using independent OSC for GSCLK with spread spectrum.

# Figure 2-5. Test Results of Using 3.3 V IO Voltage Setup, GSCLK with SSC and Remove Buffer (Vertical Direction) from 45 MHz to 439 MHz

#### 2.2.2.4 Without Using Buffer on GSCLK

Although using OSC which has spread spectrum function to be GSCLK can largely reduce the EMI noise, it is still over specification in some frequency band. Lowering the GSCLK energy is the way to reduce the EMI. Common ways to reduce EMI energy are without using buffer on the premise that the system operate normally and signal waveform meet specification and leave enough margin. Figure 2-6 shows test results without using buffer for GSCLK.

(3)

7

# 2.2.2.5 Using Snubber on GSCLK

In the basis of previous section, Figure 2-7 shows test results adding snubber on GSCLK.

Figure 2-7. Test Results of Using 3.3V IO Voltage Setup, GSCLK with SSC and Add Snubber on GCLK (Vertical Direction) from 45MHz to 439MHz

#### 2.2.2.6 Lower the Signal Frequency

In particular with TLC6C5748-Q1, the data throughput of the local dimming SPI interface (SIN, SCLK) is calculated in Equation 3. For example, a 336-zone design with 60 Hz frame rate requires about 0.32 MHz SCLK/SIN. TLC6C5748-Q1 only updates the brightness when the LAT pulse arrives, thus the whole frame period could be used for brightness data transfer.

$$Data rate = Deive counts \times 769 bit \times frame rate$$

Besides, GSCLK is an independent clock for PWM dimming counter. In some applications, high PWM (for example, >20 kHz) dimming frequency is needed to avoid audible noise and moiré pattern. On TLC6C5748-Q1, the control bit of ESPWM is recommended to be set when high PWM dimming frequency is required. With ESPWM enabled, the relationship between PWM dimming frequency and GSCLK is given as shown in Equation 4.

$$f_{LED} = \frac{GSCLK}{2^{16}} \times 128\tag{4}$$

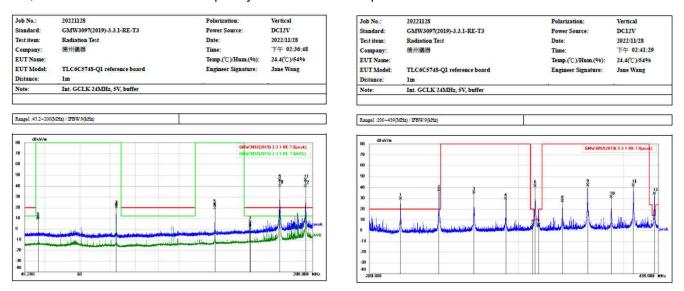

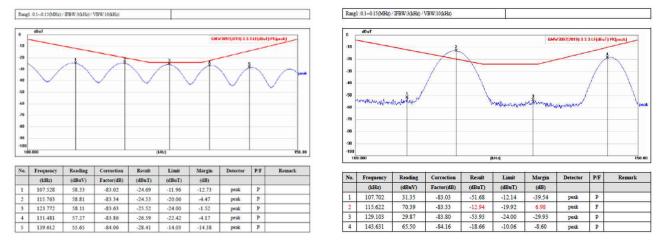

For example, to achieve a PWM dimming frequency over 20 kHz, it requires 10.24 MHz GSCLK frequency in minimum. Some OEMs may have limitations for near-field magnetic field emission in specific low frequency band. In most cases, such kind of low frequency magnetic radiated emission directly sourced from the current loop during PWM dimming operation. The radiated spikes on the frequency spectrum is directly related to the GSCLK frequency because the PWM dimming frequency is divided from GSCLK. Thus, it's also important to select the GSCLK frequency carefully to avoid the spikes locates at the sensitive band. For audible noise, in addition to boost the PWM dimming frequency, we can use Tantalum - Polymer capacitors. Compared with MLCC (Mount Multilayer Ceramic Capacitors), the Tantalum - Polymer capacitors will not have vibration noise. And the common method to pass the near-field magnetic field emission is lowering down the GSCLK. For example, GMW3097 specification has limitation of near-field magnetic field emission in 100 kHz to 150 kHz. According to Equation 4, PWM dimming frequency is 7.8 kHz and 48.8 kHz when GSCLK is 4 MHz and 14.3 MHz. Lower frequency of the signals, the lower amplitude in the high frequency range as shown in Figure 2-8.

Figure 2-8. Near Field Test Results of Original Setup from 100kHz to 150kHz

According to Equation 4, to design an appropriate LED dimming frequency is also a good way to pass the specification. For example, 50 kHz LED dimming frequency is appropriate because it has EMI noise peak on 50 kHz, 100 kHz, 150 kHz and so on which means that it can avoid the tight limitation on 100 kHz to 150 kHz. Figure 2-9 shows the near field test result when GSCLK is 25 MHz and turn on the ESPWM. In addition, spread the regulated capacitors over the LED board can also reduce the EMI noise from LED dimming frequency.

| No. | Frequency | Reading | Correction | Result     | Limit  | Margin | Detector | P/F | Remark |

|-----|-----------|---------|------------|------------|--------|--------|----------|-----|--------|

|     |           | (kHz)   | (dBuV)     | Factor(dB) | (dBuT) | (dBuT) | (dB)     |     |        |

| 1   | 100.406   | 55.81   | -82.73     | -26.92     | -4.44  | -22.48 | peak     | р   |        |

| 2   | 113.210   | 30.34   | -83.24     | -52.90     | -17.61 | -35.29 | peak     | р   |        |

| 3   | 122.028   | 30.57   | -83.57     | -53.00     | -24.00 | -29.00 | peak     | P   |        |

| 4   | 136.699   | 27.23   | -83.99     | -56.76     | -16.98 | -39.78 | peak     | P   |        |

| 5   | 146.158   | 66.10   | -84.22     | -18.12     | -7.63  | -10.49 | peak     | P   |        |

| _   |           |         |            |            |        |        |          | -   |        |

Figure 2-9. Near Field Test Results of Optimized Setup from 100kHz to 150kHz

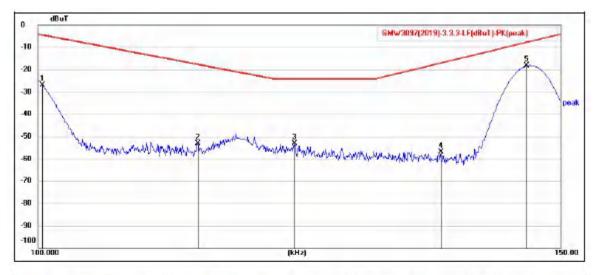

#### 2.2.2.7 Placement and PCB layout

As shared previously, R-C or FB-C filters can be used to dump the high frequency harmonics. The recommendation is to place the R-C filters on the system board. Another filter on LED board is also recommended to have more attenuation, and the filter needs to be placed as close as possible to the connectors.

Besides the general PCB layout guidelines on TLC6C5748-Q1, it is also important to provide a low impedance return path for the signal traces. An integrated and continuous GND plane might not be easy for 2-layer PCB board, but it needs to be done as much as possible. For the signal traces, GSCLK, SIN, SCLK should be placed on the bottom layer only. It's better not to use vias on these traces. While the signal traces are parallel, evenly spaced vias need to be put between them to have the GND plane integrated.

Figure 2-10 shows the reference layout bottom layer (blue) and top layer (red).

Figure 2-10. Bottom Layer of PCB Layout

| الصفاعا بالجراب المارك بالمتراب المتراج |

|-----------------------------------------------------------------------------------------------------------------|

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

| المراجع المحصص مرجع بتعليك فيتعلم متعادي المحاد والمتعاد والمحاد والمحاد والمحاد والمحاد والمحاد والمحاد والمحا |

|                                                                                                                 |

|                                                                                                                 |

| ا سن ا صر به بر بور به بر بور به بر به بر به بر به                          |

|                                                                                                                 |

|                                                                                                                 |

| and the feat the test the test test test test test                                                              |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

|                                                                                                                 |

| الله المرتجر بحريف المراجر بحريك المرتف المرتجر بحريك المرتب                                                    |

|                                                                                                                 |

Figure 2-11. Top layer of PCB Layout

#### 2.2.2.8 ESD Enhancement

System level ESD is another critical topic in EMC specification. The possible paths affect the LED commonly from three paths, LED voltage, LED driver Vcc voltage and GND. To select appropriate ESD place on LED voltage rail and LED driver Vcc voltage rail is the good way to pass the system-level ESD. For LED voltage rail, the suggestion is TPD1E10B09-Q1 (9V, VBR) and for LED driver Vcc (3.5V, VBR), the suggestion is TPD1E01B04-Q1. For more detailed information, please see the reference board circuit.

#### 2.2.2.9 Demo and Test Results

A demo has been designed and tested to prove the information shared in Section 2. The test setup is shown as Figure 2-12.

Figure 2-12. Test Setup

There are two PCB boards in this demo. The system board has an MCU to generate and send out the backlighting data. Also integrated is a TPS552882-Q1 as the buck-boost converter for LED board power supply. The LED board has 336 pcs LEDs. Each zone has 1 pcs LED.

Table 2-2 lists some basic parameters of the demo.

| Parameter             | Value          |  |  |  |

|-----------------------|----------------|--|--|--|

| Panel size            | 12.3 inch      |  |  |  |

| Zone                  | 320            |  |  |  |

| LED configuration     | 1 pcs per zone |  |  |  |

| Typical LED current   | 15 mA          |  |  |  |

| Maxim backlight power | 30 W           |  |  |  |

| VLED supply voltage   | 6 V            |  |  |  |

#### Table 2-2. Basic Parameters

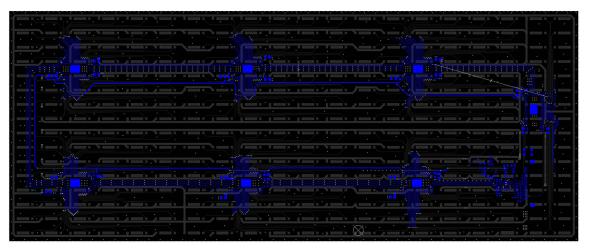

#### 2.2.2.10 Bench Test Results

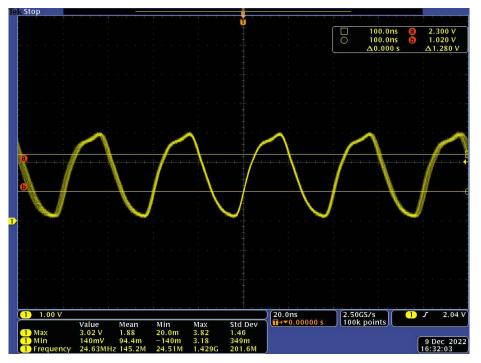

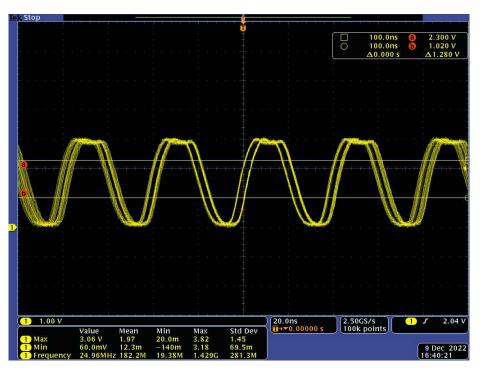

After adding countermeasures, checking if the signal integrity is essential, especially GSCLK. Sometimes, GSCLK waveform was affected when adding snubber. Per the data sheet, it should be checked whether GSCLK meet the chip criteria *high/low pulse larger than 10us*. For the TLC6C5748-Q1 structure, checking first TLC6C5748-Q1 and last TLC6C5748-Q1 GSCLK pin to confirm whether meeting the data sheet.

Figure 2-13. First TLC6C5748-Q1 GSCLK Waveform

Figure 2-14. Last TLC6C5748-Q1 GSCLK Waveform

# 3 Summary

This application note describes how to lower the EMI noise on local dimming LED driver circuit board. The process begins with the identification of the EMI noise source. By adding the snubber, external oscillator, and adjusting I/O voltage level can better the ECMI performance. Lastly, after doing all the countermeasures, please double check the signal waveform to meet the data sheet requirements.

# **4** References

• Texas Instruments, *TLC6C5748-Q1 48-Channel, 16-bit, PWM LED Driver with Internal Current Settings*, data sheet.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated