# Application Note Analysis and Improvement of Using Boost Converter to Generate the Negative and Positive Voltage Rails

Roy Chou and Lei Zhong

### ABSTRACT

Many TFT-LCD panels require negative voltage rail and positive voltage rail to power the amplifiers from the 12-V or 5-V power supply. *Generating Negative and Positive Voltage Rail With Boost Converter TLV61048*, application note used TLV61048 device and referred to *Design for a Discrete Charge Pump*, application note to demonstrate an example to generate the negative voltage rail and positive voltage rail. For asynchronous boot converter, the forward diode can help reduce the gap between positive voltage rail and negative voltage rail and for synchronous boost converter, due to MOSFET integration, the forward voltage drop is very low, but it also can use a diode to minimize the gap. But the diode cannot effectively reduce the voltage gap through the full load current range. This application note demonstrates using the resistor to effectively reduce the gap. The application can also design a calculator to simplify the design procedure. The components based on the asynchronous boost converter using the Boost Converter± Quick Calculator available for download from the TPS61377 product folder. Last, the document shows an example using TPS61377 and shows the precaution for the schematic design and layout design.

# **Table of Contents**

| 1 Introduction                                                                 | 2 |

|--------------------------------------------------------------------------------|---|

| 2 Analysis of Dual Polarity Voltage Rails Design With Boost Converter          |   |

| 2.1 Analysis of Factors Affecting Negative Voltage Rail                        |   |

| 2.2 Improvement of Gap Between Negative Voltage Rail and Positive Voltage Rail | 2 |

| 3 Boost Converter ± Quick Calculator Design                                    | 4 |

| 4 Demo and Test                                                                |   |

| 4.1 Simulation Results                                                         | 5 |

| 4.2 Demo Board Example                                                         | 6 |

| 5 Summary                                                                      |   |

| 6 References                                                                   |   |

|                                                                                |   |

# Trademarks

All trademarks are the property of their respective owners.

# **1** Introduction

Section 2 analyzes the original design from Generating Negative and Positive Voltage Rail With Boost Converter TLV61048 and then using the formula to describe main side effect. To reduce the side effect, the section also provides a design. Section 3 uses *Boost Converter*± *Quick Calculator* to design a circuit in specific condition. Section 4 demonstrates the schematic example and layout example for the application.

# 2 Analysis of Dual Polarity Voltage Rails Design With Boost Converter

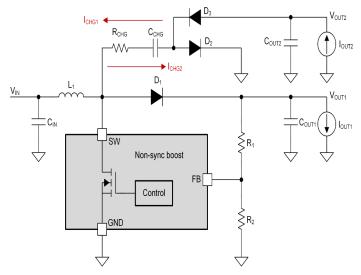

Figure 2-1 shows the typical circuit of dual polarity voltage rails design with asynchronous boost converter. The image uses the RCHG, CCHG, D2 and D3 to achieve the negative voltage rail.

# Figure 2-1. Typical Circuit of Dual Polarity Voltage Rails Design With Asynchronous Boost Converter

# 2.1 Analysis of Factors Affecting Negative Voltage Rail

Negative voltage rail DC voltage can be estimated through Equation 1. The negative voltage rail can have a gap comparing with positive voltage rail. Main factors causing negative voltage gap are RCHG and forward voltage of D2 and D3.

$$-V_{OUT2} = (V_{OUT1} + V_{D1}) - (I_{CHG1} + I_{CHG2}) \times R_{CHG} - V_{D2} - V_{D3}$$

(1)

$$I_{CHG1} = \frac{1}{D} \times I_{OUT2}$$

(2)

$$I_{CHG2} = \frac{1}{1-D} \times I_{OUT2}$$

(3)

But forward voltage of D1 helps the voltage gap. Normally, selecting higher forward voltage of D1 to cover the gap is the common method and the higher forward voltage can help the gap in full load, but in light load condition, the higher forward voltage can generate the extra voltage on the negative voltage rail if we select higher forward voltage of D1.

Negative voltage drop =

$$\frac{1}{D(1-D)} \times I_{OUT2} \times R_{CHG} + V_{D2} + V_{D3} - V_{D1}$$

(4)

# 2.2 Improvement of Gap Between Negative Voltage Rail and Positive Voltage Rail

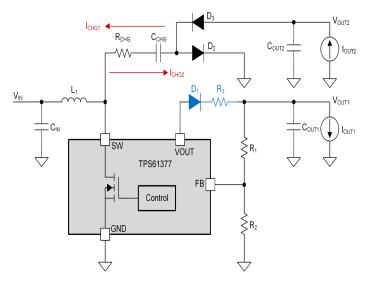

Figure 2-2 shows the improvement. To select appropriate R3 and forward voltage of D1 can improve the gap. The negative voltage rail formula can be edited as Equation 5. For best practice have the design meet Equation 6 to reduce the gap. To reduce the gap in full load current range, the commendation is to design to eliminate the forward voltage drop. And can simplify the Equation 7 to Equation 8.

\_

$$V_{OUT2} = \left(V_{OUT1} + V_{D1} + \frac{I_{OUT1}}{1 - D} \times R_3\right) - (I_{CHG1} + I_{CHG2}) \times R_{CHG} - V_{D2} - V_{D3}$$

(5)

$$V_{D1} + \frac{I_{OUT1}}{1 - D} \times R_3 = \frac{1}{D(1 - D)} \times I_{OUT2} \times R_{CHG} + V_{D2} + V_{D3}$$

(6)

$$I_{OUT1} \times R_3 = \frac{1}{D} \times I_{OUT2} \times R_{CHG}$$

(7)

$$R_3 = \frac{1}{D} \times R_{CHG} \times \frac{I_{OUT2}}{I_{OUT1}}$$

(8)

Figure 2-2. Improvement of Voltage Gap Between Negative Voltage Rail and Positive Voltage Rail

# 3 Boost Converter ± Quick Calculator Design

Table 3-1 shows the example of the test condition.

Table 3-1. Test Condition Example

| Test condition |         |  |

|----------------|---------|--|

| Input voltage  | 12V     |  |

| Output voltage | ± 19V   |  |

| Output load    | ± 100mA |  |

And the application note uses TPS61377 to achieve the design. The switching frequency is 650kHz. Table 3-2 shows the preliminary results.

| I/O condition     |         |      |                                                   |

|-------------------|---------|------|---------------------------------------------------|

| System Parameters | Value   | Unit | Remark                                            |

| Vin(typ)          | 12      | V    | Typical input voltage                             |

| VOUT1             | 19      | V    | Positive power rail voltage                       |

| VOUT2             | -19     | V    | Negative power rail voltage                       |

| Fsw               | 650     | kHz  | Switching frequency                               |

| IOUT1             | 0.1     | A    | Load current of positive voltage rail             |

| IOUT2             | 0.1     | A    | Load current of negative voltage rail             |

| Efficiency        | 90      | %    | Estimated value, used 90% as default              |

| Ripple of VCOUT2  | 0.19    | V    | 1% of VOUT                                        |

| CCHG              | 0.81    | μF   | Recommended CCHG that achieve desired Vout ripple |

| RCHG              | 0.32733 | Ω    | Recommended RCHG, by using Ts = RCHG × CCHG       |

Table 3-2. I/O Condition in Boost Converter ± Quick Calculator Design

Table 3-3 shows the components selection. The forward voltage of D2 and D3 are better to select the smaller to minimize the power loss of the architecture. In the previous section, the recommendation is to forward voltage of D1 and R3. For the power loss of R3 needs be carefully designed.

#### Table 3-3. Components Selection in Boost Converter ± Quick Calculator Design

|                   | Components selection |      |                                                                                 |

|-------------------|----------------------|------|---------------------------------------------------------------------------------|

| System Parameters | Value                | Unit | Remark                                                                          |

| CCHG              | 4.70                 | μF   | Real CCHG, suggest > recommended value for derating                             |

| RCHG              | 1                    | Ω    | Real RCHG, suggest >= $1\Omega \&$<br>recommended value, use $1\Omega$ as first |

| VD2               | 0.35                 | V    | Real forward voltage of VD2, smaller is good                                    |

| VD3               | 0.35                 | V    | Real forward voltage of VD3, smaller is good                                    |

| VD1               | 0.7                  | V    | Recommended forward voltage of VD1=VD2+VD3                                      |

| VD1               | 0.7                  | V    | Real forward voltage of VD1                                                     |

| R3                | 2.32                 | Ω    | Recommended R3 by using real VD1                                                |

| R3                | 2.32                 | Ω    | Real VD1 resistor                                                               |

| PR3               | 0.0408               | W    | Average power of R3                                                             |

Table 3-4 shows the calculation result after inputting the I/O condition and Component selection. Original gap means that the architecture without using R3 and D1. After R3, the gap can be effectively reduced.

|                    | Calculation result |      |                                 |

|--------------------|--------------------|------|---------------------------------|

| System Parameters  | Value              | Unit | Remark                          |

| D                  | 0.43               |      | Duty cycle of boost converter   |

| Ts                 | 1.54               | μs   | Duty time                       |

| Ton                | 0.66               | μs   | Duty on time                    |

| ICHG1              | 0.23               | A    | Averaged ICHG1                  |

| ICHG2              | 0.18               | A    | Averaged ICHG2                  |

| ΔVCHG              | 0.033              | V    | Ripple of the CCHG              |

| VCHG               | 19.17              | V    | DC voltage of the CCHG          |

| Original -VCOUT2   | 18.59              | V    | Original negative voltage rail  |

| Original Gap       | 0.41               | V    | Original gap                    |

| Output capacitance | 0.4603             | μF   | Cout need for VOUT1             |

| Optimized -VCOUT2  | 19.0005            | V    | Optimized negative voltage rail |

| PRCHG              | 0.0408             | W    | Power of RCHG                   |

| Optimized Gap      | -0.0005            | V    | Optimized gap                   |

#### Table 3-4. Calculation Result in Boost Converter ± Quick Calculator Design

# 4 Demo and Test

### 4.1 Simulation Results

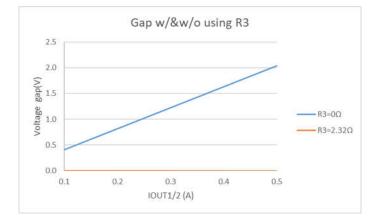

Simulation uses the Table 4-1 test parameters to analyze the function of R3 in Figure 4-1.

#### **Table 4-1. Test Parameters**

| Test parameters |         |  |

|-----------------|---------|--|

| Input voltage   | 12V     |  |

| Output voltage  | ± 19V   |  |

| Output load     | ± 500mA |  |

Table 4-2 shows the gap between with using R3 and without using R3. R3 can effectively eliminate the DC offset using the architecture.

| IOUT1/2 (A) | R3=2.32ohm, Gap(V) | R3 = 0ohm, Gap(V) |

|-------------|--------------------|-------------------|

| 0           | 0.0000             | 0.0000            |

| 0.1         | -0.0005            | 0.41              |

| 0.2         | -0.0010            | 0.82              |

| 0.3         | -0.0015            | 1.22              |

| 0.4         | -0.0021            | 1.63              |

| 0.5         | -0.0024            | 2.04              |

#### Table 4-2. Gap With and Without Using R3

Figure 4-1. Gap With and Without Using R3

# 4.2 Demo Board Example

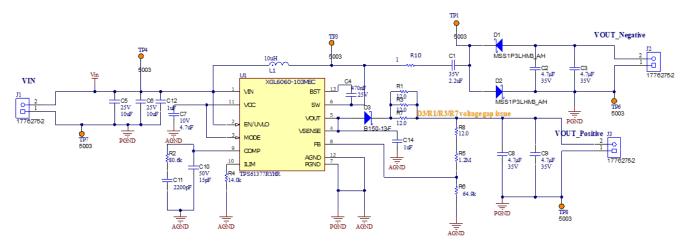

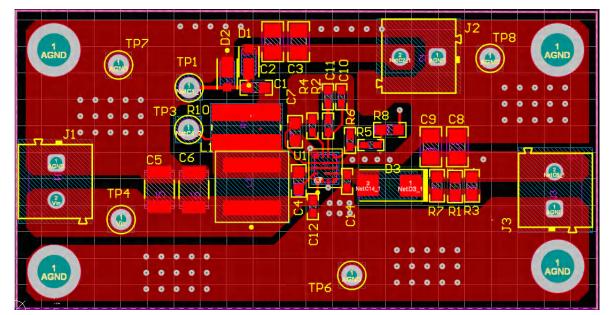

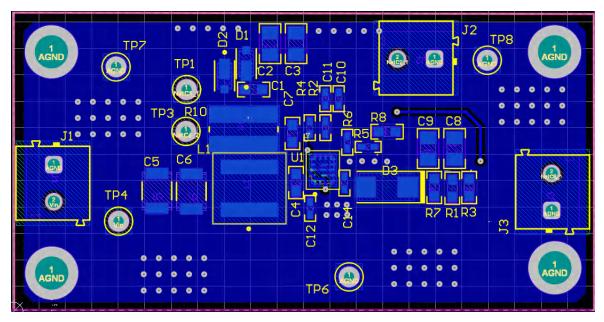

Figure 4-2, Figure 4-3, and Figure 4-4 demonstrate a schematic and two-layered layout example using TPS61377 to achieve Table 4-1 requirements. To minimize the output power loop, the recommendation is to add 1µF capacitor on VOUT pin to GND like C14 showing in the schematic.

Figure 4-2. TPS61377 Schematic

Figure 4-3. TPS61377 Layout (Top)

Figure 4-4. TPS61377 Layout (Bottom)

# 5 Summary

This application note shows the method to eliminate the DC offset issuing using charge pump circuit with traditional boost converter. But the method is not recommended to use in high power rating application because the method needs to select high power rating charge resistor and the method can cause higher power loss, cost, and size. The Boost Converter ± Quick Calculator can be used to evaluate the resistors power rating need to do further design and complete assessment in advance.

# 6 References

- Texas Instruments, *Design for a Discrete Charge Pump*, application note.

- Texas Instruments, Generating Negative and Positive Voltage Rail With Boost Converter TLV61048, application note.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated