# TPS65094x Design Guide

This document is meant to be used as a guide for designers to ensure the proper design of the TPS65094x PMIC. The TPS65094x is an analog chip containing several power resources which each have different constraints when creating the schematic and layout. The purpose of this guide is to provide a better understanding for these constraints and, through example, give an explanation of how proper layout can be done. The guide is intended to be used with the TPS65094xSchematic Checklist, Layout Checklist, and ILIM Calculator tool (SLVA735).

#### **Contents**

| 1  | Device Description – TPS65094x               | 1  |  |  |  |  |  |  |

|----|----------------------------------------------|----|--|--|--|--|--|--|

| 2  | Schematic Guidelines                         | 2  |  |  |  |  |  |  |

|    | 2.1 Controller Design Procedure              | 2  |  |  |  |  |  |  |

|    | 2.2 Converter Design Procedure               | 5  |  |  |  |  |  |  |

|    | 2.3 LDO Design Procedure                     |    |  |  |  |  |  |  |

| 3  | Layout Guidelines                            |    |  |  |  |  |  |  |

|    | 3.1 PCB Build Up                             |    |  |  |  |  |  |  |

|    | 3.2 External Components Choice               |    |  |  |  |  |  |  |

|    | 3.3 PCB General Layout Check List            | 14 |  |  |  |  |  |  |

|    | List of Figures                              |    |  |  |  |  |  |  |

| 1  | PMIC Functional Block Diagram                | 9  |  |  |  |  |  |  |

| 2  | Controller Diagram                           |    |  |  |  |  |  |  |

|    |                                              |    |  |  |  |  |  |  |

| 3  | Converter Diagram                            |    |  |  |  |  |  |  |

| 4  | EVM Board Stackup                            |    |  |  |  |  |  |  |

| 5  | Device Package and Pin Locations             |    |  |  |  |  |  |  |

| 6  | Example of Poor Ground Loop                  | 10 |  |  |  |  |  |  |

| 7  | Example of Improved Ground Loop              | 10 |  |  |  |  |  |  |

| 8  | Frequency and Current Impact on Ground Plane |    |  |  |  |  |  |  |

| 9  | EVM Overall Layout                           | 14 |  |  |  |  |  |  |

| 10 | Schematic Example of Controller Layout       | 15 |  |  |  |  |  |  |

| 11 | EVM Layout of Controllers                    | 16 |  |  |  |  |  |  |

| 12 | Schematic Example of Converter Layout        | 16 |  |  |  |  |  |  |

| 13 | Example Converter Routing                    | 17 |  |  |  |  |  |  |

| 14 | V <sub>RFF</sub> Layout                      | 18 |  |  |  |  |  |  |

### 1 Device Description – TPS65094x

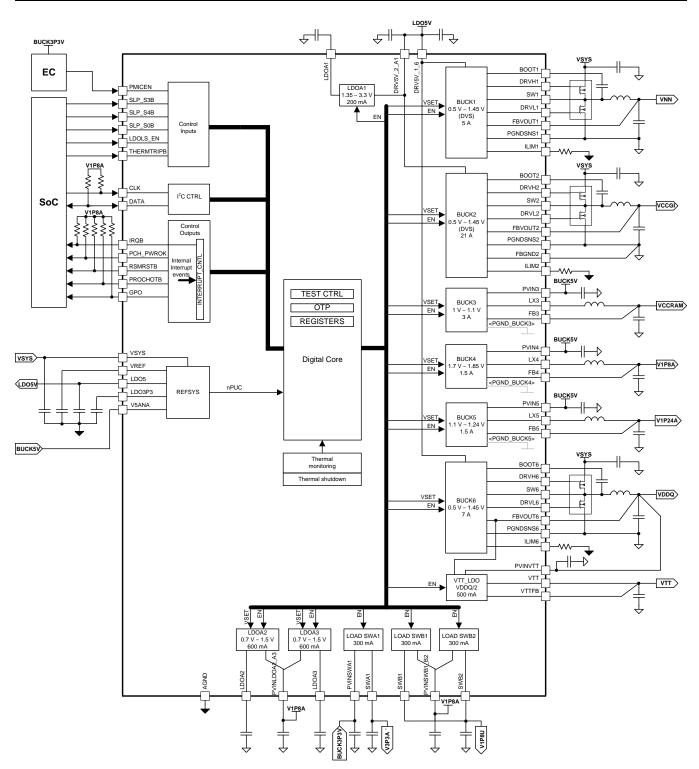

The TPS65094x is a single-chip solution power-management IC designed specifically for the Intel Apollo Lake SoC targeted for tablets, ultrabooks, and notebooks with NVDC or non-NVDC power architectures, using 2S, 3S, or 4S Li-lon battery packs. The device features 3 controllers and 3 converters for high power, high efficiency rails. A sink/source LDO (VTT), 3 LDO's and 3 load switches are controlled by power-up sequence logic to provide the proper power rails, sequencing, and protection. An I<sup>2</sup>C interface allows simple control either by an embedded controller (EC) or by a SoC. The PMIC comes in an 8 × 8 single-row QFN package with thermal pad for good thermal dissipation and ease-of-board routing.

Schematic Guidelines www.ti.com

Figure 1. PMIC Functional Block Diagram

### 2 Schematic Guidelines

### 2.1 Controller Design Procedure

Designing the controller can be broken down into the following steps:

www.ti.com Schematic Guidelines

- 1. Design the output filter

- 2. Select the FETs

- 3. Select the bootstrap capacitor

- 4. Select the input capacitors

- 5. Set the current limits

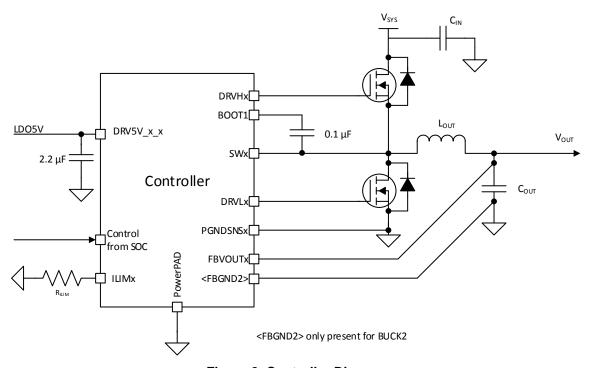

Controllers BUCK1, BUCK2, and BUCK6 require a 5-V supply and capacitors at their corresponding DRV\_x\_x pins. For most applications, the DRV\_x\_x input should come from the LDO5P0 pin to ensure uninterrupted supply voltage; a 2.2 µF, X5R, 20%, 10-V, or similar capacitor must be used for decoupling.

Figure 2. Controller Diagram

#### 2.1.1 Selecting the Inductor

Placement of an inductor is required between the external FETs and the output capacitors. Together, the inductor and output capacitors make the double-pole that contributes to stability. In addition, the inductor is directly responsible for the output ripple, efficiency, and transient performance. As the inductance used increases the ripple current decreases, which typically results in an increased efficiency. However, with an increase in inductance used, the transient performance decreases. Finally, the inductor selected must be rated for appropriate saturation current, core losses, and DC resistance (DCR).

Equation 1 shows the calculation for the recommended inductance for the controller.

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times Iout_{MAX} \times K_{IND}}$$

#### where

- V<sub>OUT</sub> is the typical output voltage

- V<sub>IN</sub> is the typical input voltage

- f<sub>sw</sub> is the typical switching frequency

- lout<sub>MAX</sub> is the maximum load current

- K<sub>IND</sub> is the ratio of I<sub>Lripple</sub> to the I<sub>out(max)</sub>. For this application, TI recommends that K<sub>IND</sub> is set to a value from 0.2 to 0.4.

Schematic Guidelines www.ti.com

With the chosen inductance value, the peak current for the inductor in steady state operation,  $I_{L(max)}$ , can be calculated using Equation 2. The rated saturation current of the inductor must be higher than the  $I_{L(max)}$  current.

$$I_{LMAX} = Iout_{MAX} + \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times V_{IN} \times f_{SW} \times L}$$

(2)

Following the previous equations, the preferred inductor selected for the controllers are listed Table 1.

| MANUFACTURER    | PART NUMBER | VALUE          | SIZE              | HEIGHT |  |

|-----------------|-------------|----------------|-------------------|--------|--|

| Cyntec          | PIME031B    | 0.47 μH–1 μΗ   | 3.3 mm × 3.7 mm   | 1.2 mm |  |

| Cyntec          | PIMB041B    | 0.33 μΗ–2.2 μΗ | 4.45 mm × 4.75 mm | 1.2 mm |  |

| Cyntec          | PIMB051B    | 1 μΗ–3.3 μΗ    | 5.4 mm × 5.75 mm  | 1.2 mm |  |

| Cyntec          | PIME051E    | 0.33 μΗ–4.7 μΗ | 5.4 mm × 5.75 mm  | 1.5 mm |  |

| Cyntec          | PIMB051H    | 0.47 μΗ–4.7 μΗ | 5.4 mm × 5.75 mm  | 1.8 mm |  |

| Cyntec          | PIME061B    | 0.56 μΗ–3.3 μΗ | 6.8 mm × 7.3 mm   | 1.2 mm |  |

| Cyntec          | PIME061E    | 0.33 μΗ–4.7 μΗ | 6.8 mm × 7.3 mm   | 1.5 mm |  |

| Cyntec PIMB061H |             | 0.1 μΗ–4.7 μΗ  | 6.8 mm × 7.3 mm   | 1.8 mm |  |

| Cyntec PIMB062D |             | 0.1 μΗ–6.8 μΗ  | 6.8 mm × 7.3 mm   | 2.4 mm |  |

Table 1. Recommended Inductors

### 2.1.2 Selecting the Output Capacitors

TI recommends using ceramic capacitors with low ESR values to provide the lowest output voltage ripple. The output capacitor requires an X7R or an X5R dielectric. Y5V and Z5U dielectric capacitors, aside from their wide variation in capacitance over temperature, become resistive at high frequencies. Due to the DCAP2 architecture, all output capacitors can be ceramic.

At light load currents, the controller operates in PFM mode, and the output voltage ripple is dependent on the output-capacitor value and the PFM peak inductor current. Higher output-capacitor values minimize the voltage ripple in PFM mode. To achieve specified regulation performance and low output voltage ripple, the DC-bias characteristic of ceramic capacitors must be considered. The effective capacitance of ceramic capacitors drops with increasing DC bias voltage.

TI recommends the use of small ceramic capacitors placed between the inductor and load with many vias to the PGND plane for the output capacitors of the BUCK controllers. This solution typically provides the smallest and lowest cost solution available for DCAP2 controllers.

The output capacitance must equal or exceed the minimum capacitance listed in the datasheet for BUCK1, BUCK2, and BUCK6 in order to meet the transient specifications (assuming quality layout techniques are followed).

### 2.1.3 Selecting the FETs

This controller is designed to drive two NMOS FETs. Typically, lower R<sub>DSON</sub> values are better for improving the overall efficiency of the controller. However, as the R<sub>DSON</sub> for the low-side FET decreases, the minimum current limit increases; therefore, ensure selection of the appropriate values for the FETs, inductor, output capacitors, and current limit resistor. The Texas Instruments' CSD87381P and CSD87588N devices are recommended for the controllers, depending on the required maximum current.

### 2.1.4 Bootstrap Capacitor

To ensure the internal high-side gate drivers are supplied with a stable low-noise supply voltage, a capacitor must be connected between the SWx pins and the respective BOOTx pins. TI recommends placing ceramic capacitors with the value of 0.1  $\mu$ F for the controllers.

TI recommends reserving a small resistor in series with the bootstrap capacitor during prototype development in case the turnon and turnoff of the FETs must be slowed to reduce voltage ringing on the switch node, which is a common practice for controller design.

www.ti.com Schematic Guidelines

### 2.1.5 Setting the Current Limit

The buck controllers (BUCK1, BUCK2, and BUCK6) have inductor-valley current-limit architecture and the current limit is programmable by an external resistor at the ILIMx pin. Equation 3 shows the calculation for a desired resistor value, depending on specific application conditions.  $I_{LIMREF}$  is the current source out of the ILIMx pin that is typically 50  $\mu$ A, and  $R_{DSON}$  is the maximum channel resistance of the low-side FET. The scaling factor is 1.3 to take into account all errors and temperature variations of  $R_{DSON}$ ,  $I_{LIMREF}$ , and  $R_{ILIM}$ . Finally, 8 is another scaling factor associated with  $I_{LIMREF}$ .

$$R_{ILIM} = \frac{R_{DSON} \times 8 \times 1.3 \times (I_{LIM} - \frac{I_{ripple,min}}{2})}{I_{LIMREE}}$$

#### where

I<sub>LIM</sub> is target current limit. An appropriate margin should be allowed when one determines I<sub>LIM</sub> from maximum output DC load current.

$$\label{eq:loss_loss} I_{ripple,min} = \frac{V_{out}(v_{in,min} - V_{out})}{L_{max} \times V_{in,min} \times f_{sw,max}}$$

#### where

- L<sub>max</sub> is maximum inductance

- f<sub>sw.max</sub> is maximum switching frequency

- V<sub>in.min</sub> minimum input voltage to the external power stage (4)

### 2.1.6 Selecting the Input Capacitors

Due to the nature of the switching controller with a pulsating input current, a low ESR input capacitor is required for best input voltage filtering and also for minimizing the interference with other circuits caused by high input-voltage spikes. For the controller, a typical 2.2 µF capacitor can be used for the DRV5V\_x\_x pin to handle the transients on the driver. For the FET input, 10 µF of input capacitance (after derating) is recommended for most applications. To achieve the low ESR requirement, a ceramic capacitor is recommended. However, the voltage rating and DC-bias characteristic of ceramic capacitors must be considered. For better input-voltage filtering, the input capacitor can be increased without any limit.

**NOTE:** Use the correct value for the ceramic capacitor capacitance after derating to achieve the recommended input capacitance.

TI recommends placing a ceramic capacitor as close as possible to the FET across the respective VSYS and PGND pins of the FETs. The preferred capacitors for the controllers are two Murata GRM21BR61E226ME44: 22-µF, 0805, 25-V, ±20%, or similar capacitors.

#### 2.2 Converter Design Procedure

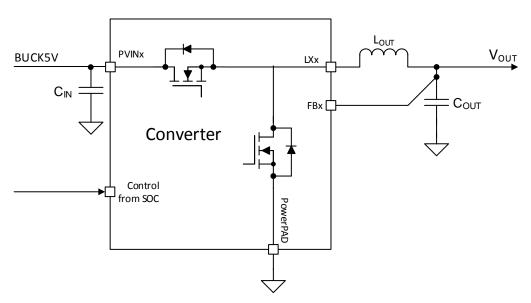

Designing the converter has only two steps: design the output filter and select the input capacitors.

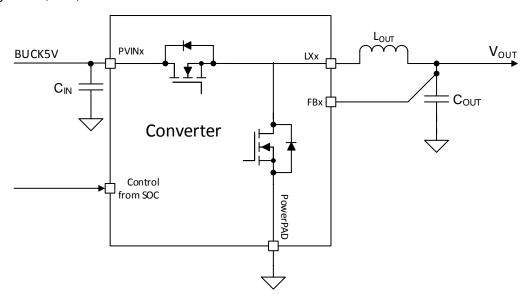

The converter must be supplied by a 5-V source. Figure 3 shows a diagram of the converter.

Schematic Guidelines www.ti.com

Figure 3. Converter Diagram

### 2.2.1 Selecting the Inductor

It is required that an inductor be placed between the external FETs and the output capacitors. Together, the inductor and output capacitors form a double pole in the control loop that contributes to stability. In addition, the inductor is directly responsible for the output ripple, efficiency, and transient performance. As the inductance used increases, the ripple current decreases; this typically results in an increase in efficiency. However, with an increase in inductance used, the transient performance decreases. Finally, the inductor selected must be rated for appropriate saturation current, core losses, and DC resistance (DCR).

**NOTE:** Internal parameters for the converters are optimized for a 0.47 µH inductor, however it is possible to use other inductor values as long as they are chosen carefully and thoroughly validated.

Equation 5 shows the calculation for the recommended inductance for the converter.

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times Iout_{MAX} \times K_{IND}}$$

#### where

- V<sub>OUT</sub> is the typical output voltage

- V<sub>IN</sub> is the typical input voltage

- f<sub>sw</sub> is the typical switching frequency

- lout<sub>MAX</sub> is the maximum load current

- K<sub>IND</sub> is the ratio of I<sub>Lripple</sub> to the I<sub>out(max)</sub>. For this application, TI recommends that K<sub>IND</sub> is set to a value from 0.2 to 0.4

With the chosen inductance value and the peak current for the inductor in steady state operation,  $I_{L(MAX)}$  can be calculated using Equation 6. The rated saturation current of the inductor must be higher than the  $I_{L(MAX)}$  current.

$$I_{LMAX} = Iout_{MAX} + \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times V_{IN} \times f_{SW} \times L}$$

(6)

Following these equations, the preferred inductor selected for the converters are listed in Table 2

www.ti.com Schematic Guidelines

#### Table 2. Recommended Inductors

| MANUFACTURER PART NUMBER |                  | VALUE   | SIZE            | HEIGHT |  |

|--------------------------|------------------|---------|-----------------|--------|--|

| Cyntec                   | PIFE32251B-R47MS | 0.47 μΗ | 3.2 mm x 2.5 mm | 1.2 mm |  |

#### 2.2.2 Selecting the Output Capacitors

Ceramic capacitors with low ESR values are recommended because they provide the lowest output voltage ripple. The output capacitor requires either an X7R or X5R rating. Y5V and Z5U capacitors, aside from the wide variation in capacitance over temperature, become resistive at high frequencies.

At light load currents, the converter operates in PFM mode and the output voltage ripple is dependent on the output-capacitor value and the PFM peak inductor current. Higher output-capacitor values minimize the voltage ripple in PFM mode. To achieve specified regulation performance and low output voltage ripple, the DC-bias characteristic of ceramic capacitors must be considered. The effective capacitance of ceramic capacitors drops with increasing DC-bias voltage.

For the output capacitors of the BUCK converters, TI recommends placing small ceramic capacitors between the inductor and load with many vias to the PGND plane. This solution typically provides the smallest and lowest-cost solution available for DCAP2 controllers.

In order to meet the transient specifications, the output capacitance must equal or exceed the minimum capacitance listed in the datasheet for BUCK3, BUCK4, and BUCK5 (assuming quality layout techniques are followed).

#### 2.2.3 Selecting the Input Capacitors

Due to the nature of the switching converter with a pulsating input current, a low ESR input capacitor is required for best input-voltage filtering and for minimizing the interference with other circuits caused by high input-voltage spikes. For the PVINx pin,  $2.5~\mu F$  of input capacitance (after derating) is required for most applications. A ceramic capacitor is recommended to achieve the low ESR requirement. However, the voltage rating and DC-bias characteristic of ceramic capacitors must be considered. The input capacitor can be increased without any limit for better input-voltage filtering.

A ceramic capacitor placed as close as possible to the FET, across the respective VSYS and PGND pins of the FETs is recommended. The preferred capacitor for the converters is one Samsung CL05A106MP5NUNC: 10-µF, 0402, 10-V, ±20%, or similar capacitor.

### 2.3 LDO Design Procedure

The VTT LDO must handle the fast load transients from the DDR memory for termination. Therefore, it is recommended to use ceramic capacitors to maintain a high amount of capacitance with low ESR on the VTT LDO outputs and inputs. The preferred output capacitors for the VTT LDO are the GRM188R60J226MEA0 from Murata (22  $\mu$ F, 0603, 6.3 V, ±20%, or similar capacitors). The preferred input capacitor for the VTT LDO is the CL05A106MP5NUNC from Samsung (10- $\mu$ F, 0402, 10-V, ±20%, or similar capacitor).

The remaining LDOs must have input and output capacitors chosen based on the values in the datasheet.

### 3 Layout Guidelines

### 3.1 PCB Build Up

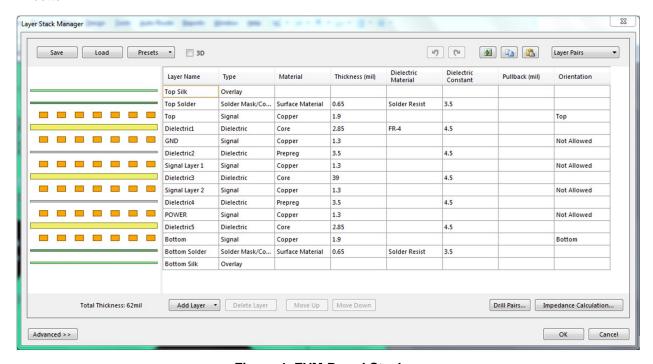

Before the layout is started, the PCB build up is needed to have a good strategy of what signals to place on each layer. There is a lot of theory to go through if a good and proper design is the goal; some of the theories are conflicting, so a complete foolproof strategy is not possible. Hence, the design of the PCB has trade-offs, and the strategy is important to get the best possible design even with the compromises. The recommendations in this document refer to a 6-layer PCB stackup with the TPS65094x device implemented. Designing with a minimum of 6 layers is a great general-purpose guideline for constructing a board with low electromagnetic interference (EMI). Additional layers may be incorporated into the PCB if needed, but they are not required to achieve an efficient design because all necessary routing for the TPS65094x can be accomplished in 6 layers. If complex designs warrant the need for more layers, the designer must always strive to preserve symmetry by using even numbered layer counts, as this helps prevent board warping during the fabrication process. Figure 4 shows the EVM board stack-up from top to bottom.

Figure 4. EVM Board Stackup

### 3.1.1 PCB Strategy

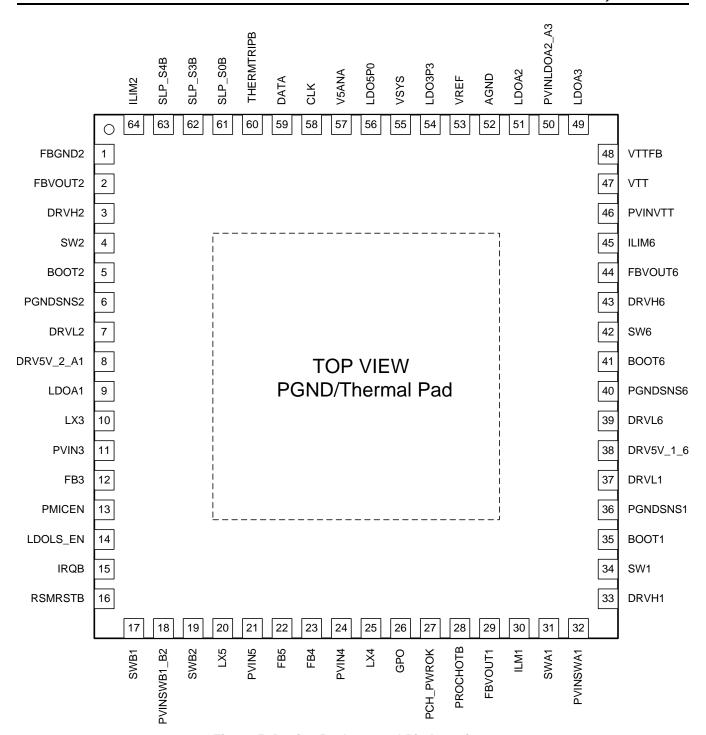

When defining the PCB build-up, there are a number of considerations to take into account. All of the options are related to cost and there will be tradeoffs between the cost and the options chosen. Figure 5 shows the TPS65094x device package and pin locations.

www.ti.com Layout Guidelines

Figure 5. Device Package and Pin Locations

### 3.1.2 Layer Definition

Before starting the layout, a routing strategy needs to be defined by considering the physical location of specific signals.

Sensitive signals can be affected by aggressive signals which are routed close to them.

For instance, the ground loop of high-power consumption devices should not surround sensitive signals which are prone to EMI.

In Figure 6, signals are placed in the ground loop (layers 3, 4, and 5); this is not recommended. The signals in the ground loop are affected by the flux generated by the current in the loop. This must be avoided, especially when dealing with sensitive signals such as the reference voltage, and so forth.

Figure 6. Example of Poor Ground Loop

The supply line and the ground path are both crucial. The supplies must be placed and calculated so that their flux does not affect any sensitive signals. The ground plane must be solid, especially close to the supply trace; if this is not considered, the risk for noise pollution increases. Moreover, no sensitive signals should be in parallel with the supply line and the corresponding ground path. As Figure 7 shows, the problem is solved by choosing other layers for supply and ground, with no signal layer between the ground loop. Some concerns still must be considered.

Figure 7. Example of Improved Ground Loop

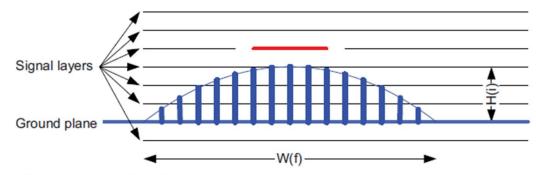

The reason for not routing sensitive signals in parallel with the supply line and corresponding ground path is due to capacitive coupling across layers; the flux generated in either supply path or in ground path affects the neighboring layers. For high frequency, the current in the ground path approaches the one of the supply path. Figure 8 shows the flux in the ground path. This flux "cloud" is affected by frequency and current level.

The width of the flux is determined by the frequency; high frequency and the flux cloud will be very concentrated in parallel with the supply path.

The height is controlled mostly by the current level; higher current is equal to higher flux density and, therefore, can impact other layers.

For both the frequency and the current, the transition period is important. During this phase, the current shifts state and issues can arise due to the current change.

Note: The red trace is the supply track.

Figure 8. Frequency and Current Impact on Ground Plane

#### 3.1.3 Signal Grouping

Critical signals for layout are classified as following:

- Sensitive signals

- Reference

- Voltage sense

www.ti.com Layout Guidelines

- SMPS feedbacks

- Power switching (aggressive signals)

- Switching node of SMPS

- VSYS to controllers/converters

- Noisy grounds

- · Power passive output lines (IR drops to be considered)

- Output of LDOs

- Output of switches

- Ground of DC-DC power (short, wide traces)

- Quiet GNDs

- AGND (VREF)

- LDO GND

- Load Switch GND

- ILIM GND

- Limit resistivity between all grounds

Details about signal connections are provided in the *TPS65094xSchematic Checklist*, *Layout Checklist*, and *ILIM Calculator tool* (SLVA735).

#### 3.1.4 Ground Strategy

There are several ground strategies which have advantages and drawbacks; the following strategy is advised. Use solid ground planes to decrease the resistance path and thus avoid voltage discrepancies. Do not use too many mechanical vias side-by-side which could obstruct the current flux in the ground plane. A good practice is to check the integrity of the ground planes at the end of PCB design by turning off all layers except the grounds.

#### 3.1.4.1 Grounds Classification

Grounds can be classified as follows:

- Clean grounds

- AGND (VREF)

- ILIM GND

- Noisy grounds

- Controller GND

- Converter GND

- Nonaggressive grounds

- LDO GND

- Load Switch GND

Noisy grounds should not be connected to any other grounds on the top layer. All grounds should be merged in grounds planes, making sure that big enough via are used to connect power grounds to ground planes.

### 3.1.4.2 Clean Grounds

AGND and ILIM GND are reference grounds which should be protected from noisy signals.

### 3.2 External Components Choice

Placement of external components has to be done with engineering skills. The placement is expected to be affected by the mechanical dimension, and hereby also the placement of the TPS65094x device. The distance to the supplied devices (for example, the processor) must be considered when determining placement of the TPS65094x. The placement has requirements to both placement of external components and also to the possibility to route power lines from the integrated PMU to power consuming devices such as processors.

**Table 3. Recommended Manufacturer's Components List**

|                                | QTY | Function         | Value  | Description                                                  | Foot-Print | Part Number        | MFR               |

|--------------------------------|-----|------------------|--------|--------------------------------------------------------------|------------|--------------------|-------------------|

| BUCK1 (VNN) DVS at 5 A         | 1   | Output Capacitor | 220 µF | CAP, CERM, 220 μF, 4 V, +/- 20%, X5R, 1206                   | 1206       | GRM31CR60G227ME11  | Murata            |

|                                | 0   | Output Capacitor | 22 µF  | CAP, CERM, 22 μF, 6.3 V, +/- 20%, X5R, 0603                  | 0603       | GRM188R60J226MEA0D | Murata            |

|                                | 1   | Bootstrap Cap    | 0.1 µF | CAP, CERM, 0.1 µF, 10 V, X5R, 10%, 0402                      | 402        | GRM155R61A104KA01D | Murata            |

|                                | 2   | Input Capacitor  | 22 µF  | CAP, CERM, 22 μF, 25 V, X5R, 20%, 0805                       | 805        | GRM21BR61E226ME44  | Murata            |

|                                | 1   | Power Block      |        |                                                              |            | CSD87381P          | Texas Instruments |

|                                | 1   | ILIM Resistor    | 8.87k  | RES, 8.87k, 1%, 0.063 W, 0402                                | 402        | STD                | STD               |

|                                | 1   | Inductor         | 0.47uH | Inductor, Choke, Metal Dust Core, 0.47uH, 18 A, 8.4mohm, SMD |            | PIMB061H-R47MS     | Cyntec            |

| BUCK2 (VCCGI) DVS at 21 A      | 2   | Output Capacitor | 220 µF | CAP, CERM, 220 µF, 4 V, X5R, 20%, 1206                       | 1206       | GRM31CR60G227ME11  | Murata            |

|                                | 5   | Output Capacitor | 22 µF  | CAP, CERM, 22 μF, 6.3 V, +/- 20%, X5R, 0603                  | 0603       | GRM188R60J226MEA0D | Murata            |

|                                | 1   | Bootstrap Cap    | 0.1 µF | CAP, CERM, 0.1 µF, 10 V, X5R, 10%, 0402                      | 402        | GRM155R61A104KA01D | Murata            |

|                                | 2   | Input Capacitor  | 22 µF  | CAP, CERM, 22 μF, 25 V, X5R, 20%, 0805                       | 805        | GRM21BR61E226ME44  | Murata            |

|                                | 1   | Power Block      |        |                                                              |            | CSD87381P          | Texas Instruments |

|                                | 1   | ILIM Resistor    | 18.7k  | RES, 18.7k, 1%, 0.063 W, 0402                                | 402        | STD                | STD               |

|                                | 1   | Inductor         | 0.22uH | Inductor, Choke, Metal Dust Core, 0.33uH, 22 A, 6.8mohm, SMD |            | PIMB061H-R22MS     | Cyntec            |

| BUCK3 (VCCRAM) 1.05 V at 3 A   | 1   | Input Capacitor  | 10 μF  | CAP, CERM, 10 µF, 10 V, X5R, 20%, 0402                       | 402        | GRM155R60J106ME44D | Murata            |

|                                | 4   | Output Capacitor | 22 µF  | CAP, Ceramic, 22 µF, 6.3 V, X5R, 20%, 0603                   | 603        | GRM188B30J226MEA0  | Murata            |

|                                | 1   | Inductor         | 0.47uH | Inductor, Choke, Metal Dust Core, 0.47uH, 5.1 A, 30mohm, SMD |            | PIFE32251B-R47MS   | Cyntec            |

| BUCK4 (V1P8A) 1.8 V at 1.5 A   | 1   | Input Capacitor  | 10 μF  | CAP, CERM, 10 μF, 10 V, X5R, 20%, 0402                       | 402        | GRM155R60J106ME44D | Murata            |

|                                | 2   | Output Capacitor | 22 µF  | CAP, Ceramic, 22 µF, 6.3 V, X5R, 20%, 0603                   | 603        | GRM188B30J226MEA0  | Murata            |

|                                | 1   | Inductor         | 0.47uH | Inductor, Choke, Metal Dust Core, 0.47uH, 5.1 A, 30mohm, SMD |            | PIFE32251B-R47MS   | Cyntec            |

| BUCK5 (V1P24A) 1.24 V at 1.5 A | 1   | Input Capacitor  | 10 µF  | CAP, CERM, 10 μF, 10 V, X5R, 20%, 0402                       | 402        | GRM155R60J106ME44D | Murata            |

|                                | 2   | Output Capacitor | 22 µF  | CAP, Ceramic, 22 µF, 6.3 V, X5R, 20%, 0603                   | 603        | GRM188B30J226MEA0  | Murata            |

|                                | 1   | Inductor         | 0.47uH | Inductor, Choke, Metal Dust Core, 0.47uH, 5.1 A, 30mohm, SMD |            | PIFE32251B-R47MS   | Cyntec            |

| BUCK6 (VDDQ) 1.2 V at 7 A      | 1   | Output Capacitor | 220 µF | CAP, CERM, 220 μF, 4 V, X5R, 20%, 1206                       | 1206       | GRM31CR60G227ME11  | Murata            |

|                                | 1   | Output Capacitor | 100 μF | CAP, Ceramic, 100 µF, 4 V, X5R, 20%, 0805                    | 805        | GRM21BR60G107ME15  | Murata            |

|                                | 1   | Bootstrap Cap    | 0.1 µF | CAP, CERM, 0.1 μF, 10 V, X5R, 10%, 0402                      | 402        | GRM155R61A104KA01D | Murata            |

|                                | 2   | Input Capacitor  | 22 µF  | CAP, CERM, 22 μF, 25 V, X5R, 20%, 0805                       | 805        | GRM21BR61E226ME44  | Murata            |

|                                | 1   | Power Block      |        |                                                              |            | CSD87381P          | Texas Instruments |

|                                | 1   | ILIM Resistor    | 12.1k  | RES, 12.1 k, 1%, 0.063 W, 0402                               | 402        | STD                | STD               |

|                                | 1   | Inductor         | 0.47uH | Inductor, Choke, Metal Dust Core, 0.47uH, 18 A, 8.4mohm, SMD |            | PIMB061H-R47MS     | Cyntec            |

## Table 3. Recommended Manufacturer's Components List (continued)

|                              | QTY | Function                                  | Value   | Description                                  | Foot-Print | Part Number        | MFR               |

|------------------------------|-----|-------------------------------------------|---------|----------------------------------------------|------------|--------------------|-------------------|

| VTT 0.5x VDDQ at 0.5 A       | 1   | Input Capacitor                           | 10 µF   | CAP, CERM, 10 μF, 6.3 V, X5R, 20%, 0402      | 402        | GRM155R60J106ME44  | Murata            |

|                              | 1   | Output Capacitor                          | 47 µF   | CAP, CERM, 47 µF, 4 V, X5R, 20%, 0805        | 805        | GRM219R60G476ME44  | Murata            |

| LDOA2 1.15 V at 0.5 A        | 1   | Input Capacitor                           | 4.7 µF  | CAP, CERM, 4.7 µF, 6.3 V, X5R, 20%, 0402     | 402        | GRM155R60J475ME47  | Murata            |

| LDOA3 1.2 V at 0.5 A         | 2   | Output Capacitor                          | 4.7 µF  | CAP, CERM, 4.7 µF, 6.3 V, X5R, 20%, 0402     | 402        | GRM155R60J475ME47  | Murata            |

| LDOA1 1.8 V/3.3 V at 0.2 A   | 1   | Output Capacitor                          | 4.7 µF  | CAP, CERM, 4.7 µF, 6.3 V, X5R, 20%, 0402     | 402        | GRM155R60J475ME47  | Murata            |

| SWA1 3.3 V at 0.3 A          | 1   | Input Capacitor                           | 1 µF    | CAP, CERM, 1 µF, 6.3 V, X5R, 20%, 0402       | 402        | GRM155C70J105ME11  | Murata            |

|                              | 1   | Output Capacitor                          | 0.1 μF  | CAP, CERM,0.1 µF, 6.3 V, X5R, 20%, 0402      | 402        | GRM022R60J104ME15  | Murata            |

| SWB1 / SWB2 (V1P8U) 1.8 V at | 1   | Input Capacitor                           | 1 μF    | CAP, CERM, 1 μF, 6.3 V, X5R, 20%, 0402       | 402        | GRM155C70J105ME11  | Murata            |

| 0.6 A                        | 2   | Output Capacitor                          | 0.1 μF  | CAP, CERM,0.1 µF, 6.3 V, X5R, 20%, 0402      | 402        | GRM022R60J104ME15  | Murata            |

| Misc.                        | 1   | Input Capacitor at VSYS Pin               | 1 μF    | CAP, CERM, 1 µF, 35 V, X5R, 10%, 0402        | 402        | GRM155R6YA105KE11D | Murata            |

|                              | 1   | Output Capacitor for LDO5                 | 4.7 μF  | CAP, CERM, 4.7 μF, 6.3 V, +/- 20%, X5R, 0402 | 402        | GRM155R60J475ME47D | Murata            |

|                              | 1   | Output Capacitor for LDO3P3               | 4.7 µF  | CAP, CERM, 4.7 μF, 10 V, X5R, 20%, 0603      | 603        | GRM185C81A475ME11  | Murata            |

|                              | 1   | Output Capacitor at<br>VREF               | 0.22 μF | CAP, CERM, 0.22 μF, 6.3 V, X5R, 10%, 0402    | 402        | C1608X5R1A106M     | Murata            |

|                              | 2   | Input Capacitor for Controller 5-V supply | 2.2 µF  | CAP, CERM, 2.2 μF, 10 V, X5R, 20%, 0402      | 402        | GRM155B31A225ME95  | Murata            |

|                              | 6   | Pull-up Resistors                         | 2.2k    | RES, 2.2k, 1%, 0.063W, 0402                  | 402        | STD                | STD               |

|                              | 1   | TPS65094x PMIC                            |         |                                              | 8x8 QFN    | TPS65094x          | Texas Instruments |

#### 3.2.1 Placement Overview

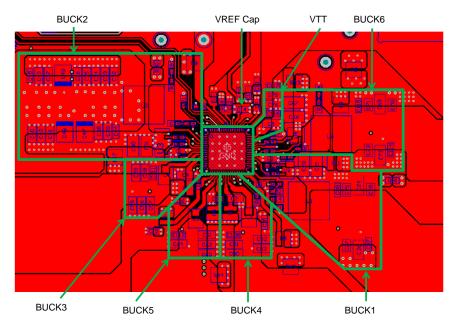

In the following placement recommendations, the EVM board can be a reference regarding good part placement. Figure 9 shows the EVM component placement.

Figure 9. EVM Overall Layout

### 3.3 PCB General Layout Check List

- All inductors, input/output caps and FETs for the converters and controller should be on the same board layer as the IC.

- Place feedback connection points near the output capacitors and minimize the control feedback loop as much as possible to achieve the best regulation performance.

- Bootstrap capacitors should be placed near the IC from the SWx trace to the BOOTx pins.

- DRVLx signals must be routed on the same layer as the IC and the FETs and minimize the length and parasitic inductance of the trace as much as possible.

- The internal reference regulators must have their input and output caps close to the IC pins.

#### 3.3.1 Controller

TPS65094x controllers have bootstrapped drivers optimized to drive external power FETs, thereby offer higher load current capability. Ideally external power FETs are placed close to the controller to achieve optimum performance and avoid EMI concerns.

The bootstrap capacitor should be placed close to the IC rather than near the FET, though other components, such as the input capacitors, will take a higher priority.

Controllers can be used to drive far end loads, if the end application accommodates PCB routing with lower trace parasitics and any potential EMI concerns. This requires good PCB routing and signal return paths need to be provided below the signals for minimum loop area.

- Input capacitors to the FET must be placed as close as possible to the FET, with excellent connections

to both the VSYS plane and GND plane.

- SW trace needs to be routed below DRVH and ensure small return loop for minimum EMI.

- PGND needs to be routed below DRVL and ensure small return loop for minimum EMI.

www.ti.com Layout Guidelines

**NOTE:** This is not PGNDSNS, but an actual PGND connection to the PowerPAD from the FET GND, typically through a second layer PGND plane.

· This routing is recommended but not required when not driving far end loads

Figure 10. Schematic Example of Controller Layout

Limitations on length are set by parasitic inductance (approximately 8 nH, but will vary by application). By simulation, a 10-mil trace can support a max length of 1 in, 20-mil trace can support up to 3.5 in potentially. The addition of a damping resistor can improve performance at long length.

For the FET layout, the CSD87381P datasheet (<u>SLPS405</u>) has a good section regarding proper implementation. The primary concern here is the input capacitor must be as close as possible across the VIN and PGND pins of the FET. There need to be plenty of vias connecting these two planes on the top layer to their respective planes in the layer stack.

For the PGNDSNS node, it needs to be connected as close as possible to the FET PGND pad but out of the main current path to avoid any excess IR drop. Additionally, insure that the trace does not merge with the power GND plane at any point. This will require keep outs on the vias.

Output capacitor placement will vary based on requirements. For optimum load transient performance, it is recommended to place them near the load. Additionally, the output path to the load should be short and wide to minimize parasitics. It is not recommended to route the controller outputs long distances. If there are EMI concerns, capacitors can be placed near the inductor to reduce EMI on the output node, though SW node typically dominates.

An example from the EVM can be seen in Figure 11.

Figure 11. EVM Layout of Controllers

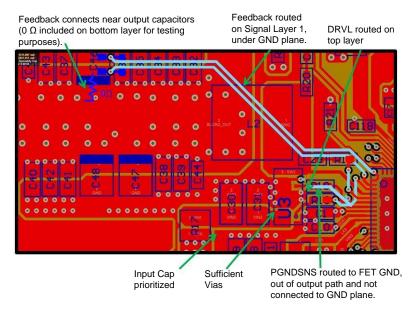

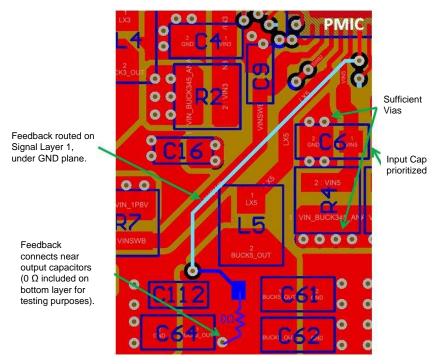

### 3.3.2 Converter

As for all switching power supplies, the board layout is an important step in the design. High-speed operation of the TPS65094x device demands careful attention to PCB layout. Care must be taken in board layout to get the specified performance. If the layout is not carefully done, the regulator could show poor line and/or load regulation, stability issues as well as EMI problems. It is critical to provide a low inductance, low impedance ground path. Therefore, use wide and short traces for the main current paths along PVINx, LXx, and the PowerPAD.

Figure 12. Schematic Example of Converter Layout

The input capacitors and inductor should be routed as close as possible to the IC with sufficiently wide and short traces. The load should be as close to the IC as possible.

Output capacitor placement will vary based on requirements. For optimum load transient performance, it is recommended to place them near the load. Additionally, the output path to the load should be short and wide to minimize parasitics. It is not recommended to route the converter outputs long distances. If there are EMI concerns, capacitors can be placed near the inductor to reduce EMI on the output node, though SW node typically dominates.

The output voltage sense line (FBx) should be connected to the center of the output capacitors and routed in a manner to minimize control loop area while also avoiding noisy nets (the SW node, for example). Its trace should be small and placed in a way where no signals can affect the voltage level, as that is used to adjust the output voltage from the BUCK converter.

The same output capacitor strategy can be used here as with the controllers.

Ideally, the sense line should not be routed on the same layer as switched lines, but on a lower layer isolated from switched lines by a ground plane, as shown in Figure 13.

Figure 13. Example Converter Routing

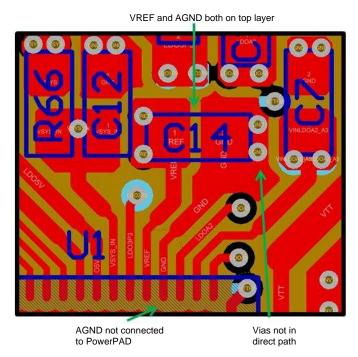

#### 3.3.3 Reference Voltage Routing

The reference voltage needs connection to an external capacitor (100 nF). Avoid aggressors signal surrounding the trace to the capacitor. The trace can be small due to low current on the reference.

The reference voltage requires a clean ground. Hence, the AGND ground is used as the ground connection for its filter capacitor. The AGND pin must be connected to a dedicated ground island. A dedicated ground island is connected to main ground in one point (with a via, shrunken ground plane, or shunt resistor). The ground island is located on the top layer.

17

Figure 14. V<sub>REF</sub> Layout

### 3.3.4 I<sup>2</sup>C Interfaces

Interfaces can be aggressors due to high frequency; up to 1 MHz for I<sup>2</sup>C. Avoid critical signals close to I<sup>2</sup>C nets, or use large spacing between sensible signals (3x weight).

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive amplifier.ti.com Communications and Telecom www.ti.com/communications Amplifiers **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical

Logic logic.ti.com Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity