# AN-1432 The LM4935 Headset and Push-Button Detection Guide

# ABSTRACT

The LM4935 features an advanced headset detection scheme that can sense the insertion or removal of any type of available headset.

#### Contents

| 1 | Introduction                                             | 1 |

|---|----------------------------------------------------------|---|

| 2 | OCL and AC-Coupled Modes                                 | 2 |

| 3 | Headset Status Feedback                                  | 3 |

| 4 | Reduced Power Consumption                                | 4 |

| 5 | Push-Button Press and Release Detect                     | 5 |

| 6 | Headset and Push-Button Debouncing                       | 5 |

| 7 | Enabling the Headset and Push-Button Detect Circuit      | 6 |

| 8 | Push-To-Talk (PTT) Handset Push-Button Detect Capability | 6 |

| 9 | Revision Table                                           | 6 |

#### List of Figures

| 1 | Headset Configurations Supported by the LM4935     | 2 |

|---|----------------------------------------------------|---|

| 2 | OCL and AC-Coupled Headset Jack Connection Schemes | 3 |

#### List of Tables

| 1 | STATUS (0x18h) | 3 |

|---|----------------|---|

| 2 | DETECT (0x17h) | 4 |

| 3 | MIC_2 (0x0Ch)  | 5 |

| 4 | BASIC (0x00h)  | 6 |

#### 1 Introduction

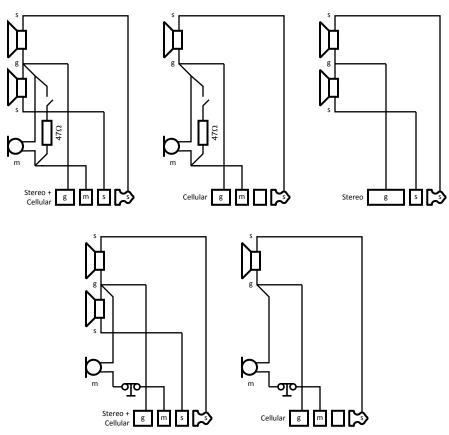

The headset detect circuitry can differentiate between mono, stereo, mono with microphone, and stereo with microphone headsets, as shown in Figure 1. It can operate while the LM4935 is placed into low current standby mode, which promotes extended battery life. In standby mode, it consumes no extra current, if the headset has not been inserted into the headset jack.

All trademarks are the property of their respective owners.

Figure 1. Headset Configurations Supported by the LM4935

# 2 OCL and AC-Coupled Modes

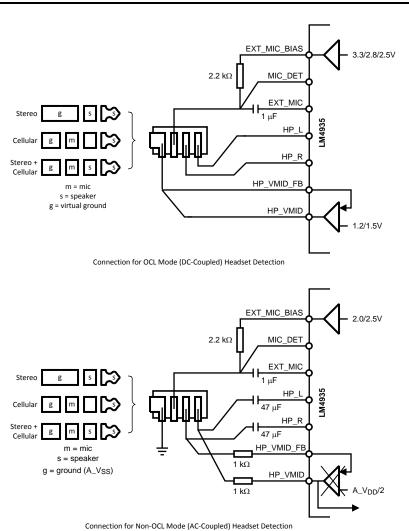

The headset detect circuitry also accommodates AC-coupled and output capacitor-less (OCL) headphone amplifier configurations. However, the connections between the headset jack and the LM4935 depend on the configuration of the headphone amplifier, as shown in Figure 2.

2

www.ti.com

Figure 2. OCL and AC-Coupled Headset Jack Connection Schemes

## 3 Headset Status Feedback

The headset detect circuitry takes advantage of the LM4935's read and write I2C interface by updating bits 0 through 3 of the amplifier's STATUS register (0x18h) in real time.

| Bits | Field              | Description                                                                                                                                                                                                                                    |

|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | HEADSET            | This field is a logic high when headset presence is detected (only valid if the detection system is enabled).                                                                                                                                  |

| 1    | STEREO_<br>HEADSET | This field is a logic high when a headset with stereo speakers is detected (only valid if the detection system is enabled).                                                                                                                    |

| 2    | MIC                | This field is a logic high when a headset with a microphone is detected (only valid if the detection system is enabled).                                                                                                                       |

| 3    | BTN                | This field is a logic high when the button on a headset is pressed (only valid if the detection system is enabled). The IRQ is cleared when the button has been released <b>and</b> a write command has been initiated on the status register. |

| 4    | SAR TRIG 1         | If this field is a logic high, then an event has happened on SAR trigger 1 (write to this register to clear the IRQ).                                                                                                                          |

| 5    | SAR TRIG 2         | If this field is a logic high, then an event has happened on SAR trigger 2 (write to this register to clear the IRQ).                                                                                                                          |

Table 1. STATUS (0x18h)

www.ti.com

#### Table 1. STATUS (0x18h) (continued)

| Bits | Field | Description                                                                                                                                                                                                                                                                 |  |  |

|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 6    | TEMP  | If this field is a logic high, then a temperature event has occurred (write to this register to clear the IRQ). This bit will stay high even when the IRQ is cleared, so long as the event occurs. This bit is only valid whenever the loudspeaker amplifier is turned off. |  |  |

| 7    | GPIN  | When GPIO_SEL is set to a readable configuration, a digital input on GPIO1 can be read back here.                                                                                                                                                                           |  |  |

Setting the LM4935's DETECT register (0x17h) bit 0 to a logic high causes the amplifier to issue an interrupt (set the IRQ pin high) when a headset insert and removal event has occurred. An I2C read transaction is triggered by an interrupt request, when the contents of the STATUS register (0x18h) are read back by the baseband IC (or microprocessor). This allows the baseband IC to perform the appropriate function dictated by the change in the mobile phone's headset status.

| Bits                                   | Field                                                       | Description                                                                                                                                                                                                                                                                                                                                    |                                                       |  |  |

|----------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|

| 0                                      | DET_INT                                                     | If set, an IRQ is issued when a change is detected in the headset status. Clearing this bit will clear an IRQ that has been triggered by the headset detect.                                                                                                                                                                                   |                                                       |  |  |

| 1                                      | BTN_INT                                                     | If set, an IRQ is issued when the headset button is been triggered by a button event.                                                                                                                                                                                                                                                          | pressed. Clearing this bit will clear an IRQ that has |  |  |

| 2                                      | TEMP_INT                                                    | If set, an IRQ is issued during a temperature event. If cleared, the LM4935 will still automatically cycle the power amplifiers off when the internal temperature is too high. This bit should not be set whenever the loudspeaker amplifier is turned on. Clearing this bit will clear an IRQ that has been triggered by a temperature event. |                                                       |  |  |

| 6:3                                    | HS_<br>DBNC_TIME                                            | Sets the time used for debouncing the analog signals from the detection inputs used to sense the insertion/removal of a headset.                                                                                                                                                                                                               |                                                       |  |  |

|                                        |                                                             | HS_DBNC_TIME                                                                                                                                                                                                                                                                                                                                   | Time (ms)                                             |  |  |

|                                        |                                                             | 00002                                                                                                                                                                                                                                                                                                                                          | 0                                                     |  |  |

|                                        | 0001 <sub>2</sub><br>0010 <sub>2</sub><br>0011 <sub>2</sub> |                                                                                                                                                                                                                                                                                                                                                | 8                                                     |  |  |

|                                        |                                                             |                                                                                                                                                                                                                                                                                                                                                | 16                                                    |  |  |

|                                        |                                                             |                                                                                                                                                                                                                                                                                                                                                | 32                                                    |  |  |

|                                        |                                                             | 01002                                                                                                                                                                                                                                                                                                                                          | 48                                                    |  |  |

|                                        |                                                             | 01012                                                                                                                                                                                                                                                                                                                                          | 64                                                    |  |  |

|                                        |                                                             | 01102                                                                                                                                                                                                                                                                                                                                          | 96                                                    |  |  |

|                                        | 01112                                                       |                                                                                                                                                                                                                                                                                                                                                | 128                                                   |  |  |

| 1000 <sub>2</sub><br>1001 <sub>2</sub> |                                                             | 10002                                                                                                                                                                                                                                                                                                                                          | 192                                                   |  |  |

|                                        |                                                             | 10012                                                                                                                                                                                                                                                                                                                                          | 256                                                   |  |  |

|                                        |                                                             | 10102                                                                                                                                                                                                                                                                                                                                          | 384                                                   |  |  |

| 101                                    |                                                             | 10112                                                                                                                                                                                                                                                                                                                                          | 512                                                   |  |  |

|                                        |                                                             | 11002                                                                                                                                                                                                                                                                                                                                          | 768                                                   |  |  |

|                                        |                                                             | 11012                                                                                                                                                                                                                                                                                                                                          | 1024                                                  |  |  |

|                                        |                                                             | 11102                                                                                                                                                                                                                                                                                                                                          | 1536                                                  |  |  |

|                                        | 2048                                                        |                                                                                                                                                                                                                                                                                                                                                |                                                       |  |  |

#### Table 2. DETECT (0x17h)

## 4 Reduced Power Consumption

4

To reduce power consumption and processor loading, the headset detect circuitry automatically disables audio amplifiers that are not in use. The left and right headphone amplifiers will be disabled when the LM4935 is set to active mode, the headset detect is enabled, and a headset is not present. In the AC-coupled configuration, the headphone amplifiers will be muted. In the OCL configuration, the headphone amplifiers will be switched off. The external microphone bias pin (EXT\_BIAS) is disabled for both AC-coupled and OCL configurations. However, the automatic changes made by the headset detect circuitry while the LM4935 is running in active mode will take precedence over I2C control register settings.

#### 5 Push-Button Press and Release Detect

The LM4935 has the capability to detect button press if a button is present on the headset microphone. Both parallel push-button (push-button in parallel with the headset microphone) and series push-button (push-button in series with the headset microphone) headsets can be detected. However, the button type (series or parallel) needs to be predefined by BUTTON\_TYPE (bit 3 of the MIC\_2 (0x0Ch) register). Button presses can be detected even when the part is in standby mode; this consumes 10  $\mu$ A of analog supply current for a series push-button and 100  $\mu$ A for a parallel push-button. Upon push-button press or release, the headset detect circuitry updates bit 3 of the STATUS (0x18h) register. If a parallel push-button headset is inserted into the headset jack in active OCL mode with the internal microphone selected (INT\_EXT = 0; bit 6 of reg (0x0Bh)), the INT\_EXT bit must be set to a logic high before BTN (bit 3 of STATUS (0x18h)) can be read. When a button press is sensed, the LM4935 can also be programmed to raise an interrupt on the IRQ pin by setting bit 1 of DETECT(0x17h).

| Bits | Field                        | Description                                                                                                                                                                                                                                                                                                                                                                                                            |                                    |                                    |

|------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|

| 0    | OCL_<br>VCM_                 | Selects the voltage used as virtual ground (HP_VMID pin) in OCL mode. This will depend on the available supply and the power output requirements of the headphone amplifiers.                                                                                                                                                                                                                                          |                                    |                                    |

|      | VOLTAGE                      | OCL_VCM_VOLTAGE Volta                                                                                                                                                                                                                                                                                                                                                                                                  |                                    | age                                |

|      |                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.2 V                              |                                    |

|      |                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5                                | 5 V                                |

| 2:1  | MIC_<br>BIAS_<br>VOLTAGE     | Selects the voltage as a reference to the internal and external microphones. Only one bias pin is driven at once depending on the INT_EXT bit setting found in the MIC_1 (0x0Bh) register.<br>MIC_BIAS_VOLTAGE should be set to '11' only if $A_V_{DD} > 3.4V$ . In OCL mode, MIC_BIAS_VOLTAGE = '00' (EXT_BIAS = 2.0V) should not be used to generate the EXT_BIAS supply for a cellular headset external microphone. |                                    |                                    |

|      |                              | MIC_BIAS_VOLTAGE                                                                                                                                                                                                                                                                                                                                                                                                       | EXT_BIAS                           | INT_BIAS                           |

|      |                              | 002                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.0 V                              | 2.0 V                              |

|      |                              | 012                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.5 V                              | 2.5 V                              |

|      |                              | 102                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.8 V                              | 2.8 V                              |

|      |                              | 112                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.3 V                              | 3.3 V                              |

| 3    | BUTTON_TYPE                  | If set, the LM4935 assumes that the button (if used) in the headset is in series (series push button) with the microphone, opening the circuit when pressed. The default is for the button to be in parallel (parallel push button), shorting out the microphone when pressed.                                                                                                                                         |                                    |                                    |

| 5:4  | BUTTON_<br>DEBOUNCE_<br>TIME | Sets the time used for debouncing                                                                                                                                                                                                                                                                                                                                                                                      | the pushing of the button on a hea | adset with a parallel push button. |

|      |                              | BUTTON_DEBOUNCE_TIME                                                                                                                                                                                                                                                                                                                                                                                                   |                                    | Time (ms)                          |

|      |                              | 002                                                                                                                                                                                                                                                                                                                                                                                                                    |                                    | 0                                  |

|      |                              | 012                                                                                                                                                                                                                                                                                                                                                                                                                    |                                    | 8                                  |

|      |                              | 102                                                                                                                                                                                                                                                                                                                                                                                                                    |                                    | 16                                 |

|      |                              | 112                                                                                                                                                                                                                                                                                                                                                                                                                    |                                    | 32                                 |

#### Table 3. MIC\_2 (0x0Ch)

## 6 Headset and Push-Button Debouncing

The LM4935 provides debounce programmability for both headset insertion/removal and push-button press detect. Headset debounce programmability is used to avoid false detection by ignoring glitches generated by the physical act of inserting or removing a headset from a headset jack. This debounce time is defined by HS\_DBNC\_TIME (bits 6:3 of DETECT(0x17h)) and can be set for up to 2048 ms. Parallel push-button debounce programmability is used to avoid false detection by ignoring glitches due to mechanical switch bouncing during a parallel push-button press or release. Parallel push-button debounce time is defined by BTN\_DBNC\_TIME (bits 5:4 of MIC\_2(0x0Ch)) and can be set for up to 32ms. Because the initial effect of a series push-button press (microphone disconnected) is indistinguishable from a headset removal, the debounce time for a series push-button is defined by the headset debounce time, HS\_DBNC\_TIME.

5

Enabling the Headset and Push-Button Detect Circuit

www.ti.com

#### 7 Enabling the Headset and Push-Button Detect Circuit

For reliable headset and push-button detection, it is recommended to program the settings of the headset detect circuitry first before activating the headset detect circuitry. The following bits should be defined in this order:

- OCL (bit 7 of BASIC(0x00h)), which programs the LM4935's headphone amplifier to be either ACcoupled or OCL.

- HS\_DBNC\_TIME (bits 6:3 of DETECT(0x17h)), which sets the headset insertion/removal and series push-button (if used) debounce time.

- BUTTON\_TYPE (bit 3 of MIC\_2(0x0Ch)), which predefines whether a series or parallel type pushbutton on the headset is going to be used.

- BTN\_DBNC\_TIME (bits 5:4 of MIC\_2(0x0Ch)), which sets the parallel push-button (if used) debounce time.

Once these bits have been defined, the headset and push-button detection circuitry can be enabled by setting CHIP\_MODE (bit 0 of BASIC(0x00h)).

| Bits | Field     | Description                                                                                                                                                                                                                                              |                                                           |  |                                            |  |

|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--------------------------------------------|--|

| 1:0  | CHIP_MODE | The LM4935 can be placed in one of four modes which dictate its basic operation. When a new mode is selected, the LM4935 will change operation silently and re-configure the power management profile automatically. The modes are described as follows: |                                                           |  |                                            |  |

|      |           | CHIP MODE Audio System Detection System Typical Application                                                                                                                                                                                              |                                                           |  |                                            |  |

|      |           | 002                                                                                                                                                                                                                                                      | Off Off Power-down Mode                                   |  | Power-down Mode                            |  |

|      |           | 012                                                                                                                                                                                                                                                      | Off On Stand-by mode with headset event detec             |  | Stand-by mode with headset event detection |  |

|      |           | 10 <sub>2</sub>                                                                                                                                                                                                                                          | On Off Active without headset event detection             |  | Active without headset event detection     |  |

|      |           | 11 <sub>2</sub>                                                                                                                                                                                                                                          | 11 <sub>2</sub> On On Active with headset event detection |  |                                            |  |

| 7    | OCL       | If set, the part is placed in OCL (Output Capacitor Less) mode.                                                                                                                                                                                          |                                                           |  |                                            |  |

## Table 4. BASIC (0x00h)

# 8 Push-To-Talk (PTT) Handset Push-Button Detect Capability

The LM4935 can be seamlessly integrated into systems utilizing a PTT (push-to-talk) push-button located on the handset itself. A PTT push-button press can be detected using the LM4935's multipurpose successive approximation register (SAR) ADC. A logic signal set by the position of the PTT push-button can be applied to either the VSAR1 or VSAR2 input pins of the LM4935. The LM4935 can issue an interrupt when this signal passes a preprogrammed logic signal threshold voltage. The logic signal applied to either pin, an IRQ is issued. SAR\_TRIG\_1 (bit 4 of STATUS(0x18h)) becomes a logic high whenever a SAR trigger event is detected on the VSAR1 input pin. SAR\_TRIG\_2 (bit 5 of STATUS(0x18h)) becomes a logic high whenever a SAR trigger event is detected on the operation and programmability of the SAR ADC, see the LM4935 data sheet.

A PTT push-button press can also be detected using the LM4935's GPIO interface. A logic level set by the position of the PTT push-button is applied to the LM4935's GPIO1 pin. The voltage that is applied to the GPIO1 pin can be read via GPIN (bit 7 of STATUS(0x18h)). GPIN directly monitors the status of the PTT push-button. This method does not automatically raise an interrupt request upon a PTT push-button press. Therefore, a periodic read of the STATUS(0x18h) register is required when using the GPIO1 pin for PTT push-button detect.

## 9 Revision Table

| Rev | Date     | Description      |

|-----|----------|------------------|

| 0.1 | 04/24/06 | Initial release. |

www.ti.com

7

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated