TB-01 Preventing Latch-Up in the COMBO II CODEC/Filter

Literature Number: SNLA005

# **Preventing Latch-Up** in the COMBO II™ CODEC/Filter

National Semiconductor Application Brief TB- 01 August 1988

#### INTRODUCTION

Despite the superior latch-up resistance already achieved, there are still conditions under which the COMBO II family of CODEC/Filter devices can be made to latch-up. These conditions are well understood and some simple precautions will prevent them from occurring.

#### **LATCH-UP MECHANISM**

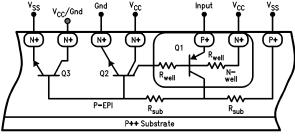

The latch-up mechanisms for CMOS circuits operating with single supplies such as logic devices are generally well understood and easily controlled. The situation is a more complicated with mixed signal analog and digital devices such as CODEC/Filters, which operate from dual supplies. Figure 1 illustrates some of the parasitic transistors which have been found to play the most significant role in triggering latch-up in dual supply N-well CMOS devices. Once activated, the latch-up mechanism is essentially the same as for single supply devices.

#### TRIGGERING LATCH-UP

The normal method of preventing latch-up in CMOS devices involves minimizing the gain of the parasitic transistors and insuring, through layout techniques, that a low value resistance is connected across the base-emitter junction of one or both of the parasitic transistors (PNP and NPN). In a single supply device,  $V_{SS}$  and GND in Figure 1 would be connected together at frequent intervals through the device layout, insuring the Rsub is of sufficiently low value to shunt all injected current away from the base of Q2. In dual supply devices where VSS and GND are separated by 5V, it would at first seem that any current injected by parasitic transistors such as Q1 would flow harmlessly to VSS, maintaining the base-emitter junction of Q2 safely reverse biased. If however. Vss were to momentarily become positive relative to GND, the base-emitter junction of Q2 would forward bias and the low value of Rsub would be of no benefit in shunting away base current. It would, in fact, become the path through which base current flowed to Q2. As will be explained, this is the mechanism which triggers latch-up in COMBO II devices.

#### SUSTAINING LATCH-UP

Once Q2 turns on, its collector current provides the source of base current for Q1 and other PNP parasitic transistors not shown in the figure. Q1 then supplies additional base current to Q2, resulting in latch-up or at very minimum a high current operating state. At this point, there may be sufficient current flowing that connecting  $V_{\mbox{\footnotesize SS}}$  will not turn off fQ2 but will turn on Q3, further intensifying the latch-up.

#### LATCH-UP SENARIO

The fundamental trigger mechanism for latch-up in dual supply CMOS devices is  $V_{\mbox{SS}}$  going positive relative to GND. Several relatively common situations which can activate this mechanism will be discussed. Clearly, all of these situations deal in some way with VSS "floating", at least momentarily, since V<sub>SS</sub> being positive relative to GND is an essential element of the trigger mechanism.

### **HOT INSERTION OF LINECARDS**

In linecard applications, it is frequently necessary to insert the card into the line frame "hot", i.e., with power already on. It is assumed that the GND pin on the card always makes contact before the supply pins or any signal pins as recommended in Application Note AN-370.

#### INPUT SIGNALS APPLIED BEFORE VCC

AN-370 also recommends that the  $V_{CC}$  and  $V_{SS}$  pins make contact before any signal pins. But depending on the type of connector it may not be possible to have three pin lengths (for GND, V<sub>CC</sub> and V<sub>SS</sub>, and signal pins). In this case, V<sub>CC</sub>, V<sub>SS</sub> and all signal pins may connect in any sequence depending on how the card is inserted. Another fairly common practice, which is not recommended, is to connect the inputs of the COMBO device directly to the backplane. Since power is on and the backplane is active, the following situation may arise:

- GND connects

- Signal inputs are connected and inputs are either at +5V or have active logic signals on them

- The V<sub>CC</sub> and V<sub>SS</sub> pins are not connected

In this situation transistor Q1 is turned on, since the V<sub>CC</sub> pin is not connected yet and is therefore at a lower potential than the inputs. Since V<sub>CC</sub> tends to have large filter capaci-

FIGURE 1

TI /H/10020-1

COMBO™ and COMBO II™ are trademarks of National Semiconductor Corporation

tors connected to it, Q1 has an ample source of base current. Current flows from the emitter of Q1 through its collector to the  $V_{SS}$ . Since the  $V_{SS}$  pin is not yet connected,  $V_{SS}$  is pulled positive, forward biasing the base of Q2. Part of the collector current from Q2 provides additional base current for Q1, the rest of the collector current from Q2 flows to  $V_{CC}$ . If  $V_{CC}$  connects at this time, very large currents can flow because the gain of the vertical PNP Q1 is very high, and essentially none of it's collector current is shunted away from the base of Q2. Even though only a portion of the Q2 collector current reaches the base of Q1, there may be a significant net gain around the Q1–Q2 loop. At this point sufficient current may be flowing such that connecting  $V_{SS}$  will not stop the latch-up and Q3 will turn on with similar results.

#### EXTERNAL CIRCUITS CONNECT FROM V<sub>CC</sub> TO V<sub>SS</sub>

If the inputs to the COMBO device are buffered from the backplane by logic devices operating from the same +5V supply, the inputs cannot rise above  $V_{\rm CC}$ , turning on Q1 and pulling  $V_{\rm SS}$  positive. In some cases, however, external circuits such as operational amplifiers may provide a direct current path from  $V_{\rm CC}$  to  $V_{\rm SS}.$  In this case, the following situation may arise:

- GND connects

- The V<sub>CC</sub> pin connects

Since  $V_{SS}$  is still floating, the external circuit may actually pull  $V_{SS}$  positive, turning on Q2. This situation is not as likely to cause latch-up unless the external circuit provides fairly large currents to  $V_{SS}$ , but it is something to watch out for none-the-less.

#### **POWER SUPPLY SEQUENCING**

Normally, power supply sequencing is not an issue. One special case where it is of concern is when separate supplies are used for digital circuitry on the linecard and the COMBO device. In this case, if the logic  $+5\mathrm{V}$  supply is turned on before the COMBO  $+5\mathrm{V}$  supply and  $\mathrm{V}_{SS}$ , the situation may be essentially the same as described in Input Signals Applied before  $\mathrm{V}_{CC}$  above. Another situation which can produce similar results arises when the same  $+5\mathrm{V}$  supply is used but very heavy filtering is used on the

COMBO supply. This can cause the COMBO's  $V_{CC}$  voltage to rise slower than its input voltage with similar consequences.

#### PREVENTING LATCH-UP

There are a number of very simple precautions which if followed will insure that COMBO II will not latch-up.

The minimum solution is

- Insure that the GND pin on the circuit board makes contact before the supply or signal pins.

- Connect a Schottky diode from V<sub>SS</sub> to GND. We recommend a 1N5817 which provides excellent protection at low cost. No series impedance should isolate the Schottky diode from the device's V<sub>SS</sub> pin.

The best solution is to follow the advice of Application Note AN-370. This means that in addition to the items above:

- $\bullet$  Connect a Schottky diode (1N5817) from  $V_{\mbox{\footnotesize{CC}}}$  to GND.

- The COMBO inputs and outputs should be buffered from the backplane.

While the precautions above provide excellent protection at low cost, there are of course alternative ways to achieve the same goal. Two such approaches, either one of which will work are:

A Apply  $V_{\mbox{\footnotesize SS}}$  and then  $V_{\mbox{\footnotesize CC}}$  BEFORE any inputs, or  $\dots$

B Use 1 k $\Omega$  series resistors to limit the current into device inputs that go directly to the backplane or to sources which can be active before V<sub>CC</sub> is applied.

#### CHMMARV

The latch-up trigger mechanism in COMBO II has been explained and several simple, low cost precautions presented to insure safe and reliable operation of the device under real operational conditions. We at National will continue to work on improving the already excellent latch-up resistance of the COMBO II family. However the precautions described above and in AN-370 are always recommended and will provide maximum reliability with a minimum of inconvenience. In the mean time, remember,

- Ground first . . .

- Schottky diode from VSS to GND ...

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

National Semiconductor Europe

Fax: (+49) 0.180-530 85 86

Email: onjwge@tevm2.nsc.com

Deutsch Tel: (+49) 0.180-530 85 85

English Tel: (+49) 0.180-532 78 32

Français Tel: (+49) 0.180-532 35

Italiano Tel: (+49) 0.180-534 16 80

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

## Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Interface interface.ti.com Security www.ti.com/security

Logic Space, Avionics and Defense <u>www.ti.com/space-avionics-defense</u>

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity www.ti.com/wirelessconnectivity

TI E2E Community Home Page <u>e2e.ti.com</u>