# DP83822 Energy Efficient Ethernet IEEE 802.3az

Ross Pimentel

# ABSTRACT

The DP83822 was designed to meet the needs of rugged and high performance applications while still offering a wide range of options for minimizing power consumption. This application note will discuss how the DP83822 Energy Efficient Ethernet feature works and how to implement Energy Efficient Ethernet.

#### Contents

| 1 | Introduction              | 2  |

|---|---------------------------|----|

| 2 | Energy Efficient Ethernet | 2  |

| 3 | Conclusion                | 14 |

# 1 Introduction

The DP83822 10/100Mbps Industrial Ethernet PHY offers a wide range of power saving modes that can be applied individually or in combination with each other depending on the desired operation. Supported low power modes include:

- Energy Efficient Ethernet IEEE802.3az

- Wake-on-LAN

- Magic Packet Detection

- Magic Packet Detection with Secure-ON

- Custom Packet Detection

- Low Power Sleep Modes

- Passive Sleep

- Active Sleep

- IEEE Power Down

- Deep Power Down

This application note will discuss EEE.

## Table 1. Terminology

| Acronym | Defintion                   |  |

|---------|-----------------------------|--|

| DUT     | Device Under Test           |  |

| MAC     | Media Access Controller     |  |

| LP      | Link Partner                |  |

| EEE     | Energy Efficient Ethernet   |  |

| WoL     | Wake-on-LAN                 |  |

| Opcode  | Operation Code              |  |

| PHY     | Physical Layer Transceiver  |  |

| SMI     | Serial Management Interface |  |

| IPG     | Inter-Packet Gap            |  |

| LPI     | Low-Power Idle              |  |

| NLP     | Normal Link Pulse           |  |

| ТХ      | Transmit – Digital Pins     |  |

| RX      | Receive – Digital Pins      |  |

| TD      | Transmit – Analog Pins      |  |

| RD      | Receive – Analog Pins       |  |

# 2 Energy Efficient Ethernet

This section discusses the principles behind EEE and implementation of EEE.

## 2.1 EEE – Principles of Operation

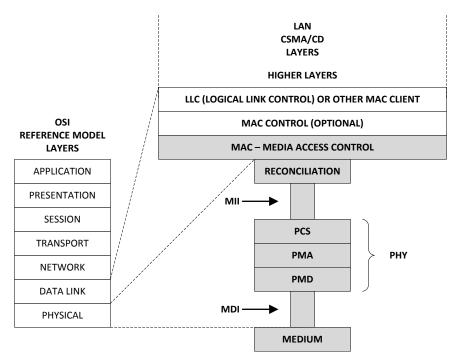

Energy Efficient Ethernet (EEE) is a mechanism by which current consumption is lowered during periods of low packet traffic. The MAC and PHY must both support EEE functionality since EEE is an IEEE standard (IEEE802.3az) that governs both Layer 1 and Layer 2 operations.

**Note**: 10 Mbps EEE is achieved using only signal amplitude reduction and does not require any negotiation with a Link Partner (LP) or require MAC-PHY handshaking. 10BASE-T and 10BASE-Te only send link pulses during IPG, unlike 100 Mbps and 1000 Mbps operation where there is a constant stream of IDLES between frames.

## Figure 1. IEEE802.3az relationship to the ISO/IEC Open Systems Interconnection (OSI) reference model and the IEEE802.3 CSMA/CD LAN model

100BASE-TX sends IDLES during the Inter-Packet Gap (IPG). These IDLES allow the PHY to maintain signal equalization and link status. The DUT and the LP also use IDLEs to recover the other device's transmit clock for their own internal recovered clock. The PHYs constantly send IDLEs even when no traffic is present, current consumption is high because the line drivers are always active. EEE helps minimize current consumption by allowing quiet periods during Low-Power Idle (LPI) operation.

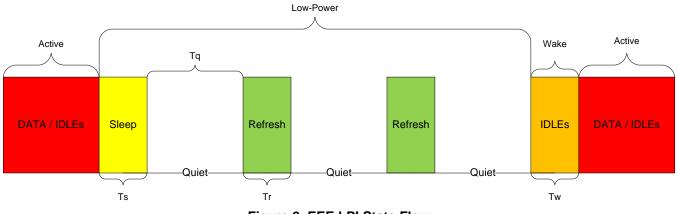

LPI consists of a five main states: Active, Sleep, Quiet, Refresh and Wake. However the simplified diagram shown in Figure 2, with just Active, Low-Power and Wake is also acceptable.

Table 2. EEE LPI Timing

| Line State | Symbol | Timing Parameter<br>(Transmit) | Timing Parameter<br>(Receive) | Line Signals              |

|------------|--------|--------------------------------|-------------------------------|---------------------------|

| SLEEP      | Ts     | 200 μs – 220 μs                | 240 μs - 260 μs               | 4B5B code-group /P/       |

| QUIET      | Τq     | 20 ms – 22 ms                  | 24 ms – 26 ms                 | Differential DC zero volt |

| REFRESH    | Tr     | 200 μs – 220 μs                | 240 μs - 260 μs               | 4B5B code-group /P/       |

| WAKE       | Tw     | 30 µs – 36 µs                  | 30 µs - 36 µs                 | 4B5B code-group /l/       |

A PHY transitions into the Low-Power state when the MAC asserts EEE LPI opcode on the TX PHY MAC pins. Periodic Refresh, a series of Sleep code-groups, is required to ensure link, maintain PLL lock (clock recovery) and signal equalization. When the MAC requests that the PHY exit LPI, IDLE code-groups will persist to inform the link partner that the device is transitioning into an active state.

## **Table 3. Transmit Opcodes**

| TX_EN | TX_ER | TXD[3:0]          | Function           |

|-------|-------|-------------------|--------------------|

| 0     | 0     | 0000 through 1111 | Normal Inter-Frame |

| 0     | 1     | 0                 | Reserved           |

| 0     | 1     | 1                 | EEE LPI            |

| 0     | 1     | 0010 through 1111 | Reserved           |

| 1     | 0     | 0000 through 1111 | Data Transmission  |

| 1     | 1     | 0000 through 1111 | Transmit Error     |

## **Table 4. Receive Opcodes**

| RX_DV | RX_ER | RXD[3:0]          | Function                   |

|-------|-------|-------------------|----------------------------|

| 0     | 0     | 0000 through 1111 | Normal Inter-Frame         |

| 0     | 1     | 0000              | Normal Inter-Frame         |

| 0     | 1     | 0001              | EEE LPI                    |

| 0     | 1     | 0010 through 1111 | Reserved                   |

| 0     | 1     | 1110              | False Carrier Indication   |

| 0     | 1     | 1111              | Reserved                   |

| 1     | 0     | 0000 through 1111 | Normal Data Reception      |

| 1     | 1     | 0000 through 1111 | Data Reception with Errors |

Once the MAC initiates the LPI request by presenting the EEE LPI opcode on the TX pins, the PHY is responsible for providing the correct 4B5B code-group that is used to inform the LP that it is going to enter into a Quiet state. When the LP receives the Sleep request, the LP is responsible for informing its MAC through the receive pins that LPI is to be initiated by the DUT.

# Table 5. 4B5B Code-Groups

| PCS code-group<br>[4:0]<br>4 3 2 1 0 | Name | MII<br>(TX[3:0]/RX[3:0])<br>3 2 1 0 | Interpretation                         |

|--------------------------------------|------|-------------------------------------|----------------------------------------|

| 11110                                | 0    | 0 0 0 0                             | Data 0                                 |

| 01001                                | 1    | 0 0 0 1                             | Data 1                                 |

| 10100                                | 2    | 0010                                | Data 2                                 |

| 10101                                | 3    | 0011                                | Data 3                                 |

| 01010                                | 4    | 0100                                | Data 4                                 |

| 01011                                | 5    | 0101                                | Data 5                                 |

| 01110                                | 6    | 0110                                | Data 6                                 |

| 01111                                | 7    | 0111                                | Data 7                                 |

| 10010                                | 8    | 1000                                | Data 8                                 |

| 10011                                | 9    | 1001                                | Data 9                                 |

| 10110                                | А    | 1010                                | Data A                                 |

| 10111                                | В    | 1011                                | Data B                                 |

| 11010                                | С    | 1 1 0 0                             | Data C                                 |

| 1 1 0 1 1                            | D    | 1 1 0 1                             | Data D                                 |

| 1 1 1 0 0                            | E    | 1110                                | Data E                                 |

| 11101                                | F    | 1111                                | Data F                                 |

| 11111                                | I    | Undefined                           | IDLE                                   |

| 00000                                | Р    | 0 0 0 1                             | SLEEP; Low-Power Idle                  |

| 11000                                | J    | 0101                                | Start-of-Stream Delimiter; Part 1 of 2 |

| 10001                                | К    | 0101                                | Start-of-Stream Delimiter; Part 2 of 2 |

| 01101                                | Т    | Undefined                           | End-of-Stream Delimiter; Part 1 of 2   |

| 00111                                | R    | Undefined                           | End-of-Stream Delimiter; Part 2 of 2   |

| 00100                                | Н    | Undefined                           | Transmit Error                         |

| 0 0 0 0 1                            | V    | Undefined                           | Invalid code                           |

| 00010                                | V    | Undefined                           | Invalid code                           |

| 0 0 0 1 1                            | V    | Undefined                           | Invalid code                           |

| 00101                                | V    | Undefined                           | Invalid code                           |

| 00110                                | V    | Undefined                           | Invalid code                           |

| 01000                                | V    | Undefined                           | Invalid code                           |

| 01100                                | V    | Undefined                           | Invalid code                           |

| 10000                                | V    | Undefined                           | Invalid code                           |

| 1 1 0 0 1                            | V    | Undefined                           | Invalid code                           |

www.ti.com

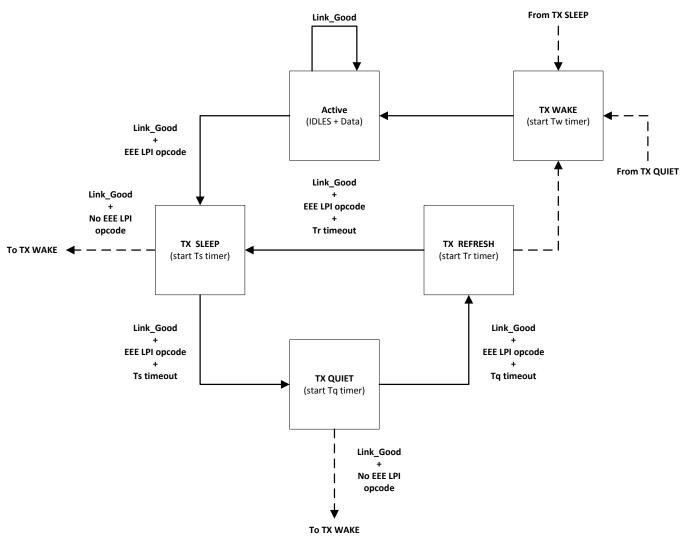

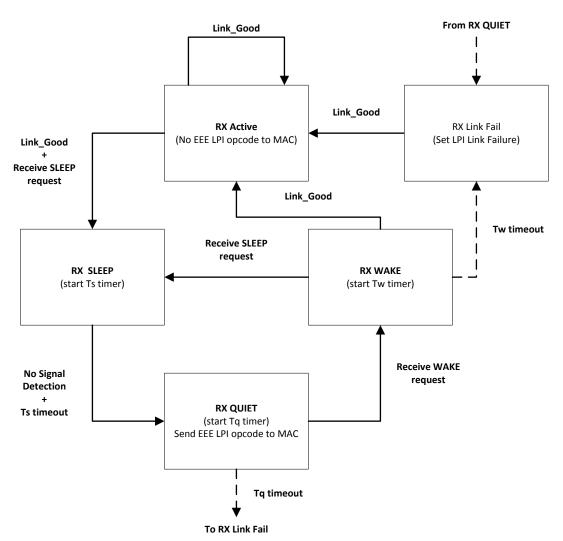

Figure 3 and Figure 4 show the progression of states for both transmit and receive paths when EEE LPI is enabled. Notice that at any point in the LPI state machine, a PHY can quickly exit out of the Low-Power mode and enter into an Active mode.

Figure 3. Transmit Path LPI State Diagram

## Figure 4. Receive Path LPI State Diagram

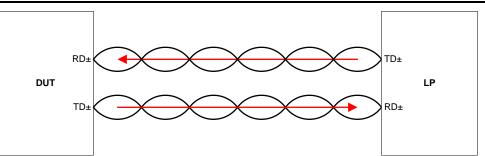

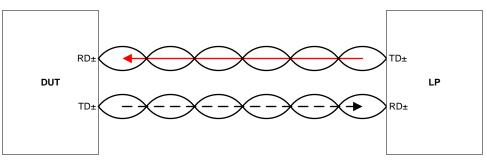

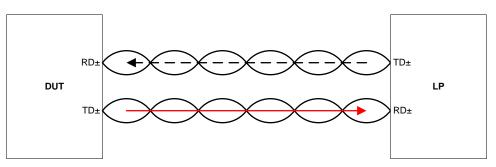

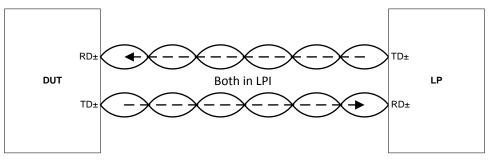

During Auto-Negotiation, PHYs capable of EEE operation at 100 Mbps speed advertise their abilities to inform their LPs. The exchange of abilities is part of NEXT PAGE advertisement. The control and status bits for EEE are found in MMD3 and MMD7 registers in the PHY's extended register set. Once both partners acknowledge EEE supported abilities, links can operate in any one of four combinations described in Figure 5, Figure 6, Figure 7 and Figure 8 for 100BASE-TX operation.

www.ti.com

Figure 5. Both Active

Figure 6. LP Active and DUT in LPI

Figure 7. LP in LPI and DUT Active

Figure 8. Both in LPI

Additionally, TX\_CLK and RX\_CLK can be stopped during LPI operation. Since TX and RX opcodes are static during LPI operation, there is no need to continually clock the digital signals. Power is lowered further by stopping these digital pins from toggling.

**Note**: MII only allows RX\_CLK to be stopped since TX\_CLK is an output from the PHY and is necessary to clock in the correct opcode. RGMII allows for both TX\_CLK and RX\_CLK to be stopped since RX\_CLK is an output from the PHY and TX\_CLK is an output from the MAC.

# 2.2 EEE - Implementation

EEE can be enabled through two different methods: hardware bootstrap and register configuration using the SMI.

# 2.2.1 Bootstrap Method

During RESET (either through power-cycle, RESET\_N pin activation or using bit [15] in the Basic Mode Control Register; register 0x001F), the DP83822 will configure all digital pins to tri-state for over 100 ms. During this time period, external or internal resistors on specified bootstrap pins will pull the pin to a desired voltage state. An internal comparator samples the state of each bootstrap pin and will configure the PHY to its intended function.

RX\_D1 (pin #31) is a dual purpose bootstrap pin, responsible for PHYAD\_2 and EEE\_EN bootstrap functions. Dual purpose bootstrap pins have four strap modes; Mode 1 through Mode 4. A default mode is assigned to each pin by use of weak internal pull resistors. RX\_D1 is by default Mode 1 and has the following configuration:

## Table 6. Bootstrap Mode 1

| Bootstrap Name | Setting | Function                              |

|----------------|---------|---------------------------------------|

| PHYAD_2        | 0       | PHY Address bit [2] is '0'            |

| EEE_EN         | 0       | Energy Efficient Ethernet is Disabled |

Only strap Mode 2 and Mode 3 will enable EEE advertisement functionality. The purpose for two modes to support EEE advertisement is because it allows for two different PHYAD\_2 fields to support EEE as well. The following two configurations support EEE:

## Table 7. Bootstrap Mode 2

| Bootstrap Name | Setting | Function                             |

|----------------|---------|--------------------------------------|

| PHYAD_2        | 0       | PHY Address bit [2] is '0'           |

| EEE_EN         | 1       | Energy Efficient Ethernet is Enabled |

## Table 8. Bootstrap Mode 3

| Bootstrap Name | Setting | Function                             |

|----------------|---------|--------------------------------------|

| PHYAD_2        | 1       | PHY Address bit [2] is '1'           |

| EEE_EN         | 1       | Energy Efficient Ethernet is Enabled |

## 2.2.2 Register Configuration Method

Additionally, EEE advertisement can be enabled using register configuration. The DP83822 offers two methods for enabling EEE advertisement depending on user preference.

The typical method is through MMD3 and MMD7 extended register sets. These register maps are only accessible when the correct Device Address (DEVAD) Register Control is used. DEVAD is found in register 0x000D (REGCR) bits [4:0]. Vendor specific DEVAD cannot access MMD3 and MMD7 extended register sets. The DP83822 uses the vendor specific DEVAD [4:0] = '11111' for accesses to register 0x04D1 and lower. For MMD3 access, the DEVAD [4:0] = '00011'. For MMD7 access, the DEVAD [4:0] = '00111'.

To configure the DP83822 for 100BASE-TX EEE Advertisement, use the following register write steps:

| Step | Register | Value | Description                                        |

|------|----------|-------|----------------------------------------------------|

| 1    | 000D     | 0007  | Access MMD7 through REGCR                          |

| 2    | 000E     | 003C  | Access Register 0x003C in MMD7                     |

| 3    | 000D     | 4007  | Write to Register 0x003C with no Post<br>Increment |

| 4    | 000D     | 0002  | Advertise 100BASE-TX EEE                           |

| 5    | 0000     | 3300  | Restart Auto-Negotiation                           |

Table 9. EEE 100BASE-TX Advertisement Configuration Steps

The DP83822 has an added feature that allows for EEE advertisement using the vendor specific DEVAD. Register 0x04D1 is a DP83822 vendor specific register that has the ability to bypass MMD3 and MMD7 extended registers. This feature allows for a simpler driver control since it allows for a single DEVAD to be used.

To configure the DP83822 for 100BASE-TX EEE Advertisement with vendor specific register 0x04D1, use the following register write steps:

| Table 10. EEE 100BASE-TX Advertisement | Vendor S | Specific Config | guration Steps |

|----------------------------------------|----------|-----------------|----------------|

|----------------------------------------|----------|-----------------|----------------|

| Step | Register | Value | Description              |

|------|----------|-------|--------------------------|

| 1    | 04D1     | 018F  | Advertise 100BASE-TX EEE |

| 5    | 0000     | 3300  | Restart Auto-Negotiation |

#### www.ti.com

# 2.2.3 EEE – DP83822 Waveform

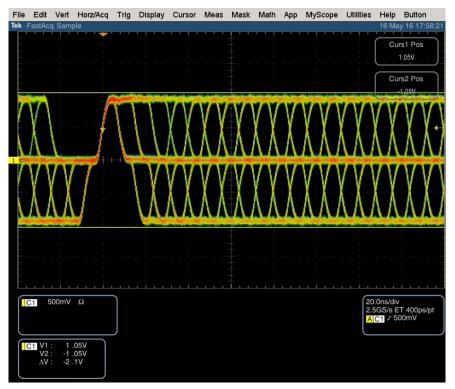

For reference, the DP83822 Eye diagram is shown in Figure 9. This was achieved by forcing the DP83822 into 100 Mbps with Auto-MDIX disabled. Upper and lower horizontal cursors are enabled to provide the IEEE802.3u min/max PMD amplitude limits.

**Note**: All images are using Tektronix FastAcq with positive edge trigger.

Figure 9. DP83822 Eye Diagram

A constant stream of IDLEs can be seen, which is expected for 100 Mbps operation as described in Section 2.1. There are three distinct levels to 100BASE-TX MLT-3 signaling; +1, 0 and -1. MLT-3 when viewed with variable persistence or infinite persistence will result in this stacked eye waveform.

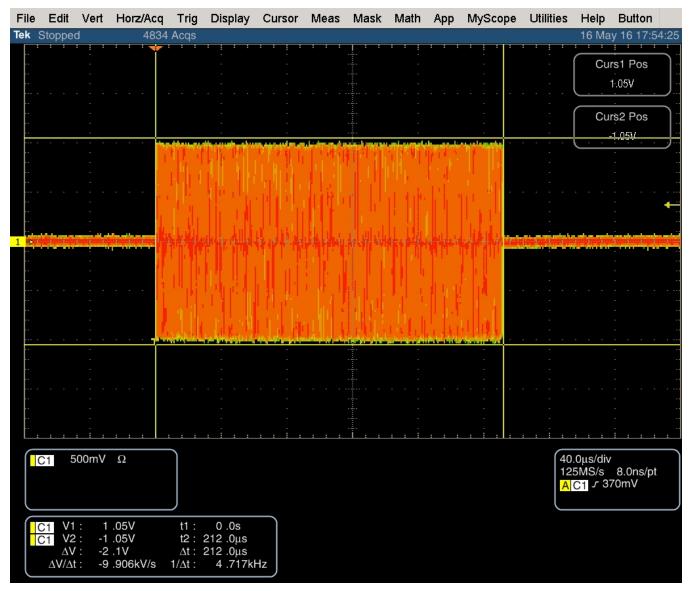

An image of the DP83822 Refresh can be seen in Figure 10. Upper and lower horizontal cursors are enabled to provide the IEEE802.3 min/max PMD amplitude limits. The positive edge trigger provides the starting reference point for the Refresh burst and a vertical cursor is placed on this location (t1). A second vertical cursor is placed at the end of the Refresh burst (t2). Total Refresh burst time is 212  $\mu$ s. This is well within the 200  $\mu$ s – 220  $\mu$ s Refresh burst time limits.

www.ti.com

Figure 10. Refresh Burst

Zoomed out views of DP83822 Refresh bursts can be seen in Figure 11 and Figure 12. The first image shows two Refresh bursts with horizontal and vertical cursors to show the IEEE limits described above. A vertical cursor is placed on the rising edge of the first Refresh burst (t1). The second vertical cursor is placed on the rising edge of the second Refresh burst (t2). The Quiet period is 22 ms. The DP83822 is configured for the maximum allowable quiet time, which provided the most energy savings.

| File         | Edit                          | Vert         | Horz/Acq                      | Trig                           | Display                                 | Cursor | Meas | Mask    | Math                        | Арр             | MyScope        | Utilities | Help                           | Button                                           |

|--------------|-------------------------------|--------------|-------------------------------|--------------------------------|-----------------------------------------|--------|------|---------|-----------------------------|-----------------|----------------|-----------|--------------------------------|--------------------------------------------------|

| Tek          | FastAco                       | q Samp       | ble                           |                                |                                         |        |      |         |                             |                 |                |           | 16 Ma                          | / 16 17:55:22                                    |

| ••           |                               | · · ·        |                               |                                |                                         |        |      |         |                             |                 |                |           | Cur                            | s1 Pos                                           |

| ···<br>··    |                               |              |                               |                                |                                         |        |      |         |                             |                 |                |           | <u> </u>                       | 0.0s                                             |

| <br><br>     |                               |              |                               |                                |                                         |        |      |         |                             |                 | -<br>-<br>-    |           | Cur                            | s2 Pos                                           |

|              |                               |              |                               |                                |                                         |        |      | <u></u> |                             |                 |                |           | 2                              | <u>2.0me</u>                                     |

|              |                               |              |                               |                                |                                         |        |      |         |                             |                 |                |           |                                |                                                  |

| <br>         |                               |              |                               |                                |                                         |        |      |         |                             |                 |                |           |                                |                                                  |

|              |                               |              |                               |                                |                                         |        |      |         |                             |                 | -              |           |                                | · • · ·                                          |

| 1 <b>⇒</b> ∎ |                               |              |                               |                                | ann à scanda<br>Isteileachta            |        |      |         | in de ministra<br>I - I - I | i inclusione in |                |           | i. i. i.                       | in han an a sa a sa i<br>Ing kan han han ing kan |

|              |                               | -<br>-<br>-  |                               |                                |                                         |        |      | ·       |                             |                 |                |           |                                |                                                  |

| <br><br>     |                               |              |                               |                                |                                         |        |      |         |                             |                 | ·<br>· · · · · |           |                                | · · · · · · · · ·                                |

| <br>         |                               |              |                               |                                |                                         |        |      |         |                             |                 |                |           |                                | <br>                                             |

|              |                               |              | <u>· · · •</u>                |                                |                                         |        |      |         |                             |                 | · · · · ·      |           |                                |                                                  |

| <br>         |                               |              |                               |                                |                                         |        |      |         |                             |                 |                |           |                                | · · ·                                            |

|              |                               |              |                               |                                |                                         |        |      |         |                             |                 | · · · ·        |           |                                | · · · · · · · · · · · · · · · · · · ·            |

| <br>         |                               |              |                               |                                |                                         |        |      |         |                             |                 |                |           |                                | <br>                                             |

|              | C1 5                          | 00mV         | Ω                             |                                |                                         |        |      |         |                             |                 |                | 25        | 0ms/div<br>.0MS/s<br><u>C1</u> | 40.0ns/pt<br>'0mV                                |

|              | C1 V1<br>C1 V2<br>ΔV<br>ΔV/Δt | : -1<br>: -2 | .05V<br>.05V<br>.1V<br>.45V/s | t1 :<br>t2 :<br>∆t :<br>1/∆t : | 0 .0s<br>22 .0ms<br>22 .0ms<br>45 .45Hz |        |      |         |                             |                 |                |           |                                |                                                  |

Figure 11. Two Refresh Bursts with Quiet Period

The second image shows four Refresh bursts with horizontal and vertical cursors to show the IEEE limits described above. A consistent Refresh burst is critical for maintaining quality link. DP83822 consistent timers can be seen in Figure 12. Again, a vertical cursor is placed on the rising edge of the first Refresh burst (t1). The second vertical cursor is placed on the rising edge of the second Refresh burst (t2). The Quiet period is 22 ms. All subsequent Quiet periods are 22 ms as well.

| File              | Edit                          | Vert            | Horz/Acq                      | Trig                           | Display                                 | Cursor  | Meas | Mask  | Math    | Арр | MyScope     | Utilities | Help                                     | Button          |

|-------------------|-------------------------------|-----------------|-------------------------------|--------------------------------|-----------------------------------------|---------|------|-------|---------|-----|-------------|-----------|------------------------------------------|-----------------|

| Tek               | =astAco                       | q Samp          | ole                           |                                |                                         |         |      |       |         |     |             |           |                                          | y 16 17:56:04   |

| <br><br>          |                               |                 |                               |                                |                                         |         |      |       |         |     |             |           | Cu                                       | 0.0s            |

| <br><br>          |                               | -               |                               |                                | ·<br>·<br>·                             |         |      | ····· | · · ·   |     | -<br>-<br>- | -         |                                          | rs2 Pos         |

| <br><br><br>      |                               |                 |                               |                                |                                         |         |      |       |         |     |             |           |                                          | · · · ·         |

| ••<br>••<br>••    | īī                            |                 |                               |                                |                                         |         |      |       |         |     |             |           |                                          |                 |

|                   |                               |                 |                               |                                | -                                       |         |      |       |         |     |             | -         |                                          |                 |

| <br><br>          |                               |                 |                               |                                |                                         |         |      |       |         |     |             |           |                                          | · · ·           |

| ··· ·<br>··<br>·· |                               | <br>-<br>-<br>- |                               |                                | · · · · ·                               | · · · · |      |       | · · · · |     | -           |           | · · ·                                    | · · · · · · · · |

| <br><br><br>      |                               |                 |                               |                                |                                         |         |      |       |         |     |             |           |                                          |                 |

|                   | : :<br>C1 5                   | : : :<br>00mV   | Ω                             |                                |                                         |         |      |       |         |     |             | 10        | : : :<br>.0ms/div<br>.0MS/s<br><u>C1</u> | 100ns/pt        |

|                   | 21 V1<br>21 V2<br>ΔV<br>ΔV/Δt | : -1<br>: -2    | .05V<br>.05V<br>.1V<br>.45V/s | t1 :<br>t2 :<br>∆t :<br>1/∆t : | 0 .0s<br>22 .0ms<br>22 .0ms<br>45 .45Hz |         |      |       |         |     |             |           |                                          |                 |

Figure 12. Four Refresh Bursts and Three Quiet Periods

# 3 Conclusion

This application note provided details on the principles behind EEE and the mechanisms to enable EEE in the DP83822.

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products<br>Audio<br>Amplifiers<br>Data Converters<br>DLP® Products | www.ti.com/audio<br>amplifier.ti.com<br>dataconverter.ti.com<br>www.dlp.com | Applications<br>Automotive and Transportation<br>Communications and Telecom<br>Computers and Peripherals<br>Consumer Electronics | www.ti.com/automotive<br>www.ti.com/communications<br>www.ti.com/computers<br>www.ti.com/consumer-apps |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| DSP                                                                 | dsp.ti.com                                                                  | Energy and Lighting                                                                                                              | www.ti.com/energy                                                                                      |

| Clocks and Timers                                                   | www.ti.com/clocks                                                           | Industrial                                                                                                                       | www.ti.com/industrial                                                                                  |

| Interface                                                           | interface.ti.com                                                            | Medical                                                                                                                          | www.ti.com/medical                                                                                     |

| Logic                                                               | logic.ti.com                                                                | Security                                                                                                                         | www.ti.com/security                                                                                    |

| Power Mgmt                                                          | power.ti.com                                                                | Space, Avionics and Defense                                                                                                      | www.ti.com/space-avionics-defense                                                                      |

| Microcontrollers                                                    | microcontroller.ti.com                                                      | Video and Imaging                                                                                                                | www.ti.com/video                                                                                       |

| RFID                                                                | www.ti-rfid.com                                                             |                                                                                                                                  |                                                                                                        |

| OMAP Applications Processors                                        | www.ti.com/omap                                                             | TI E2E Community                                                                                                                 | e2e.ti.com                                                                                             |

| Wireless Connectivity                                               | www.ti.com/wirelessconne                                                    | ctivity                                                                                                                          |                                                                                                        |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated