# Application Note Interfacing LVDS Driver With a Sub-LVDS Receiver

TEXAS INSTRUMENTS

#### ABSTRACT

Sub-LVDS is a reduced voltage version of the LVDS electrical specification. Sub-LVDS varies from LVDS in that its common mode and differential signal levels are reduced, but are still able to drive an LVDS receiver. The problem arises when an LVDS driver needs to interface with a sub-LVDS receiver. Since the drivers' signal voltage levels are not in a suitable range to ensure proper communication with the receiver, it is necessary to alter the drivers output to guarantee appropriate voltage levels. This application report discusses how to interface between an LVDS driver and sub-LVDS receiver and how a simple resistor network can be used to modify the signal voltage levels in a way to ensure compatibility.

## **Table of Contents**

| 1 Introduction                          | 2 |

|-----------------------------------------|---|

| 2 Simulation Setup                      |   |

| 3 Devices Without Termination Resistors |   |

| 4 Devices With Termination Resistors    |   |

| 5 Other Applications                    |   |

| 6 Summary                               |   |

| •                                       |   |

## **List of Figures**

| igure 2-1. Simulation Block Diagram                                     |

|-------------------------------------------------------------------------|

| igure 2-2. Schematic Breakdown                                          |

| igure 2-3. DS90LV011A Data Sheet Electrical Characteristics4            |

| igure 3-1. Equations for a Receiver Without Internal Termination5       |

| igure 3-2. Schematic for Receivers Without Internal Termination5        |

| igure 3-3. Simulation Results for Devices Without Internal Termination6 |

| igure 4-1. Equations for a Receiver With Internal Termination7          |

| igure 4-2. Schematic for Receivers With Internal Termination            |

| igure 4-3. Simulation Results for Devices With Internal Termination8    |

## List of Tables

| Table 1-1. LVDS Driver Output and Sub-LVDS Receiver Input | 2 |

|-----------------------------------------------------------|---|

| Table 2-1. SubLVDS Driver Electrical Specifications       | 4 |

| Table 2-2. SubLVDS Receiver Electrical Specifications     | 4 |

#### Trademarks

All trademarks are the property of their respective owners.

1

## 1 Introduction

In order to use an LVDS driver such as the TI DS90LV011A and pair it with a Sub-LVDS receiver, a step-down resistor network must be used in order to provide the proper interface between the LVDS driver and Sub-LVDS receiver. Since an LVDS driver has a typical fixed common mode voltage output of 1.2 V and typical differential voltage swing of 350 mV, the goal of the step-down resistor network is to achieve a fixed common mode voltage of 0.9 V as well as output differential voltage swing of 150 mV. Table 1-1 shows the differences between LVDS driver output levels and Sub-LVDS receiver input levels.

There are two methods in which you could implement this step-down resistor network. The method chosen depends on whether or not your receiver has internal termination integrated into it or not. The first section will focus on the formulas and simulations in a device without internal termination, while the second portion will focus on a device that includes internal termination.

|                                            | LVDS Driver Output Levels |     |      | SubLVDS Receiver Input Levels |     |     |      |

|--------------------------------------------|---------------------------|-----|------|-------------------------------|-----|-----|------|

| Parameter                                  | Min                       | Тур | Max  | Min                           | Тур | Max | Unit |

| V <sub>CMF</sub> Fixed Common Mode Voltage | 0.05                      | 1.2 | 2.35 | 0.5                           | 0.9 | 1.3 | V    |

| V <sub>OD</sub> Differential Voltage Swing | 247                       | 350 | 454  | 100                           | 150 | 200 | mV   |

| V <sub>TH</sub> Threshold Voltage          |                           |     |      | -25                           |     | 25  | mV   |

| Table 1-1. LVD | S Driver | · Output and | Sub-LVDS | <b>Receiver</b> I | nput |

|----------------|----------|--------------|----------|-------------------|------|

|----------------|----------|--------------|----------|-------------------|------|

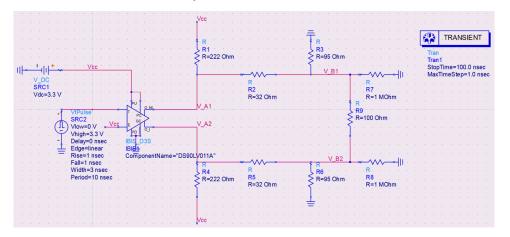

## 2 Simulation Setup

The simulations will be done using Keysight ADS with the TI DS90LV011A IBIS model (ds90lv001atmf.ibs) that can be downloaded from the URL: .

Figure 2-1. Simulation Block Diagram

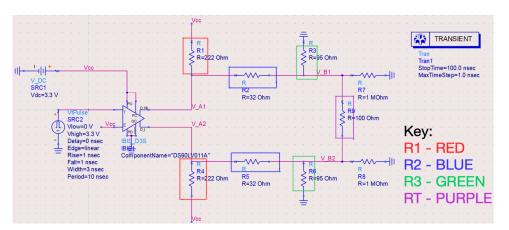

Figure 2-2. Schematic Breakdown

- R<sub>1</sub>, R<sub>2</sub>, & R<sub>3</sub> make up the resistor network that needs to be created to interface between LVDS and Sub-LVDS. Each differential pair will be made up of these three resistors.

- R<sub>T</sub> is the value of the termination resistor for devices that contain internal termination (100Ω will be used for this simulation).

- R<sub>E</sub> is the equivalent resistance of all the resistors in the resistor network

#### Note

The Thevenin resistance of these resistors must be approximately  $50\Omega$  if the device does or does not contain internal termination; this ensures that the circuit will have a  $100\Omega$  equivalent termination resistance between the transmitter and receiver for both differential pairs. The appropriate formulas for each scenario can be seen in the sections below.

- V<sub>A</sub> is equivalent to the fixed common mode voltage (V<sub>CMF</sub>) of the LVDS driver output (1.2 V will be used for this simulation).

- V<sub>OD</sub> is the output differential voltage from the LVDS driver.

- The values used can be obtained from the "Electrical Characteristics" section of the data sheet for your specific device.

- For more information, see the DS90LV011A 3V LVDS Single High Speed Differential Driver Data Sheet.

| www.ti.com       |                                                             |                                                  |                              | SN              | LS140C -M | AY 2002-1 | REVISED A | PRIL 2 |

|------------------|-------------------------------------------------------------|--------------------------------------------------|------------------------------|-----------------|-----------|-----------|-----------|--------|

| Electric         | al Characteristics                                          |                                                  |                              |                 |           |           |           |        |

| Over Supp        | bly Voltage and Operating Tempe                             | rature ranges.                                   | unless otherwise speci       | fied, (1)(2)(3) |           |           |           |        |

| Symbol           | Parameter                                                   |                                                  | Conditions                   | Pin             | Min       | Тур       | Max       | Unit   |

| Vool             | Output Differential Voltage                                 | R <sub>L</sub> = 100Q<br>(Figure 2 and Figure 3) |                              | OUT+,           | 250       | 350       | 450       | mV     |

| ΔV <sub>OD</sub> | Vop Magnitude Change                                        |                                                  |                              | OUT-            |           | 3         | 35        | mV     |

| Vos              | Offset Voltage                                              | R <sub>I</sub> = 100Ω<br>(Figure 2)              |                              | 7               | 1.125     | 1.22      | 1.375     | V      |

| ΔV <sub>OS</sub> | Offset Magnitude Change                                     |                                                  |                              |                 | 0         | 1         | 25        | mV     |

| LOFF             | Power-off Leakage                                           | Vout = 3.6V                                      | or GND, V <sub>DD</sub> = 0V | 1               |           | ±1        | ±10       | μΑ     |

| los              | Output Short Circuit Current <sup>(4)</sup>                 | VOUT+ and V                                      | VOUT+ and VOUT- = 0V         |                 |           | -6        | -24       | mA     |

| losp             | Differential Output Short Circuit<br>Current <sup>(4)</sup> | V <sub>OD</sub> = 0V                             |                              |                 |           | -5        | -12       | mA     |

| COUT             | Output Capacitance                                          |                                                  |                              |                 |           | 3         |           | pF     |

| VIH              | Input High Voltage                                          |                                                  |                              | TTL IN          | 2.0       |           | VDD       | V      |

| VIL              | Input Low Voltage                                           |                                                  |                              |                 | GND       |           | 0.8       | V      |

| l <sub>H</sub>   | Input High Current                                          | V <sub>IN</sub> = 3.3V or                        | r 2.4V                       |                 |           | ±2        | ±10       | μΑ     |

| IL.              | Input Low Current                                           | VIN = GND o                                      | r 0.5V                       |                 |           | ±1        | ±10       | μA     |

| VCL              | Input Clamp Voltage                                         | I <sub>CL</sub> = -18 mA                         | 1                            |                 | -1.5      | -0.6      |           | V      |

| CIN              | Input Capacitance                                           |                                                  | dia to a dia                 |                 |           | 3         |           | pF     |

| loo              | Power Supply Current                                        | No Load                                          | VIN = VDD or GND             | V <sub>DD</sub> |           | 5         | 8         | mA     |

|                  |                                                             | R <sub>L</sub> = 100Ω                            |                              |                 |           | 7         | 10        | mA     |

(d) Outputs.

(e) Outputs hort circuit current (los) is specified as magnitude only, minus sign indicates direction only

### Figure 2-3. DS90LV011A Data Sheet Electrical Characteristics

- V<sub>B</sub> is equivalent to the fixed common mode voltage (V<sub>CMF</sub>) of typical Sub-LVDS driver outputs (0.9V will be used for this simulation).

- V<sub>ID</sub> is the output differential voltage of a Sub-LVDS driver. The goal of the simulation is to obtain a value in the operating range for Sub-LVDS transmitters.

- The values for a Sub-LVDS driver output can be seen in Table 2-1.

- The values for a Sub-LVDS receiver input can be seein in Table 2-2.

#### Table 2-1. SubLVDS Driver Electrical Specifications

|                                            | SubLVDS Driver Output Levels |     |     |      |  |

|--------------------------------------------|------------------------------|-----|-----|------|--|

| Parameter                                  | Min                          | Тур | Max | Unit |  |

| V <sub>CMF</sub> Fixed Common Mode Voltage | 0.8                          | 0.9 | 1   | V    |  |

| V <sub>OD</sub> Differential Voltage Swing | 100                          | 150 | 200 | mV   |  |

#### Table 2-2. SubLVDS Receiver Electrical Specifications

|                              | SubLVDS Receiver Input Levels |     |     |      |  |  |  |  |

|------------------------------|-------------------------------|-----|-----|------|--|--|--|--|

| Parameter                    | Min                           | Тур | Max | Unit |  |  |  |  |

| Input Voltage                | 0.5                           | 0.9 | 1.3 | V    |  |  |  |  |

| Threshold Voltage            | -25                           |     | 25  | mV   |  |  |  |  |

| Termination Resistance Value | 80                            | 100 | 120 | Ω    |  |  |  |  |

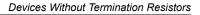

### **3 Devices Without Termination Resistors**

- Verify in your data sheet whether the receiver that you are using for your design contains an internal termination resistor. The formulas used are similar to obtain values with small differences taking the termination resistor into consideration.

- If your device does not contain internal termination then the equations shown in Figure 3-1 will be used.

a.

$$V_A = \frac{R_2 + R_3}{R_1 + R_2 + R_3} \times V_{CC}$$

b.  $V_B = \frac{R_3}{R_2 + R_3} \times V_A$

c.  $R_E = R_1 || (R_2 + R_3)$

d.  $V_{ID} = \frac{R_3}{R_2 + R_3} \times V_{OD}$ ,100 mV >  $V_{ID}$  > 200 mV

#### Figure 3-1. Equations for a Receiver Without Internal Termination

- For the simulation, the following values will be used:

- V<sub>CC</sub> = 3.3 V

- V<sub>A</sub> = 1.2 V, LVDS driver output fixed common mode voltage

- V<sub>B</sub> = 0.9 V, Sub-LVDS driver output fixed common mode voltage

- $-R_{E} = 50\Omega$

- Using the formulas a, b, and c from Section 2, create a system of equations in order to solve for the resistance values that will best fit the desired parameters for Sub-LVDS. The following values were obtained from the system of equations:

- $R_1 = 110\Omega$

- $R_2 = 35\Omega$

- $R_3 = 50\Omega$

Now proceed to simulate the circuit in order to verify the behavior.

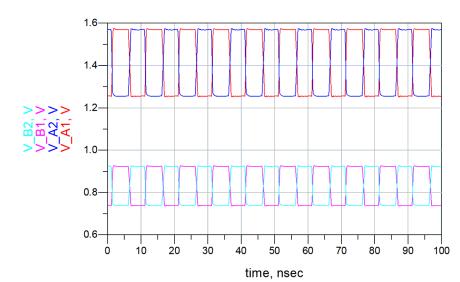

Figure 3-2. Schematic for Receivers Without Internal Termination

#### Note

$R_7$  and  $R_8$  are used to imitate the high impedance inputs of a receiver.

- The simulation shown in Figure 3-3 demonstrates a voltage swing of approximately:

- V<sub>ID</sub> ≈ 185 mV

- V<sub>OD</sub> ≈ 320 mV

- $V_{ID}$  falls within the desired range. If the formulas are used to obtain values for  $V_{ID}$ ,  $V_{CMF}$ , and  $R_E$  with the resistor values and the measured values for  $V_{OD}$  &  $V_A$ , then the following results can be obtained:

- V<sub>ID</sub> = 188 mV

- $-V_{\rm B} = 0.85 \,\rm V$

$-R_{E} = 48\Omega$

Figure 3-3. Simulation Results for Devices Without Internal Termination

### **4 Devices With Termination Resistors**

- The following scenario is used when the device that is being used for the receiver already contains a termination resistor. The process and the equations are roughly the same with just a few adjustments due to the added resistance. Ensure that the receiver being used contains a termination resistor and obtains the value of the resistance from the data sheet.

- If your device does contains internal termination, then the equations shown in Figure 4-1 will be used.

a.

$$V_A = \frac{R_2 + R_3}{R_1 + R_2 + R_3} \times V_{CC}$$

b.  $V_B = \frac{R_3}{R_2 + R_3} \times V_A$

c.  $R_E = R_1 || \left( R_2 + \left( R_3 || \frac{R_T}{2} \right) \right)$

d.  $V_{ID} = \frac{\left( R_3 || \frac{R_T}{2} \right)}{R_2 + \left( R_3 || \frac{R_T}{2} \right)} \times V_{OD}, 100 \text{ mV} > V_{ID} > 200 \text{ mV}$

#### Figure 4-1. Equations for a Receiver With Internal Termination

- For the simulation, the following values will be used:

- $-V_{CC} = 3.3 V$

- V<sub>A</sub> = 1.2 V, LVDS driver output fixed common mode voltage

- V<sub>B</sub> = 0.9 V, Sub-LVDS driver output fixed common mode voltage

- $R_{E}^{-} = 50\Omega$

- $-R_{T}^{-}$  = 100 $\Omega$ , value of termination resistor inside device

- Using the formulas a, b, and c from Section 2 creates a system of equations in order to solve for the

resistance values that will best fit the desired parameters for Sub-LVDS. The following values were obtained

from the system of equations:

- $R_1 = 222\Omega$

- $-R_{2} = 32\Omega$

- $R_3 = 95\Omega$

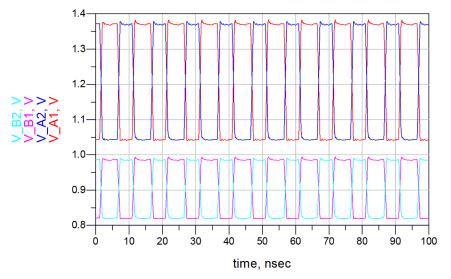

Proceed to simulate the circuit in order to verify the correct behavior.

Figure 4-2. Schematic for Receivers With Internal Termination

**Note** Resistors  $R_7$  and  $R_8$  are used to imitate the high impedance inputs of a receiver.

The simulation shown in Figure 4-3 demonstrates a voltage swing of approximately:

7

– V<sub>ID</sub> ≈ 160 mV

- V<sub>ID</sub> falls within the desired range. If the formulas are used to obtain values for V<sub>ID</sub>, V<sub>CMF</sub>, and R<sub>E</sub> with the resistor values and the measured values for V<sub>OD</sub> and V<sub>A</sub> then we obtain the following results:

- V<sub>ID</sub> = 163 mV

- $-V_{B} = 0.9 V$

- $-R_{\rm F}=50\Omega$

Figure 4-3. Simulation Results for Devices With Internal Termination

### **5** Other Applications

The method described above specifically details how to apply the step-down resistor network in order to interface between an LVDS driver and the sub-LVDS receiver. It may be useful to note that the same network can also be used to interface between an LVPECL driver and an LVDS receiver. The formulas used are the same, the main difference comes in the values used in the formulas. The values for an LVPECL driver output and an LVDS receiver would instead replace the values used in the calculations in order to solve for the ideal resistor values used in the network.

### 6 Summary

In conclusion, using a simple resistor network to interface between an LVDS driver and a sub-LVDS receiver is a viable and economical option to support the lower signal voltage levels required by a sub-LVDS receiver.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated