# OA-22 Pushing Low Quiescent Power Op Amps to Greater Than 55dBM 2-Tone Intercept

#### **ABSTRACT**

It is commonly expected that very low distortion amplifiers must dissipate considerable quiescent power to achieve their high linearity. With the advent of intrinsically low distortion current feedback op amps, along with the linearity improvements achieved by the negative feedback used in these devices, wideband low distortion amplifiers have become available at much lower quiescent power levels. This application report focuses on the 2-tone, 3rd order intermodulation distortion of current feedback amplifiers. Following a brief review the harmonic distortion mechanisms of current feedback op amps, a simple means to further improve an already high intercept is described. Having pushed the 3rd order spurious levels into the noise, an automated means of measuring these very low distortion levels is described.

#### Contents

| 1  | Harmonic Distortion in a Current Feedback Amplifier                            | 2  |

|----|--------------------------------------------------------------------------------|----|

| 2  | Distortion Mechanism's in Current Feedback Amplifiers                          | 4  |

| 3  | Improving Distortion by Shaping the Loop Gain                                  |    |

| 4  | Measuring 2-Tone, 3rd Order Intercepts above 50dBm                             |    |

| 5  | Test Results for the Improved Intercept Amplifier                              |    |

| 6  | Conclusions                                                                    |    |

| 7  | References                                                                     |    |

| 8  | Notes                                                                          | 21 |

|    | List of Figures                                                                |    |

| 1  | Simplified Current Feedback Topology                                           | 3  |

| 2  | Closed-Loop Transfer Function                                                  | 4  |

| 3  | Loop Gain Effect on Non-Linearity                                              | 5  |

| 4  | Control Theory Model of Distortion                                             | 6  |

| 5  | Forward and Feedback Transimpedance                                            | 7  |

| 6  | 2-tone, 3rd Order Intercept vs. Quiescent Power (dBm)                          | 8  |

| 7  | Loop Gain Shaping Network                                                      | 9  |

| 8  | Transfer Function for Parallel and Inductor Coupled Feedback                   | 10 |

| 9  | Loop Gain Analysis for Parallel and Inductor Coupled Feedback                  | 11 |

| 10 | Forward Transimpedance with Shaped Feedback Showing Increased Loop Gain        | 12 |

| 11 | Test Circuit for Increasing Loop Gain                                          | 13 |

| 12 | Measured Frequency Response for Wide Dynamic Range Test Circuit Using a CLC221 | 14 |

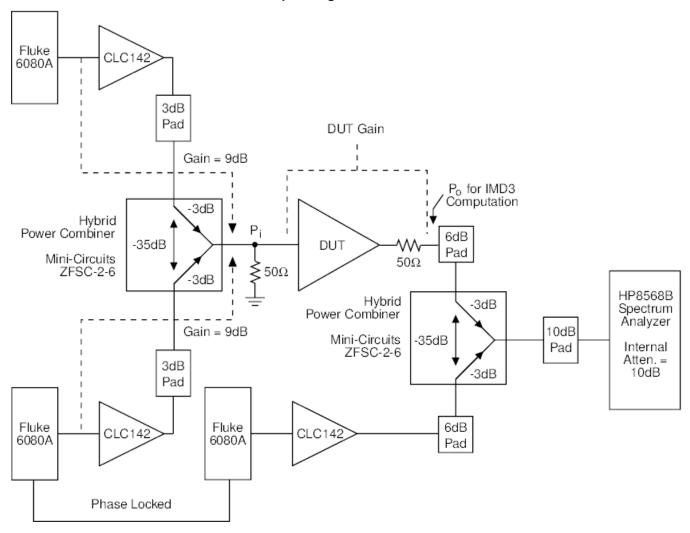

| 13 | Intermod Test Setup                                                            | 15 |

| 14 | Improved Dynamic Range Intermod Test Setup                                     | 16 |

| 15 | Test Power Levels for 10MHz Test                                               | 17 |

| 16 | Spurious Measurement at 10.3MHz                                                | 18 |

| 17 | Test Power Levels at the Analyzer with Single-Tone Cancellation                | 19 |

| 10 | · · · · · · · · · · · · · · · · · · ·                                          | 20 |

All trademarks are the property of their respective owners.

## 1 Harmonic Distortion in a Current Feedback Amplifier

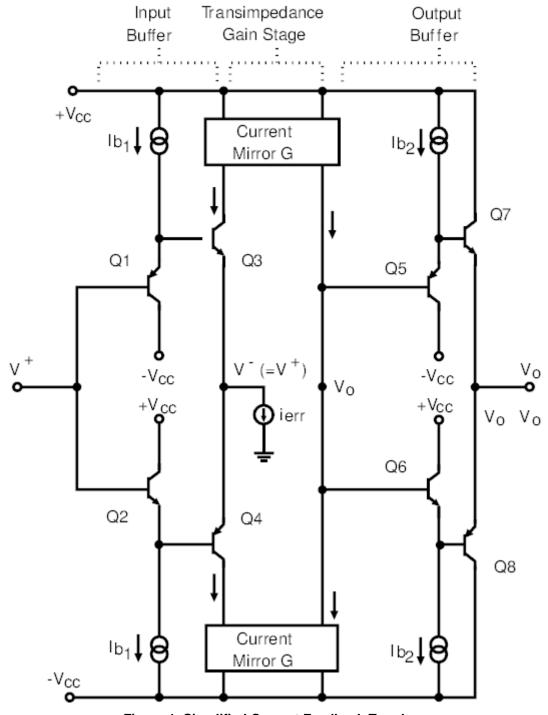

Figure 1 shows a simplified internal circuit for a current feedback operational amplifier. Note that the structure is very symmetric with complementary NPN and PNP devices. The input buffer stage, Q1-Q4, forms an open loop voltage buffer from the non-inverting input to the inverting pin. Transistors Q3 and Q4 provide a means to simultaneously drive the inverting node voltage and cascode an error current signal through their collectors to a current mirror stage. The outputs of the two symmetric current mirror stages are fed back together to form the high transimpedance node for the amplifier. This is the high gain node for the amplifier. Small changes in the error current (fed back through Q3 and Q4) will have a significant transimpedance gain to a voltage at the outputs of the two current mirrors. This voltage (V<sub>o</sub>') is buffered to the output pin by another open loop voltage buffer, transistors Q5-Q8. This buffer's high input impedance contributes to achieving a high forward transimpedance gain through the amplifier while providing a low impedance output drive. Both the input buffer and the output buffer are essentially Class AB buffer stages (see reference [1] for a more complete description of a current feedback op amp).

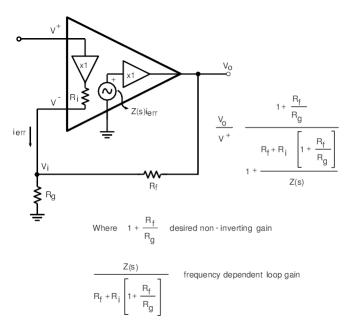

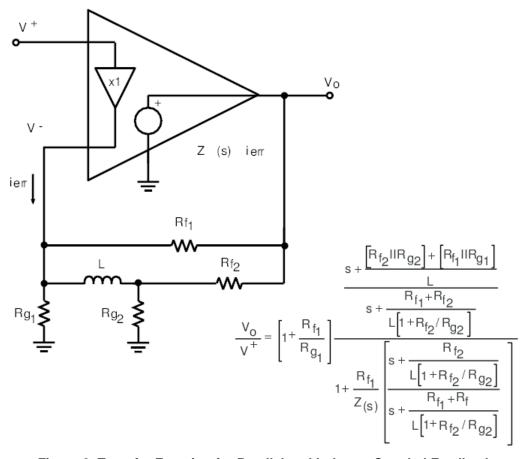

To this point, the amplifier's internal elements have been treated from an open loop standpoint. When the output is connected back to the inverting input through a feedback resistor, with a gain setting resistor to ground on the inverting node, we get the closed loop op amp configuration. Figure 2 shows the closed loop current feedback op amp block diagram along with the resulting transfer function.

Looking at the transfer function, the numerator expression is our desired signal gain in Volts/Volts. While the denominator expression represents the error terms due to a finite forward gain in the amplifier. If the forward transimpedance gain, Z(s), were infinite, this error term would drop out and the amplifier would produce exactly the gain shown in the numerator. The forward transimpedance is, however, a frequency dependent gain, having a very large value at DC with a dominant low frequency pole along with higher frequency poles (see Texas Instruments op-amp data sheets for open loop transimpedance plots). When the magnitude of Z(s) has rolled off to equal the value of the feedback transimpedance ( $R_f + R_i \times (1 + R_f/R_g)$ ), the loop gain has dropped to one and the overall amplifier frequency response begins to roll off. The  $R_i \times (1 + R_f/R_g)$  part of the feedback transimpedance is the principal parasitic effect limiting the amplifier's bandwidth as higher closed loop  $(1 + R_f/R_g)$  gains are desired ( $R_i$  is the output impedance of the buffer driving out of the inverting node). For the remainder of this discussion this  $R_i$  term will be set to zero leaving the feedback transimpedance set by only  $R_f$ .

One of the basic advantages offered by the current feedback topology is that, with the loop gain, and hence the frequency response, set externally by  $R_{\rm f}$ , the desired signal gain may be set by  $R_{\rm g}$  with minimal impact on the frequency response. It is through this mechanism that the current feedback op amp is said to offer a Gain-Bandwidth product "independence". For a more complete discussion of the current feedback transfer function and frequency response control, see reference [4].

Figure 1. Simplified Current Feedback Topology

Figure 2. Closed-Loop Transfer Function

# 2 Distortion Mechanism's in Current Feedback Amplifiers

From an open loop standpoint, harmonic distortion arises from any non-linearities in going from the inverting error current signal to the output voltage. Although we have shown this transimpedance gain to be a frequency dependent linear gain, Z(s), at any particular frequency, Z can actually be represented by a polynomial expression from the error current to the output voltage. This polynomial will have a very high linear gain term (at low frequencies) with relatively small coefficients for the higher order terms.

The signal path from the inverting input to the output follows two symmetric paths as shown in Figure 1. The open loop 2nd order coefficient is set by any transfer mismatches between the upper and lower signal paths to the output. The open loop 3rd order coefficient is principally set by the 3rd order curvature (crossover distortion) in the transfer function of the Class AB output buffer. (See reference [2], page 694 for a discussion of Class AB buffer distortion).

With the 2nd order distortion arising from mismatch effects, it is often observed that this distortion is strongly dependent on the DC operating point at the output. Changing the relative voltages across the two halves of the forward gain path will effect the balance of the parasitic effects (voltage dependent base-collector capacitance and output impedances) that give rise to this non-linearity. Similarly, for a ground centered, sinusoidal, output swing, inbalancing the power supplies can be used to null the 2nd harmonic at a specific frequency.

The magnitude of the open loop 3rd harmonic distortion term, at a given frequency, is principally a function of the output load current vs. the biasing current,  $I_{b2}$ , in the output stage. Hence, as signal swings go up, load resistors go down, or quiescent biasing current goes down, this third order distortion will increase. Conversely, as the load impedance increases, the signal swing decreases, or the quiescent biasing current increases, this 3rd order distortion will be decreased.

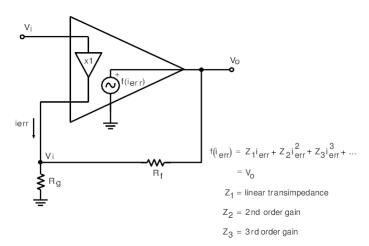

The intrinsic symmetry of the forward gain path, with well matched PNP and NPN signal paths, along with the fully complementary Class AB output buffer, yields low open loop distortion. This distortion is further reduced by the action of the negative feedback when the loop is closed (as shown in Figure 2). At a particular frequency, Z(s) can be taken to have specific values for the coefficients of a polynomial approximation to the transimpedance gain from the inverting error current to the output voltage. Figure 3 steps through a transfer function development using a polynomial expression for the forward transimpedance gain. Although this approach does not yield a closed form solution for the output voltage polynomial vs. an input signal, it does illustrate the loop gain dependence of the higher order terms.

Figure 3. Loop Gain Effect on Non-Linearity

Summing currents at the inverting node:

$$\begin{bmatrix} \frac{V_{i}}{R_{g}} = i_{err} + \frac{V_{o}}{R_{f}} \end{bmatrix} R_{f} \quad \text{,multiplying through by } R_{f} \text{ and grouping terms}$$

$$V_{i} \begin{bmatrix} 1 + \frac{R_{f}}{R_{g}} \end{bmatrix} + R_{f} I_{err} + V_{o}$$

$$(1)$$

From the above expression for V<sub>O</sub> (using the first three terms):

$$i_{err} = \frac{V_o}{Z_1} \frac{Z_2}{Z_1} i_{err}^2 \frac{Z_3}{Z_1} i_{err}^3$$

(2)

Should isolate and solve for  $i_{err}$  polynomial here, but this does not yield a very clear result. Simply putting this  $i_{err}$  expression into the above expression:

$$\sqrt{[-\frac{n}{2}]^2} \sqrt{[-\frac{n}{2}]^2} \sqrt{[-\frac{n}{2}]$$

Then, solving for  $V_{\Omega}$ :

$$V_0 = V_1 \frac{1 - \frac{R_1}{R_g}}{1 - \frac{R_1}{Z_1}} = \frac{Z_2}{Z_1/R_g} i_{err}^3 - \frac{Z_3}{Z_1/R_g} i_{err}^3$$

where  $\frac{Z_1}{R_g}$  - Loop gain (4)

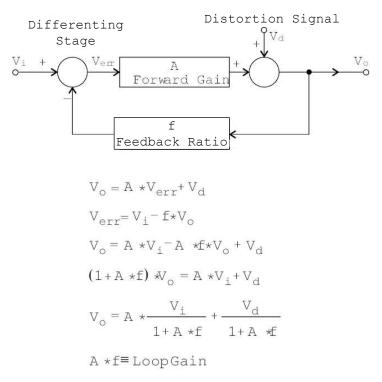

A more common way to show the effect of negative feedback on forward gain distortion effects is to introduce an error signal at the output of the forward gain block. Figure 4 shows this control theory approach with a similar result to Figure 3 - open loop distortion effects are reduced by the loop gain in a negative feedback closed loop configuration. This approach also does not reach a closed form solution for  $V_o$ , ( $V_d$  should actually depend on  $V_i$ ).

Figure 4. Control Theory Model of Distortion

For a single frequency input, it is the loop gain at the fundamental frequency that is applicable to determining the loop gain's impact on the distortion. Some of the literature seems to imply that it is the loop gain at the harmonics that is acting to linearize the closed loop performance to decrease the distortion (reference [2], page 418). However, testing with a loop gain tailored to be higher at the fundamental than at the harmonics has shown a direct dependence on the loop gain at the fundamental, but not at the harmonics.

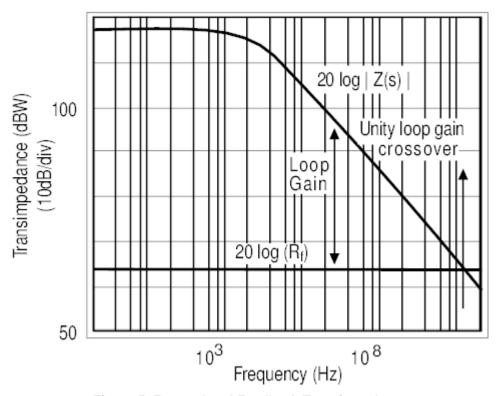

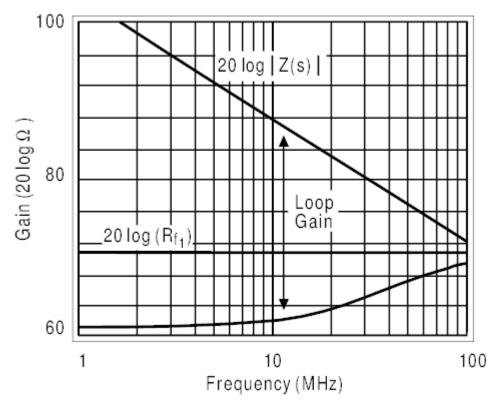

For the 3rd order terms, the achievable harmonic and 2-tone, intermod, distortion levels are set by the intrinsic 3rd order distortion of the output buffer and the loop gain at the fundamental frequency of operation. Figure 5 shows a Bode plot of the frequency dependent forward transimpedance,  $20 \times \log(|Z(s)|)$ , for a typical current feedback amplifier. The solid horizontal line intersecting this plot at about 100 MHz is  $20 \times \log(R_f)$ , the feedback transimpedance. The vertical distance between the forward Z(s) and this solid horizontal line is the loop gain,  $|Z(s)|/R_f$ .

As is apparent from Figure 5, this loop gain decreases with increasing frequency as the forward transimpedance gain rolls off. The intersection of Z(s) and the feedback transimpedance is of critical importance in determining the closed loop frequency response flatness. This decreasing loop gain with frequency is the dominant cause for an increase in harmonic distortion with increasing frequency for negative feedback amplifiers. One of the key contributions of the current feedback amplifier is the ability to use higher loop gains to higher frequencies than for equivalent voltage feedback parts. Typically, however, we still see the 3rd order distortion terms starting to increase, for a given output power level and gain, for frequencies above 5MHz. Conversely, as operating frequencies go below about 5MHz, the distortion performance typically reaches a minimum value in the region of the dominant open loop pole.

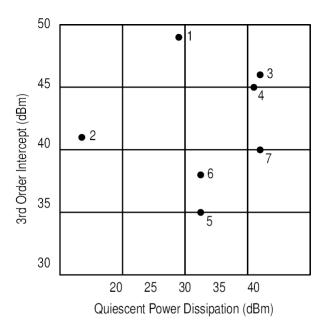

Figure 5. Forward and Feedback Transimpedance

As a point of comparison, this discussion will focus on the 2-tone 3rd order intermodulation distortion at 10MHz. Figure 6 shows a plot of 3rd order intercept (at 10MHz) vs. quiescent power dissipation (in dBm) for two current feedback amplifiers along with several other high linearity amplifiers. Many of these other amplifiers use a Class A output which requires significantly higher quiescent power to achieve low distortion. Also, minimal feedback, and hence minimal distortion improvement due to loop gain, is generally used in these other parts. This yields a distortion performance that is not nearly as frequency dependent. Basically, these Class A output amplifiers have driven the forward path non-linearities down with high quiescent currents and used minimal feedback to keep their distortion performance constant over a wider frequency range.

The data of Figure 6 shows that, for HF frequencies, considerably higher intercepts per mW of quiescent dissipation can be achieved with current feedback op amps through the use of a very linear forward gain path and high loop gain in the feedback network. The principal drawbacks to using the current feedback op amp in an HF or RF application is a steadily decreasing intercept above 5MHz, usable bandwidths limited to about 100MHz, and relatively poor noise performance. Intercepts have typically dropped to below 30dBm by 50MHz for the Texas Instruments op amps shown in Figure 6 (note [1])

National CLC221

National CLC401

Advancd Milliwave Lab ARO1003252

Adams Russell AM-109

Avantek UTO-509

Watkins Johnson WJ-A59

Q-Bit QB-210

Figure 6. 2-tone, 3rd Order Intercept vs. Quiescent Power (dBm)

# 3 Improving Distortion by Shaping the Loop Gain

Since a current feedback amplifier allows the loop gain to be set separately from the signal gain, it should be possible to adjust the loop gain to yield an improved distortion performance without changing the signal gain. The simplest way to do this would be to scale the resistor values down, keeping the same ratio for  $R_f$ . Decreasing  $R_f$  will increase the loop gain over the full frequency range, but runs the risk of inadequate phase margin at the crossover, where  $|Z(s)| = R_f$ . It would be preferable to decrease the feedback transimpedance at lower frequencies but return to the nominal design value for  $R_f$  where this feedback R is intended to equal Z(s).

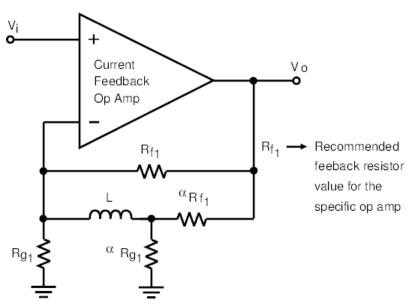

Figure 7 shows one possible circuit that achieves this loop gain shaping. This circuit was originally reported in the literature as a means to improve the equivalent input noise (reference [3]). At low closed loop gain settings, the relatively large inverting input current noise for a current feedback amplifier can dominate the overall noise performance. This noise current shows up at the output pin multiplied by the feedback resistor. The circuit of Figure 7 reduces the feedback resistor by using a parallel combination of the two feedback resistors as the low frequency gain for this noise current. The coupling inductor is set to remove this parallel feedback path before the unity loop gain crossover frequency (where  $Z(s) = R_{f1}$ ) with approximately 60 degree phase margin.

Figure 7. Loop Gain Shaping Network

Figure 8 shows a generalized transfer function for the circuit of Figure 7. In general, this circuit could be used to shape both the loop gain and the forward signal gain. At low frequencies, the gain is set by the parallel combination of the two  $R_{\rm g}$ 's divided by the parallel combination of the two  $R_{\rm g}$ 's. At high frequencies, once the inductor has opened up the connection between the two feedback's, the gain is simply  $(1 + R_{\rm fl}/R_{\rm gl})$ . Similarly, the feedback transimpedance at low frequencies is the parallel combination of the two feedback R's while at high frequencies it has increased to equal  $R_{\rm fl}$ . In going from low to high frequencies, this circuit shows a zero/pole pair for both the signal gain and the feedback transimpedance.

Figure 8. Transfer Function for Parallel and Inductor Coupled Feedback

For this loop gain shaping application, we will take the ratio of  $R_{\rm fl}/R_{\rm g1}=R_{\rm f2}/R_{\rm g2}$ . Under this condition, the numerator of the transfer function in Figure 8 simplifies to equal 1+  $R_{\rm fl}/R_{\rm g1}$  indicating a flat frequency response up to the roll-off frequency. The principle concern here is the frequency dependence of the feedback transimpedance. The loop gain has been increased due to the decreased feedback transimpedance at low frequencies which should provide an improved harmonic distortion performance. The feedback transimpedance now shows a zero/pole pair due to the inductor coupling the two feedback paths together. Figure 9 shows an analysis of the loop gain for this parallel, inductor coupled, feedback to set the pole and zero frequencies.

With

$$1 + \frac{R_{f_1}}{R_{g_1}} = 1 + \frac{R_{f_2}}{R_{g_2}} = A_v$$

,

Let

$$R_{f_2} = \alpha R_{f_1}$$

; Normally  $\alpha \le 1$

Rewriting the Loop Gain in terms of  $\alpha$  and A,

$$\begin{array}{c|c} \text{Loop gain} & \frac{Z(s)}{s + \dfrac{R_{f_1} \alpha}{L \, A_{\nu}}} & \frac{\text{forward transimpedance}}{\text{feedback transimpedance}} \\ R_{f_1} & \frac{s + \dfrac{R_{f_1} (1 + \alpha)}{L \, A_{\nu}}}{s + \dfrac{R_{f_1} (1 + \alpha)}{L \, A_{\nu}}} \end{array}$$

At high frequencies, the feedback transimpedance =  $R_{f_1}$ .

Define the ratio of this high frequency feedback transimpedance

to the DC feedback transimpedance as

$$\beta = \frac{R_{f_1}}{R_{f_1} || R_{f_2}} = 1 + \frac{R_{f_1}}{R_{f_2}}$$

.

20 log ( $\beta$ ) is then the increase in low frequency loop gain in dB from the high frequency value of R<sub>f.</sub>.

The resulting feedback transimpedance

$$\frac{\text{zero}}{\text{pole}}$$

ratio =  $\frac{\alpha}{\alpha + 1} = \frac{1}{\beta}$

Typically we would target the pole frequency to occur at a lower frequency than the nominal crossover frequency for  $\rm R_{\rm f_1}$

(recommended value for amplifier)

Then L =

$$\frac{R_{f_1} \alpha}{\text{Pole frequency * A}_{v}}$$

This will set the zero frequency to

$$\frac{\text{pole frequency}}{\beta}$$

Figure 9. Loop Gain Analysis for Parallel and Inductor Coupled Feedback

To use this approach to increasing the low frequency loop gain, the following steps would be followed:

- 1. The desired signal gain would be set.

- 2. A current feedback amplifier appropriate for this gain range would be selected.

- 3. R<sub>f1</sub> is set to the selected op amp's nominal recommended value (note [2]).

- 4. The pole frequency for the feedback transimpedance is set to be less than nominal unity loop gain crossover frequency for the selected op amp.

- 5. The desired reduction in feedback transimpedance at low frequencies is set. This will also determine the zero frequency.

The pole/zero ratio is equal to

$$\beta \left( = 1 + \frac{R_{f_1}}{R_{f_2}} \right)$$

6. The coupling inductor (L) is solved from the equation in Figure 9.

- 7.  $R_{12}$  and  $R_{\alpha 2}$  are solved using \_ and the desired signal gain.

- 8. The additional loading on the output due to the additional feedback network (R<sub>f2</sub> + R<sub>g2</sub>) should be checked to see that it is not significantly lowering the intended load.

Figure 10 shows a Bode plot of the same forward transimpedance gain of Figure 6 with a 4:1 reduction in the DC feedback transimpedance using this paralleled, inductor coupled, feedback. Note that the targeted pole frequency was 80MHz which forces the zero frequency to be at 20MHz. This yields a 12dB (4 times) increase in the low frequency loop gain. This loop gain has decreased by 3dB at 20MHz and continues on up to only a 3dB improvement from the nominal  $R_{\rm f1}$  value at 80MHz. The goal here was to be approximately back to an  $R_{\rm f1}$  feedback impedance by the 100MHz unity loop gain crossover point on the forward transimpedance curve. This 12dB improvement in the loop gain at 10MHz should translate directly into a 6dB increase in the 2-tone, 3rd order intermodulation intercept (one half of a 12dB decrease in the spurious levels for a given output power level will yield a 6dB increase in intercept).

Figure 10. Forward Transimpedance with Shaped Feedback Showing Increased Loop Gain

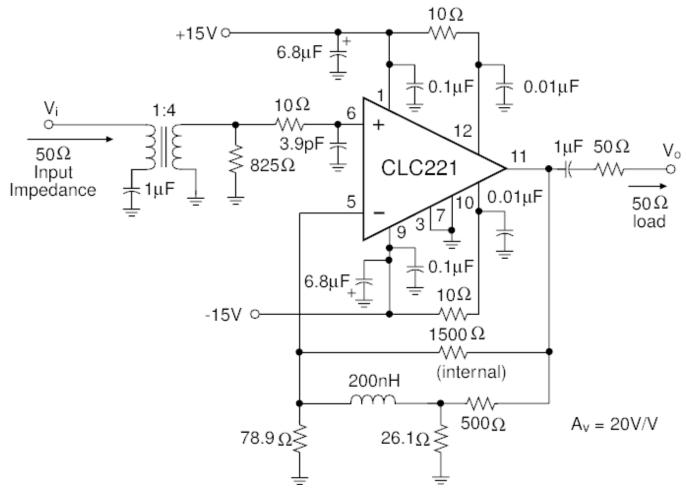

Figure 11 shows an example circuit using the paralleled feedback approach to increasing the loop gain at low frequencies. This circuit also uses a 1:4 step up transformer at the input to improve the Noise Figure (reference [4]). This input stage presents a  $50\Omega$  input impedance in the passband of the transformer and reduces the overall Noise Figure to 7.2dB for this test circuit. Although this transformer will AC couple the signal path, it is important to remember that the amplifier itself is a true DC coupled device. Since the input is already AC coupled, a  $1\mu F$  blocking capacitor at the output has been added to strip off any amplifier DC offsets that may be present. The op amp itself presents a very low output impedance. To get into a  $50\Omega$  system, a series, discrete,  $50\Omega$  resistor must be added. The defined measurement point for both gain and intercept is at the  $50\Omega$  load.

Figure 11. Test Circuit for Increasing Loop Gain

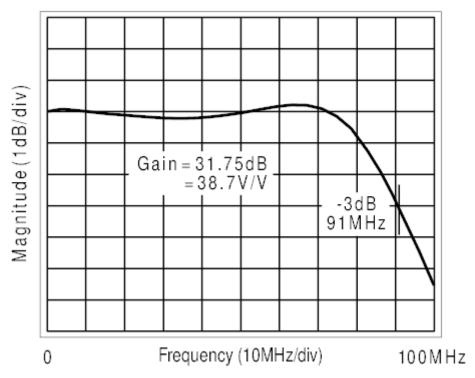

The overall gain for this circuit is 40V/V (32dB). Figure 12 shows the measured frequency response for this test circuit. Although the CLC221 is specified to provide >165MHz -3dB bandwidth in the gain of +20 configuration used here, the transformer and the input RC filter limit the bandwidth to approximately 90MHz. Significant latitude in trading off gain, bandwidth, and noise are possible when using op amps in these types of applications. For additional discussion of interpreting and using op amp specifications in RF applications, see *OA-11 A Tutorial on Applying Op Amps to RF Applications* (SNOA390).

Figure 12. Measured Frequency Response for Wide Dynamic Range Test Circuit Using a CLC221

At 10MHz, the CLC221, without any loop gain shaping, has a 49dBm 3rd order intercept while dissipating only 900mW quiescent power. Using  $\pm 15$  volt supplies, the full scale output pin voltage swing is approximately  $\pm 5$  volts in order to satisfy the 50mA maximum output current into the  $100\Omega$  load. For 2-tone, 3rd order intercept testing, this translates into a maximum 12dBm test power level for each of the two test frequencies at the  $50\Omega$  load. Given a maximum peak to peak swing at the amplifier output, from either a voltage swing or current limit standpoint, the maximum single tone power level at the load is for a voltage swing 1/4 this level. This accounts for the 6dB loss in going through the matching network and the fact that the full voltage envelope for a two tone test is the sum of the peak to peak swings for the individual test frequencies.

Pushing a full 12dBm in each test tone at the load puts the amplifier into a slightly higher distortion mode. The 49dBm intercept for the amplifier by itself is not observed until the single tone power at the load has dropped to 8dBm. Using this as a test condition will yield a  $3V_{pp}$  swing for the voltage envelope at the load.

This test circuit shows bipolar supplies for the amplifier. True DC coupled devices typically use balanced bipolar supplies. However, since most current feedback amplifiers don't actually use a ground reference in their design, single supply operation is perfectly acceptable. Application Report OA-11 (SNOA390) describes this in detail.

#### 4 Measuring 2-Tone, 3rd Order Intercepts above 50dBm

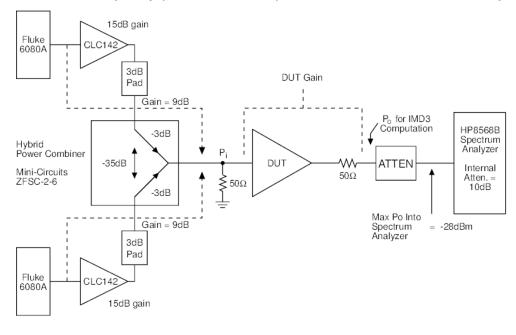

The 3rd order spurious levels for 8dBm test power levels and 50dBm intercept would be -74dBm (note [3]). This 82dB dynamic range requirement is right at the edge of what most spectrum analyzers can measure. Figure 13 shows a typical test setup for measuring intercepts where the dynamic range requirement is less than 90dB. One of the principle requirements for this measurement are to provide clean input test tones, with no intermodulation of the sources. The amplifiers following the sources and the

hybrid power combiner achieve this quite well. These amplifiers, the CLC142, can provide 27dBm output power through 100MHz and are particularly useful in getting enough power to the DUT for testing low gain devices. They also isolate any leveling loops in the output stage of the sources from mixing together and can themselves provide in excess of 50dBm intercepts through 10MHz (although their intercept performance does not limit this test).

The 2nd primary requirement for the test setup of Figure 13 is to attenuate the fundamental power levels at the input of the spectrum analyzer mixer to a low enough power level to eliminate any analyzer produced inter-modulation products. This typically translates into a -36 to -40dBm power level at the mixer.

The test set up of Figure 13 would begin to have trouble making this measurement as the required dynamic range extends beyond 85dB. This would occur as the test power level is decreased (to evaluate if intercept performance is observed) or if higher intercepts were to be measured. The anticipated 55dBm intercept for the test circuit described earlier would exceed the measurement range for the test configuration of Figure 13. With 8dBm test power levels at the load, the anticipated spurious power levels would be at -86dBm for a 55dBm intercept. This 94dB dynamic range is probably beyond most spectrum analyzers. Averaging could be used to lower the noise floor in an attempt to pull this very low spurious out of the noise. As the test power is decreased, the required averaging would significantly extend the test time. An alternative technique would be to filter out one or both of the two test frequencies after the DUT and before the signal is applied to the analyzer. This realistically requires a relatively broad spacing of the test input frequencies (to avoid filtering the spurious frequencies) and is not particularly useful for swept frequency measurements.

Figure 14 shows a modification to the basic test setup of Figure 13 to extend the dynamic range of this intermodulation measurement system. In this approach a 3rd signal source, phase locked to one of the other two input signal sources, is used to null out one test frequency at the output of the DUT. The same type of power combiner used at the input is used here to combine the output signal with a nulling signal from a 3rd signal generator. The Fluke 6080A sources offer a programmable phase capability that allows the nulling source to be tuned to very nearly 180 degrees out of phase with one of the test signals at the DUT output. The output of this 2nd power combiner will then have one of the test frequencies plus the original intermodulation tones at the output of the DUT. This allows the system to use less attenuation to the analyzer mixer since no intermodulation terms will be generated in the analyzer. This technique also offers the advantage of being fully programmable over a wide range of frequencies and test powers.

## Low Frequency (100KHz to 10MHz) 3rd Order Intermodulation Intercept Test Setup Template

Figure 13. Intermod Test Setup

# Low Frequency (100KHz to 10MHz) 3rd Order Intermodulation Intercept Test Setup Template with Output Single Tone Cancellation

Figure 14. Improved Dynamic Range Intermod Test Setup

# 5 Test Results for the Improved Intercept Amplifier

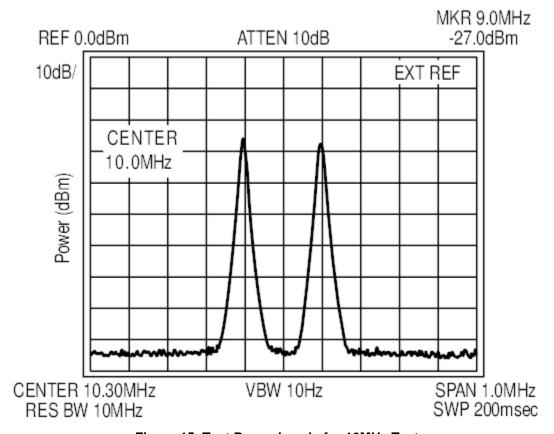

The intermodulation intercept for the circuit of Figure 11 was first measured using the basic setup of Figure 13. This measurement resulted in approximately a 52dBm intercept. Figure 15 shows the test signals at 100kHz around 10MHz. Note that the measured power is -27dBm or -37dBm at the mixer considering the analyzer's internal 10dB attenuator.

Figure 15. Test Power Levels for 10MHz Test

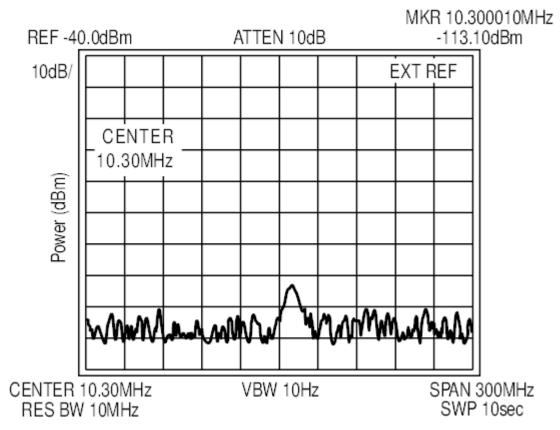

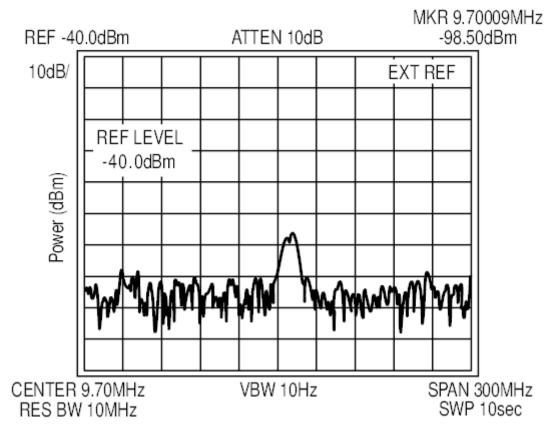

Figure 16 shows the measurement for the upper spurious signal at 10.3MHz. Note the very narrow resolution bandwidth, video bandwidth, and span to make this measurement. The low phase noise of the sources and phase locking all of the sources and the analyzer together are critical to this measurement.

Figure 16. Spurious Measurement at 10.3MHz

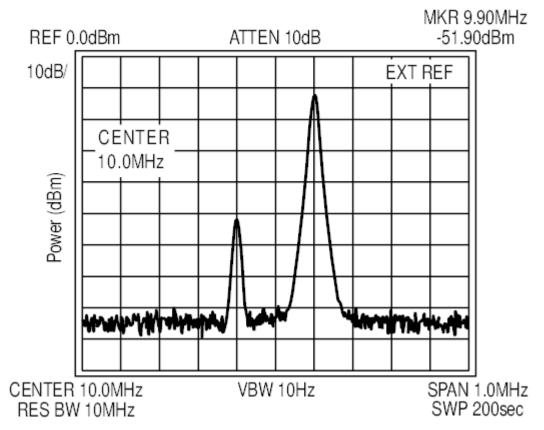

Continuing on to the same measurement with the test set up of Figure 14 did allow a slightly increased measurement range. After nulling out the lower test frequency, the test signal plot of Figure 17 shows the widely disparate power levels going into the analyzer. It is important to remember that equal test power levels are still being generated at the DUT output. Note that the measured power on the uncancelled test tone has increased to approximately -11dBm from the earlier -27dBm level. This reflects the reduced (19dB) attenuation used at the output signal path. Also note that the lower test tone has been attenuated by 40dB from the upper tone with this cancelling technique. Although the mixer is seeing a fairly high absolute power level for the upper tone, -21dBm, since the lower tone is significantly lower, no analyzer generated intermodulation terms should interfere with this measurement.

Figure 17. Test Power Levels at the Analyzer with Single-Tone Cancellation

Figure 18 shows the measured lower spurious at 9.7MHz using the test setup of Figure 14. This measured spurious level is about 8dB more out of the noise than the earlier measurement. However, the noise floor has clearly come up along with this reduced attenuation from the DUT output to the analyzer input. This indicates that the DUT output noise is a significant part of the total noise at the analyzer. Taking the measured test tone power to be at -11dBm, while the DUT output power at the load was 8dBm, this yields a (-11-(-98.5))/2+8=51.75dBm intercept.

Figure 18. Spurious Measurement with Single Test Tone Cancellation

The loop gain shaping network of Figure 11 appears to have improved the intercept by only 3dBm instead of the 6dBm expected. Further investigation revealed that this can be attributed to the non-zero inverting input impedance of the current feedback amplifier. With this impedance >0, some of the feedback error signal splits off and is wasted through the gain setting resistors. This reduces the loop gain. Simulations including this effect revealed only a 6dB improvement in loop gain at 10MHz which is consistent with the 3dBm increase in intermodulation intercept.

However, the intercept does continue to improve as the test frequency is decreased. The following table shows the measured intercepts from 5MHz to 10MHz for the circuit of Figure 11 using the test setup of Figure 14. Below 5MHz, a 56dBm intercept is achieved.

| Frequency | Intercept |

|-----------|-----------|

| 5MHz      | 55.8dBm   |

| 6MHz      | 54.9dBm   |

| 7MHz      | 54.0dBm   |

| 8MHz      | 52.8dBm   |

| 9MHz      | 52.4dBm   |

| 10MHz     | 51.5dBm   |

www.ti.com Conclusions

#### 6 Conclusions

High speed current feedback amplifiers can offer exceptional 2-tone 3rd order intercept performance at relatively low quiescent powers. This intercept performance does decrease with frequency due to the decreasing loop gain as frequency is increased. Although the example device used here, the CLC221, is a high performance hybrid amplifier, similar results at lower maximum output power levels can be achieved with monolithic current feedback amplifiers (such as the CLC409, CLC401, and CLC404, particularly). A simple loop gain shaping network can be used to further increase the intercept at low frequencies. And finally, a simple means to extend the measurement dynamic range through output test signal cancellation has been described and demonstrated. This approach offers the principle advantage of being easily programmable over a wide range of frequencies.

#### 7 References

- 1. Current Feedback Amplifiers, Sergio Franco; reprinted in National 1993 Databook

- 2. Integrated Electronics: Analog and Digital Circuits and Systems, Millman & Halkias; McGraw/Hill 1972

- 3. T Network Quiets Current-Feedback Op Amps, Howard Bandell; EDN, Aug. 20, 1990 page 152

- 4. OA-14 Improving Amplifier Noise for High 3rd Intercept Amplifiers Application Report (SNOA389)

#### 8 Notes

- 1. The 49dBm intercept shown for the CLC221 does not agree with the data sheet plot showing 55dBm at 10MHz. The data in Figure 6 was taking the signal power at a 50Ω load through a series 50Ω output matching resistor. The CLC221 data sheet plot was taking the test power at the output pin which yields a 6dBm higher intercept. More recent data sheets, and all of this discussion, are taking the signal power to be at the matched load.

- 2. For a discussion of setting R<sub>f</sub> for various signal gains, see *OA-13 Current Feedback Loop Gain Analysis and Performance Enhancement Application Report* (SNOA366).

- 3. Equal test powers  $P_{spurious} = 2 [1.5P_{test} Intercept]$  in dBm. At 8dBm test and 49dBm intercept,  $P_{spurious} = 2 [1.5(8) P_{test} 49] = -74dBm$

Note: The circuits included in this application note have been tested with Texas Instruments parts that may have been obsoleted and/or replaced with newer products. Please refer to the CLC to LMH conversion table to find the appropriate replacement part for the obsolete device.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>