# TL431 Pin FMEA

Marcoo Zamora

# ABSTRACT

The TL431 and TL432 are three-terminal adjustable shunt regulators with specified thermal stability over automotive, commercial, and military temperature ranges. The TL431 devices have sharp turnon time and can act as replacements for Zener diodes in many applications.

#### Contents

| 1 | Pin FMEA                               | 1 |

|---|----------------------------------------|---|

| 2 | Scope                                  | 2 |

| 3 | TL431 Pin Configurations and Functions | 3 |

| 4 | FMEA Analysis                          | 4 |

|   |                                        |   |

#### List of Figures

| 1 | 3-Pin SOT-23 Package (Top View) | 3 |

|---|---------------------------------|---|

| 2 | TL431 Schematic                 | 3 |

### List of Tables

| 1 | Pin FMEA Analysis for Pin Short Circuit to Ground                        | 4 |

|---|--------------------------------------------------------------------------|---|

| 2 | Pin FMEA Analysis for Pin Short Circuit to $V_{\ensuremath{\mathbb{N}}}$ | 4 |

| 3 | Pin FMEA Analysis for Pin Short Circuit to an Adjacent Pin               | 4 |

| 4 | Pin FMEA Analysis for Pin Open Circuit                                   | 4 |

# Trademarks

All trademarks are the property of their respective owners.

# 1 Pin FMEA

This application note provides a Failure Modes and Effects Analysis (FMEA) for the device pins of the TL431. The failure conditions covered in this document include the typical pin-by-pin failure scenarios:

- Pin short-circuited to Ground;

- Pin short-circuited to TL431 V<sub>IN</sub>;

- · Pin short-circuited to an adjacent pin; and

- Pin is open circuited.

This application note also details how these pin conditions affect the device:

- Does the pin condition cause permanent damage?

- Is the device is functional under the pin condition?

- How does a particular pin condition affect the device operation?

1

## 2 Scope

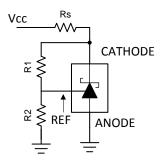

The TL431 is composed of an error amplifier and a transistor that has two modes: open-loop mode and closed-loop mode.

- Closed-Loop mode is where the input voltage pin, REF, is connected to the output voltage pin, Cathode. In this configuration, the output voltage is regulated to a specified value based on the feedback loop that is connected to the REF pin.

- Open-Loop mode is where the input voltage pin, REF, has no connection path to the output voltage pin, Cathode. In this configuration, the output voltage has no feedback loop connection to the REF pin, and thus the cathode voltage is dependent on the voltage on the REF pin. This configuration is commonly known as the comparator mode configuration as the REF pin is used as a comparator.

In many applications, the most common configuration is the closed-loop mode because the cathode voltage is stable in this mode and is regulated across temperature so long as the parameters are is within the recommend operating range. Having the TL431 in open-loop mode is beyond the scope of this report.

For the purposes of this report:

- Unless otherwise specified, the voltage applied to the CATHODE and REF are within the TL431 recommended operating range.

- The V<sub>IN</sub> for the purposes of document is the CATHODE pin as it provides voltage to the error amplifier.

- The feedback network in closed-loop has gain due to R1 and R2, but the CATHODE voltage is still within the recommended operating range.

2

www.ti.com

# 3 TL431 Pin Configurations and Functions

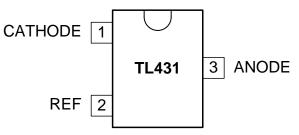

Figure 1. 3-Pin SOT-23 Package (Top View)

# Figure 2. TL431 Schematic

## **Pin Functions**

| PIN    |         | I/O | DESCRIPTION                              |  |  |

|--------|---------|-----|------------------------------------------|--|--|

| NUMBER | NAME    | 1/0 | DESCRIPTION                              |  |  |

| 1      | CATHODE | I/O | Shunt Current/ Voltage input             |  |  |

| 2      | REF     | I   | Threshold relative to common anode       |  |  |

| 3      | ANODE   | 0   | Common pin, normally connected to ground |  |  |

# 4 FMEA Analysis

| PIN    |         | SHORT TO VIN |            |                                         |  |  |

|--------|---------|--------------|------------|-----------------------------------------|--|--|

| NUMBER | NAME    | DAMAGE       | FUNCTIONAL | COMMENTS                                |  |  |

| 1      | CATHODE | No           | No         | No damage to device. Increases leakage. |  |  |

| 2      | REF     | No           | Yes        | Cathode voltage is unregulated          |  |  |

| 3      | ANODE   | No           | Yes        | No effect                               |  |  |

## Table 1. Pin FMEA Analysis for Pin Short Circuit to Ground

## Table 2. Pin FMEA Analysis for Pin Short Circuit to VIN

| P      | PIN     | SHORT TO V <sub>IN</sub> |            |                                                                                |  |

|--------|---------|--------------------------|------------|--------------------------------------------------------------------------------|--|

| NUMBER | NAME    | DAMAGE                   | FUNCTIONAL | COMMENTS                                                                       |  |

| 1      | CATHODE | No                       | Yes        | No Effect                                                                      |  |

| 2      | REF     | No                       | Yes        | Voltage might be regulated differently depending on the feedback of the device |  |

| 3      | ANODE   | No                       | No         | No damage to device. Increases leakage.                                        |  |

# Table 3. Pin FMEA Analysis for Pin Short Circuit to an Adjacent Pin

| PIN SHO |             | SHOR   | t to Pin | SHORT TO ADJACENT PIN |            |                                                                            |

|---------|-------------|--------|----------|-----------------------|------------|----------------------------------------------------------------------------|

| NUMBER  | NAME        | NUMBER | NAME     | DAMAGE                | FUNCTIONAL | COMMENTS                                                                   |

| 1       | CATHOD<br>E | 2      | REF      | No                    | Yes        | Voltage might be regulated differently depending on the gain of the device |

| 2       | REF         | 3      | ANODE    | No                    | Yes        | Cathode voltage is unregulated                                             |

| 3       | ANODE       | 1      | CATHODE  | No                    | No         | No damage to device. Increases leakage.                                    |

# Table 4. Pin FMEA Analysis for Pin Open Circuit

| PIN    |         | OPEN              |    |                         |  |  |

|--------|---------|-------------------|----|-------------------------|--|--|

| NUMBER | NAME    | DAMAGE FUNCTIONAL |    | COMMENTS                |  |  |

| 1      | CATHODE | No                | No | No output voltage.      |  |  |

| 2      | REF     | No                | No | Output is not regulated |  |  |

| 3      | ANODE   | No                | No | Output is not regulated |  |  |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated