# LP87332D and LP873220 User's Guide to Power AM570x

This user's guide can be used as a guide for powering AM570x with the LP87332D and LP873220 power devices.

|   | Contents                                                            |   |

|---|---------------------------------------------------------------------|---|

| 1 | Introduction                                                        | 2 |

| 2 | Device Versions                                                     | 2 |

| 3 | Platform Connection                                                 | 2 |

| 4 | OTP Memory Configuration, Static Platform Settings                  | 4 |

| 5 | OTP Memory Configuration, Power-Up and Power-Down Sequence Settings | 7 |

#### List of Figures

| 1 | Processor Connection With LP87332D and LP873220 | 3 |

|---|-------------------------------------------------|---|

| 2 | Power-Up and Power-Down Sequence                | 7 |

#### List of Tables

| 1 | OTP Settings Differentiation                        | 2 |

|---|-----------------------------------------------------|---|

| 2 | BUCK0 and BUCK1 OTP Settings                        | 4 |

| 3 | LDO0 and LDO1 OTP Settings                          | 4 |

| 4 | EN, CLKIN and GPIO Pin Settings                     | 4 |

| 5 | PGOOD OTP Settings                                  | 5 |

| 6 | Protections OTP Settings                            | 5 |

| 7 | Device Identification and I <sup>2</sup> C Settings | 6 |

| 8 | Interrupt Mask Settings                             | 6 |

|   |                                                     |   |

# Trademarks

All trademarks are the property of their respective owners.

#### 1 Introduction

This user's guide can be used as a guide for powering AM570x with LP87332D and LP873220 power devices.

This user's guide describes the platform connections as well as the power-up and power-down sequences along with the OTP configurations. This user's guide does not provide details about the power resources, external components, or the functionality of the device. For such information, refer to *LP87332D Dual High-Current Buck Converters And Dual Linear Regulators* and *LP873220 Dual High-Current Buck Converters And Dual Linear Regulators*.

In the event of any inconsistency between the official specification and any user's guide, application report, or other referenced material, the datasheet specification will be the definitive source.

#### 2 Device Versions

The OTP settings for LP87332D and LP873220 are described in this document. The OTP version can be read from the OTP\_REV register as shown in Table 1.

In addition, a power solution is available using the TPS65916 device as described in the *TPS65916 User's Guide to Power AM570x*. See Table 1 to determine the recommended part number based on the  $V_{DD}$  current requirement of the processor and other features.

Texas Instruments recommends having 15% margin in the load current. Therefore the current requirements listed in Table 1 are 15% lower than the maximum capability of the regulator. For example, the LP87332D device supports 3 A maximum, so the recommended load current is 15% less, or 2.55 A. If the  $V_{DD}$  current of the processor in the application is unknown, select the TPS65916 configuration because it supports the maximum performance of the processor.

| DDR MEMORY<br>TYPE |                          | SPECIAL FEATURES                                              | ORDERABLE PART<br>NUMBER       | CONTENT OF OTP_REV<br>REGISTER |

|--------------------|--------------------------|---------------------------------------------------------------|--------------------------------|--------------------------------|

| DDR3L              | V <sub>DD</sub> < 2.55 A | N/A                                                           | LP87332DRHDR +<br>LP873220RHDR | 0x2D, 0x20                     |

| DDR3L              | V <sub>DD</sub> < 3 A    | VBUS detection,<br>Integrated dual-voltage<br>LDO for SD card | TPS659163RGZR                  | See User's Guide               |

#### Table 1. OTP Settings Differentiation

# **3** Platform Connection

2

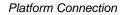

Figure 1 shows the detailed connections between the processor and LP87332D and LP873220.

- When high speed SD card requiring 1.8V support is used, the external LDO TPS74801 is needed instead of LDO0 of LP87332D

- When system has only 3.3V rail available, VDDA\_USB3V3 should be connected to 3.3V rail via load switch. LDO1 of LP87332D can be used as enable for the load switch.

- PGOOD outputs of LP87332D and LP873220 are combined together with GPO2 of LP87332D to create PWR\_PORz signal.

- GPO of LP873220 is available for system control, see Figure 2.

www.ti.com

Figure 1. Processor Connection With LP87332D and LP873220

## 4 **OTP Memory Configuration, Static Platform Settings**

Each device has predefined values stored in OTP which control the default configuration of the device. The tables in this section list the OTP-programmed values for each device, distinguished by the OTP\_REV. Power-up and power-down sequences are described in the next chapter.

Table 2 shows device settings for BUCK0 and BUCK1. Maximum allowed slew-rate for BUCKx depends on the output capacitance. BUCK1 of LP873220D is supply for memory where larger capacitance is expected to be used and because of ths slew-rate is set to lower value. Refer to the device datasheets for output capacitance boundary conditions.

|                    | DESCRIPTION                    | BIT NAME                       | LP87332D | LP873220                                                                                     | NOTES                  |

|--------------------|--------------------------------|--------------------------------|----------|----------------------------------------------------------------------------------------------|------------------------|

| Buck configuration | Spread spectrum                | EN_SPREAD_SPEC                 | No       | No                                                                                           | Yes / No               |

| BUCK0              | Output voltage                 | BUCK0_VSET                     | 1.15 V   | 1.8 V                                                                                        |                        |

|                    | Enable, EN-pin or I2C register | BUCK0_EN_PIN_CTRL,<br>BUCK0_EN | EN       | EN                                                                                           | EN or I <sup>2</sup> C |

| BUCK0              | Force PWM                      | BUCK0_FPWM                     | No       | No     V   1.8 V     EN     No     3 A     /µs   10 mV/µs     V   1.35 V     EN     No   3.4 | Yes / No               |

|                    | Peak current limit             | BUCK0_ILIM                     | 4 A      | 3 A                                                                                          |                        |

|                    | Slew rate                      | BUCK0_SLEW_RATE                | 10 mV/µs | 1.8 V     EN     No     3 A     10 mV/μs     1.35 V     EN     No                            |                        |

|                    | Output voltage                 | BUCK1_VSET                     | 1.06 V   | 1.35 V                                                                                       |                        |

|                    | Enable, EN-pin or I2C register | BUCK1_EN_PIN_CTRL,<br>BUCK1_EN | EN       | EN                                                                                           | EN or I <sup>2</sup> C |

| BUCK1              | Force PWM                      | BUCK1_FPWM                     | No       | No                                                                                           | Yes / No               |

|                    | Peak current limit             | BUCK1_ILIM                     | 4 A      | 3 A                                                                                          |                        |

|                    | Slew rate                      | BUCK1_SLEW_RATE                | 10 mV/µs | 7.5 mV/µs                                                                                    |                        |

## Table 2. BUCK0 and BUCK1 OTP Settings

Table 3 lists the device settings for LDO0 and LDO1.

#### Table 3. LDO0 and LDO1 OTP Settings

|      | DESCRIPTION                    | BIT NAME                     | LP87332D | LP873220 | NOTES                  |

|------|--------------------------------|------------------------------|----------|----------|------------------------|

|      | Output voltage                 | LDO0_VSET                    | 3.3 V    | 1.8 V    |                        |

| LDO0 | Enable, EN-pin or I2C register | LDO0_EN_PIN_CTRL,<br>LDO0_EN | EN       | EN       | EN or I <sup>2</sup> C |

|      | Output voltage                 | LDO1_VSET                    | 3.3 V    | 1.8 V    |                        |

| LDO1 | Enable, EN-pin or I2C register | LDO1_EN_PIN_CTRL,<br>LDO1_EN | EN       | EN       | EN or I <sup>2</sup> C |

Table 4 lists the device settings for GPIOs.

# Table 4. EN, CLKIN and GPIO Pin Settings

|           | DESCRIPTION                                                                                    | BIT NAME      | LP87332D | LP873220 | NOTES                 |

|-----------|------------------------------------------------------------------------------------------------|---------------|----------|----------|-----------------------|

| EN pin    | EN pin pull-down resistor enable / disable                                                     | EN_PD         | Enabled  | Enabled  | Enabled /<br>disabled |

| CLKIN pin | CLKIN or GPO2 mode selection                                                                   | CLKIN_PIN_SEL | GPO2     | GPO2     |                       |

|           | CLKIN pin pull-down resistor enable /<br>disable (applicable for both CLKIN and<br>GPO2 modes) | CLKIN_PD      | Disabled | Disabled | Enabled /<br>disabled |

|           | Frequency of external clock when connected to CLKIN                                            | EXT_CLK_FREQ  | 2 MHz    | 2 MHz    |                       |

|           | Enable for the internal PLL. When PLL disabled, internal RC OSC is used                        | EN_PLL        | Disabled | Disabled | Enabled /<br>disabled |

|      | DESCRIPTION                    | BIT NAME                   | LP87332D | LP873220 | NOTES                  |

|------|--------------------------------|----------------------------|----------|----------|------------------------|

|      | DESCRIPTION                    | DII NAME                   | LP0/332D | LP0/3220 | NOTES                  |

|      | GPO output type                | GPO_OD                     | OD       | OD       | PP / OD                |

| GPO  | Enable, EN-pin or I2C register | GPO_EN_PIN_CTRL,<br>GPO_EN | EN       | EN       |                        |

| GPO2 | Control for GPO                | GPO_EN                     | High     | High     | Low / High             |

|      | GPO2 output type               | GPO2_OD                    | OD       | OD       | PP / OD                |

|      | Enable, EN-pin or I2C register | GPO2_EN_PIN_CTRL           | EN       | EN       | EN or I <sup>2</sup> C |

|      | Control for GPO2               | GPO2_EN                    | High     | High     | Low / High             |

## Table 4. EN, CLKIN and GPIO Pin Settings (continued)

Table 5 shows device settings for PGOOD.

|                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BIT NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LP87332D    | LP873220    | NOTES                                                                      |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|----------------------------------------------------------------------------|

| Signals monitored<br>by PGOOD | BUCK0 output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EN_PGOOD_BUCK0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Yes         | Yes         | Yes / No                                                                   |

|                               | BUCK1 output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EN_PGOOD_BUCK1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Yes         | Yes         | Yes / No                                                                   |

|                               | LDO0 output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | output voltage EN_PGOOD_BUCK0 Yes Yes No   output voltage EN_PGOOD_BUCK1 Yes Yes No   utput voltage EN_PGOOD_LDO0 No Yes No   utput voltage EN_PGOOD_LDO1 No Yes No   utput voltage EN_PGOOD_TWARN Yes Yes No   I warning EN_PGOOD_WINDOW_BUCK Window Window U   D Thresholds for BUCK0, BUCK1 PGOOD_WINDOW_BUCK Window Window U   D Thresholds for LDO0, LDO1 PGOOD_WINDOW_LDO Window Window U   D Thresholds for LDO0, LDO1 PGOOD_MODE Window U U   D operating mode PGOOD_MODE Window U U   D operating mode PG_FAULT_GATES_PGOOD Status Status U   D output mode PGOOD_OD OD OD OD OD | Yes / No    |             |                                                                            |

| 5,10000                       | LDO1 output voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EN_PGOOD_LDO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | No          | Yes         | Yes / No                                                                   |

|                               | BUCK0 output voltage EN_PGOOD_BUCK0 Yes Yes   BUCK1 output voltage EN_PGOOD_BUCK1 Yes Yes   DO0 output voltage EN_PGOOD_LDO0 No Yes   DD1 output voltage EN_PGOOD_LDO1 No Yes   DO1 output voltage EN_PGOOD_TWARN Yes Yes   PGOOD Thresholds for BUCK0, BUCK1 PGOOD_WINDOW_BUCK Window Window   PGOOD Thresholds for LDO0, LDO1 PGOOD_WINDOW_BUCK Window Window   PGOOD operating mode PGOOD_MODE Detecting<br>UNUSUAL<br>situations Detecting<br>UNUSUAL<br>situations   PGOOD signal mode PGOOD_OD OD OD OD | Yes / No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |             |                                                                            |

|                               | PGOOD Thresholds for BUCK0, BUCK1                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PGOOD_WINDOW_BUCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Window      | Window      | Undervolta<br>ge /<br>Window<br>(undervolta<br>ge and<br>overvoltage<br>)  |

|                               | PGOOD Thresholds for LDO0, LDO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PGOOD_WINDOW_LDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Window      | Window      | Undervolta<br>ge /<br>Window<br>(undervolta<br>ge and<br>overvoltage<br>)  |

|                               | PGOOD operating mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PGOOD_MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UNUSUAL     | UNUSUAL     | Detecting<br>UNUSUAL<br>situations /<br>Detecting<br>UNVALID<br>situations |

|                               | PGOOD signal mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PG_FAULT_GATES_PGOOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Status      | Status      | Status /<br>Latched<br>until fault<br>source<br>read                       |

|                               | PGOOD output mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PGOOD_OD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OD          | OD          | OD / PP                                                                    |

|                               | PGOOD polarity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PGOOD_POL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Active high | Active high | Active<br>(power<br>valid) high /<br>Iow                                   |

#### Table 5. PGOOD OTP Settings

Table 6 lists the device settings for thermal warning. Also refer to Table 5 for PGOOD and Table 8 for interrupts.

# **Table 6. Protections OTP Settings**

|             | DESCRIPTION           | BIT NAME        | LP87332D | LP873220 | NOTES             |

|-------------|-----------------------|-----------------|----------|----------|-------------------|

| Protections | Thermal Warning level | TDIE_WARN_LEVEL | 137°C    | 137°C    | 125°C or<br>137°C |

Table 7 shows device settings for I<sup>2</sup>C and OTP revision ID values.

OTP Memory Configuration, Static Platform Settings

## Table 7. Device Identification and I<sup>2</sup>C Settings

|                          | DESCRIPTION                         | BIT NAME | LP87332D | LP873220 | NOTES |

|--------------------------|-------------------------------------|----------|----------|----------|-------|

| I <sup>2</sup> C address |                                     |          | 0x60     | 0x61     |       |

| OTP_ID                   | Identification code for OTP version | OTP_ID   | 0x2D     | 0x20     |       |

Table 8 lists device settings for interrupts. When interrupt from an event is unmasked, an interrupt is generated to nINT pin.

|         | Interrupt event                       | BIT NAME        | LP87332D | LP873220 | NOTES                |

|---------|---------------------------------------|-----------------|----------|----------|----------------------|

|         | PGOOD pin changing active to inactive | PGOOD_INT_MASK  | Masked   | Masked   | Masked /<br>Unmasked |

|         | Sync Clock appears or disappears      | SYNC_CLK_MASK   | Masked   | Masked   | Masked /<br>Unmasked |

| General | Thermal warning                       | TDIE_WRN_MASK   | Unmasked | Unmasked | Masked /<br>Unmasked |

|         | Load measurement ready                | I_MEAS_MASK     | Unmasked | Unmasked | Masked /<br>Unmasked |

|         | Register Reset                        | RESET_REG_MASK  | Masked   | Masked   | Masked /<br>Unmasked |

|         | Buck0 PGood active                    | BUCK0_PGR_MASK  | Masked   | Masked   | Masked /<br>Unmasked |

| BUCK0   | Buck0 PGood inactive                  | BUCK0_PGF_MASK  | Masked   | Masked   | Masked /<br>Unmasked |

|         | Buck0 Current limit                   | BUCK0_ILIM_MASK | Unmasked | Unmasked | Masked /<br>Unmasked |

|         | Buck1 PGood active                    | BUCK1_PGR_MASK  | Masked   | Masked   | Masked /<br>Unmasked |

| BUCK1   | Buck1 PGood inactive                  | BUCK1_PGF_MASK  | Masked   | Masked   | Masked /<br>Unmasked |

|         | Buck1 Current limit                   | BUCK1_ILIM_MASK | Unmasked | Unmasked | Masked /<br>Unmasked |

|         | LDO0 PGood active                     | LDO0_PGR_MASK   | Masked   | Masked   | Masked /<br>Unmasked |

| LDO0    | LDO0 PGood inactive                   | LDO0_PGF_MASK   | Masked   | Masked   | Masked /<br>Unmasked |

|         | LDO0 Current limit                    | LDO0_ILIM_MASK  | Unmasked | Unmasked | Masked /<br>Unmasked |

| LDO1    | LDO1 PGood active                     | LDO1_PGR_MASK   | Masked   | Masked   | Masked /<br>Unmasked |

|         | LDO1 PGood inactive                   | LDO1_PGF_MASK   | Masked   | Masked   | Masked /<br>Unmasked |

|         | LDO1 Current limit                    | LDO1_ILIM_MASK  | Unmasked | Unmasked | Masked /<br>Unmasked |

#### **Table 8. Interrupt Mask Settings**

www.ti.com

OTP Memory Configuration, Power-Up and Power-Down Sequence Settings

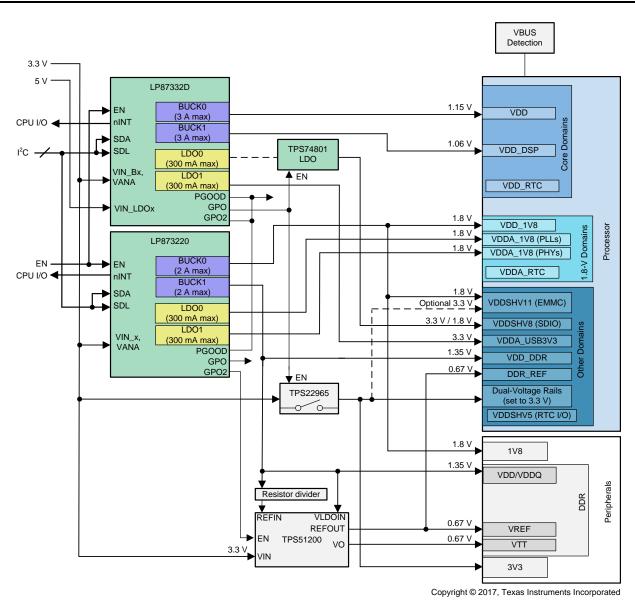

## 5 OTP Memory Configuration, Power-Up and Power-Down Sequence Settings

A power sequence is an automatic preprogrammed sequence handled by the LP87332D and LP873220 devices to configure the device resources: BUCKs, LDOs and GPOs into ON or OFF state.

| EN                             |             | ]        |

|--------------------------------|-------------|----------|

| 1V8 (LP873220_BUCK0)           | 0 ms        | 5 ms     |

| 1V8_PLL (LP873220_LDO0)        | 0.5 ms      | 1.5 ms   |

| 1V35_DDR (LP873220_BUCK1)      | → 1 ms      | 1.5 ms   |

| EN_TPS51200 (LP873220_GPO2)    | 1 ms        | → 1.5 ms |

| VDD (1V15, LP87332D_BUCK0)     | ▶ 1.5 ms    | 1 ms     |

| VDD_DSP (1V06, LP87332D_BUCK1) | 2 ms        | 1 ms     |

| 3V3_USB (LP87332D_LDO1)        | ► 2.5 ms    | 1 ms     |

| 1V8_PHY (LP873220_LDO1)        | 3 ms        | 1 ms     |

| 3V3(1V8)_SDIO (LP87332D_LDO0)  | ► 3.5ms     | 0 ms     |

| SW_3V3 (LP87332D_GPO)          | 3.5ms       | 0 ms     |

| PORz (LP87332D_GPO2)           | 5 ms        | 0 ms     |

| (LP873220_GPO)                 | <b>5</b> ms | 0 ms     |

Figure 2. Power-Up and Power-Down Sequence

Revision History

www.ti.com

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (May 2017) to A Revision |                                                                     | Page |

|------------------------------------------------|---------------------------------------------------------------------|------|

| •                                              | Added TPS65916 solution information, and added link to user's guide | 2    |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated