*TMS320 DSP DESIGNER'S NOTEBOOK*

## Reading a 16-Bit Bus With the TMS320C5x Serial Port

APPLICATION BRIEF: SPRA270

Manuel Rodrigues Digital Signal Processing Products Semiconductor Group

*Texas Instruments May 1996*

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

### TRADEMARKS

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

## CONTACT INFORMATION

| US TMS320 HOTLINE | (281) 274-2320 |

|-------------------|----------------|

| US TMS320 FAX     | (281) 274-2324 |

| US TMS320 BBS     | (281) 274-2323 |

| US TMS320 email   | dsph@ti.com    |

## Contents

| Abstract       | 7 |

|----------------|---|

| Design Problem | 8 |

| Solution       | 8 |

|                |   |

## Figures

| Figure 1. | Connecting a 16-bit Bus to the TMS320C5x's Serial Port | 8  |

|-----------|--------------------------------------------------------|----|

| Figure 2. | Synchro principle 1                                    | 0  |

| Figure 3. | Typical Load/Shift Sequence 1                          | 10 |

# Reading a 16-Bit Bus With the TMS320C5x Serial Port

## Abstract

It is possible to read data directly from a parallel bus. Each word is loaded by a signal, for example /WE. In order to read this kind of word with a synchronous serial port, it has to be converted in series and synchronized by a transmission clock. The solution presented in this document uses the clock signal coming from the DSP, although an independent clock source could be implemented successfully. This solution contains two 8-bit registers instead of one single 16-bit register, such as a 74LS674, because if the bus is only 8 bits wide, you must remove one to adapt the device. A complete schematic of the solution is provided.

## **Design Problem**

How can I read a word from a 16-bit bus with the synchronous serial port of a TMS320C5x DSP?

## Solution

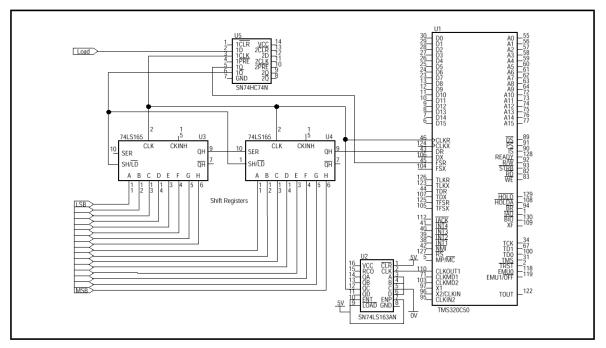

It is possible to compute data directly from a parallel bus. In this case, every word is loaded by a signal, for example /WE. In order to read this kind of word with a synchronous serial port, it has to be converted in series and synchronized by a transmission clock. The solution presented in Figure 1 uses the clock signal coming from the DSP, although an independent clock source could be implemented successfully. The following solution contains two 8-bit registers instead of one single 16-bit register, such as a 74LS674, because if the bus is only 8 bits wide, you must remove one to adapt the device.

Figure 1. Connecting a 16-bit Bus to the TMS320C5x's Serial Port

#### Data Transmission on the Serial Port

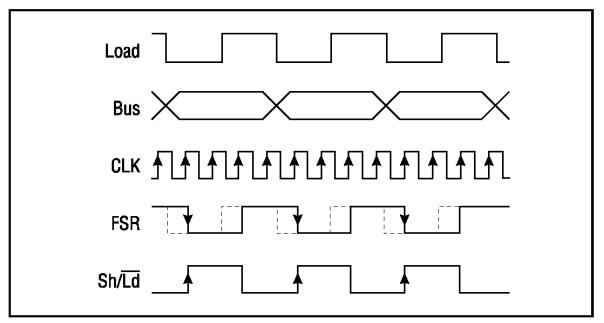

The DSP's serial port, which runs in burst mode, consists of three types of signals: the clock (CLK), which imposes the pace of the bit sequence and which equals the bit rate of the communication; the frame synchro (FS), which indicates the beginning of a bit sequence, on a negative slope, to the other device; and finally, the data line (D), which conveys the bits. The bit rate and the synchro signal are imposed by the device. Data is transmitted and loaded MSB first and is right justified.

#### **Schematic Details**

The clock out frequency from the DSP is 20 MHz. The maximum bit rate for data transmission through the serial port is 5 Mbit/s. Using the 74LS163 counter, the 20-MHz frequency is divided by 2 (QA), by 4 (QB), by 8 (QC), and by 16 (QD). So, we have three different bit rates: 1.25 MHz, 2.5 MHz, and 5 MHz. The choice of the rate depends on the loading frequency of the bus.

#### Signal Principles

In our solution, a low state of load signal indicates that the bus is valid. This signal has to be synchronized by a positive clock slope, thanks to a '74 flip-flop before it enables the shift sequence, making the system fully synchronous. When the shift sequence begins, the FS signal performs a negative transition, which is done selectively by the inverted synchronous load signal by using it as the inverted output of the '74 flip-flop Sh/Ld (see Figure 2).

Two shift registers in cascade provide the parallel-to-serial conversion. If the bus is only 8 bits wide, you can remove one of the two registers. In this case, the 8-bit word will be inserted into the DSP's internal 16-bit word memory as the most significant bits (MSB). The other 8 bits will be set at the least significant bits (LSB) value.

ţi)

Figure 2. Synchro principle

## **Constraints on the Loading Signal**

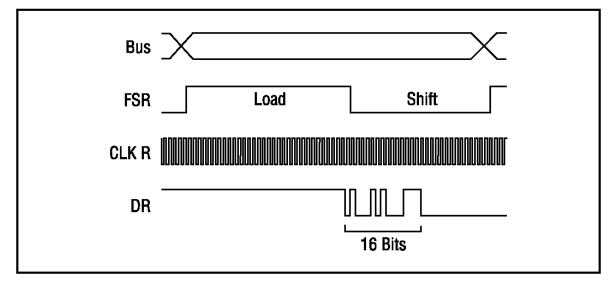

It is necessary that the bus value does not change during the shift sequence. The shift sequence duration is  $T_{SH} = 16/F_{CLK}$ . So, be aware that the Sh/ Ld signal is high during at least  $T_{SH}$  whereas data on the bus is stable (see Figure 3).

Figure 3. Typical Load/Shift Sequence

#### How to Choose the Right Bit Rate

One must also take into account that as the clock frequency is increased, distortion in the signal increases as well. This consideration might lower the maximum bit rate under 5 Mbit/s (maximum clock frequency for the DSP). On the other hand, it is possible to calculate the minimum bit rate  $F_{CLK}$ , knowing the frequency  $F_{LD}$  and the duty cycle of the loading signal (active low).

$F_{\text{CLK}}$  =  $F_{\text{LD}} \times$  16 /  $\alpha$

ſĒ.