# Understanding the TMS320F240 External Memory Interface

APPLICATION REPORT: SPRA452

Jeff Crankshaw Digital Signal Processor Products Semiconductor Group

Digital Signal Processing Solutions June 1998

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current and complete.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated

#### TRADEMARKS

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

# CONTACT INFORMATION

| US TMS320 HOTLINE | (281) 274-2320 |

|-------------------|----------------|

| US TMS320 FAX     | (281) 274-2324 |

| US TMS320 BBS     | (281) 274-2323 |

| US TMS320 email   | dsph@ti.com    |

| Abstract                                       | 7  |

|------------------------------------------------|----|

| Product Support                                | 8  |

| Related Documentation                          | 8  |

| World Wide Web                                 | 8  |

| Email                                          | 8  |

| Introduction                                   | 9  |

| External Memory Interface Example              | 11 |

| TMS320F240 Interfaced to Two 32k x 8-Bit SRAMs |    |

| External Memory Interface Operation            |    |

| External Bus Cycle Definition                  |    |

| Read Cycles                                    |    |

| Write Cycles                                   |    |

| Typical External Data Space Access Sequences   |    |

| Read-Read-Write Sequence                       |    |

| Write-Write-Read Sequence                      |    |

| Bus Cycle vs. Execution Cycle Correlation      | 29 |

| External Program Space Accesses                |    |

| Program Fetch Cycles                           | 31 |

| Table Read and Write Cycles                    | 33 |

| External I/O Space Accesses                    | 36 |

| IN and OUT Cycles                              |    |

| IO Space Decoding for the Range 0xff00-0xfffe  |    |

| External Access Summary                        | 39 |

| Address Visibility Mode                        |    |

| Address Trace and Internal Accesses            |    |

| Address Trace with Peripheral Accesses         |    |

| Address Trace with External Accesses           |    |

| Address Visibility Summary                     | 50 |

| Appendix A. Test Setup                         | 51 |

| Appendix B. Assemble and Link Options          | 52 |

| asmlnk.bat                                     |    |

| evm_lnk.cmd                                    |    |

| Appendix C. Header Files                       |    |

| f240regs.h                                     |    |

| Appendix D. Assembly Language Programs         |    |

| xidstime.asm                                   |    |

| xi fetch.asm                                   |    |

| xi_table.asm                                   |    |

| xi_inout.asm                                   |    |

| avis_chk.asm                                   |    |

|                                                |    |

| Debugger Command Files<br>f240evm.cmd          |    |

| xidstime.cmd                                   |    |

| xidstime.cmd                                   |    |

| xi_inout.cmd                                   |    |

|                                                |    |

# Contents

| avis chk.cmd | 78 |

|--------------|----|

|--------------|----|

# Figures

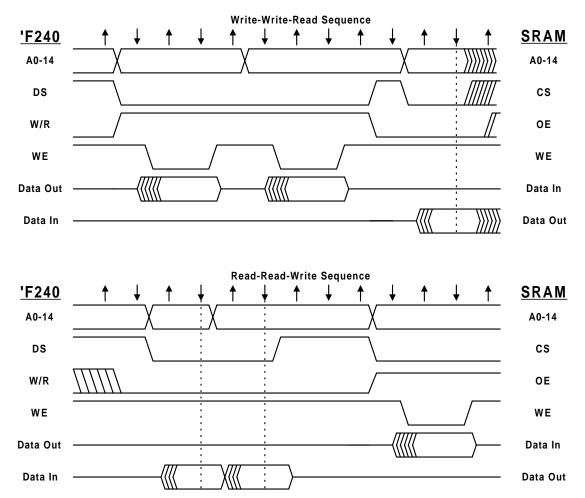

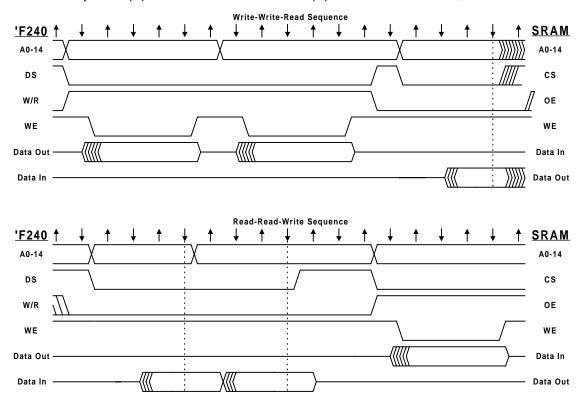

| Figure 1.  | Typical Timing Sequence for 'F240 Connected to SRAM in Data Space: (a)<br>Write-Write-Read and (b) Read-Read-Write; Zero Wait States | 12 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.  | Typical Timing Sequence for 'F240 Connected to SRAM in Data Space: (a)                                                               |    |

| 0          | Write-Write-Read and (b) Read-Read-Write; One Wait State                                                                             | 14 |

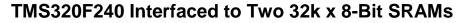

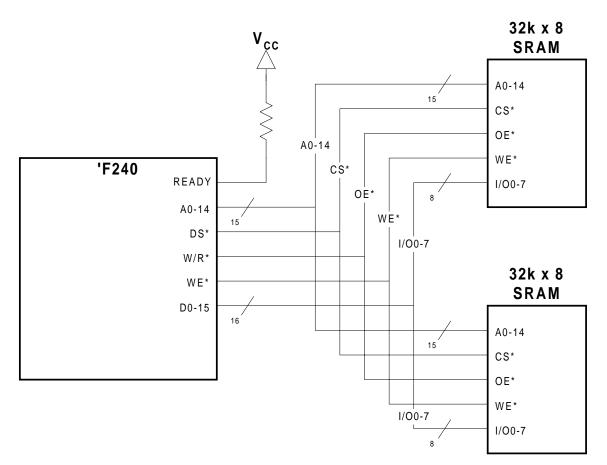

| Figure 3.  | Simplified Block Diagram of TMS320F240 Interface to a Pair of 32k x 8                                                                |    |

| 0          | SRAMs                                                                                                                                | 15 |

| Figure 4.  | Trace of External Data Space Reads with Zero Wait States                                                                             |    |

| Figure 5.  | Trace of External Data Space Reads with One Wait States                                                                              | 22 |

| Figure 6.  | Trace of External Data Space Writes with Zero Wait States                                                                            | 23 |

| Figure 7.  | Trace of External Data Space Writes with One Wait States                                                                             | 24 |

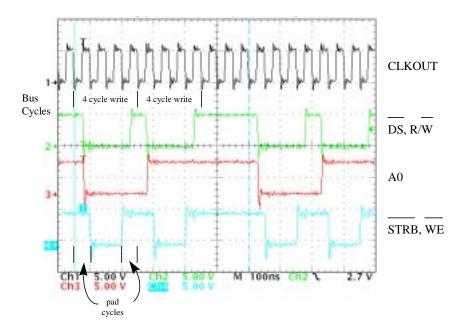

| Figure 8.  | Trace of External Data Space Read-Read-Write Sequence, Zero Wait States 2                                                            | 26 |

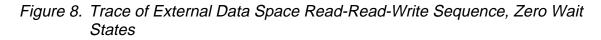

| Figure 9.  | Trace of External Data Space Read-Read-Write Sequence, One Wait State2                                                               | 26 |

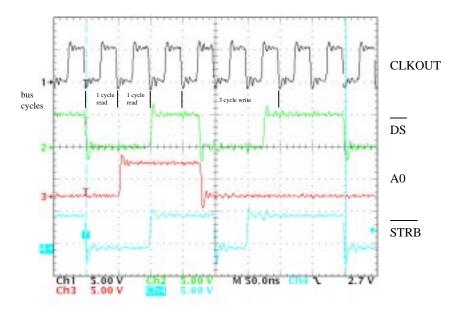

| Figure 10. | Trace of External Data Space Write-Write-Read Sequence, Zero Wait States 2                                                           | 28 |

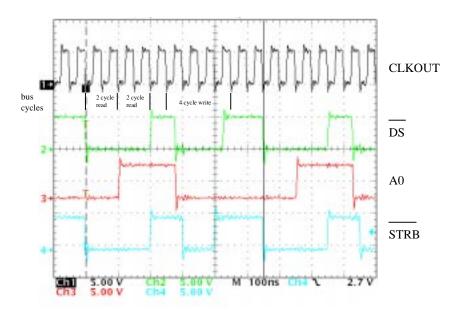

| Figure 11. | Trace of External Data Space Write-Write-Read Sequence, One Wait State2                                                              | 28 |

| Figure 12. | Trace of External Data Space Write-Read-Read-Write Sequence                                                                          | 30 |

| Figure 13. | Trace of External Program Space Instruction Fetch with Zero Wait States                                                              | 32 |

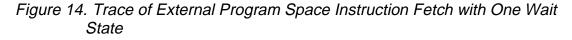

| Figure 14. | Trace of External Program Space Instruction Fetch with One Wait State                                                                | 33 |

| Figure 15. | Trace of External Table Read and Write Operations with Zero Wait States                                                              | 34 |

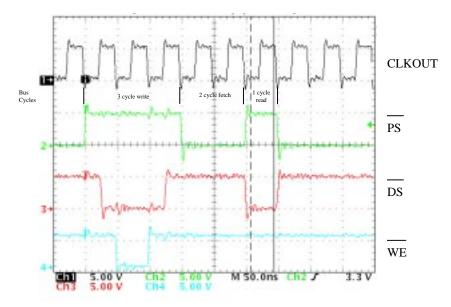

| Figure 16. | Trace of External Table Read and Write Operations with One Wait State                                                                | 36 |

| Figure 17. | Trace of External IN and OUT Operations with Zero Wait States                                                                        | 37 |

| Figure 18. | Trace of External IN and OUT Operations with One Wait State                                                                          | 38 |

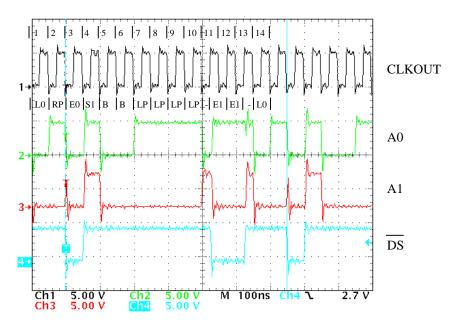

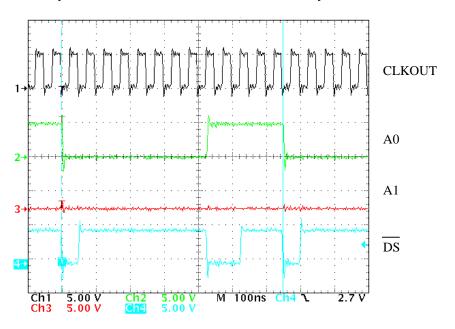

| Figure 19. | Address Visibility Trace on A0-2 for Internal DARAM Accesses                                                                         | 42 |

| Figure 20. | Address Visibility Trace on A0-2 for Peripheral Register Accesses                                                                    | 45 |

| Figure 21. | Address Visibility Trace on A0-2 for External Memory Accesses                                                                        | 48 |

| Figure 22. | Address Visibility Trace on A0-1 and $\overline{DS}$ for External Memory Accesses                                                    | 48 |

|            | Address Visibility Mode Disabled for External Memory Accesses                                                                        |    |

|            |                                                                                                                                      |    |

# Tables

| Table 1.  | Summary of Read/Write Execution Cycles for '240 Address Space       | . 10 |

|-----------|---------------------------------------------------------------------|------|

| Table 2.  | Pipeline Flow Diagram of Write-Read Delay                           | . 11 |

| Table 3.  | Read Switching Characteristics, Adapted from TMS320F240 Data Sheet  | . 13 |

| Table 4.  | Read Timing Requirements, Adapted from TMS320F240 Data Sheet        | . 13 |

| Table 5.  | Write Switching Characteristics, Adapted from TMS320F240 Data Sheet | . 14 |

| Table 6.  | Typical SRAM Read Switching Characteristics                         | . 16 |

| Table 7.  | Typical SRAM Write Switching Characteristics                        | . 16 |

| Table 8.  | Summary of External Memory Interface Signal Transitions             | . 19 |

| Table 9.  | Bus Cycle vs. Execution Cycle Correlation                           | . 29 |

| Table 10. | Execution Cycle Count for External Memory Accesses                  | . 39 |

| Table 11. | Analysis of AVIS_B2 Code                                            | . 42 |

| Table 12. | Instruction Fetch vs. Execution of AVIS_B2 Code over Time           | . 43 |

| Table 13. | Analysis of AVIS_PER Code                                           | . 44 |

| Table 14. | Instruction Fetch vs. Execution of AVIS_PER Code over Time          | . 45 |

| Table 15. | Analysis of AVIS_EXT Code                                           | . 47 |

| Table 16. | Instruction Fetch vs. Execution of AVIS_EXT Code over Time          | . 49 |

# Understanding the TMS320F240 External Memory Interface

# Abstract

This application report describes the features and operation of the Texas Instruments (TI<sup>™</sup>) TMS320F240 digital signal processing (DSP) external memory interface. First, a simple interface example is provided to show the considerations for connecting SRAMs to the 'F240. Following this, the basic operation of a single read and a single write access is described to provide an understanding of the signal relationships and characteristics unique to each type of operation. This analysis forms the foundation upon which the interaction of reads and writes are described in all three program spaces: data, program, and I/O spaces. All descriptions include waveforms captured using a digitizing oscilloscope and assembly code sequences used to generate the waveforms. In addition, examples are included for both zero and one software wait state modes of operation.

In addition to the description of the basic modes of operation, a description of the address visibility mode is provided. This mode enables the user to trace the instruction fetch address at the external address pins when the program code resides in the internal ROM of the '240.

The program name, code excerpts, test setup, and oscilloscope plots of the signals of interest are provided for each case. Actual assembly programs, assemble/link options, and sample debugger initialization files are provided in the appendices.

# **Product Support**

# **Related Documentation**

The following list specifies product names, part numbers, and literature numbers of corresponding TI documentation.

- TMS320C24x DSP Controllers Reference Set Volume 1: CPU System, and Instruction Set, September 1997, Literature number SPRU160 revision B or later

- TMS320C24x DSP Controllers Reference Set Volume 2: Peripheral Library and Specific Devices, December 1997, Literature number SPRU161 revision B or later

- TMS320C240, TMS320F240 DSP Controllers Data Sheet, December 1997, Literature number SPRS042 revision B or later.

# World Wide Web

Our World Wide Web site at **www.ti.com** contains the most up to date product information, revisions, and additions. Users registering with TI&ME can build custom information pages and receive new product updates automatically via email.

# Email

For technical issues or clarification on switching products, please send a detailed email to **dsph@ti.com**. Questions receive prompt attention and are usually answered within one business day.

# Introduction

Traditionally, the DSP external memory interface is documented in two places: the user's guide and the data sheet. Both of these document forms provide the user of the DSP with a focused description of the external memory interface. The *user's guide* provides a general overview of the memory interface features such as pin names, pin descriptions, and address reach. The *data sheet* provides the formal specification of the memory interface and includes important parameters such as operating temperature range, switching characteristics, and timing parameters. Both documents satisfy important needs; however, neither provides all the information a designer may want. This application report will draw information from both sources and expand on several key areas to provide a complete description on the use of the external memory interface.

This report is organized into several sections which cover the basic read and write bus cycles, specific bus cycles resulting from commonly used instructions in all three address spaces, and a description of the address visibility mode and examples on how that may be used for internal program address tracing. The flow of information of the report as a whole and within the individual sections begins with simple concepts and builds on those to cover more advanced topics. The intention is to provide a description suitable for both beginners and experienced users.

As an introduction to the external memory interface, it is first useful to understand how external accesses relate to internal accesses. Table 1 provides a summary of the different types of accesses to program, data, and I/O space, with the external address ranges highlighted in gray. The minimum number of wait states, the minimum number of execution cycles, and the number of delay cycles due to an external read immediately following an external write are included. The minimum number of execution cycle counts are obtained from Chapter 8, "Assembly Language Instructions," of the TMS320C24X DSP Controllers Reference Set Volume 1: CPU System Instruction Set Volume 1.

| V |

|---|

|---|

| Space   | State of MP / MC    | Address Range       | Min. #<br>of Wait<br>States | Access<br>Type | Min. # of<br>Execution<br>Cycles | Write-Read<br>Delay<br>Cycles |

|---------|---------------------|---------------------|-----------------------------|----------------|----------------------------------|-------------------------------|

| Program | 1                   | 0x0 - 0xffff (ext.) | 0                           | fetch          | 1+ws                             | 2                             |

|         |                     |                     |                             | TBLR           | 3+ws                             | -                             |

|         |                     |                     |                             | TBLW           | 4+ws                             | -                             |

|         | 0                   | 0x0 - 0x3fff (ROM)  | 0                           | fetch          | 1                                | -                             |

|         |                     | 0x4000 - 0xffff     | 0                           | fetch          | 1+ws                             | 2                             |

|         |                     |                     |                             | TBLR           | 3+ws                             | -                             |

|         |                     |                     |                             | TBLW           | 4+ws                             | -                             |

| I/O     | 1 or 0              | or 0 0x0 - 0xffff   | 0                           | IN             | 2+ws                             | 2                             |

|         |                     |                     |                             | OUT            | 3+ws                             | -                             |

| Data    | 1 or 0 0x0 - 0x6fff |                     | 0                           | read           | 1                                | -                             |

|         |                     | (DARAM blocks)      |                             | write          | 1                                | -                             |

|         |                     | 0x7000 - 0x73ff     | 2                           | read           | 1+2                              | 2                             |

|         |                     | (peripherals)       |                             | write          | 2+2                              | -                             |

|         |                     | 0x7400 - 0x7fff     | 0                           | read           | 1                                | 2                             |

|         |                     | (Event Manager)     |                             | write          | 2                                | -                             |

|         |                     | 0x8000 - 0xffff     | 0                           | read           | 1+ws                             | 2                             |

|         |                     | (external)          |                             | write          | 2+ws                             | -                             |

Table 1. Summary of Read/Write Execution Cycles for '240 Address Space

The Write-Read delay column provides an indication of the ranges where a CPU delay may be incurred if a read operation immediately follows a write operation. This delay is due to a bus conflict between competing read and write bus cycles. The write operation occurs in the Execute stage of the pipeline, while the read operation occurs in the preceding Operand Fetch stage. In the case of a load accumulator instruction from external memory, the bus cycle associated with the external memory read occurs in the Operand Fetch stage. This places the external operand fetch in conflict with the external write of the store accumulator instruction, which happens in the Execute Stage.

The pipeline flow diagram in Table 2 illustrates how this delay occurs for the following write-read instruction sequence:

| Write | SACL 8000 | ; write to external memory at 0x8000  |

|-------|-----------|---------------------------------------|

| Read  | LACL 8001 | ; read from external memory at 0x8001 |

| -       |      |      |      |      | •    |      |      |      |   |    |

|---------|------|------|------|------|------|------|------|------|---|----|

|         | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9 | 10 |

| Fetch   | SACL | LACL |      |      |      |      |      |      |   |    |

| Decode  |      | SACL | LACL | LACL | LACL | LACL |      |      |   |    |

| Operand |      |      | SACL | х    | х    | dly  | LACL |      |   |    |

| Execute |      |      |      | SACL | SACL | х    | х    | LACL |   |    |

Table 2. Pipeline Flow Diagram of Write-Read Delay

During cycles 4 and 5, the external bus is used for the write operation, and the operand fetch of the LACL instruction must wait for the write operation to clear the bus. A single delay is inserted in the operand fetch stage for cycle 6 to prevent bus contention between the read and the write. In cycle 7, the LACL operand fetch proceeds and subsequently completes execution in cycle 8.

# **External Memory Interface Example**

In this section, the external memory interface will be described by picking a specific example. The timing diagrams and tables are based on those in the *TMS320C240, TMS320F240 DSP Controllers Data Sheet*. In this case, the external clock frequency of the TMS320F240 is programmed to be 20Mhz (CLKOUT = CPUCLK).

The timing parameters contained in Table 3, through Table 5 are derived from those in the *TMS320C240, TMS320F240 DSP Controllers Data Sheet*, with the exception that all references to the parameter, H, have been resolved.

The timing diagrams in Figure 1 show a write-write-read sequence and a read-read-write sequence in external data space with zero wait states. The timing diagrams in Figure 2 are modified to show the same sequence, except with one software wait state. In both cases, the external pin READY, though not shown, is tied to  $V_{CC}$ through a pull-up resistor.

The memory interface design task may be broken into two phases. The first involves narrowing down the search requirement by determining the access time requirement for the memory. The key access time parameter is generally the access time from valid address, and is usually named  $t_{a(A)}$ . For the TMS320F240 device, this parameter is specified by the following equation:

$t_{a(A)} = t_{c(CO)} - t_{d(CO-A)} - t_{su(D-COL)RD} + N \times t_{c(CO)}$

where N is the number of wait states.

By substituting the numbers from Table 3 and Table 4, the access times for zero and one wait states can be calculated as follows:

Ų

$t_{a(A)} = 50$ ns - 17ns - 15ns + 0ns = 18ns, for zero wait states.

$t_{a(A)} = 50$ ns - 17ns - 15ns + 1× 50ns = 68ns, for one wait state.

These values are also provided in Table 4. With this information, it is possible to select a category of memory devices and move to the second phase, which involves a detailed timing analysis.

Figure 1. Typical Timing Sequence for 'F240 Connected to SRAM in Data Space: (a) Write-Write-Read and (b) Read-Read-Write; Zero Wait States

|                                | Parameter                                                  | MIN | MAX | UNIT |

|--------------------------------|------------------------------------------------------------|-----|-----|------|

| t <sub>c(CO)</sub>             | Cycle time, CLKOUT                                         | 50  |     | ns   |

| н                              | Cycle time, one half CLKOUT (H=0.5 $t_{c(CO)}$ )           | 25  |     | ns   |

| t <sub>d(CO-A)RD</sub>         | Delay time, address valid after CLKOUT/IOPC1 low           |     | 17  | ns   |

| $t_{d(\text{CO-SL})\text{RD}}$ | Delay time, STRB low after CLKOUT/IOPC1 low                |     | 10  | ns   |

| t <sub>d(CO-SH)RD</sub>        | Delay time, STRB high after CLKOUT/IOPC1 high              |     | 6   | ns   |

| $t_{d(CO-ACTL)RD}$             | Delay time, PS, DS, IS, and BR low after CLKOUT/IOPC1 low  |     | 10  | ns   |

| t <sub>d(CO-ACTH)RD</sub>      | Delay time, PS, DS, IS, and BR high after CLKOUT/IOPC1 low |     | 10  | ns   |

Table 3. Read Switching Characteristics, Adapted from TMS320F240 Data Sheet

| Table 4. | Read Timing Requirements | s, Adapted from | TMS320F240 Data Sheet |

|----------|--------------------------|-----------------|-----------------------|

|----------|--------------------------|-----------------|-----------------------|

|                                                         | Parameter                                              |                  | MIN | MAX | UNIT |

|---------------------------------------------------------|--------------------------------------------------------|------------------|-----|-----|------|

| t <sub>a(A)</sub>                                       | Access time, read data from address valid $^{\dagger}$ | zero wait states |     | 18  | ns   |

|                                                         |                                                        | one wait state   |     | 68  |      |

| t <sub>su(D-COL)RD</sub>                                | D-COL)RD Setup time, data read before CLKOUT/IOPC1 low |                  | 15  |     | ns   |

| th(D-COL)RD Hold time, data read after CLKOUT/IOPC1 low |                                                        | 2                |     | ns  |      |

|                                                         |                                                        |                  |     |     |      |

† Calculated value is based on other characterized data and not tested.

Figure 2. Typical Timing Sequence for 'F240 Connected to SRAM in Data Space: (a) Write-Write-Read and (b) Read-Read-Write; One Wait State

Table 5. Write Switching Characteristics (from TMS320F240 Data Sheet)

|                          | Parameter                                                   | MIN | MAX | UNIT |

|--------------------------|-------------------------------------------------------------|-----|-----|------|

| t <sub>d(CO-A)W</sub>    | Delay time, address valid after CLKOUT/IOPC1 high           |     | 17  | ns   |

| t <sub>d(CO-D)</sub>     | Delay time, data bus driven after CLKOUT/IOPC1 low          |     | 15  | ns   |

| t <sub>h(A)W</sub>       | Hold time, address valid after WE high $^{\dagger}$         | 25  |     | ns   |

| t <sub>w(WH)</sub>       | Pulse width, WE high                                        | 39  |     | ns   |

| t <sub>w(VVL)</sub>      | Pulse width, WE low                                         | 39  |     | ns   |

| t <sub>d(CO-WL)</sub>    | Delay time, WE low after CLKOUT/IOPC1 low                   |     | 9   | ns   |

| t <sub>d(CO-WH)</sub>    | Delay time, WE high after CLKOUT/IOPC1 low                  |     | 9   | ns   |

| T <sub>su(D)W</sub>      | Setup time, write data valid before WE high $^{\dagger}$    | 44  |     | ns   |

| T <sub>hz(D)W</sub>      | High-impedance time, WE high to data bus Hi-Z $^{\ddagger}$ | 0   | 5   | ns   |

| $T_{d(CO-SL)W}$          | Delay time, STRB low after CLKOUT/IOPC1 low                 |     | 10  | ns   |

| $T_{d(CO-SH)W}$          | Delay time, STRB high after CLKOUT/IOPC1 low                |     | 6   | ns   |

| $T_{d(CO-ACTL)W}$        | Delay time, IS, PS, DS, and BR low after CLKOUT/IOPC1 high  |     | 10  | ns   |

| T <sub>d(CO-ACTH)W</sub> | Delay time, IS, PS, DS, and BR high after CLKOUT/IOPC1 high |     | 10  | ns   |

| $t_{d(CO-RWL)W}$         | Delay time, R/W low after CLKOUT/IOPC1 high                 |     | 10  | ns   |

| $t_{d(CO-RWH)W}$         | Delay time, R/W high after CLKOUT/IOPC1 high                |     | 10  | ns   |

+ Calculated value is based on other characterized data and not tested.

‡ Parameter is specified by design and not tested.

İF

In this section, a detailed timing analysis will be carried out for the 'F240 interfaced to two generic 32k x 8-bit SRAMs in external data space using zero software wait states. A simplified block diagram of the interface is shown in Figure 3.

Figure 3. Simplified Block Diagram of TMS320F240 Interface to a Pair of 32k x 8 SRAMs

A comparison of typical SRAM switching characteristics versus the comparable 'F240 values is listed in Table 6 and Table 7. In general, the 'F240 can meet a typical 15ns SRAM specification. Of course, SRAM specifications vary from manufacturer to manufacturer, so be sure to check with the specification for the SRAM selected.

|   |                  |                                          | MIN | Тур –15 | 'F240 | Margin | Unit |

|---|------------------|------------------------------------------|-----|---------|-------|--------|------|

|   |                  |                                          | or  | SRAM    | Тур   |        |      |

|   |                  |                                          | MAX | Value   | Value |        |      |

| 1 | t <sub>RC</sub>  | Read cycle time                          | min | 15      | 50    | 35     | ns   |

| 2 | t <sub>AA</sub>  | Data access time from address valid      | max | 15      | 18    | 3      | ns   |

| 3 | t <sub>OH</sub>  | Output hold time from address change     | min | 3       | 0     | 3      | ns   |

| 4 | t <sub>AC</sub>  | Data access time from chip select low    | max | 15      | 25    | 10     | ns   |

| 5 | t <sub>OE</sub>  | Data access time from output enable low  | max | 7       | 50    | 43     | ns   |

| 6 | t <sub>LZC</sub> | Output in low z from chip select low     | min | 3       | -     | -      | ns   |

| 7 | t <sub>HZC</sub> | Output in high z from chip select high   | max | 7       | -     | -      | ns   |

| 6 | t <sub>LZO</sub> | Output in low z from output enable low   | min | 0       | -     | -      | ns   |

| 7 | t <sub>HZO</sub> | Output in high z from output enable high | max | 7       | -     | -      | ns   |

Table 6. Typical SRAM Read Switching Characteristics

Table 7. Typical SRAM Write Switching Characteristics

|    |                    |                                        | MIN<br>or<br>MAX | Typ –15<br>SRAM<br>Value | ʻF240<br>Typ<br>Value | Margin | Unit |

|----|--------------------|----------------------------------------|------------------|--------------------------|-----------------------|--------|------|

|    |                    |                                        |                  | 45                       | 100                   | 05     |      |

| 8  | twc                | Write cycle time                       | min              | 15                       | 100                   | 85     | ns   |

| 9  | t <sub>AW</sub>    | Address valid to end of write          | min              | 10                       | 67                    | 57     | ns   |

| 10 | t <sub>CW</sub>    | Chip select low to end of write        | min              | 10                       | 74                    | 64     | ns   |

| 11 | t <sub>AS</sub>    | Address setup to start of write        | min              | 0                        | 17                    | 17     | ns   |

| 12 | t <sub>WP</sub>    | Pulse width, write enable low          | min              | 9                        | 39                    | 39     | ns   |

| 13 | t <sub>AH</sub>    | Address hold time from write end       | min              | 0                        | 25                    | 25     | ns   |

| 14 | $\mathbf{t}_{DW}$  | Data setup time to end of write        | min              | 7                        | 44                    | 33     | ns   |

| 15 | t <sub>DH</sub>    | Data hold time from end of write       | min              | 0                        | 0                     | 0      | ns   |

| 16 | t <sub>WLZ</sub>   | Output in low z from write enable high | min              | 4                        | -                     | -      | ns   |

| 16 | $\mathbf{t}_{HZW}$ | Output in high z from write enable low | max              | 6                        | -                     | -      | ns   |

The 'F240 typical values shown in the preceding two tables were determined using the following analysis:

- 1)  $t_{RC}$  The minimum read cycle time on the 'F240 is one CPU clock cycle, which is given by the spec value  $t_{c(CO)}$  as 50ns.

- t<sub>AA</sub> The maximum time from address valid before data is latched by the 'F240 is calculated by the following equation:

$t_{c(CO)} - t_{d(CO-A)RD} - t_{su(D-COL)RD} = 50ns - 17ns - 15ns = 18ns$

t<sub>OH</sub> For the 'F240, the minimum time data must remain valid after the address changes, t<sub>h(D-COL)RD</sub>, gives a minimum hold time after clock out low. Since the address switches after clock out low, the soonest the address will change is 0ns.

4) t<sub>AC</sub> The maximum time from data strobe low before data is latched by the 'F240 is given by the following equation:

$t_{c(CO)} - t_{d(CO-ACTL)RD} - t_{su(D-COL)RD} = 50$ ns - 10ns -15ns = 25ns. The memory timing number must be less than this value.

5)  $t_{OE}$  The maximum time from write/read low before data is latched into the 'F240 is given by the following equation: 1.5 $t_{c(CO)}$  -  $t_{d(CO-RWL)W}$  -  $t_{su(D-COL)RD}$  = 75ns - 10ns -15ns = 50ns.

The memory timing number must be less than this value.

6)  $t_{LZC}, t_{LZO}$  The times from chip select and/or output enable to low-z of the data pins are used to determine the length of time the data bus will be in high impedance state between the end of a write cycle and the start of a read cycle. These timings determine when the memory will begin driving outputs to the 'F240 data pins. The 'F240 parameter,  $t_{hz(D)W}$ , determines when the 'F240 ceases to drive data out. The bus hi-z time is determined by the difference between these two events. For a memory interface where  $\overline{DS}$  is connected to the memory output enable input, the following equations can be used to determine the minimum hi-z time between a write and a read:

$t_{hz(W-RD)} = min( t_{d(WH-ACTL)} + t_{LZC} - t_{hz(D)W} , t_{d(WH-RWL)} + t_{LZO} - t_{hz(D)W} )$ where,

$t_{d(\text{WH-ACTL})}$  =  $t_{c(\text{CO})}$  +  $t_{d(\text{CO-ACTL})\text{RD}}$  -  $t_{d(\text{CO-WH})}$  = 50ns + 10ns - 9ns = 51ns

and

$t_{d(WH\text{-}RWL)} = 0.5 t_{c(CO)} + t_{d(CO\text{-}RWL)} - t_{d(CO\text{-}WH)} = 25 \text{ns} + 10 \text{ns} - 9 \text{ns} = 24 \text{ns}.$

:  $t_{hz(W-RD)} = min(51 + 3 - 5, 24 + 0 - 5) = min (49ns, 19ns) = 19ns.$

7)  $t_{HZC}$ , $t_{HZO}$  The times from chip select and/or output enable to high-z of the data pins are used to determine the length of time the data bus will be in high impedance state between the end of a read cycle and the start of a write cycle. These timings determine when the memory will stop driving outputs to the 'F240 data pins. The 'F240 parameter,  $t_{d(CO-D)}$ , provides an indication of when the 'F240 begins to drive data out. Since data out is delayed from the falling edge of clock out, the time to low-z can be determined no sooner than that, or Ons from clock out low. The bus hi-z time is determined by the difference between the maximum hi-z time of the memory and the minimum low-z time of the 'F240. For a memory interface where  $\overline{DS}$  is connected to the memory output enable input, the following equations can be used: For  $\overline{CS} = \overline{DS}$ ,

$t_{hz(RD-W)} = 2t_{c(CO)} - t_{HZC} - t_{d(CO-ACTH)W} = 100ns - 7ns - 10ns = 83ns.$

- 8)  $t_{WC}$  The minimum write cycle time for the 'F240 is two CPU clock cycles, which is given by the spec value  $2t_{c(CO)}$ , and is 100ns.

- 9)  $t_{AW}$  The minimum time from address valid either  $\overline{WE}$  or  $\overline{DS}$  high can be calculated by the following equations:

For  $\overline{WE}$  -controlled writes,

1.5 $t_{c(CO)}$  -  $t_{d(CO-A)W}$  +  $t_{d(CO-WH)}$  = 75ns - 17ns + 9ns = 67ns For  $\overline{DS}$  -controlled writes,

$2t_{c(CO)} - t_{d(CO-A)W} + t_{d(CO-ACTH)W} = 100ns - 17ns + 10ns = 93ns$ ∴  $t_{AW} = min(67ns, 93ns) = 67ns.$

10) t<sub>CW</sub> For the 'F240, the minimum time from data strobe low to write enable low is calculated by the following equation:

$1.5t_{c(CO)} - t_{d(CO-ACTL)W} + t_{d(CO-WH)} = 75ns - 10ns + 9ns = 74ns$

11) t<sub>AS</sub> The minimum time from address valid to write enable low is calculated by the following equation:

$0.5t_{c(CO)} + t_{d(CO-WL)} - t_{d(CO-A)W} = 25ns + 9ns - 17ns = 17ns.$

The memory timing number must be less than this value.

12)  $t_{WP}$  The 'F240 parameter,  $t_{w(WL)}$ , provides this value directly, and is 2H-11, or 39ns.

The memory timing number must be less than this value.

13)  $t_{AH}$  The 'F240 parameter,  $t_{h(A)W}$ , provides this value directly, and is H, or 25ns.

The memory timing number must be less than this value.

14)  $t_{DW}$  The 'F240 parameter,  $t_{su(D)W}$ , provides this value directly, and is 2H-6, or 44ns.

The memory timing number must be less than this value.

15)  $t_{DH}$  The 'F240 parameter,  $t_{hz(D)W}$ , provides this value directly, and is 0ns.

The memory timing number must be less than or equal to this value.

16)  $t_{WLZ}$ ,  $t_{HZW}$  These memory parameters are for interfaces where  $\overline{OE}$  is tied low, and are not applicable to this interface example.

# **External Memory Interface Operation**

This section discusses the range of external memory interface operations beginning with the definition of an external bus cycle and its attributes. This is followed by a description of the basic read and write bus cycles. Specific examples are then provided which show the read and write bus cycles in context with instructions in each address space, such as table reads/writes in program space and in/out operations in I/O space. For each example, the code sequences used to create each access is presented and described. All accesses are shown for both zero and one wait state. Each description is supported by oscilloscope waveforms, which illustrate the relationship between the key signals.

# **External Bus Cycle Definition**

External memory accesses are defined in terms of bus cycles, where a bus cycle is the period of time between consecutive falling edges of the CPU clock as observed on the *CLKOUT* pin. By this definition, one bus cycle equals one CPU cycle. A bus cycle is further defined as either active or inactive. An active bus cycle generally occurs when one of the address strobes,  $\overline{DS}$ ,  $\overline{PS}$ , or  $\overline{IS}$ , is in its active low state. By definition then, both read and write bus cycles begin with the falling edge of *CLKOUT*. For read bus cycles, or hereafter just reads, all address, data and control signals also switch or are latched by the falling edge of *CLKOUT*. In contrast, for writes, only data,  $\overline{STRB}$ , and  $\overline{WE}$  switch with respect to the falling edge of *CLKOUT*. This relationship between transition of the clock output and the external memory interface signals is summarized in Table 8.

| Bus Cycle | Clock Out<br>Transition | Signal Name                                                                                           |

|-----------|-------------------------|-------------------------------------------------------------------------------------------------------|

| Read      | Falling edge            | $A0-15$ , $D0-15$ , $\overline{STRB}$ , $\overline{DS}$ , $\overline{PS}$ , and $\overline{IS}$ .     |

| Write     | Falling edge            | $D0-15$ , $\overline{STRB}$ , and $\overline{WE}$ .                                                   |

|           | Rising edge             | $A0-15$ , $\overline{DS}$ , $\overline{PS}$ , $\overline{IS}$ , $W/\overline{R}$ and $R/\overline{W}$ |

Table 8. Summary of External Memory Interface Signal Transitions

The instruction set of the 'C2xx CPU includes many instructions which will generate external read or write bus cycles. Read bus cycles can be generated in data space by load accumulator, and bit test instructions, or in program space by instruction fetches or table read instructions, or in I/O space by the in instruction. Similarly, write bus cycles can be generated by many different instructions and in all three address spaces. The simplest way to generate reads and writes is to use the load/store accumulator instructions to access external data space. The basic read and write bus cycle will be described using these two instructions as the metric.

#### Read Cycles

The simple code sequence in Example 1 is written to generate two distinct read bus cycles on the external memory interface. This code provides a tight loop for synchronization of the oscilloscope and capture of the key signal transitions that define the read bus cycle.

#### Example 1. External Read to Data Space Code Sequence - xidstime.asm

```

R_TIMING:

```

```

LDP #08000h/80h ; use Data Page of first location in

; external data space

RLOOP

LACL 0 ; read from external memory 0x8000

NOP

LACL 1 ; read from external memory 0x8001

B RLOOP

```

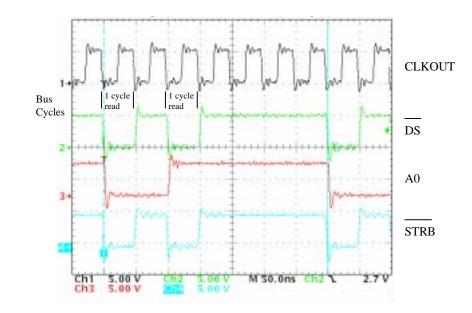

The resulting signal trace, shown in Figure 4, captures a one-cycle read, one inactive cycle (NOP), another one-cycle read, four inactive cycles (branch) and then repeats the first one-cycle read. Every read cycle begins when  $\overline{DS}$  ( $\overline{PS}$  or  $\overline{IS}$ ) and  $\overline{STRB}$  transition to their active low states and addresses becoming valid with the falling edge of *CLKOUT*. The read cycle ends when  $\overline{DS}$  ( $\overline{PS}$  or  $\overline{IS}$ ) and  $\overline{STRB}$  switch back to their inactive high states, again coincident with the falling edge of *CLKOUT*. The incoming data is also latched by this last falling edge of *CLKOUT*. Note that the address pins retain the last valid address until the next valid bus cycle, which in this case is the second read. All signals transition based on the falling edge of *CLKOUT*, as previously defined in Table 8.

Figure 4. Trace of External Data Space Reads with Zero Wait States

The one wait state read bus cycle is very similar to the zero wait state case just discussed. The simple code change shown in Example 2 will reconfigure the software wait state generator for one wait state in data space.

#### Example 2. Code Example for One Software Wait State in Data Space

```

* Load Address of wait-state generator register, WSGR, into AR1,

* and turn off address visibility mode, AVIS.

LDP #0 ; set DP to page zero, includes B2 RAM

SPLK #02h,070h ; 70h <= 0002h

OUT 70h,0ffffh ; WSGR <= (07h). AVIS off; 1 ws for DS, 0

; ws for IS & PS

```

The result of this change can be seen in Figure 5. The only difference from the zero wait state case is that each read cycle now takes two *CLKOUT* cycles to complete. The addition of one wait state has done just that: added one additional cycle to each access. All other signal transitions remain the same.

Figure 5. Trace of External Data Space Reads with One Wait States

#### Write Cycles

The discussion of the basic write bus cycle proceeds using the same approach to the previous read discussion. The code sequence in Example 3 generates two distinct write bus cycles on the external memory interface.

Example 3. External Write to Data Space Code Sequence - xidstime.asm

| W_TIMING: |             |                                                                                                                              |

|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------|

| LDP       | #08000h/80h | i ; use Data Page of first location in external ds                                                                           |

| WLOOP     |             |                                                                                                                              |

| SA        | CL 0        | ; write to external memory 0x8000                                                                                            |

| NOP       |             |                                                                                                                              |

| SACL      | . 1         | ; write to external memory 0x8001                                                                                            |

| В         | WLOOP       |                                                                                                                              |

|           |             | The resulting signal trace, shown in Figure 6, captures two<br>consecutive three-cycle writes, three inactive bus cycles (br |

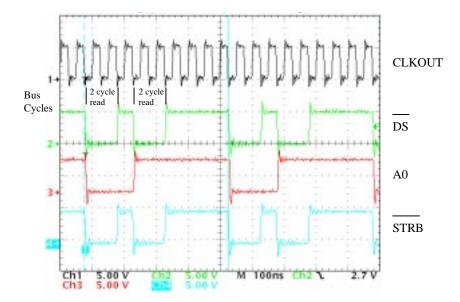

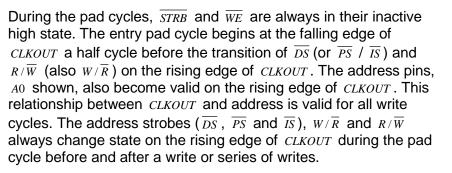

The resulting signal trace, shown in Figure 6, captures two consecutive three-cycle writes, three inactive bus cycles (branch), and then repeats. The write bus cycle is different from the read bus cycle described in the previous section. The main difference is that write bus cycles always have one inactive (pad) cycle of *CLKOUT* surrounding a write operation; one cycle before and one cycle after. This pad allows a smooth transition between the write operation and any adjacent bus operations, including other writes, and prevents bus contention between read and write operations.

For the actual write operation,  $\overline{STRB}$  and  $\overline{WE}$  both go active low on the falling edge of *CLKOUT* and stay low for one cycle, returning high on the next falling edge of *CLKOUT*. Write data is driven by the '240 on the same falling edge of *CLKOUT* that cause  $\overline{STRB}$  and  $\overline{WE}$  to go low, and is held for a little more than one cycle of *CLKOUT*. The exit pad cycle for the first write occurs during the next cycle of *CLKOUT*, and is immediately followed by the entry pad cycle of the second write.

Figure 6. Trace of External Data Space Writes with Zero Wait States

The one wait state write bus cycle is very similar to the zero state bus cycle. The resulting trace is shown in Figure 7. With the addition of one state, the active low time of both  $\overline{STRB}$  and  $\overline{WE}$  has been extended by one cycle for a total of two *CLKOUT* cycles. The entry and exit pad cycles remain one cycle each, for a four bus cycle write.

ſ.

Figure 7. Trace of External Data Space Writes with One Wait States

One final note on the  $W/\overline{R}$  and  $R/\overline{W}$  signals. The decoding logic used for  $W/\overline{R}$  is different than that used for  $R/\overline{W}$ . For accesses in data space between 0x7000 and 0x7fff, the  $W/\overline{R}$  signal is not blocked, and transitions of this signal for internal accesses in this range are driven external to the device. All other control, address and data signals are in their inactive state when this occurs.

#### **Typical External Data Space Access Sequences**

To this point, both read and write bus cycles have been described and examples presented which show how these bus cycles look. Rarely are only reads or only writes performed in isolation. A more common and practical case would involve both reads and writes in varying combinations. The next two subsections discuss examples that show different interactions between read and write bus cycles in external data space. The read-read-write sequence will demonstrate bus behavior for consecutive reads and also for the read-write boundary. Similarly, the write-write-read sequence demonstrates the bus behavior for consecutive writes and for the write-read boundary. All other bus activity in external data space can be extrapolated based on these two sequences.

#### **Read-Read-Write Sequence**

The simple code sequence in Example 4 is written to generate the consecutive read-read-write bus cycles on the external memory interface. This code provides a tight loop for synchronization of the oscilloscope and capture of the signal key signal transitions which define the bus cycles.

Example 4. External Data Space Read-Read-Write Sequence - xidstime.asm

| RRW_TI | MING:   |          |   |                                            |

|--------|---------|----------|---|--------------------------------------------|

|        | LDP #08 | 000h/80h |   | Data Page of first location in external ds |

| RLOOP2 |         |          |   |                                            |

|        | LACL    | 0        | ; | read from external memory 0x8000           |

|        | LACL    | 1        | ; | read from external memory 0x8001           |

|        | SACL    | 2        | ; | write to external memory 0x8002            |

|        | В       | RLOOP2   |   |                                            |

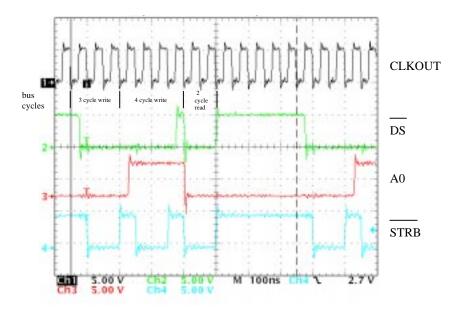

The resulting signal traces for zero and one wait states are shown in Figure 8 and Figure 9. Notice that the  $\overline{STRB}$  and  $\overline{DS}$  signals do not change from the first to the second read cycle. This is typical for consecutive reads. Only the address and data signals switch between consecutive reads. For zero wait states, each read completes in one cycle, as expected. In general, n reads require n bus cycles. In the case of one wait state, both reads are extended by one additional cycle, for two two-cycle reads.

The read-write boundary is defined by the single inactive bus cycle between the read and write bus cycles. This inactive bus cycle is due to the pipeline execution of the read, which occurs one cycle after the read bus cycle. The write bus cycle actually begins immediately after the read completes execution, even though it appears as if a one-cycle delay occurs.

Figure 9. Trace of External Data Space Read-Read-Write Sequence, One Wait State

**L**ij

# Write-Write-Read Sequence

The write-write-read sequence covers the opposite situation as presented by the read-read-write sequence. In this case, consecutive writes and the write-read boundary are discussed. The simple code sequence in Example 5 generates consecutive write-write-read bus cycles on the external memory interface.

Example 5. External Data Space Write-Write-Read Sequence - xidstime.asm

| WWR_TIMING: |

|-------------|

|-------------|

|        | LDP #08 | 8000h/80h | ;1 | use Data Page of first location in<br>;external ds |

|--------|---------|-----------|----|----------------------------------------------------|

| WLOOP2 |         |           |    |                                                    |

|        | SACL    | 0         | ;  | write to external memory 0x8001                    |

|        | SACL    | 1         | ;  | write to external memory 0x8001                    |

|        | LACL    | 2         | ;  | read from external memory 0x8002                   |

|        | В       | WLOOP2    |    |                                                    |

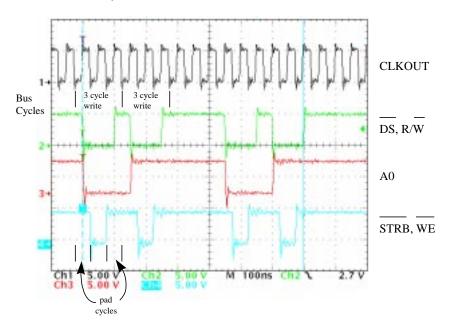

The resulting signal traces for zero and one wait states are shown in Figure 10 and Figure 11. Notice that the  $\overline{STRB}$  and  $\overline{WE}$  signals switch from their active to inactive state between the first and second write cycles. This is the pad cycle described previously, and is typical for consecutive writes. Only the  $\overline{DS}$  and read/write  $(W/\overline{R} \text{ and } R/\overline{W})$  signals remain in their active state. For zero wait states, single writes require three bus cycles. For two consecutive writes, however, only five bus cycles are required; two for the first write and three for the last write. This is because consecutive writes share a pad cycle. In general, n consecutive writes require 2n+1 bus cycles. In the case of one wait state, both writes are extended by one additional cycle, for one three-cycle and one four-cycle write.

The transition from write to a read bus cycle in this case is immediate. The read bus cycle begins as soon as the write bus cycle completes.

Figure 10. Trace of External Data Space Write-Write-Read Sequence, Zero Wait States

Figure 11. Trace of External Data Space Write-Write-Read Sequence, One Wait State

Ü

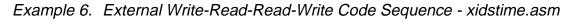

The definition and duration of an external bus cycle provides a consistent and easy to understand method of describing external memory accesses. However, the number of bus cycles per access is not necessarily equal to the number of execution cycles of the associated instruction. In the case of load accumulator instructions, the number of bus cycles is consistent with the execution time. But, in the case of a table read instruction, there will be one bus cycle for the external read, while the number of execution cycles is typically three (depending on operand source, destination and wait states). The same difference exists for write bus cycles. For a store accumulator instruction, the write bus cycle count is three, while the execution cycle count is only two. However, in the case of a write to I/O space, both bus cycle count and execution cycle count are three cycles. Clearly, there is no easily stated, general relationship between the number of bus cycles and execution cycles for an instruction.

The purpose of this section is to provide a reference for determining the difference between the execution and bus cycle counts. Since the load and store accumulator instructions have been described in detail with regard to bus cycles, these instructions will be used to compare execution and bus cycle counts. A comparison of execution and bus cycles for the key boundary conditions is provided in Table 9.

| Bus Operation (loads and stores only) | # Bus<br>Cycles | # Execution<br>Cycles |

|---------------------------------------|-----------------|-----------------------|

| single Read                           | 1               | 1                     |

| n consecutive Reads                   | n               | n                     |

| single Write                          | 3               | 2                     |

| n consecutive Writes                  | 2n+1            | 2n                    |

| consecutive Write-Write-Read          | 3+3+1           | 2+(2+2)+1             |

| consecutive Read-Read-Write           | 1+1+3           | 1+1+2                 |

Table 9. Bus Cycle vs. Execution Cycle Correlation

A write-read-read-write sequence is presented to illustrate how this comparison is performed. The resulting signal trace is shown in Figure 12. There are eight active bus cycles: two three-cycle writes and two one-cycle reads. From an execution point of view, external reads take one cycle and writes take two cycles. This leaves two additional cycles unaccounted for. These two cycles are due to the write-read delay discussed in the introduction. If correlation between the bus cycle and execution cycle is needed, this same method can be applied to other code sequences.

| WRRW_TIM | 4ING:  |          |   |                                                      |

|----------|--------|----------|---|------------------------------------------------------|

| L        | DP #08 | 000h/80h |   | ; use Data Page of first location in<br>;external ds |

| RLOOP2   |        |          |   |                                                      |

| S.       | ACL    | 3        | ; | write to external memory 0x8003                      |

| L.       | ACL    | 0        | ; | read from external memory 0x8000                     |

| L.       | ACL    | 1        | ; | read from external memory 0x8001                     |

| S.       | ACL    | 2        | ; | write to external memory 0x8002                      |

| В        | 5      | RLOOP2   |   |                                                      |

Figure 12. Trace of External Data Space Write-Read-Read-Write Sequence

# **External Program Space Accesses**

Accesses to external program space are essentially no different from data space accesses. The same basic read and write operations take place, just the instructions used to perform these operations are different. For external program space, there are three types of accesses. To perform read operations, the program fetch and table read instruction are used. For write operations, the table write instruction is used. The discussion of external program space accesses will focus on these three types.

ĬF

# **Program Fetch Cycles**

External program, or instruction, fetch cycles take place whenever the program code is located in external program space. Any code sequence located as such would result in program space read operations. The code used to generate the trace in this discussion is shown in Example 7. The basic instruction sequence in the LOOP section of code is:

- Store accumulator to external data space

- Load accumulator from external data space

The purpose of this particular instruction sequence is to show how program fetches are interleaved with other external memory accesses.

Example 7. External Program Instruction Fetch Code Sequence - xi\_fetch.asm

FETCH\_TEST:

LOOP

LAR AR1,#8700h LACC #05555h SACL \*+ LACL \*-B LOOP

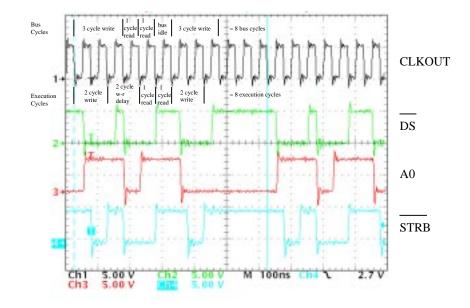

The resulting signal trace from this code loop is captured in Figure 13. This trace shows *CLKOUT* (Ch.1),  $\overline{PS}$  (Ch.2),  $\overline{DS}$  (Ch.3), and  $\overline{WE}$  (Ch.4). Before discussing the interleave aspect of this signal trace, it is important to point out that all signals switch with respect to *CLKOUT* as described by the guidelines provided in Table 8. For reads, both  $\overline{PS}$  and  $\overline{DS}$  falling edge transitions are with respect to *CLKOUT* falling. For writes,  $\overline{DS}$  falling edge occurs on the rising edge of *CLKOUT* and  $\overline{WE}$  falling edge occurs on the falling edge of *CLKOUT*.

Figure 13. Trace of External Program Space Instruction Fetch with Zero Wait States

The program fetch operation works like any read operation in data space. The only difference is that  $\overline{PS}$  is active instead of  $\overline{DS}$ . The alternating active low periods for  $\overline{PS}$  and  $\overline{DS}$  show how the interleaving of both access types occurs when using the external memory interface. Normally, a write-read sequence takes three cycles for the write and one cycle for the read. In the case where an external instruction fetch coincides with an external data space access, the effective execution time of the write-read sequence is extended by one cycle for both the write and the read due to the one-cycle instruction fetch required for both instructions.

The effective execution of the data space accesses is further delayed by the addition of one wait state in program space. Example 8 shows the code modification necessary to configure the external memory interface for one program space and zero data and I/O space wait states.

#### Example 8. Modification of Example 7 Code for One Software Wait State

```

* Load Address of wait-state generator register, WSGR, into AR1,

* and turn off address visibility mode, AVIS.

LDP#0 ; set DP to page zero, includes B2 RAM

SPLK #01h,070h ; 70h <= 0001h

OUT 70h,0fffh ; WSGR <= (07h). AVIS off; 1 ws for PS, 0

; ws for IS & DS

```

The resulting signal trace in Figure 14 shows the same signals as in Figure 13. In this trace, the instruction fetches take two cycles, extending the effective execution times to five cycles for the data space write and three cycles for the data space read.

#### **Table Read and Write Cycles**

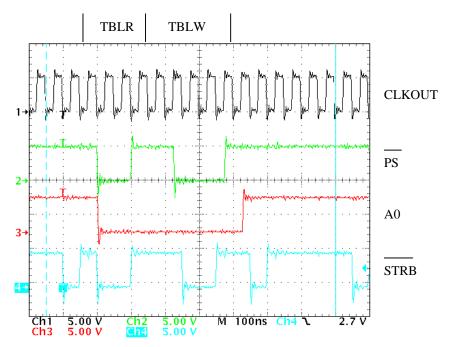

Besides the instruction fetch, the table read and table write operations are commonly used to access program space memory. Example 9 shows the code sequence used in this description. This sequence loads the external program space address 0xce00 into the accumulator for later use by the table read (TBLR) and table write (TBLW) instructions. The store accumulator (SACL) instruction that surrounds the table instructions provides an externally visible indication of when the TBLR instruction begins execution and the TBLW instruction ends execution. This makes for easier interpretation of the trace results shown in Figure 15, which shows *CLKOUT* (Ch.1),  $\overline{PS}$  (Ch.2),  $\overline{WE}$  (Ch.3), and  $\overline{STRB}$ (Ch.4).

Ĭ.

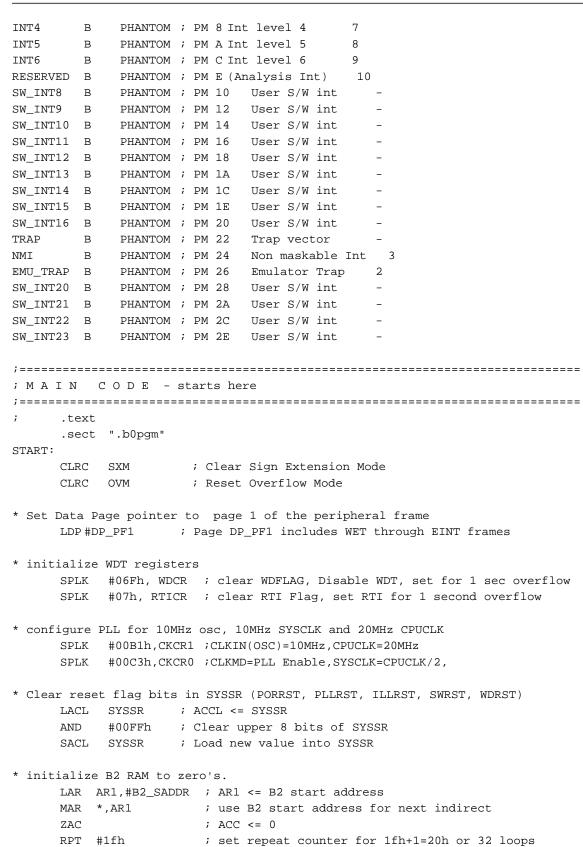

Example 9. External Table Read and Table Write Code Sequence - xi\_table.asm

```

Begin main body of code.

Access external program space

LAR AR1,#08701h

; AR1 <= External Data RAM

MAR *, AR1

LACC

#0ce00h ;

*

PS

SACL

TBLR

060h

060h

TBLW

*

SACL

B PS

```

The resulting trace actually shows three write operations in data space, which occur when  $\overline{WE}$  and  $\overline{STRB}$  are low, and  $\overline{PS}$  is high. The first two  $\overline{DS}$  write operations bound the table read and write instructions. The third is a repeat of the first.

Figure 15. Trace of External Table Read and Write Operations with Zero Wait States

Understanding the TMS320F240 External Memory Interface

ŦF

The table read instruction begins with the first falling edge of  $\overline{PS}$ . It behaves just like the program fetch and data read accesses described in previous sections. All control signals switch as described in Table 8.

To correctly interpret the trace results for table reads or writes, it is necessary to understand how these instructions are executed by the 'C2xx CPU. The TBLR and TBLW instructions execute in a minimum of three cycles. This breaks down into three tasks:

- Program space address calculation

- Program space access

- Data space access

In a zero wait state system, each of these three tasks will take one cycle, which results in the three cycle minimum. The order of execution for these tasks is different, depending on whether a TBLR or TBLW instruction is executed. For TBLR, where data from program space (read) is copied to data space (write), the order is as presented. Tasks two and three switch places for table writes, where data from data space (read) is copied to program space (write).

In the case of an external source/destination for a TBLR/TBLW operation, the number of wait states associated with the read/write to program space will be added to the minimum cycle count. In the case shown in Figure 15, both program and data space are configured for zero wait states. However, since all external writes take two cycles, the TBLW instruction takes four cycles to complete. The labels at the top of the trace show the clock cycles during which the TBLR and TBLW instructions execute.

The impact of one wait state for program memory accesses can be seen in Figure 16. The table read operation now takes four cycles and the table write operation takes five cycles.

# **External I/O Space Accesses**

At this point, the simple read and write accesses have been described for the data space accesses. Then, these same basic operations were shown to be "dressed-up" within the more complicated table read and write operations in program space. I/O space accesses are accomplished with the IN (read) and OUT (write) instructions, which are similar to the program space TBLR and TBLW instructions. Both are multi-task, multi-cycle instructions that include the basic read and write operations.

# **IN and OUT Cycles**

Each IN or OUT instruction consists of two accesses: one in data space and one in I/O space. In the case of the IN instruction, the read from I/O space takes place first, followed by the writing of that value into a data space location. For the OUT instruction, a read from a data space address is performed first, followed by a write to I/O space.

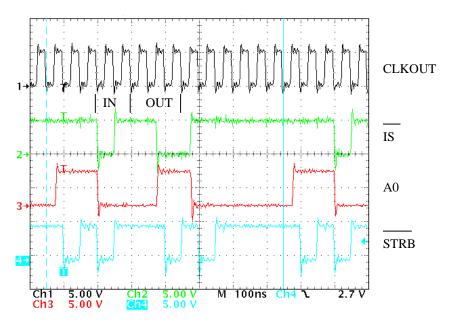

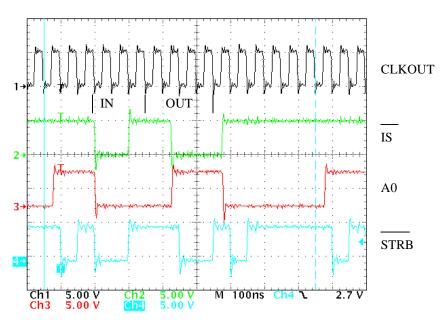

Example 10. External IN and OUT Code Sequence - xi\_inout.asm

```

* * * * * *

*****

Access external I/O space

INOUT:

;AR1 <= External Data RAM

LAR AR1,#08701h

MAR *, AR1

IS

SACL

*+

IN 060h,8876h

;Read I/O at 0x8876 and write to

; DARAM at 0x60

OUT 060h,8877h

;Read DARAM at 0x60 and write to

; I/O at 0x8877

SACL

*_

B IS

```

The code sequence used for this description is shown in Example 10. The store accumulator (SACL) instruction that surrounds the IN and OUT instructions provides an externally visible indication of when the IN instruction begins execution and the OUT instruction ends execution. This makes for easier interpretation of the trace results shown in Figure 17, which shows *CLKOUT* (Ch.1),  $\overline{IS}$  (Ch.2),  $\overline{WE}$  (Ch.3), and  $\overline{STRB}$  (Ch.4).

The IN instruction begins with the first falling edge of  $\overline{IS}$ . It behaves just like the program fetch and data read accesses described in previous sections. All control signals switch as described in Table 8.

Figure 17. Trace of External IN and OUT Operations with Zero Wait States

The best case execution cycle counts for the IN and OUT instructions are two and three cycles, respectively. In the case of an external source/destination for an IN/OUT operation, the number of wait states associated with the read/write to I/O space will be added to the minimum cycle count. In the case shown in Figure 17, both I/O and data space are configured for zero wait states. The IN instruction will still take two cycles, and the OUT instruction will take three cycles to complete. The labels at the top of the trace show the clock cycles during which the IN and OUT instructions execute.

Figure 18. Trace of External IN and OUT Operations with One Wait State

The impact of one wait state for I/O memory accesses can be seen in Figure 18. The IN instruction now takes three cycles and the OUT instruction takes four cycles.

## IO Space Decoding for the Range 0xff00-0xfffe

When the external memory interface was designed, it was decided to only block  $\overline{IS}$  in the address range 0xff00 to 0xfffe in IO space. Decoding and blocking the other signals ( $\overline{WE}$ ,  $\overline{STRB}$ ,  $W/\overline{R}$ ,  $R/\overline{W}$ , and *A0-A15*) would have added additional delays to all other memory accesses. Since the address range 0xff00 to 0xfffe is reserved, it was decided not to add the additional decode logic required to prevent these pins from switching. Any external peripheral or memory located in I/O space must use the  $\overline{IS}$  signal as part of its chip select logic. An inactive high state on  $\overline{IS}$  is sufficient to block any accesses to I/O space above 0xff00. For accesses to I/O space in the range 0xff00-0xffff, the pins  $\overline{WE}$ ,  $\overline{STRB}$ ,  $W/\overline{R}$ ,  $R/\overline{W}$ , and *A0-A15* switch, even when  $\overline{IS}$  is inactive.

## **External Access Summary**

The previous three sections presented an in-depth look at the external memory interface characteristics for the key instructions and/or access types for each of the three address spaces: program, data, and I/O.

The results from each section are summarized in Table 10.

| Address<br>Space | Instruction | Zero Wait<br>States | One Wait<br>State |

|------------------|-------------|---------------------|-------------------|

| Data             | LACL        | 1                   | 2                 |

|                  | SACL        | 2                   | 3                 |

| Program          | Fetch       | 1                   | 2                 |

|                  | TBLR        | 3                   | 4                 |

|                  | TBLW        | 4                   | 5                 |

| I/O              | IN          | 2                   | 3                 |

|                  | OUT         | 3                   | 4                 |

Table 10. Execution Cycle Count for External Memory Accesses<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> The execution cycle counts in this table are for the specific examples presented in this report. These counts will vary depending on the source and destination of the data.

## Address Visibility Mode

The external memory interface has the capability to provide program address trace through the use of address visibility mode. This mode is controlled by the AVIS bit in the wait state generator register. At reset, the AVIS bit is set to 1 and address visibility mode is enabled.

Due to the pipelined architecture of the 'C2xx CPU, interpretation of the program address trace can be difficult. A few simple programs are provided to aid in this interpretation. These programs allow the scope to be used to trace the program fetch sequence. The control signals,  $\overline{DS}$  and *CLKOUT*, and the address pins, *A*0, *A*1, and *A*2, are monitored to indicate the access type. Examples of the following three ranges in data space are presented and analyzed:

- □ Internal data space at 0x0060 (B2 DARAM)

- Internal data space at 0x7098 and 0x709a (I/O port register PADATDIR and PBDATDIR)

- External data space at 0x8000 and 0x8001

To interpret the program address trace, it is also helpful to understand the time delay between the fetch and execution of each instruction. In the 'C2xx CPU, there are four pipeline stages:

- Instruction Fetch

- Instruction Decode

- Operand Fetch

- Instruction Execute

In the following three sections, a program code segment and resulting signal trace will be presented, followed by an instruction address to execute a correlation exercise. This exercise will make use of a code analysis which includes the instruction address, the predetermined cycle count for each instruction, and an abbreviation of the instruction. The code analysis and the signal trace data are then used to generate an idealized version of the execution path of each instruction, presented with respect to the four pipeline stages. This idealized pipeline view is provided to assist in the interpretation of the address trace but is not necessarily an exact representation of how the 'C2xx pipeline processes instructions. Even so, this approximation does provide a reasonable foundation on which to base an understanding of the fetch address traces presented herein.

## **Address Trace and Internal Accesses**

The simplest case to interpret the program address trace provided by the Address Visibility feature is when all program activity is confined within the CPU. This includes accesses to the CPU registers ST0 & ST1, internal DARAM blocks B0, B1 and B2, and flash EEPROM. Since the peripheral and external buses are not in use, all program address bus activity can be sent to the external address bus.

The code sequence used for this first case is presented in Example 11.

Example 11. Internal B2 DARAM Code Sequence - avis\_chk.asm

```

AVIS_B2:

* Load Address of wait-state generator register, WSGR, into AR1,

* and turn off address visibility mode, AVIS.

LDP #0 ; set DP to page zero, includes B2 RAM

SPLK #08h,070h ; 70h <= 0000h

OUT 70h, 0ffffh ; WSGR <= (07h). AVIS ON; 0 ws for DS, IS

;& PS

SPLK #03h,071h ;

MAR *, AR1

LOOP

LACL 60h

; read from B2 DARAM

LACL 61h

;

RPT 71h ; stop fetching for 4 cycles

NOP

SACL 64h

; write to B2 DARAM

SACL 67h

;

LOOP

в

```

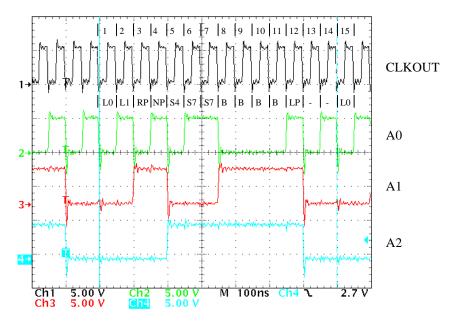

Based on the linked output file and the instruction execution times, a table summarizing the key attributes of this program excerpt is compiled in Table 11. Included in this table are the instruction, an abbreviation used in the pipeline chart, the linked program address, and the execution cycle count of each instruction. The total execution time for one iteration of this code loop is 14 cycles.

| Abbreviation | Instruction/Operand | Program Address     | # Cycles |

|--------------|---------------------|---------------------|----------|

| LO           | LACL 60h            | 0x30                | 1        |

| L1           | LACL 61h            | 0x31                | 1        |

| RP           | RPT 71h             | 0x32                | 2        |

| NP           | NOP                 | 0x33                | 4x1      |

| S4           | SACL 64h            | 0x34                | 1        |

| S7           | SACL 67h            | 0x35                | 1        |

| В            | В                   | 0x36                | 4        |

| LP           | LOOP                | 0x37                | -        |

|              | Total Loop Ex       | ecution Cycle Count | 14       |

Table 11. Analysis of AVIS\_B2 Code

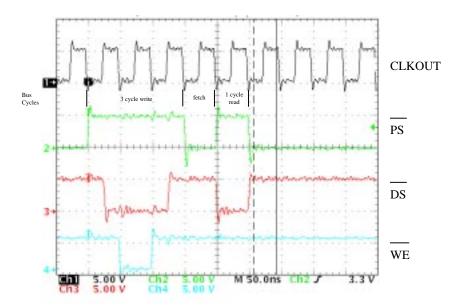

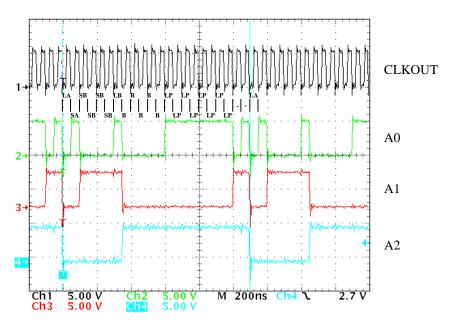

The resulting signal trace in Figure 19 shows the address pins, *A*0, *A*1, and *A*2, and confirms the execution cycle count of 14 cycles. Each address corresponding to the instruction fetch is present on the external address pins, starting with 0x30 for L0 and continuing through 0x37 for LP.

Figure 19. Address Visibility Trace on A0-2 for Internal DARAM Accesses

This trace also provides visibility into the relationship between instruction fetch and execution. For example, the address 0x35 of S7 remains on the external address pins for two cycles, which corresponds to the execution of the RPT instruction. Likewise, the address of 0x36 of B remains on the external address pins for four cycles, which corresponds to the execution of the NOP instruction, repeated four times. This relationship is shown graphically in Table 12. Each cycle of the code loop is numbered from 1 to 14. The address present on the external address pins and the approximate instruction path through the pipeline are listed under the corresponding cycle.

|         | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Address | 0  | 1  | 2  | 3  | 4  | 5  | 5  | 6  | 6  | 6  | 6  | 7  | 8  | 9  | 0  |

| Fetch   | L0 | L1 | RP | NP | S4 | S7 | S7 | В  | В  | В  | В  | LP | -  | -  | L0 |

| Decode  | -  | L0 | L1 | RP | NP | S4 | S4 | S7 | S7 | S7 | S7 | В  | LP | -  | -  |

| Operand | -  | -  | L0 | L1 | RP | NP | NP | S4 | S4 | S4 | S4 | S7 | В  | LP | -  |

| Execute | LP | -  | -  | L0 | L1 | RP | RP | NP | NP | NP | NP | S4 | S7 | В  | LP |

Table 12. Instruction Fetch vs. Execution of AVIS\_B2 Code over Time

In this case when only internal resources are accessed by the program code, interpretation of the address trace provided by address visibility mode is easily understood by examination of a few external pins using an oscilloscope. The pipeline chart and code analysis table provide additional support and confirmation of the expected operation.

## Address Trace with Peripheral Accesses

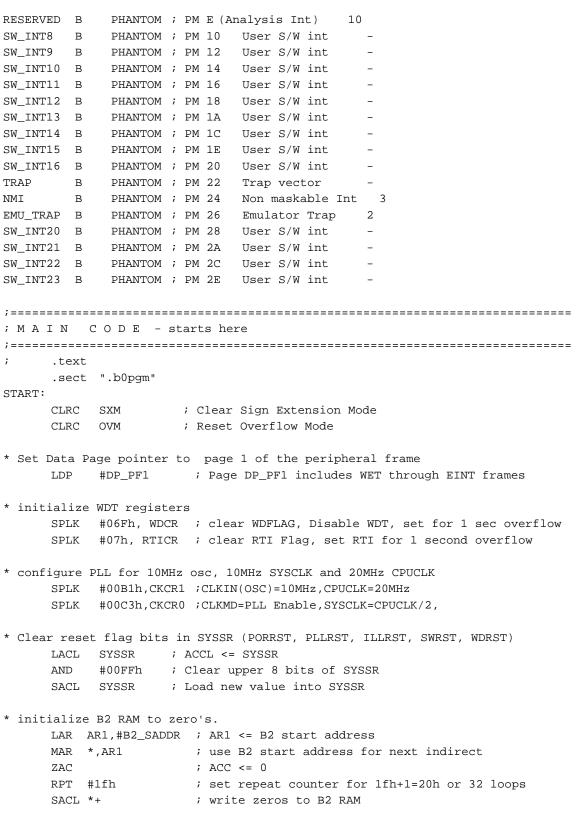

A somewhat more complicated example is provided which demonstrates how multi-cycle instructions affect instruction fetch. The program code accesses only on-chip resources, but the destination of the accesses has changed to the peripheral registers. As in the previous case, the code sequence (Example 12), code analysis (Table 13), signal trace (Figure 20), and pipeline chart (Table 14) are provided as reference.

## Example 12. Peripheral Register Access Code Sequence - avis\_chk.asm

```

AVIS_PER

* Load Address of wait-state generator register, WSGR, into AR1,

* and turn off address visibility mode, AVIS.

LDP #0

; set DP to page zero, includes B2 RAM

SPLK #08h,070h ; 70h <= 0000h

OUT70h,0ffffh ; WSGR <= (07h). AVIS ON; 0 ws for DS, IS

;& PS

LDP #07080h/80h ; use Data Page of first location in

; external ds

MAR *, AR1

LOOP1

LACL PADATDIR

;

SACL PADATDIR

SACL PBDATDIR

LACL PBDATDIR

в

LOOP1

```

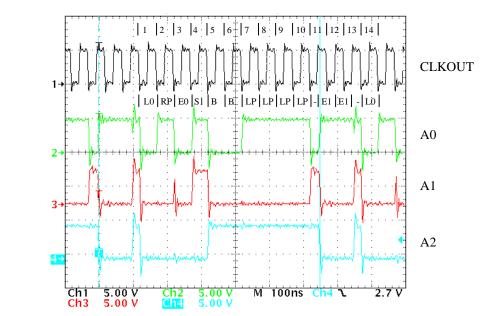

The code sequence requires 22 cycles per iteration. Since all accesses are internal to the device, every instruction fetch is visible on the external address pins. Due to the many multi-cycle instructions, most instruction fetch addresses are present for more than one cycle. This makes interpretation of the execution cycle time of the instruction more difficult, but the instruction fetch sequence is not interrupted.

Table 13. Analysis of AVIS\_PER Code

| Abbreviation | Instruction/Operand  | Program<br>Address | # Cycles |

|--------------|----------------------|--------------------|----------|

| LA           | LACL PADATDIR        | 0x40               | 4        |

| SA           | SACL PADATDIR        | 0x41               | 5        |

| SB           | SACL PBDATDIR        | 0x42               | 4+1      |

| LB           | LACL PBDATDIR        | 0x43               | 4        |

| В            | В                    | 0x44               | 4        |

| LP           | LOOP1                | 0x45               | -        |

|              | Total Loop Execution | Cycle Count        | 22       |

The resulting signal trace in Figure 20 shows the address pins, *A*0, *A*1, and *A*2, and confirms the execution cycle count of 22 cycles. Each address corresponding to the instruction fetch is present on the external address pins, starting with 0x40 for LA and continuing through 0x45 for LP.

Figure 20. Address Visibility Trace on A0-2 for Peripheral Register Accesses