Application Report SPRAB58—July 2009

# TCI648x Antenna Interface Programming

Communication Infrastructure

Brighton Feng, Jane Lu, Albert Bae

### Abstract

The TMS320TCI648x antenna interface (AIF) is a peripheral module that supports transfers of baseband antenna IQ data between uplink and downlink baseband DSP processors and a high-speed SERDES interface. The AIF supports both the OBSAI RP3 and CPRI protocols.

This document describes how to use the TCI648x Antenna Interface. Example codes based on AIF operation with the TCI6488 EVM are provided.

#### Contents

| 1 | Introduction                                                                 | 3    |

|---|------------------------------------------------------------------------------|------|

| 2 | TCl6488 EVM and AIF Test Setup                                               | 6    |

| 3 | Antenna Data Structure and EDMA Configuration                                | .10  |

|   | 3.1 AIF Antenna Data Buffer Structure                                        | .10  |

|   | 3.2 EDMA Configuration for a DL-Type Antenna Stream in AIF RAM               | .15  |

|   | 3.3 EDMA configuration for UL_RSA type antenna stream in AIF RAM             |      |

|   | 3.4 EDMA Configuration for Packet-Switched FIFO                              |      |

|   | 3.5 EDMA Configuration for CPRI Control Words                                |      |

|   | 3.6 RAC Antenna Data Buffer Structure                                        |      |

|   | 3.7 EDMA Configuration for RAC                                               |      |

|   | 3.8 Antenna Data Buffer Structure in DSP Memory                              |      |

|   | 3.9 EDMA Configuration for DSP data buffer for DL Type Antenna Stream        |      |

|   | 3.10 EDMA Configuration for DSP Data Buffer for UL_RSA Type Antenna Stream . |      |

|   | 3.11 EDMA Channels Used for AIF                                              |      |

| 4 | Frame Synchronization Configuration                                          |      |

| 5 | Antenna Interface Event Timings                                              |      |

| 6 | Antenna Interface Configuration                                              |      |

|   | 6.1 PE (Protocol Encoder) Configuration                                      |      |

|   | 6.2 PD (Protocol Decoder) Configuration                                      |      |

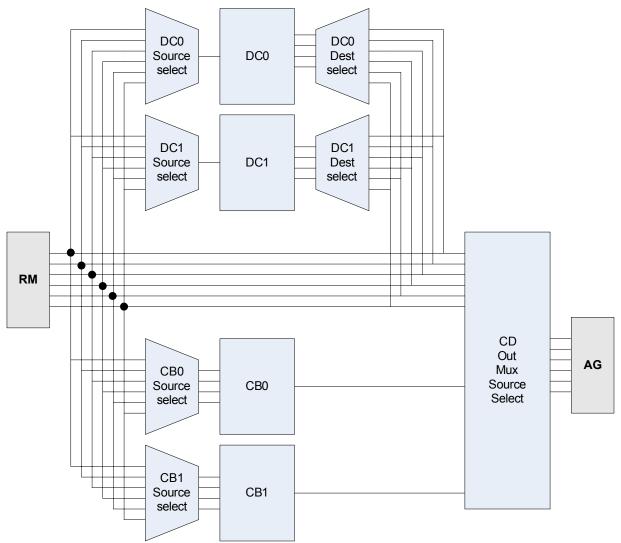

|   | 6.3 CD (Combiner/Decombiner) Configuration                                   |      |

|   | 6.4 AG (Aggregator) Configuration                                            |      |

|   | 6.5 Using the Example Codes with this Application Note                       |      |

| 7 | References                                                                   | . 50 |

|   |                                                                              |      |

RapidIO is a registered trademark of RapidIO Trade Association. All other trademarks are the property of their respective owners.

### Tables

| Table 1  | AIF Antenna Data Buffer Memory Map                          | 10 |

|----------|-------------------------------------------------------------|----|

| Table 2  | Stream Number for Different Configurations                  | 12 |

| Table 3  | EDMA configuration for DL data type in AIF RAM              | 15 |

| Table 4  | EDMA Configuration for UL_RSA Data Type in AIF RAM          | 16 |

| Table 5  | EDMA Configuration for Packet-Switched FIFO                 | 18 |

| Table 6  | EDMA Configuration for CPRI Control Words                   | 18 |

| Table 7  | EDMA Configuration for RAC                                  | 21 |

| Table 8  | EDMA Configuration for DSP Data Buffer for DL Data Type     | 24 |

| Table 9  | EDMA Configuration for DSP Data Buffer for UL_RSA Data Type | 25 |

| Table 10 | Summary EDMA Channel Usage in the Example                   | 27 |

| Table 11 | EDMA3 Synchronization Events Associated with Fsync Module   | 30 |

| Table 12 | FSync Events for AIF and Their Configuration                | 32 |

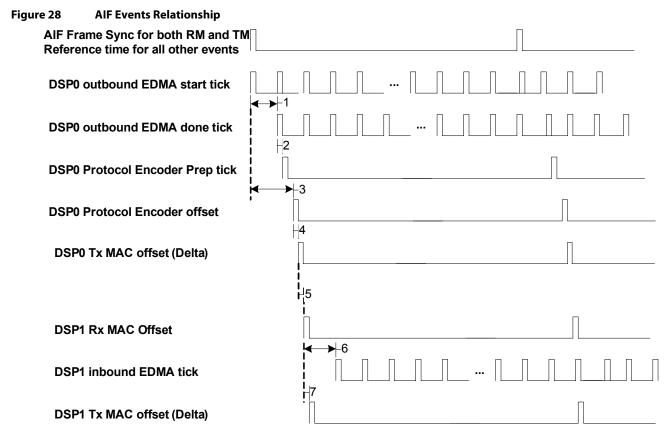

| Table 13 | AIF Events Timing Parameters                                | 35 |

| Table 14 | Source Files of the Example Codes                           | 47 |

|          |                                                             |    |

### Figures

| Figure 1  | TCI6487/8 Block Diagram and Typical Data Processing Flow           | . 3 |

|-----------|--------------------------------------------------------------------|-----|

| Figure 2  | Antenna Interface Subsystem on a TCI6487/8                         | 4   |

| Figure 3  | AIF Block Diagram                                                  | 5   |

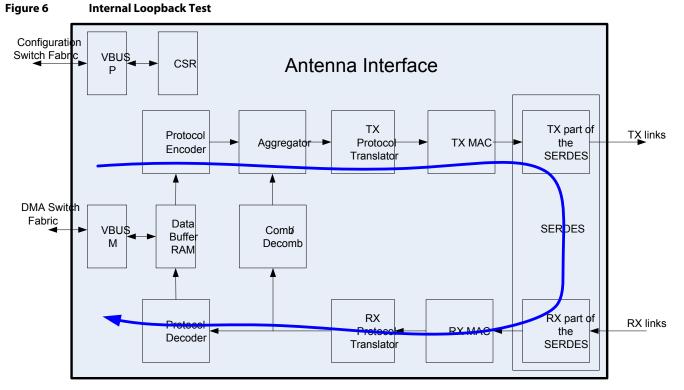

| Figure 4  | TCI6488 EVM Block Diagram                                          | 6   |

| Figure 5  | AIF Connections Between Two DSPs on TCI6488 EVM                    | 7   |

| Figure 6  | Internal Loopback Test                                             | 8   |

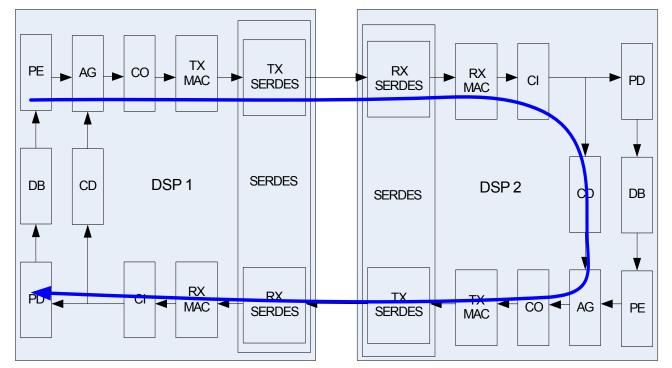

| Figure 7  | External Redirection Test.                                         |     |

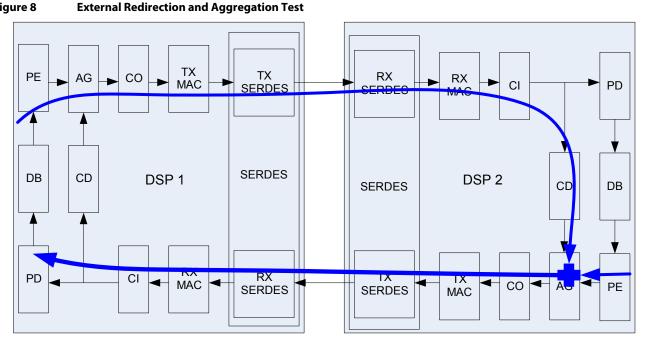

| Figure 8  | External Redirection and Aggregation Test                          | 9   |

| Figure 9  | DL Four-Chips Burst Antenna Data Format in AIF RAM                 | .11 |

| Figure 10 | UL_RSA Eight-Chips Burst Antenna Data Format in AIF RAM            | .12 |

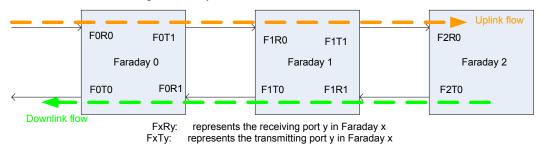

| Figure 11 | Antenna Data Flow Through AIF Daisy Chain                          |     |

| Figure 12 | Data Format in CPRI Control Word RAM for 1x Link                   | .13 |

| Figure 13 | Data Format in CPRI Control Word RAM for 2x Link                   |     |

| Figure 14 | Data Format in CPRI Control Word RAM for 4x Link                   |     |

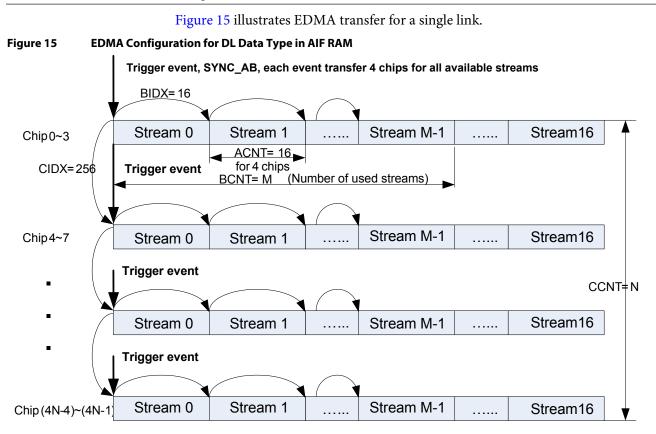

| Figure 15 | EDMA Configuration for DL Data Type in AIF RAM                     |     |

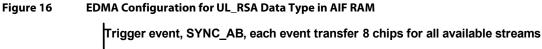

| Figure 16 | EDMA Configuration for UL_RSA Data Type in AIF RAM                 | .17 |

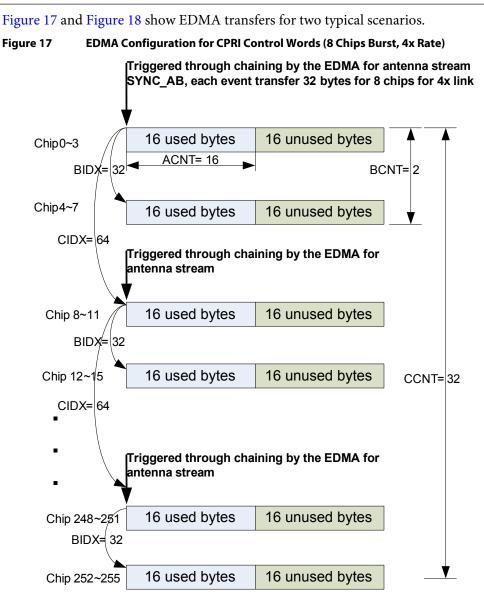

| Figure 17 | EDMA Configuration for CPRI Control Words (8 Chips Burst, 4x Rate) | .19 |

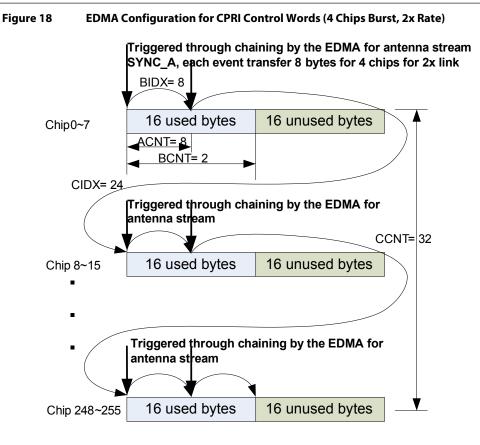

| Figure 18 | EDMA Configuration for CPRI Control Words (4 Chips Burst, 2x Rate) | .20 |

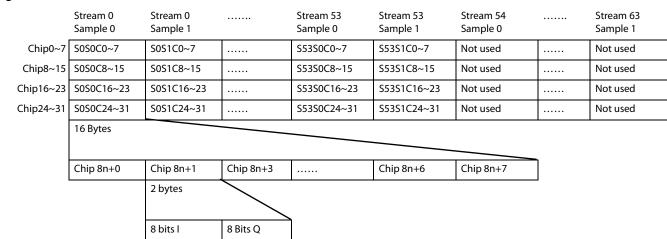

| Figure 19 | RAC Antenna Data Buffer Structure                                  |     |

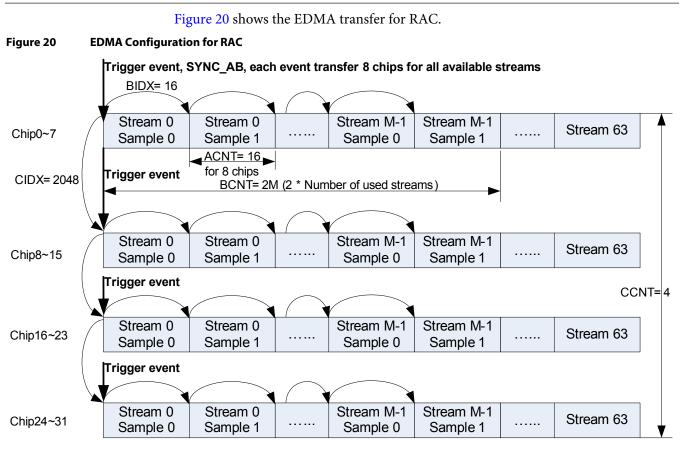

| Figure 20 | EDMA Configuration for RAC                                         |     |

| Figure 21 | DL Type Data Buffer Structure Example in DSP Memory                | .23 |

| Figure 22 | UL_RSA Type Data Buffer Structure Example in DSP Memory            | .23 |

| Figure 23 | EDMA Configuration for DSP Data Buffer for DL Data Type            | .24 |

| Figure 24 | EDMA Configuration for DSP Data Buffer for UL_RSA Data Type        | .26 |

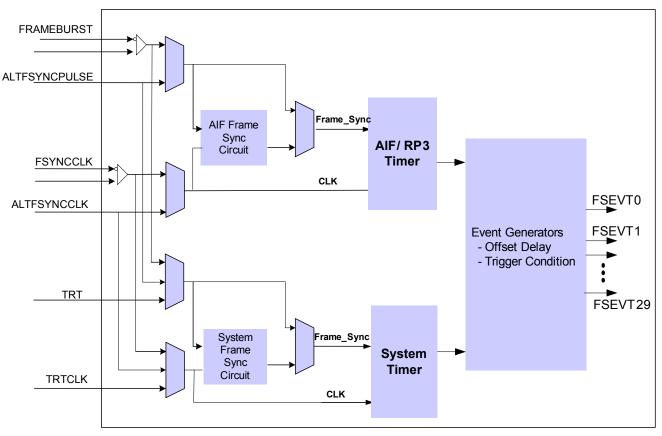

| Figure 25 | TCI648x FSync Block Diagram                                        | .29 |

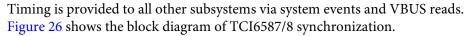

| Figure 26 | TCI6487/8 Synchronization                                          |     |

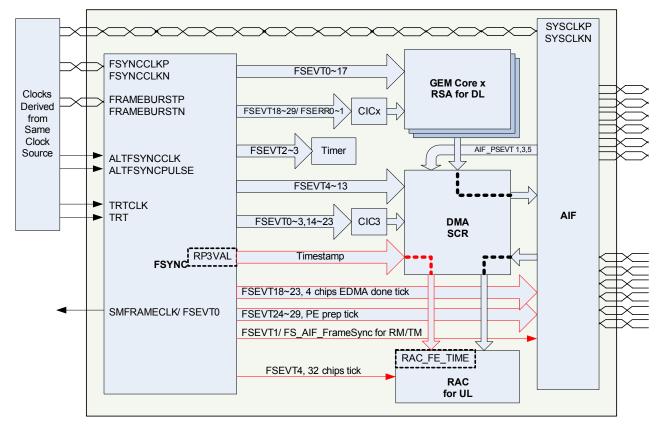

| Figure 27 | Synchronization of Two DSPs on the TCI6488 EVM                     |     |

| Figure 28 | AIF Events Relationship                                            |     |

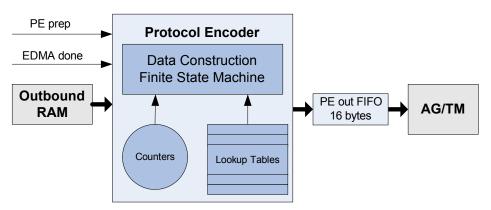

| Figure 29 | Protocol Encoder Block Diagram                                     | .37 |

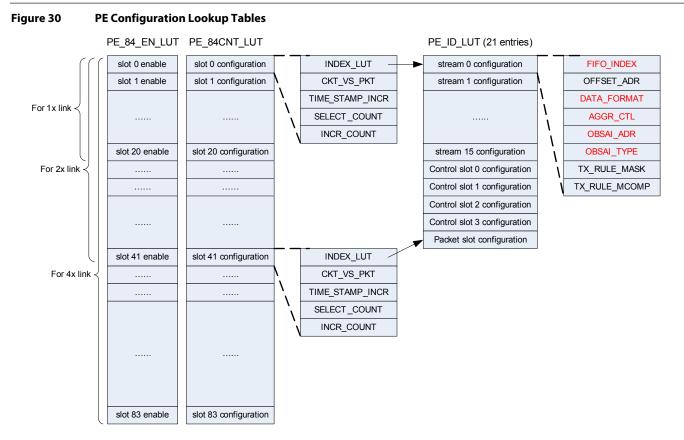

| Figure 30 | PE Configuration Lookup Tables                                     | .38 |

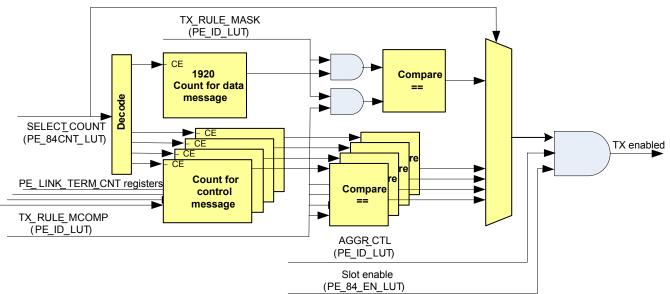

| Figure 31 | PE Transmission Enable Rules                                       |     |

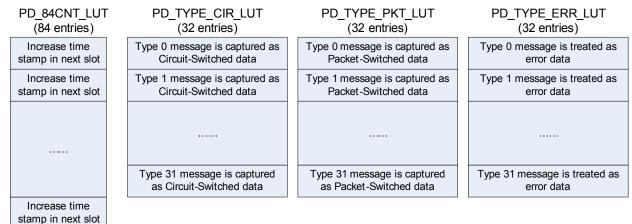

| Figure 32 | PD Configuration Lookup Tables                                     | .41 |

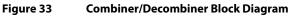

| Figure 33 | Combiner/Decombiner Block Diagram                                  | .43 |

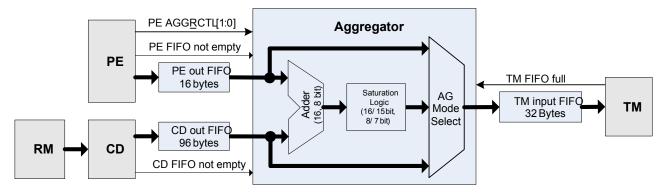

| Figure 34 | Aggregator Block Diagram                                           |     |

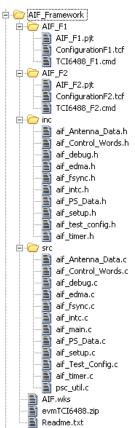

| Figure 35 | Directory Structure of Example Codes                               | .46 |

|           |                                                                    |     |

### 1 Introduction

The TCI6487/8 is a DSP designed to meet the requirements for wireless infrastructure baseband systems.

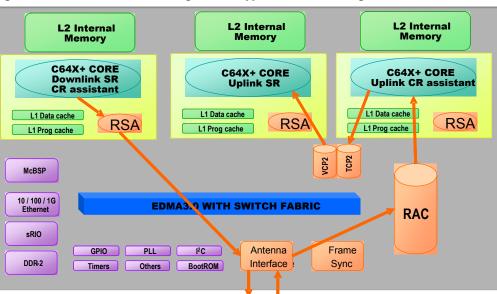

The DSP comprises three 1GHz C64x+ cores, several baseband accelerators, and several high-speed interfaces. All cores on the device have full access to the memory map and all the resources on the device. Figure 1 shows a block diagram of the TCI6487/8.

Figure 1 TCI6487/8 Block Diagram and Typical Data Processing Flow

The integrated antenna interface (AIF) supports both OBSAI (Open Base Station Architecture Initiative) and CPRI (Common Public Radio Interface) standards, which interface with the IF/RF (Intermediate Frequency/ Radio Frequency) module for antenna data transfer. The AIF transfers baseband IQ data with a high-speed SERDES interface.

The typical application of the TCI6488 is WCDMA baseband processing. For uplink processing, antenna data received from the antenna interface is sent to the RAC (Receiver Accelerator Coprocessor), which performs uplink chip-rate receive processing under the direction and control of a DSP core. The symbol data is sent to the VCP2 (Viterbi Coprocessor) or TCP2 (Turbo Coprocessor) for convolution or Turbo decoding under the control of the symbol rate processing core.

On the TCI6488, WCDMA transmit chip-rate processing is implemented by a DSP subsystem and its associated Rake Search/Spread Accelerator (RSA) extensions. These RSA extensions accelerate WCDMA transmit processing by performing spreading and scrambling functions; the generated antenna data is then sent out through the antenna interface.

Introduction

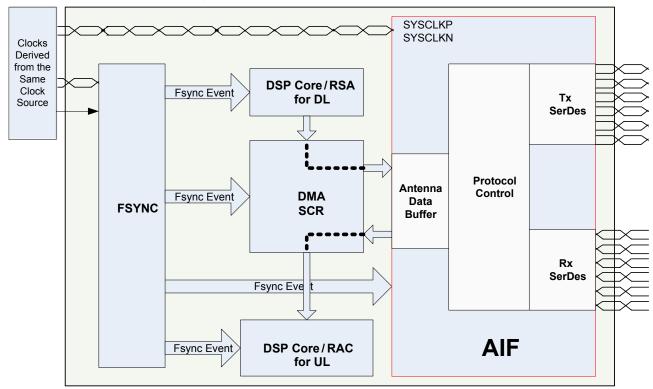

There are six AIF links on the TCI6487/8, which support up to 96 antenna streams and allow a flexible interconnection topology. Figure 2 shows the antenna interface subsystem on the TCI6487/8.

#### Figure 2 Antenna Interface Subsystem on a TCI6487/8

Introduction

Figure 3 shows the block diagram of the AIF. For more Information about the functions of each module, see the *Antenna Interface User's Guide*.

#### Figure 3 AIF Block Diagram

This document describes how to program the TCI648x Antenna Interface. Example codes based on operation with the TCI6488 EVM are also provided.

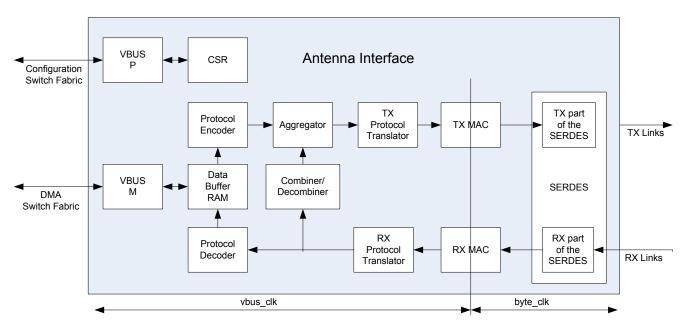

### 2 TCI6488 EVM and AIF Test Setup

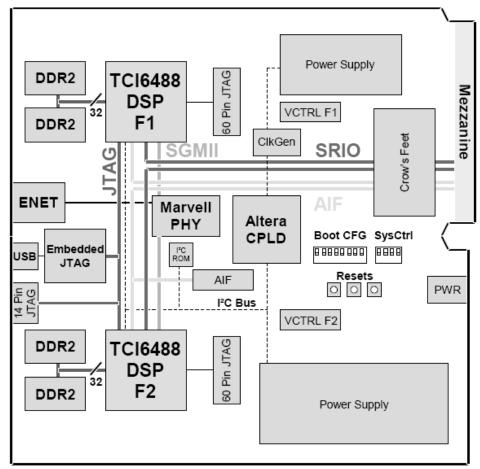

The example codes supplied with this application note are based on the TCI6488 EVM. The EVM board has two TCI6488 DSPs running at 1 GHz. Figure 4 is a block diagram of the TMS320TCI6488 EVM.

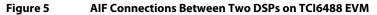

Figure 5 on page 7 shows the AIF connection between two DSPs on the TCI6488 EVM. The six AIF links are used to allow the following in the default configuration:

- Support of SMA connections for the incoming stream on DSP2 and the outgoing stream on DSP1

- Support of four full DSP-to-DSP connections. The four connections can be used to test antenna data transfer between DSPs.

- Support of one full-link connection to the AMC Connector

The example codes demonstrate diversiform working modes of the AIF; the following parameters are user-configurable to verify most functions of the AIF:

- Protocol: OBSAI, CPRI

- Link rate: 1x, 2x, 4x

- Data Type: DL, UL\_RSA

- Data Width

•

- 7 bits (CPRI only)

- 8 bits

- 15 bits (CPRI only)

- 16 bits

- Data Path

- Internal loopback

- External redirection

- External redirection and aggregation with external stream (Circuit-switched data only)

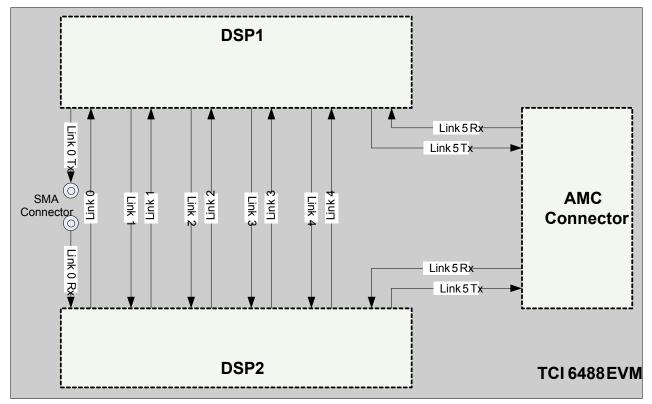

## Figure 6, Figure 7, and Figure 8 show different test data paths.

www.ti.com

•

NOTE—Link 0 and link 5 of two DSPs are not directly connected to each other on this EVM; without external connections, they can be used only for internal loopback testing.

A typical test configuration is as follows:

- Link 1: 1x, 8 bits UL\_RSA, internal loopback test on every DSP •

- Link 2: 4x, 16 bits DL, external redirection and aggregation test between two • **DSPs**

- Link 3: 2x, 8 bits UL\_RSA, external redirection test between two DSPs

- Link 4: 2x, 16 bits DL, external redirection and aggregation test between two **DSPs**

NOTE—See "Using the Example Codes with this Application Note" on page 45 for more details about the examples codes.

### 3 Antenna Data Structure and EDMA Configuration

Data structure is the basis of software programming; understanding the antenna data structure is very important for programming the antenna interface. The EDMA configuration is determined by the antenna data buffer structure.

#### 3.1 AIF Antenna Data Buffer Structure

There are several RAM buffers in the AIF module for antenna data transfer. Table 1 shows the AIF antenna data buffer memory map on the TCI6487/8.

Table 1 AIF Antenna Data Buffer Memory Map (Part 1 of 2) Address **Physical Size Mapped Size** Description 0xA000000 Inbound Circuit Switched RAM for link0 2KB 4MB 4MB 2KB 0xA0400000 Inbound Circuit Switched RAM for link1 0xA0800000 2KB 4MB Inbound Circuit Switched RAM for link2 0xA0C00000 2KB 4MB Inbound Circuit Switched RAM for link3 Inbound Circuit Switched RAM for link4 0xA1000000 2KB 4MB 0xA1400000 4MB Inbound Circuit Switched RAM for link5 2KR 0xA1800000 Reserved 0xA2000000 2KB 4MB Outbound Circuit Switched RAM for link0 Outbound Circuit Switched RAM for link1 2KB 4MR 0xA2400000 Outbound Circuit Switched RAM for link2 0xA2800000 2KB 4MB 0xA2C00000 2KB 4MB Outbound Circuit Switched RAM for link3 Outbound Circuit Switched RAM for link4 0xA3000000 2KB 4MB Outbound Circuit Switched RAM for link5 0xA3400000 2KB 4MB 0xA3800000 Reserved **OBSAI Inbound Packet Switched FIFO0** 0xA4000000 4MB 0xA4400000 4MB **OBSAI Inbound Packet Switched FIFO1** Shared 9.5KB 0xA4800000 4MB **OBSAI Inbound Packet Switched FIFO2** 0xA4C00000 4MB **OBSAI Inbound Packet Switched FIFO3** 0xA5000000 512KB **OBSAI Outbound Packet Switched FIFO0** 0xA5080000 512KB **OBSAI Outbound Packet Switched FIFO1** 512KB **OBSAI Outbound Packet Switched FIFO2** 0xA5100000 Shared 9.5KB ... 0xA5E00000 512KB **OBSAI Outbound Packet Switched FIFO28** 512KB **OBSAI Outbound Packet Switched FIFO29** 0xA5E80000 0xA5F00000 Reserved 2KB Inbound CPRI Control Word RAM for link0 0xA6000000 1KB 0xA6000800 1KB 2KB Inbound CPRI Control Word RAM for link1 2KB Inbound CPRI Control Word RAM for link2 0xA6001000 1KB 2KB Inbound CPRI Control Word RAM for link3 0xA6001800 1KB Inbound CPRI Control Word RAM for link4 0xA6002000 1KB 2KB Inbound CPRI Control Word RAM for link5 0xA6002800 1KB 2KR 0xA6003000 Reserved 0xA7000000 1KB 2KB Outbound CPRI Control Word RAM for link0

#### Antenna Data Structure and EDMA Configuration

| Table 1             | AIF Antenna Dat | a Buffer Memor | y Map (Part 2 of 2)                      |

|---------------------|-----------------|----------------|------------------------------------------|

| Address             | Physical Size   | Mapped Size    | Description                              |

| 0 <b>x</b> A7000800 | 1KB             | 2KB            | Outbound CPRI Control Word RAM for link1 |

| 0 <b>x</b> A7001000 | 1KB             | 2KB            | Outbound CPRI Control Word RAM for link2 |

| 0 <b>x</b> A7001800 | 1KB             | 2KB            | Outbound CPRI Control Word RAM for link3 |

| 0 <b>x</b> A7002000 | 1KB             | 2KB            | Outbound CPRI Control Word RAM for link4 |

| 0 <b>x</b> A7002800 | 1KB             | 2KB            | Outbound CPRI Control Word RAM for link5 |

The physical circuit-switched buffer size for one link is 2KB, but it is mapped to a 4MB memory range repeatedly. Linearly accessing the 4MB memory range accesses the 2KB memory buffer in a circular or wrap-around way. This mechanism simplifies the EDMA configuration when performing bigger frame size transfers to and from the DSP memory.

Each 2KB Inbound or Outbound RAM buffer holds 32 chips of antenna data for 16 streams; the 32-chip buffer per stream is also a circular buffer for AIF hardware to access while the DMA is accessing this buffer.

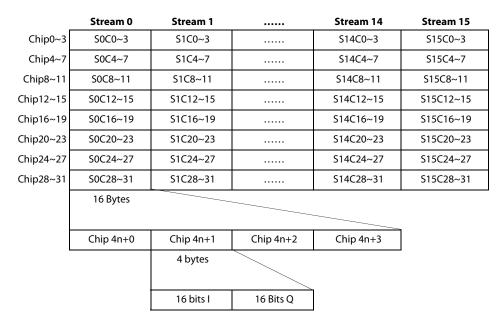

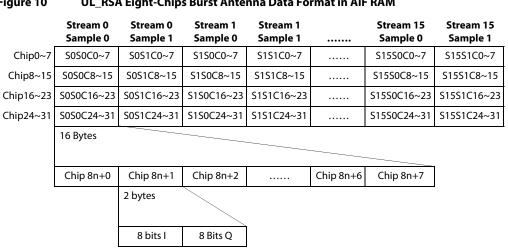

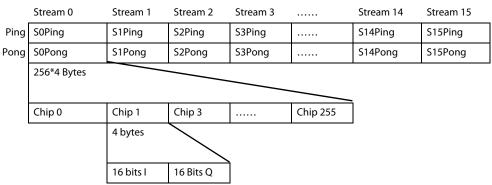

The data in the buffer is organized according to data type: DL (DownLink) or UL\_RSA (UpLink\_RSA). Figure 9 and Figure 10 show the formats of the DL and UL\_RSA data types.

#### Figure 9 DL Four-Chips Burst Antenna Data Format in AIF RAM

Figure 10 UL\_RSA Eight-Chips Burst Antenna Data Format in AIF RAM

One AIF link can support up to 16 streams. Table 2 shows the number of streams the AIF supports under different configurations. The buffer RAM organization is fixed; it does not change with the stream number. The location for the unused stream is just unused; this simplifies the implementation and programming of the AIF.

Table 2 **Stream Number for Different Configurations**

|               | 1x link rate | 2x link rate | 4x link rate |

|---------------|--------------|--------------|--------------|

| OBSAI         | 4            | 8            | 16           |

| CPRI 7/15 bit | 4            | 8            | 16           |

| CPRI 8/15 bit | 3            | 7            | 15           |

For CPRI 7-bit or 15-bit data types, every data element still occupies 8- or 16-bit memory space in the AIF buffer, but when the data is transmitted, the AIF hardware saturates the value to the 7- or 15-bits range for aggregation or throws the MSB (Most Signification Bit) for non-aggregation operation; when 7- or 15-bit data is received, it is sign-extended and saved to an 8- or 16-bit memory unit.

**NOTE**—The terms *inbound* and *outbound* do not mean *uplink* and *downlink*, respectively. Data type transport through the Inbound (input port) and Outbound (output port) can be either DL or UL\_RSA. As Figure 11 shows, the Uplink data flow (UL RSA type) goes through inbound and outbound ports of several DSPs; similarly, downlink data flow (DL type) also goes through inbound and outbound ports. It is the data type (DL or UL\_RSA), not whether it is inbound or outbound, that determines how the AIF buffer is organized.

#### Figure 11 Antenna Data Flow Through AIF Daisy Chain

DL data type must be four-chips burst and UL\_RSA data type must be eight-chips burst. One burst of data is the minimum data transferred with one EDMA transfer triggered by one event; that is, one burst of data is just one row in the data format figures above.

Inbound packet-switched RAM for OBSAI is accessed through four FIFO interfaces. The 9.5KB memory can store 512 OBSAI messages; each message occupies 19 bytes, that is, 512\*19= 9728 bytes= 9.5KB. The memory partition between four FIFOs is configurable through software. Inbound packet-switched messages from all six links are routed to one of the four FIFOs according to their OBSAI address and type, which are also configurable through software.

Outbound packet-switched RAM for OBSAI is accessed through 30 FIFO interfaces. The 9.5KB memory can also store 512 OBSAI messages. The memory allocation between 30 FIFOs is dynamically allocated by hardware without software intervention, which maximizes the use of the RAM. Outbound packet-switched messages to six links are fetched from one of the 30 FIFOs according their time slot configuration. Normally, each link can use five FIFOs, link 0 uses FIFO 0~4, link 1 uses FIFO 5~9... link 5 uses FIFO 25 to 29.

The physical CPRI Control Word RAM size for one link is 1KB, but it occupies 2KB memory space. For every 16 bytes used, there is 16 bytes of unused space as shown in Figure 12 through Figure 14. This requires a special EDMA configuration. To save the DSP memory space, the CPRI control frame buffer in DSP memory should be a compact 1KB buffer without unused space, and EDMA can access it linearly.

|              | 16 bytes for co | ontrol words |           |                       |

|--------------|-----------------|--------------|-----------|-----------------------|

|              | CW0             | CW1          | <br>CW15  | 16 bytes unused space |

|              | CW16            | CW17         | <br>CW31  | 16 bytes unused space |

| Hype Frame 0 |                 |              | <br>      |                       |

|              | CW224           | CW225        | <br>CW239 | 16 bytes unused space |

|              | CW240           | CW241        | <br>CW255 | 16 bytes unused space |

|              | CW0             | CW1          | <br>CW15  | 16 bytes unused space |

|              | CW16            | CW17         | <br>CW31  | 16 bytes unused space |

| Hype Frame 1 | •••             |              | <br>      |                       |

|              | CW224           | CW225        | <br>CW239 | 16 bytes unused space |

|              | CW240           | CW241        | <br>CW255 | 16 bytes unused space |

|              | CW0             | CW1          | <br>CW15  | 16 bytes unused space |

|              | CW16            | CW17         | <br>CW31  | 16 bytes unused space |

| Hype Frame 2 |                 |              | <br>      |                       |

|              | CW224           | CW225        | <br>CW239 | 16 bytes unused space |

|              | CW240           | CW241        | <br>CW255 | 16 bytes unused space |

#### Figure 12 Data Format in CPRI Control Word RAM for 1x Link

#### Antenna Data Structure and EDMA Configuration

|              | CW0   | CW1   | <br>CW15  | 16 bytes unused space |

|--------------|-------|-------|-----------|-----------------------|

|              | CW16  | CW17  | <br>CW31  | 16 bytes unused space |

| Hype Frame 3 |       |       | <br>      |                       |

|              | CW224 | CW225 | <br>CW239 | 16 bytes unused space |

|              | CW240 | CW241 | <br>CW255 | 16 bytes unused space |

#### Figure 13 Data Format in CPRI Control Word RAM for 2x Link

|              | 16 bytes for co | ontrol words |           | Å@                    |

|--------------|-----------------|--------------|-----------|-----------------------|

| -            | CW0             | CW1          | <br>CW7   | 16 bytes unused space |

|              | CW8             | CW9          | <br>CW15  | 16 bytes unused space |

| Hype Frame 0 |                 |              | <br>      |                       |

|              | CW240           | CW241        | <br>CW247 | 16 bytes unused space |

|              | CW248           | CW249        | <br>CW255 | 16 bytes unused space |

|              | CW0             | CW1          | <br>CW7   | 16 bytes unused space |

|              | CW8             | CW9          | <br>CW15  | 16 bytes unused space |

| Hype Frame 1 |                 |              | <br>      |                       |

|              | CW240           | CW241        | <br>CW247 | 16 bytes unused space |

|              | CW248           | CW249        | <br>CW255 | 16 bytes unused space |

#### Figure 14 Data Format in CPRI Control Word RAM for 4x Link

16 bytes for control words

|              | CW0   | CW1   | <br>CW3   | 16 bytes unused space |

|--------------|-------|-------|-----------|-----------------------|

|              | CW4   | CW5   | <br>CW7   | 16 bytes unused space |

| Hype Frame 0 |       |       | <br>•••   |                       |

|              | CW248 | CW249 | <br>CW251 | 16 bytes unused space |

|              | CW252 | CW253 | <br>CW255 | 16 bytes unused space |

There are 256 CPRI control words in a CPRI hyperframe. Each of these control words is  $\{1, 2, 4\}$  bytes corresponding to  $\{1x, 2x, 4x\}$  link rates. As a result of this difference, the allocated RAM per segment holds  $\{4, 2, 1\}$  hyperframes of CPRI control words corresponding to  $\{1x, 2x, 4x\}$  link rates.

Normally, the AIF accesses the control RAM sequentially in a circular or wrap-around way, while at every NodeB frame boundary, the AIF resets the access address to the beginning of the control RAM. For 2x or 4x link, these two addressing rules are consistent. At the NodeB frame boundary, the circular or wrap-around mechanism just makes the next access address at the beginning of the control RAM. But there is a corner case based on these two addressing rules for 1x link. At the next NodeB frame boundary, the circular or wrap-around mechanism makes the next access address at the middle of the control RAM because the access address for hyper frame 150 (next NodeB Frame boundary) is at frame block 2 (150%4= 2, totally four frame blocks in the RAM for 1x link) of the control RAM. To adapt this corner case, the EDMA should be configured manually to reset the access address to the beginning of the control RAM at the NodeB frame boundary for 1x link.

### 3.2 EDMA Configuration for a DL-Type Antenna Stream in AIF RAM

For a DL-type antenna stream, EDMA is triggered every four chips, EDMA transfers four chips for all available streams with each trigger event. Table 3 shows the configuration of important EDMA parameters for a single link.

| 5               |                        |                                                                                                                 |  |  |  |

|-----------------|------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameters      | Configuration          | Comments                                                                                                        |  |  |  |

| ACNT            | 16                     | 4 (chips) x 4 (bytes), for 4 chips of one stream                                                                |  |  |  |

| BIDX            | 16                     | index to the next stream                                                                                        |  |  |  |

| BCNT            | Number of used streams | Support maximum 16 antenna streams                                                                              |  |  |  |

| CIDX            | 256                    | 16 (bytes) x 16 (Streams), index to the next 4 chips for 16 streams.<br>This is fixed value for all link speed. |  |  |  |

| CCNT            | Ν                      | 4N chips are transferred                                                                                        |  |  |  |

| Synchronization | SYNC_AB                | EDMA transfers 4 chips for all available streams with each trigger event                                        |  |  |  |

Table 3EDMA configuration for DL data type in AIF RAM

CCNT should be as large as possible for more efficient of EDMA transfer. Although the AIF buffer size for each link is only 2KB (for 32 chips of data), it is mapped to a 4MB memory range repeatedly. Linearly accessing the 4MB memory range accesses the 2KB memory buffer in a circular or wrap-around way. So, the EDMA can linearly access 32 chips \* (4MB/ 2KB) = 64K chips of data, so the maximum CCNT can be (64K chips)/(4 chips)= 16K.

Because EDMA transfers data between the AIF buffer and the other data buffer, to determine the value of CCNT should also take into account the buffer size at the other end. So, CCNT= Min(Max CCNT for AIF buffer, Max CCNT for the other buffer). The Max CCNT for the data buffers of the other end is discussed later.

www.ti.com

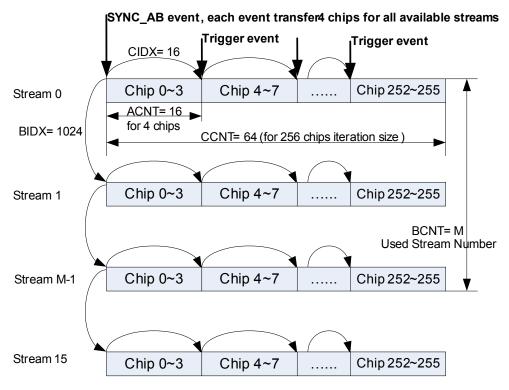

### 3.3 EDMA configuration for UL\_RSA type antenna stream in AIF RAM

fearly DCA Dete Terres in AIT DAM

For a UL\_RSA-type antenna stream, EDMA is triggered every eight chips. EDMA transfers eight chips for all available streams with each trigger event. Table 4 shows the configuration of important EDMA parameters for a single link.

| Table 4         | EDMA Configuration for UL_R | r UL_RSA Data Type in AIF RAM                                                     |  |  |

|-----------------|-----------------------------|-----------------------------------------------------------------------------------|--|--|

| Parameters      | Configuration               | Comments                                                                          |  |  |

| ACNT            | 16                          | 8 (chips) x 2 (bytes), for 8 chips of one stream                                  |  |  |

| BIDX            | 16                          | Index to the next sample, then to next stream                                     |  |  |

| BCNT            | 2* Number of used streams   | Every stream has two samples.                                                     |  |  |

|                 |                             | Support maximum 16 antenna streams.                                               |  |  |

| CIDX            | 512                         | 16 (bytes) x 2 (samples) x 16 (Streams), index to the next 8 chips for 16 streams |  |  |

| CCNT            | Ν                           | 8N chips are transferred                                                          |  |  |

| Synchronization | n SYNC_AB                   | EDMA transfers 8 chips for all available streams with each trigger event          |  |  |

CCNT should be as large as possible for more efficient EDMA transfer. Although the AIF buffer size for each link is only 2KB (for 32 chips of data), it is mapped to a 4MB memory range repeatedly. Linearly accessing the 4MB memory range accesses the 2KB memory buffer in a circular or wrap-around way. So, the EDMA can linearly access 32 chips \* (4MB/2KB) = 64K chips of data, so the maximum CCNT can be (64K chips)/ (8 chips)= 8K.

Antenna Data Structure and EDMA Configuration

Because EDMA transfers data between the AIF buffer and the other data buffer, to determine the value of CCNT should also take into account the other buffer size. So, CCNT= Min(Max CCNT for AIF buffer, Max CCNT for other buffer). The Max CCNT for the data buffers of the other end is discussed later.

Figure 16 illustrates EDMA transfer for a single link.

### 3.4 EDMA Configuration for Packet-Switched FIFO

For inbound packet-switched messages, EDMA is triggered when the FIFO is not empty. For outbound packet-switched messages, EDMA should be triggered manually under control of the application software as long as the FIFO is not full.

The DSP or DMA sends outbound packet-switched messages to the AIF over the 16-byte (128 bits) Bus. The data/DMA Bus is 16 bytes wide and the packet-switched message is 19 bytes wide. A minimum of two Bus writes/reads (32 bytes) is required for every FIFO access. This also requires the message buffer in DSP memory to be a multiple of 32 bytes though only 19 of 32 bytes are used.

| Table 5         | EDMA Configuration for Packet-Switched FIFO |                                               |

|-----------------|---------------------------------------------|-----------------------------------------------|

| Parameters      | Configuration                               | Comments                                      |

| ACNT            | 32                                          | 32 bytes per message, only 19 bytes are valid |

| BIDX            | 0                                           | Access FIFO in fixed address                  |

| BCNT            | Number of message                           |                                               |

| CIDX            | 0                                           | Access FIFO in fixed address                  |

| CCNT            | 1                                           |                                               |

| Synchronization | n SYNC_AB                                   |                                               |

#### 3.5 EDMA Configuration for CPRI Control Words

Because CPRI control words have regular/deterministic flow characteristics that are very similar to the antenna stream, the CPRI control words should be transferred with the antenna stream. The EDMA chain feature can be used to trigger the transfer of CPRI control words after the antenna stream transfer-that is, chain the EDMA for CPRI control words to the EDMA for antenna stream. That way, when the antenna stream is transferred every four or eight chips, the CPRI control words are also transferred every four or eight chips.

Table 5 shows the configuration of important EDMA parameters for single FIFO.

Table 6 shows the configuration of important EDMA parameters for a single link.

Table 6 **EDMA Configuration for CPRI Control Words**

|            | ga.a                               |                                                                                                                                                                         |

|------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters | Configuration                      | Comments                                                                                                                                                                |

| ACNT       | (burst chips)*(link rate)<br>or 16 | Every trigger should transfer control words for a burst chips (4 or 8 chips), every control word is 1 byte for<br>1x link, 2 bytes for 2x link and 4 bytes for 4x link. |

|            |                                    | ACNT should no more than 16 because of the special CPRI control RAM structure.                                                                                          |

|            |                                    | So, for burst=8 and rate=4, the ACNT=16                                                                                                                                 |

| BCNT       | 16/ACNT                            | ACNT*BCNT should be multiple of 16 bytes because of the special CPRI control RAM structure.                                                                             |

|            | or 2                               | For burst=8 and rate=4, the BCNT=2                                                                                                                                      |

| BIDX       | ACNT                               | BIDX=ACNT to access the data for next burst.                                                                                                                            |

|            | or 32                              | For burst=8 and rate=4, the ACNT=16, to access the next data block, it should skip the 16 unused space, thus the BIDX=32.                                               |

| CIDX       | ACNT+16                            | CIDX=ACNT should access the next burst, but need skip 16 unused space, so CIDX=ACNT+16                                                                                  |

|            | or 64                              | For burst=8 and rate=4, CIDX should be configured to access the next 32 bytes, but need skip 32 unused bytes, so CIDX= 64                                               |

| CCNT       | 256 *(link rate)/<br>(ACNT*BCNT)   | ACNT*BCNT*CCNT= size of one hyper frame= 256 *(link rate)                                                                                                               |

| Sync       | SYNC_A                             | Every trigger should transfer one burst of data.                                                                                                                        |

|            | or SYNC_AB                         | For burst=8 and rate=4, burst size = 32bytes = ACNT* BCNT, so, SYNC_AB should be used. For other cases, burst= ANCT, so SYNC_A should be used.                          |

www.ti.com

Antenna Data Structure and EDMA Configuration

www.ti.com

There is a special problem for the cases with ACNT<16, as shown in Figure 18 above. Because the AIF RAM interface always swaps the byte order of 16-byte blocks, when EDMA transfers bytes 0~7 in the DSP buffer, it actually accesses bytes 8~15 in the AIF control RAM; when EDMA transfers byte 8~15 in the DSP buffer, it actually accesses bytes 0~7 in the AIF control RAM. However, the AIF accesses the control RAM sequentially after the first outbound EDMA is done, so the AIF control RAM is actually accessed by EDMA and AIF as follows:

| EDMA access | EDMA access | EDMA access | EDMA access |            |  |

|-------------|-------------|-------------|-------------|------------|--|

| byte 8~15   | byte 0~7    | byte 24~31  | byte 16~23  |            |  |

|             | AIF access  | AIF access  | AIF access  | AIF access |  |

|             | byte 0~7    | byte 8~15   | byte 16~23  | byte 24~31 |  |

So, AIF may access data which has not yet arrived at the RAM. To avoid this problem, the outbound EDMA should be started earlier as shown below; this requires a special EDMA configuration.

| EDMA access ED | MA access EDI | MA access   E | EDMA access |            |            |  |

|----------------|---------------|---------------|-------------|------------|------------|--|

| byte 8~15      | oyte 0~7 by   | te 24~31      | byte 16~23  |            |            |  |

|                | AI            | F access      | AIF access  | AIF access | AIF access |  |

|                | b             | oyte 0~7      | byte 8~15   | byte 16~23 | byte 24~31 |  |

On the other hand, the EDMA for inbound control words should be delayed for the cases with ACNT<16.

### 3.6 RAC Antenna Data Buffer Structure

The RAC front-end antenna data input buffer is similar to the AIF UL\_RSA data format. The RAC supports 54 streams, but the buffer is organized for 64 streams. The location for stream 54~63 is not used. Figure 19 shows how the RAC front-end buffer is organized.

#### Figure 19 RAC Antenna Data Buffer Structure

### 3.7 EDMA Configuration for RAC

The RAC antenna data buffer format is similar to the UL\_RSA data type—EDMA is triggered every eight chips. EDMA transfers eight chips for multiple streams with each trigger event. Table 7 shows the configuration of important EDMA parameters.

#### Table 7EDMA Configuration for RAC

| Parameters      | Configuration             | Comments                                                                          |

|-----------------|---------------------------|-----------------------------------------------------------------------------------|

| ACNT            | 16                        | 8 (chips) x 2 (bytes), for 8 chips of one stream                                  |

| BIDX            | 16                        | index to the next sample, then to next stream                                     |

| BCNT            | 2* Number of used streams | Every stream has two samples.                                                     |

|                 |                           | Support maximum 16 antenna streams                                                |

| CIDX            | 2048                      | 16 (bytes) x 2 (samples) x 64 (Streams), index to the next 8 chips for 16 streams |

| CCNT            | 4                         | 32 chips are transferred                                                          |

| Synchronization | SYNC_AB                   | EDMA transfers 8 chips for all available streams with each trigger event          |

Unlike the AIF buffer, the RAC front-end buffer does not map to a larger memory range, so CCNT is fixed at four for 32 chips of data.

#### 3.8 Antenna Data Buffer Structure in DSP Memory

The normal data flow for outbound data is:

- 1. DSP processes data and stores the data in the DSP memory

- 2. EDMA transfers the data from DSP memory to the AIF data buffer

- 3. AIF fetches the data in its buffer and transmits

The normal data flow for inbound data is:

- 1. AIF receives antenna data and stores the data in its buffer

- 2. EDMA transfers the data in the AIF data buffer to DSP memory

- 3. DSP processes the data in its memory

The antenna data buffer in DSP memory should be organized to facilitate DSP processing. DSP processes antenna data stream by stream, and it achieves better performance if it processes more data in batches. The size of the data processed at a time is called *iteration size*. The bigger the iteration size, the better the DSP processing performance; however, a bigger iteration size results in more latency. So, it is up to the system designer to determine an acceptable tradeoff between iteration size and latency. Common iteration sizes are 64, 128, or 256 chips.

Because the antenna data buffer in DSP memory is accessed by both DSP and EDMA, ping-pong or circular buffer schemes should be used to avoid conflict between the DSP and EDMA. When DSP accesses one memory buffer, the EDMA should access the other buffer.

In the example provided with this application note, a ping-pong scheme is used and the iteration size corresponds to 256 chips of data. Figure 21 shows the buffer organization for DL type data in the example.

Figure 21 DL Type Data Buffer Structure Example in DSP Memory

For UL\_RSA data types, two samples of every stream should be stored separately. Figure 22 shows the buffer organization for UL\_RSA data in the example.

Figure 22 UL\_RSA Type Data Buffer Structure Example in DSP Memory

|              | Stream 0    | Stream 1 |               | Stream 14 | Stream 15 |

|--------------|-------------|----------|---------------|-----------|-----------|

| Ping Sample0 | S0S0Ping    | S1S0Ping |               | S14S0Ping | S15S0Ping |

| Ping Sample1 | S0S1Ping    | S1S1Ping |               | S14S1Ping | S15S1Ping |

| Pong Sample0 | S0S0Pong    | S1S0Pong |               | S14S0Pong | S15S0Pong |

| Pong Sample1 | S0S1Pong    | S1S1Pong |               | S14S1Pong | S15S1Pong |

|              | 256*2 Bytes |          |               |           |           |

|              |             |          |               |           |           |

|              | Chip 0      | Chip 1   |               | Chip 255  |           |

|              |             | 2 bytes  | $\overline{}$ |           |           |

|              |             |          | $\sim$        |           |           |

|              |             | 8 bits I | 8 Bits Q      |           |           |

The OBSAI packet-switched data buffer in DSP memory is fairly simple. Every message requires 32 bytes of memory (though only 19 bytes are used), the buffer size should be a multiple of 32 bytes according the message number you want to buffer. The ping-pong mechanism is required for inbound messages, but outbound messages do not require the ping-pong mechanism because the transfer is controlled by application software on the DSP core.

The CPRI control-words buffer in DSP memory is also family simple. Normally, it is a compact buffer without unused space, which should store control words for one hyper frame, for worst 4x link rate case, it is 1KB. The ping-pong mechanism is required for both inbound and outbound transfers just like circuit-switched antenna data.

**EXAS**

INSTRUMENTS

### 3.9 EDMA Configuration for DSP data buffer for DL Type Antenna Stream

For DL-type antenna streams, EDMA is triggered every four chips. EDMA transfers four chips for all available streams with each trigger event. Table 8 shows the configuration of important EDMA parameters for a single link.

### Table 8 EDMA Configuration for DSP Data Buffer for DL Data Type

| Parameters      | Configuration                        | Comments                                                                 |

|-----------------|--------------------------------------|--------------------------------------------------------------------------|

| ACNT            | 16                                   | 4 (chips) x 4 (bytes), for 4 chips of one stream                         |

| BIDX            | 16*N                                 | index to the next stream                                                 |

|                 |                                      | N is the number of 4-chip bursts                                         |

| BCNT            | Number of used streams               | Not all 16 streams are used                                              |

| CIDX            | 16                                   | index to the next 4 chips for 16 streams                                 |

| CCNT            | N (=64 for 256 chips iteration size) | 4N chips are transferred                                                 |

| Synchronization | SYNC_AB                              | EDMA transfers 4 chips for all available streams with each trigger event |

Because EDMA transfers data between AIF buffer and the data buffer in DSP memory, CCNT= Min (Max CCNT for the AIF buffer, Max CCNT for the DSP buffer). As described in the section above, the Max CCNT for AIF buffer for four chips burst is 16K; assume the iteration size for DSP processing is 256 chips, the Max CCNT for DSP buffer= 256/4 = 64. So, for 256 chips iteration size, the CCNT for DL data transfer between the AIF buffer and the DSP DL data buffer is 64.

Figure 23 shows an example of EDMA transfer for a single link.

### Figure 23 EDMA Configuration for DSP Data Buffer for DL Data Type

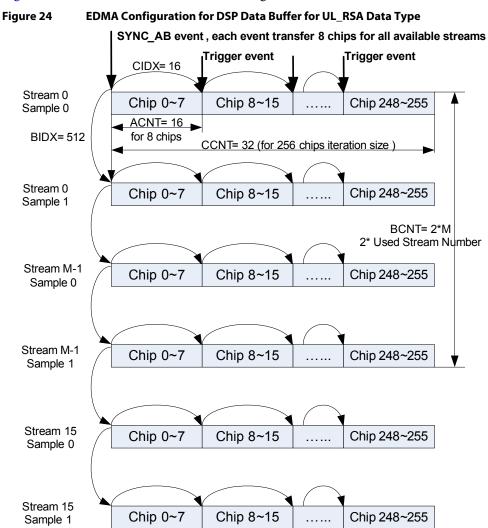

### 3.10 EDMA Configuration for DSP Data Buffer for UL\_RSA Type Antenna Stream

For a UL\_RSA-type antenna stream, EDMA is triggered every eight chips. EDMA transfers eight chips for all available streams with each trigger event. Table 9 shows the configuration of important EDMA parameters for a single link.

#### Table 9 EDMA Configuration for DSP Data Buffer for UL\_RSA Data Type

| Parameters      | Configuration                        | Comments                                                                 |

|-----------------|--------------------------------------|--------------------------------------------------------------------------|

| ACNT            | 16                                   | 8 (chips) x 2 (bytes), for 8 chips of one stream                         |

| BIDX            | 16*N (Iteration size)                | index to the next sample, then to next stream                            |

|                 |                                      | N is the number of 8-chip bursts                                         |

| BCNT            | 2* Number of used streams            | Every stream has two samples.                                            |

|                 |                                      | Not all 16 streams are used                                              |

| CIDX            | 16                                   | index to the next 8 chips for 16 streams                                 |

| CCNT            | N (=32 for 256 chips iteration size) | 8N chips are transferred                                                 |

| Synchronization | SYNC_AB                              | EDMA transfers 8 chips for all available streams with each trigger event |

Because EDMA transfers data between the AIF buffer and the data buffer in DSP memory, CCNT= Min (Max CCNT for the AIF buffer, Max CCNT for the DSP buffer). As described in the section above, the Max CCNT for the AIF buffer for eight chips burst is 8K; assume the iteration size for DSP processing is 256 chips, the Max CCNT for the DSP buffer= 256/8 = 32. So, for 256 chips iteration size, the CCNT for UL\_RSA data transfer between the AIF buffer and the DSP data buffer is 32.

Figure 24 shows an EDMA transfer for a single link.

#### 3.11 EDMA Channels Used for AIF

At least two EDMA channels are required for CS (circuit-switched) antenna data transfer for one dedicated link—one for inbound and one for outbound. In total, 12 EDMA channels may be used for six links. Generally, EDMA Channels 16 to 27 are used to service the outbound/inbound AIF CS stream data transfer between the DSP memory and the AIF data buffer.

If CPRI control-words transfer is enabled, at least two EDMA channels are required for CPRI control-words transfer for one dedicated link—one for inbound and one for outbound. In total, 12 EDMA channels may be used for six links. Any free EDMA channel can be used for CPRI control words transfer. In the example in this application note, channels 52~63 are used for CPRI control-words transfer.

If OBSAI PS (packet-switched) data transfer is enabled, every outbound link requires one EDMA channel. Any free EDMA channel can be used for OBSAI PS outbound transfer. In the example, channels 58~63 are used for AIF PS outbound data transfer, one for each outbound link. These EDMA transfers are triggered manually by the

www.ti.com

software on the DSP core. Because the OBSAI mode and CPRI mode are exclusive, channels 58~63 are used by both modes, but for different purpose. EDMA channel 40 to 42 is triggered by PS (Packet-Switched) inbound FIFO programmable\_not\_empty events and used for inbound PS data transfer.

If a ping-pong mechanism is used for EDMA transfer, every EDMA channel needs at least two reload EDMA PaRAM to implement the ping-pong mechanism. Table 10 summarizes the EDMA usage in the example in this application note.

Table 10

Summary EDMA Channel Usage in the Example

| Channel/PaRAMUsage16Outbound CS data for link017Inbound CS data for link118Outbound CS data for link119Inbound CS data for link220Outbound CS data for link221Inbound CS data for link323Inbound CS data for link424Outbound CS data for link425Inbound CS data for link426Outbound CS data for link427Inbound CS data for link428Outbound CS data for link429Outbound CS data for link420Outbound CS data for link521Inbound CS data for link522Inbound CS data for link523Inbound PS FIFO041Inbound PS FIFO142Inbound PS FIFO252Outbound CPRI control words for link053Inbound CPRI control words for link154Outbound CPRI control words for link155Inbound CPRI control words for link156Outbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link360Outbound CPRI control words for link361Inbound CPRI control words for link462Outbound CPRI control words for link463Outbound CPRI control words for link364Outbound CPRI control words for link365Inbound CPRI control words for link466Outbound CPRI control words for link467Outbound CPRI control words for link4<                                                                                                                          |               | Summary EDMA Channel Usage in the Example |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------|

| 17Inbound CS data for link018Outbound CS data for link119Inbound CS data for link120Outbound CS data for link221Inbound CS data for link323Inbound CS data for link324Outbound CS data for link425Inbound CS data for link426Outbound CS data for link527Inbound CS data for link528Outbound CS data for link429Inbound CS data for link420Outbound CS data for link421Inbound CS data for link522Inbound CS data for link523Inbound CS data for link524Outbound CS data for link625Inbound PS FIFO041Inbound PS FIFO226Outbound CPRI control words for link027Inbound CPRI control words for link028Outbound CPRI control words for link129Inbound CPRI control words for link129Inbound CPRI control words for link229Inbound CPRI control words for link229Inbound CPRI control words for link329Outbound CPRI control words for link320Outbound PS data for link120Outbound PS data for link421Outbound PS data for link422Outbound PS data for link323Inbound CPRI control words for link324Outbound PS data for link425Outbound PS data for link326Outbound PS data for link327Inbound CPRI control words for                                                                                                                                            | Channel/PaRAM |                                           |

| 18     Outbound CS data for link1       19     Inbound CS data for link2       20     Outbound CS data for link2       21     Inbound CS data for link3       22     Outbound CS data for link3       23     Inbound CS data for link4       24     Outbound CS data for link4       25     Inbound CS data for link4       26     Outbound CS data for link5       27     Inbound CS data for link5       28     Inbound CS data for link5       29     Inbound CS data for link5       20     Inbound CS data for link5       21     Inbound CS data for link5       22     Outbound PS FIFO0       41     Inbound PS FIFO1       42     Inbound CPRI control words for link0       53     Inbound CPRI control words for link1       54     Outbound CPRI control words for link1       55     Inbound CPRI control words for link2       57     Inbound CPRI control words for link3       58     Outbound CPRI control words for link3       59     Inbound CPRI control words for link4       60     Outbound PS data for link2       61     Inbound CPRI control words for link4       62     Outbound PRI control words for link4       63     Inbound CPRI control words for link4       64     Outbound PRI control w                                | 16            | Outbound CS data for link0                |

| 19       Inbound CS data for link1         20       Outbound CS data for link2         21       Inbound CS data for link3         22       Outbound CS data for link3         23       Inbound CS data for link4         24       Outbound CS data for link4         25       Inbound CS data for link4         26       Outbound CS data for link5         27       Inbound CS data for link5         28       Outbound CS data for link5         29       Inbound CS data for link5         20       Inbound CS data for link5         21       Inbound CS data for link5         22       Inbound CS data for link5         23       Inbound CS data for link5         24       Inbound CPRI control words for link0         25       Outbound CPRI control words for link1         26       Outbound CPRI control words for link1         27       Inbound CPRI control words for link2         28       Outbound CPRI control words for link3         29       Inbound CPRI control words for link3         20       Outbound PS data for link0         29       Inbound CPRI control words for link4         20       Outbound PS data for link4         20       Outbound PS data for link4 </td <td>17</td> <td>Inbound CS data for link0</td>         | 17            | Inbound CS data for link0                 |

| 20Outbound CS data for link221Inbound CS data for link322Outbound CS data for link323Inbound CS data for link424Outbound CS data for link425Inbound CS data for link526Outbound CS data for link527Inbound CS data for link540Inbound CS data for link541Inbound PS FIFO041Inbound PS FIFO142Inbound CPRI control words for link053Inbound CPRI control words for link154Outbound CPRI control words for link155Inbound CPRI control words for link256Outbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link360Outbound CPRI control words for link361Inbound CPRI control words for link462Outbound CPRI control words for link363Inbound CPRI control words for link463Inbound CPRI control words for link463Inbound CPRI control words for link463Inbound CPRI control words for link4                                                                                                                                                                                                                                                                                                                                                                                                           | 18            | Outbound CS data for link1                |

| 21     Inbound CS data for link2       22     Outbound CS data for link3       23     Inbound CS data for link4       24     Outbound CS data for link4       25     Inbound CS data for link5       26     Outbound CS data for link5       27     Inbound CS data for link5       40     Inbound CS data for link5       41     Inbound PS FIFO0       41     Inbound PS FIFO1       42     Inbound CPRI control words for link0       53     Inbound CPRI control words for link1       54     Outbound CPRI control words for link1       55     Inbound CPRI control words for link2       56     Outbound CPRI control words for link2       57     Inbound CPRI control words for link2       58     Outbound CPRI control words for link3       59     Inbound CPRI control words for link3       60     Outbound CPRI control words for link4       60     Outbound CPRI control words for link4       61     Inbound CPRI control words for link4       62     Outbound CPRI control words for link4       63     Inbound CPRI control words for link4       64     Outbound CPRI control words for link4       65     Outbound CPRI control words for link4       66     Outbound CPRI control words for link4       67     Inbound CPRI control wo | 19            | Inbound CS data for link1                 |

| 22Outbound CS data for link323Inbound CS data for link424Outbound CS data for link425Inbound CS data for link526Outbound CS data for link527Inbound CS data for link540Inbound PS FIFO041Inbound PS FIFO142Inbound CPRI control words for link053Inbound CPRI control words for link154Outbound CPRI control words for link155Inbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link360Outbound CPRI control words for link359Inbound CPRI control words for link360Outbound CPRI control words for link361Inbound CPRI control words for link461Inbound CPRI control words for link462Outbound CPRI control words for link363Inbound CPRI control words for link463Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20            | Outbound CS data for link2                |

| 23Inbound CS data for link324Outbound CS data for link425Inbound CS data for link526Outbound CS data for link527Inbound CS data for link540Inbound PS FIFO041Inbound PS FIFO142Inbound PS FIFO252Outbound CPRI control words for link053Inbound CPRI control words for link154Outbound CPRI control words for link155Inbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link30utbound CPRI control words for link360Outbound CPRI control words for link461Inbound CPRI control words for link362Outbound CPRI control words for link463Inbound CPRI control words for link463Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21            | Inbound CS data for link2                 |

| 24Outbound CS data for link425Inbound CS data for link526Outbound CS data for link527Inbound CS data for link540Inbound PS FIFO041Inbound PS FIFO142Inbound PS FIFO252Outbound CPRI control words for link053Inbound CPRI control words for link154Outbound CPRI control words for link155Inbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound CPRI control words for link360Outbound CPRI control words for link4<br>Outbound CPRI control words for link3<br>Outbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound PS data for link161Inbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link4<br>Outbound PS data for link462Outbound CPRI control words for link4<br>Outbound PS data for link363Inbound CPRI control words for link563Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                    | 22            | Outbound CS data for link3                |

| 25Inbound CS data for link426Outbound CS data for link527Inbound CS data for link540Inbound PS FIFO041Inbound PS FIFO142Inbound CPRI control words for link053Inbound CPRI control words for link154Outbound CPRI control words for link155Inbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link359Inbound CPRI control words for link360Outbound CPRI control words for link461Inbound CPRI control words for link462Outbound CPRI control words for link463Inbound CPRI control words for link4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23            | Inbound CS data for link3                 |

| 26Outbound CS data for link527Inbound CS data for link540Inbound PS FIFO041Inbound PS FIFO142Inbound PS FIFO252Outbound CPRI control words for link053Inbound CPRI control words for link154Outbound CPRI control words for link155Inbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound CPRI control words for link360Outbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link4<br>Outbound PS data for link362Outbound CPRI control words for link4<br>Outbound PS data for link363Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24            | Outbound CS data for link4                |

| 27Inbound CS data for link540Inbound PS FIFO041Inbound PS FIFO142Inbound PS FIFO252Outbound CPRI control words for link053Inbound CPRI control words for link154Outbound CPRI control words for link155Inbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link30utbound CPRI control words for link30utbound CPRI control words for link30utbound CPRI control words for link460Outbound CPRI control words for link461Inbound CPRI control words for link362Outbound CPRI control words for link363Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25            | Inbound CS data for link4                 |

| 40Inbound PS FIFO041Inbound PS FIFO142Inbound PS FIFO252Outbound CPRI control words for link053Inbound CPRI control words for link154Outbound CPRI control words for link155Inbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound CPRI control words for link3<br>Outbound PS data for link160Outbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link4<br>Outbound PS data for link362Outbound CPRI control words for link4<br>Outbound PS data for link363Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26            | Outbound CS data for link5                |

| 41Inbound PS FIFO142Inbound PS FIFO252Outbound CPRI control words for link053Inbound CPRI control words for link154Outbound CPRI control words for link155Inbound CPRI control words for link256Outbound CPRI control words for link257Inbound CPRI control words for link360Outbound CPRI control words for link379Inbound CPRI control words for link360Outbound CPRI control words for link461Inbound CPRI control words for link462Outbound PS data for link363Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27            | Inbound CS data for link5                 |

| 42Inbound PS FIFO252Outbound CPRI control words for link053Inbound CPRI control words for link054Outbound CPRI control words for link155Inbound CPRI control words for link156Outbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound PS data for link059Inbound CPRI control words for link3<br>Outbound PS data for link160Outbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link4<br>Outbound PS data for link362Outbound CPRI control words for link5<br>Outbound PS data for link463Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40            | Inbound PS FIFO0                          |

| 52Outbound CPRI control words for link053Inbound CPRI control words for link054Outbound CPRI control words for link155Inbound CPRI control words for link256Outbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound PS data for link059Inbound CPRI control words for link4<br>Outbound PS data for link260Outbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link3<br>Outbound PS data for link362Outbound CPRI control words for link5<br>Outbound PS data for link3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41            | Inbound PS FIFO1                          |

| 53Inbound CPRI control words for link054Outbound CPRI control words for link155Inbound CPRI control words for link156Outbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound PS data for link059Inbound CPRI control words for link4<br>Outbound PS data for link160Outbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link3<br>Outbound PS data for link362Outbound CPRI control words for link5<br>Outbound PS data for link3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42            | Inbound PS FIFO2                          |

| 54Outbound CPRI control words for link155Inbound CPRI control words for link156Outbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound PS data for link059Inbound CPRI control words for link4<br>Outbound PS data for link160Outbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link4<br>Outbound PS data for link362Outbound CPRI control words for link5<br>Outbound PS data for link4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52            | Outbound CPRI control words for link0     |

| 55Inbound CPRI control words for link156Outbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound PS data for link059Inbound CPRI control words for link4<br>Outbound PS data for link160Outbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link4<br>Outbound PS data for link362Outbound CPRI control words for link4<br>Outbound PS data for link463Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53            | Inbound CPRI control words for link0      |

| 56Outbound CPRI control words for link257Inbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound PS data for link059Inbound CPRI control words for link3<br>Outbound PS data for link160Outbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link3<br>Outbound PS data for link362Outbound CPRI control words for link4<br>Outbound PS data for link4<br>Outbound PS data for link363Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54            | Outbound CPRI control words for link1     |

| 57Inbound CPRI control words for link258Outbound CPRI control words for link3<br>Outbound PS data for link059Inbound CPRI control words for link3<br>Outbound PS data for link160Outbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link4<br>Outbound PS data for link362Outbound CPRI control words for link5<br>Outbound PS data for link4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55            | Inbound CPRI control words for link1      |

| 58Outbound CPRI control words for link3<br>Outbound PS data for link059Inbound CPRI control words for link3<br>Outbound PS data for link160Outbound CPRI control words for link4<br>Outbound PS data for link261Inbound CPRI control words for link4<br>Outbound PS data for link362Outbound CPRI control words for link4<br>Outbound PS data for link4<br>Outbound PS data for link463Inbound CPRI control words for link5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56            | Outbound CPRI control words for link2     |