# TMS320DM35x Digital Media System-on-Chip (DMSoC) Audio Serial Port (ASP)

# Reference Guide

Literature Number: SPRUED3C May 2006-Revised September 2007

## **Contents**

| Pre | race    |                                                        | . 6 |

|-----|---------|--------------------------------------------------------|-----|

| 1   | Introdu | ıction                                                 | . 9 |

|     | 1.1     | Purpose of the Peripheral                              | . 9 |

|     | 1.2     | Features                                               | . 9 |

|     | 1.3     | Functional Block Diagram                               | 10  |

|     | 1.4     | Industry Standard Compliance Statement                 | 10  |

| 2   | Periph  | eral Architecture                                      | 11  |

|     | 2.1     | Clock Control                                          | 11  |

|     | 2.2     | Signal Descriptions                                    | 11  |

|     | 2.3     | Clock, Frames, and Data                                | 11  |

|     | 2.4     | ASP Standard Operation                                 | 25  |

|     | 2.5     | -Law/A-Law Companding Hardware Operation               | 37  |

|     | 2.6     | Resetting the Serial Port: RRST, XRST, GRST, and RESET | 39  |

|     | 2.7     | ASP Initialization Procedure                           | 40  |

|     | 2.8     | SPI Operation Using the Clock Stop Mode                | 43  |

|     | 2.9     | Interrupt Support                                      | 50  |

|     | 2.10    | EDMA Event Support                                     | 51  |

|     | 2.11    | Power Management                                       | 52  |

|     | 2.12    | Emulation Considerations                               | 52  |

| 3   | Registe | ers                                                    | 53  |

|     | 3.1     | Data Receive Register (DRR)                            | 53  |

|     | 3.2     | Data Transmit Register (DXR)                           |     |

|     | 3.3     | Serial Port Control Register (SPCR)                    | 54  |

|     | 3.4     | Receive Control Register (RCR)                         |     |

|     | 3.5     | Transmit Control Register (XCR)                        | 59  |

|     | 3.6     | Sample Rate Generator Register (SRGR)                  |     |

|     | 3.7     | Pin Control Register (PCR)                             |     |

## **List of Figures**

| 1  | ASP Block Diagram                                              |    |

|----|----------------------------------------------------------------|----|

| 2  | Clock and Frame Generation                                     | 12 |

| 3  | Transmit Data Clocking                                         | 13 |

| 4  | Receive Data Clocking                                          | 13 |

| 5  | Sample Rate Generator Block Diagram                            | 14 |

| 6  | Digital Loopback Mode                                          | 17 |

| 7  | Programmable Frame Period and Width                            | 18 |

| 8  | Dual-Phase Frame Example                                       | 20 |

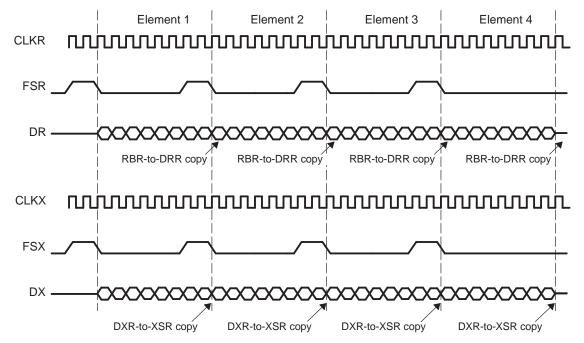

| 9  | Single-Phase Frame of Four 8-Bit Elements                      | 22 |

| 10 | Single-Phase Frame of One 32-Bit Element                       | 22 |

| 11 | Data Delay                                                     | 23 |

| 12 | ASP Standard Operation                                         | 25 |

| 13 | Receive Operation                                              | 26 |

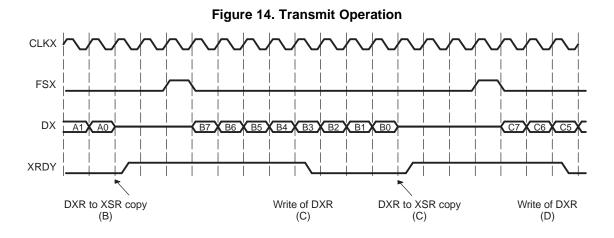

| 14 | Transmit Operation                                             | 26 |

| 15 | Maximum Frame Frequency for Transmit and Receive               | 27 |

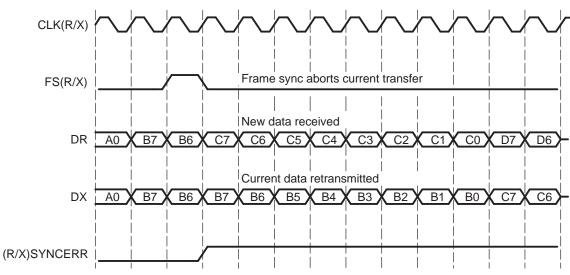

| 16 | Unexpected Frame Synchronization With (R/X)FIG = 0             | 28 |

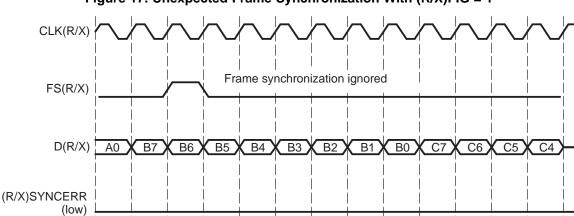

| 17 | Unexpected Frame Synchronization With (R/X)FIG = 1             | 29 |

| 18 | Maximum Frame Frequency Operation With 8-Bit Data              | 29 |

| 19 | Data Packing at Maximum Frame Frequency With (R/X)FIG = 1      | 30 |

| 20 | Serial Port Receive Overrun                                    | 31 |

| 21 | Serial Port Receive Overrun Avoided                            | 31 |

| 22 | Decision Tree Response to Receive Frame Synchronization Pulse  | 32 |

| 23 | Unexpected Receive Frame Synchronization Pulse                 | 33 |

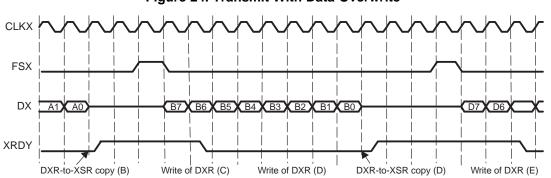

| 24 | Transmit With Data Overwrite                                   | 33 |

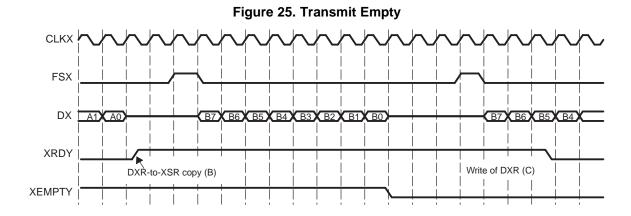

| 25 | Transmit Empty                                                 | 34 |

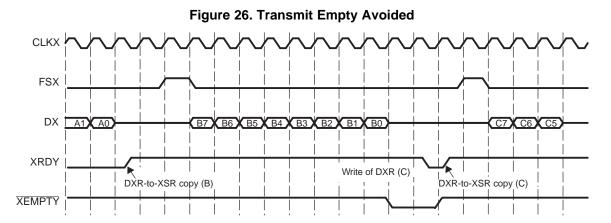

| 26 | Transmit Empty Avoided                                         | 34 |

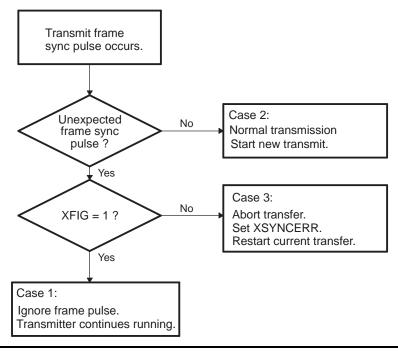

| 27 | Decision Tree Response to Transmit Frame Synchronization Pulse |    |

| 28 | Unexpected Transmit Frame Synchronization Pulse                |    |

| 29 | Companding Flow                                                |    |

| 30 | Companding Data Formats                                        |    |

| 31 | Transmit Data Companding Format in DXR                         |    |

| 32 | Companding of Internal Data                                    |    |

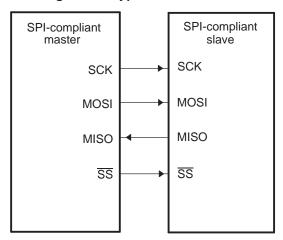

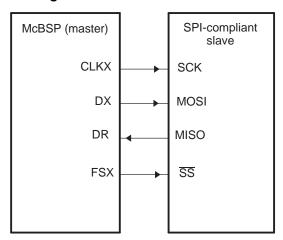

| 33 | Typical SPI Interface                                          |    |

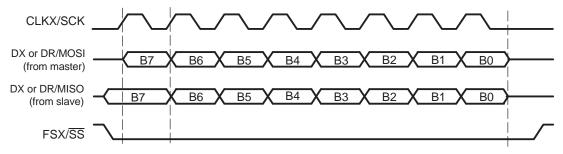

| 34 | SPI Transfer with CLKSTP = 2h (no clock delay) and CLKXP = 0   |    |

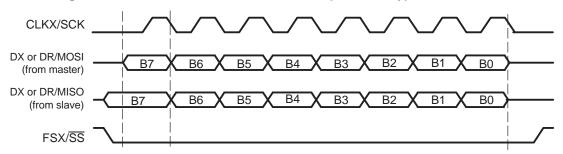

| 35 | SPI Transfer With CLKSTP = 3h (clock delay) and CLKXP = 0      |    |

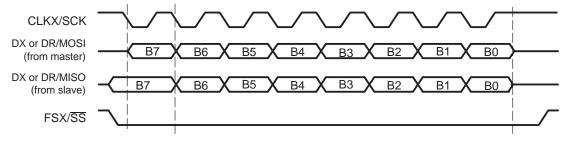

| 36 | SPI Transfer With CLKSTP = 2h (no clock delay) and CLKXP = 1   |    |

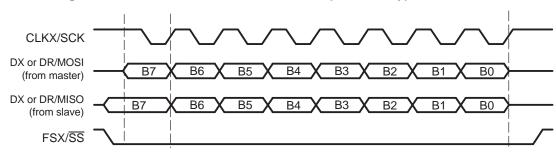

| 37 | SPI Transfer With CLKSTP = 3h (clock delay) and CLKXP = 1      | 47 |

| 38 | ASP as the SPI Master                                          |    |

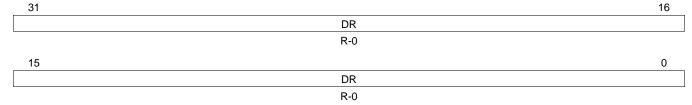

| 39 | Data Receive Register (DRR)                                    |    |

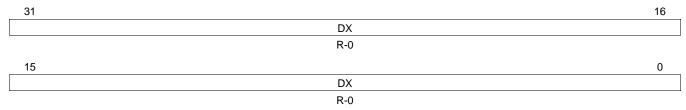

| 40 | Data Transmit Register (DXR)                                   |    |

| 41 | Serial Port Control Register (SPCR)                            |    |

| 42 | Receive Control Register (RCR)                                 |    |

| 43 | Transmit Control Register (XCR)                                |    |

| 44 | Sample Rate Generator Register (SRGR)                          |    |

| 45 | Pin Control Register (PCR)                                     | 62 |

### **List of Tables**

| 1  | ASP Interface Signals                                                                | 11 |

|----|--------------------------------------------------------------------------------------|----|

| 2  | Choosing an Input Clock for the Sample Rate Generator With the SCLKME and CLKSM Bits | 14 |

| 3  | Receive Clock Selection                                                              | 17 |

| 4  | Transmit Clock Selection                                                             | 17 |

| 5  | Receive Frame Synchronization Selection                                              | 19 |

| 6  | Transmit Frame Synchronization Selection                                             | 19 |

| 7  | RCR/XCR Fields Controlling Elements per Frame and Bits per Element                   | 20 |

| 8  | Receive/Transmit Frame Length Configuration                                          | 21 |

| 9  | Receive/Transmit Element Length Configuration                                        | 21 |

| 10 | Effect of RJUST Bit Values With 12-Bit Example Data ABCh                             | 23 |

| 11 | Effect of RJUST Bit Values With 20-Bit Example Data ABCDEh                           | 24 |

| 12 | Justification of Expanded Data in DRR                                                | 38 |

| 13 | Reset State of ASP Pins                                                              | 39 |

| 14 | Receiver Clock and Frame Configurations                                              | 40 |

| 15 | Transmitter Clock and Frame Configurations                                           | 40 |

| 16 | Bits Used to Enable and Configure the Clock Stop Mode                                | 44 |

| 17 | Effects of CLKSTP and CLKXP Bits on the Clock Scheme                                 | 45 |

| 18 | Bit Values Required to Configure the ASP as an SPI Master                            | 49 |

| 19 | ASP Emulation Modes Selectable With the FREE and SOFT Bits of SPCR                   | 52 |

| 20 | ASP Registers                                                                        | 53 |

| 21 | Data Receive Register (DRR) Field Descriptions                                       | 53 |

| 22 | Data Transmit Register (DXR) Field Descriptions                                      | 54 |

| 23 | Serial Port Control Register (SPCR) Field Descriptions                               | 55 |

| 24 | Receive Control Register (RCR) Field Descriptions                                    | 57 |

| 25 | Transmit Control Register (XCR) Field Descriptions                                   | 59 |

| 26 | Sample Rate Generator Register (SRGR) Field Descriptions                             | 61 |

| 27 | Pin Control Register (PCR) Field Descriptions                                        | 62 |

### Read This First

This document describes the Audio Serial Port (ASP) in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The ASP is a specialized version of the ASP peripheral commonly found in other TI devices.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

### TMS320DM355 Digital Media System-on-Chip (DMSoC)

#### Related Documentation From Texas Instruments

The following documents describe the TMS320DM355 Digital Media System-on-Chip (DMSoC). Copies of these documents are available on the internet at www.ti.com. Contact your TI representative for Extranet access.

- SPRS463— *TMS320DM355 Digital Media System-on-Chip (DMSoC) Data Manual* This document describes the overall TMS320DM355 system, including device architecture and features, memory map, pin descriptions, timing characteristics and requirements, device mechanicals, etc.

- **SPRZ264— TMS320DM355 DMSoC Silicon Errata** Describes the known exceptions to the functional specifications for the TMS320DM355 DMSoC.

- SPRUFB3— *TMS320DM355 ARM Subsystem Reference Guide* This document describes the ARM Subsystem in the TMS320DM355 Digital Media System-on-Chip (DMSoC). The ARM subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In general, the ARM is responsible for configuration and control of the device; including the components of the ARM Subsystem, the peripherals, and the external memories.

- SPRUED1— TMS320DM35x DMSoC Asynchronous External Memory Interface (EMIF) Reference Guide This document describes the asynchronous external memory interface (EMIF) in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The EMIF supports a glueless interface to a variety of external devices.

- SPRUED2— TMS320DM35x DMSoC Universal Serial Bus (USB) Controller Reference Guide This document describes the universal serial bus (USB) controller in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The USB controller supports data throughput rates up to 480 Mbps. It provides a mechanism for data transfer between USB devices and also supports host negotiation.

- SPRUED3— TMS320DM35x DMSoC Audio Serial Port (ASP) Reference Guide This document describes the operation of the audio serial port (ASP) audio interface in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The primary audio modes that are supported by the ASP are the AC97 and IIS modes. In addition to the primary audio modes, the ASP supports general serial port receive and transmit operation, but is not intended to be used as a high-speed interface.

- SPRUED4— TMS320DM35x DMSoC Serial Peripheral Interface (SPI) Reference Guide This document describes the serial peripheral interface (SPI) in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The SPI is a high-speed synchronous serial input/output port that allows a serial bit stream of programmed length (1 to 16 bits) to be shifted into and out of the device at a programmed bit-transfer rate. The SPI is normally used for communication between the DMSoC and external peripherals. Typical applications include an interface to external I/O or peripheral expansion via devices such as shift registers, display drivers, SPI EPROMs and analog-to-digital converters.

- SPRUED9— TMS320DM35x DMSoC Universal Asynchronous Receiver/Transmitter (UART) Reference Guide This document describes the universal asynchronous receiver/transmitter (UART) peripheral in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The UART peripheral performs serial-to-parallel conversion on data received from a peripheral device, and parallel-to-serial conversion on data received from the CPU.

- SPRUEE0— TMS320DM35x DMSoC Inter-Integrated Circuit (I2C) Peripheral Reference Guide This document describes the inter-integrated circuit (I2C) peripheral in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The I2C peripheral provides an interface between the DMSoC and other devices compliant with the I2C-bus specification and connected by way of an I2C-bus. External components attached to this 2-wire serial bus can transmit and receive up to 8-bit wide data to and from the DMSoC through the I2C peripheral. This document assumes the reader is familiar with the I2C-bus specification.

- SPRUEE2— TMS320DM35x DMSoC Multimedia Card (MMC)/Secure Digital (SD) Card Controller Reference Guide This document describes the multimedia card (MMC)/secure digital (SD) card controller in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The MMC/SD card is used in a number of applications to provide removable data storage. The MMC/SD controller provides an interface to external MMC and SD cards. The communication between the MMC/SD controller and MMC/SD card(s) is performed by the MMC/SD protocol.

- SPRUEE4— TMS320DM35x DMSoC Enhanced Direct Memory Access (EDMA) Controller Reference Guide This document describes the operation of the enhanced direct memory access (EDMA3) controller in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The EDMA controller's primary purpose is to service user-programmed data transfers between two memory-mapped slave endpoints on the DMSoC.

- SPRUEE5— TMS320DM35x DMSoC 64-bit Timer Reference Guide This document describes the operation of the software-programmable 64-bit timers in the TMS320DM35x Digital Media System-on-Chip (DMSoC). Timer 0, Timer 1, and Timer 3 are used as general-purpose (GP) timers and can be programmed in 64-bit mode, dual 32-bit unchained mode, or dual 32-bit chained mode; Timer 2 is used only as a watchdog timer. The GP timer modes can be used to generate periodic interrupts or enhanced direct memory access (EDMA) synchronization events and Real Time Output (RTO) events (Timer 3 only). The watchdog timer mode is used to provide a recovery mechanism for the device in the event of a fault condition, such as a non-exiting code loop.

- SPRUEE6— TMS320DM35x DMSoC General-Purpose Input/Output (GPIO) Reference Guide This document describes the general-purpose input/output (GPIO) peripheral in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The GPIO peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an input, you can detect the state of the input by reading the state of an internal register. When configured as an output, you can write to an internal register to control the state driven on the output pin.

- SPRUEE7— TMS320DM35x DMSoC Pulse-Width Modulator (PWM) Reference Guide This document describes the pulse-width modulator (PWM) peripheral in the TMS320DM35x Digital Media System-on-Chip (DMSoC).

- SPRUEH7— TMS320DM35x DMSoC DDR2/Mobile DDR (DDR2/mDDR) Memory Controller Reference Guide This document describes the DDR2 / mobile DDR memory controller in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The DDR2 / mDDR memory controller is used to interface with JESD79D-2A standard compliant DDR2 SDRAM and mobile DDR devices.

- SPRUF71— TMS320DM35x DMSoC Video Processing Front End (VPFE) Users Guide This document describes the Video Processing Front End (VPFE) in the TMS320DM35x Digital Media System-on-Chip (DMSoC).

- SPRUF72— TMS320DM35x DMSoC Video Processing Back End (VPBE) Users Guide This document describes the Video Processing Back End (VPBE) in the TMS320DM35x Digital Media System-on-Chip (DMSoC).

- SPRUF74— TMS320DM35x DMSoC Real Time Out (RTO) Controller Reference Guide This document describes the Real Time Out (RTO) controller in the TMS320DM35x Digital Media System-on-Chip (DMSoC).

The following documents describe TMS320DM35x Digital Media System-on-Chip (DMSoC) that are not available by literature number. Copies of these documents are available (by title only) on the internet at www.ti.com. Contact your TI representative for Extranet access.

- TMS320DM35x DDR2 / mDDR Board Design Application Note This provides board design recommendations and guidelines for DDR2 and mobile DDR.

- TMS320DM35x USB Board Design and Layout Guidelines Application Note This provides board design recommendations and guidelines for high speed USB.

## Audio Serial Port (ASP) Interface

#### 1 Introduction

This document describes the operation of the Audio Serial Port (ASP) in the TMS320DM35x Digital Media System-on-Chip (DMSoC). The ASP is a specialized version of the ASP peripheral commonly found in other TI devices.

#### 1.1 Purpose of the Peripheral

The primary use for the audio serial port (ASP) is for audio interface purposes. The primary audio modes that are supported by the ASP are the AC97 and IIS modes. In addition to the primary audio modes, the ASP can be programmed to support other serial formats but is not intended to be used as a high-speed interface.

#### 1.2 Features

The ASP provides the following functions:

- Full-duplex communication

- Double-buffered data registers, which allow a continuous data stream

- Independent framing and clocking for receive and transmit

- Direct interface to industry-standard codecs, analog interface chips (AICs), and other serially connected analog-to-digital (A/D) and digital-to-analog (D/A) devices

- External shift clock or an internal, programmable frequency shift clock for data transfer

In addition, the ASP has the following capabilities:

- Direct interface to:

- AC97 compliant devices (the necessary multiphase frame synchronization capability is provided)

- IIS compliant devices

- SPI Protocol (master mode only)

- A wide selection of data sizes, including 8, 12, 16, 20, 24, and 32 bits

- -Law and A-Law companding

- 8-bit data transfers with the option of LSB or MSB first

- Programmable polarity for both frame synchronization and data clocks

- Highly programmable internal clock and frame generation

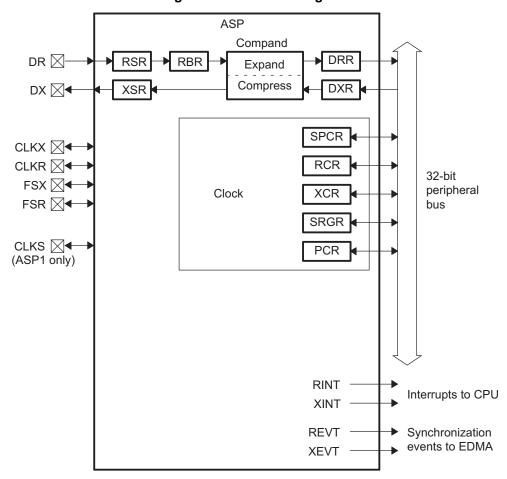

### 1.3 Functional Block Diagram

The ASP consists of a data path and control path, as shown in Figure 1

Figure 1. ASP Block Diagram

#### 1.4 Industry Standard Compliance Statement

The ASP supports the following industry standard interfaces:

**AC97**— The AC97 standard specifies a 5-wire digital serial link between an audio codec device and its digital controller.

IIS is a protocol for transmitting two channels of digital audio data over a single serial connection. The IIS bus is an industry standard three-wire interface for streaming stereo audio between devices, typically between a CPU and a DAC/ADC.

#### 2 Peripheral Architecture

This section describes the architecture of the ASP.

#### 2.1 Clock Control

The ASP can use an internal or external clock source. The internal clock source to the ASP is an output of the PLL Controller. Either clock source can be divided down inside the ASP to generate the actual interface bit clock frequency. For information on device clocking and the PLL Controller refer to the *TMS320DM35x ARM Subsystem Reference Guide* (SPRUEE8) .For detailed timing information, see the device-specific data manual. Detailed information about how the interface clock and frame synchronization signals are generated is provided in Section 2.3.

#### 2.2 Signal Descriptions

The signals used on the ASP audio interface are listed in Table 1.

Table 1. ASP Interface Signals

| Pin  | I/O/Z | Description                                                                                                                             |

|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| CLKR | I/O/Z | Receive clock - supplies or receives a reference clock for the receiver; or supplies a reference clock to the sample rate generator     |

| CLKX | I/O/Z | Transmit clock - supplies or receives a reference clock for the transmitter; or supplies a reference clock to the sample rate generator |

| DR   | I     | Received serial data                                                                                                                    |

| DX   | O/Z   | Transmitted serial data                                                                                                                 |

| FSR  | I/O/Z | Receive frame synchronization - control signal to synchronize the start of received data                                                |

| FSX  | I/O/Z | Transmit frame synchronization - control signal to synchronize the start of transmitted data                                            |

| CLKS | I     | External master clock input                                                                                                             |

#### 2.3 Clock, Frames, and Data

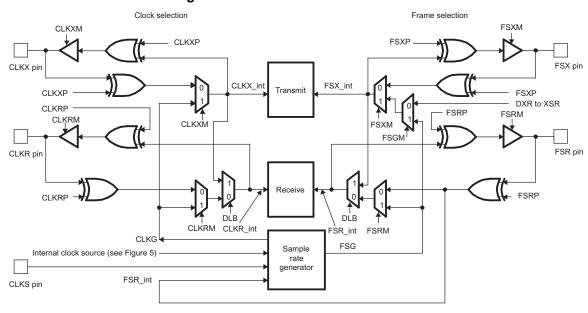

The ASP has several ways of selecting clocking and framing for both the receiver and transmitter. Clocking and framing can be sent to both portions by the sample rate generator. Each portion can select external clocking and/or framing independently. Figure 2 is a block diagram of the clock and frame selection circuitry.

Figure 2. Clock and Frame Generation

#### 2.3.1 Frame and Clock Operation

Receive and transmit frame sync pulses (FSR/X), and clocks (CLKR/X), can either be generated internally by the sample rate generator (see section Section 2.3.2) or be driven by an external source. The source of frame sync and clock is selected by programming the mode bits, FS(R/X)M and CLK(R/X)M respectively, in the pin control register (PCR).

When FSR and FSX are inputs (FSXM = FSRM = 0), the ASP detects them on the internal falling edge of clock, CLKR\_int and CLKX\_int, respectively (see Figure 2). The receive data arriving at the DR pin is also sampled on the falling edge of CLKR\_int. These internal clock signals are either derived from external source via the CLK(R/X) pins or driven by the sample rate generator clock (CLKG) internal to the ASP.

When FSR and FSX are outputs driven by the sample rate generator, they are generated (transition to their active state) on the rising edge of the internal clock, CLK(R/X)\_int. Similarly, data on DX is output on the rising edge of CLKX\_int.

FSRP, FSXP, CLKRP, and CLKXP configure the polarities of FSR, FSX, CLKR, and CLKX. All frame sync signals (FSR\_int and FSX\_int) internal to the serial port are active high. If the serial port is configured for external frame synchronization (FSR/FSX are inputs to the ASP) and FSRP = FSXP = 1, the external active (low) frame sync signals are inverted before being sent to the receiver signal (FSR\_int) and transmitter signal (FSX\_int). Similarly, if internal synchronization is selected (FSR/FSX are outputs), the internal active (high) sync signals are inverted if the polarity bit FS(R/X)P = 1, before being sent to the FS(R/X) pin. Figure 2 shows this inversion using XOR gates.

On the transmit side, the transmit clock polarity bit, CLKXP, sets the edge used to shift and clock out transmit data. Data is always transmitted on the rising edge of CLKX\_int (see Figure 3). If CLKXP = 1 and external clocking is selected (CLKXM = 0 and CLKX is an input), the external falling-edge-triggered input clock on CLKX is inverted to a rising-edge-triggered clock before being sent to the transmitter. If CLKXP = 1 and internal clocking is selected (CLKXM = 1 and CLKX is an output pin), the internal (rising-edge-triggered) clock, CLKX\_int, is inverted before being sent out on the CLKX pin.

Similarly, the receiver can reliably sample data that is clocked (by the transmitter) with a rising-edge clock. The receive clock polarity bit, CLKRP, sets the edge used to sample received data. The receive data is always sampled on the falling edge of CLKR\_int (see Figure 4). Therefore, if CLKRP = 1 and external clocking is selected (CLKRM = 0 and CLKR is an input pin), the external rising-edge triggered input clock on CLKR is inverted to a falling-edge clock before being sent to the receiver. If CLKRP = 1 and internal clocking is selected (CLKRM = 1), the internal falling-edge-triggered clock is inverted to a rising edge before being sent out on the CLKR pin.

In a system where the same clock (internal or external) is used to clock the receiver and transmitter, CLKRP = CLKXP. The receiver uses the opposite edge as the transmitter to ensure valid setup and hold times of data around this edge. Figure 4 shows how data clocked by an external serial device using a rising-edge clock can be sampled by the ASP receiver with the falling edge of the same clock.

CLKX\_int

Disable time

CLKR\_int

Data setup

Data hold

DR

B7

B6

#### 2.3.2 Sample Rate Generator Clocking and Framing

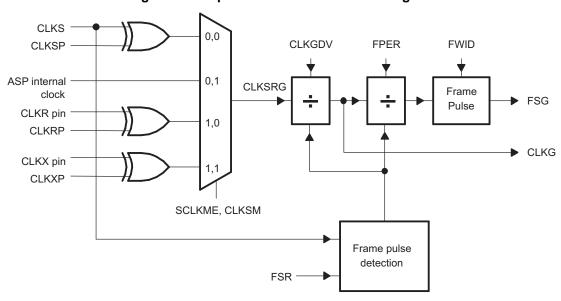

The sample rate generator is composed of a 3-stage clock divider that provides a programmable data clock (CLKG) and framing signal (FSG), as shown in Figure 5. CLKG and FSG are ASP internal signals that can be programmed to drive receive and/or transmit clocking, CLK(R/X), and framing, FS(R/X). The sample rate generator can be programmed to be driven by an internal clock source or an internal clock derived from an external clock source.

The sample rate generator is not used when CLKX, FSX, CLKR, and FSR are driven by an external source. Therefore, the GRST bit in SPCR does not need to be enabled (GRST = 1) for this setup. The three stages of the sample rate generator circuit compute:

- Clock divide-down (CLKGDV): The number of input clocks per data bit clock

- Frame period (FPER): The frame period in data bit clocks

- Frame width (FWID): The width of an active frame pulse in data bit clocks

In addition, a frame pulse detection and clock synchronization module allows synchronization of the clock divide-down with an incoming frame pulse. The operation of the sample rate generator during device reset is described in Section 2.6.

Figure 5. Sample Rate Generator Block Diagram

#### 2.3.3 Data Clock Generation

When the receive/transmit clock mode is set to 1 (CLK(R/X)M = 1), the data clocks (CLK(R/X)) are driven by the internal sample rate generator output clock, CLKG. You can select for the receiver and transmitter from a variety of data bit clocks including:

- The input clock to the sample rate generator, which can be either the internal clock source or a dedicated external clock source via the CLKX, CLKR or CLKS pins. See Section 2.3.3.1 for details on the source of the ASP internal clock.

- The input clock source (internal clock source or external clock (CLKX/CLKR/CLKS) to the sample rate generator can be divided down by a programmable value (CLKGDV) to drive CLKG.

Regardless of the source to the sample rate generator, the rising edge of CLKSRG (see Figure 5) generates CLKG and FSG.

#### 2.3.3.1 Input Clock Source Mode: CLKSM and SCLKME

The sample rate generator's input clock signal can be driven from one of four sources selectable with the SCLKME bit of the PCR and the CLKSM bit of the SRGR (see Table 2).

Table 2. Choosing an Input Clock for the Sample Rate Generator With the SCLKME and CLKSM Bits

| SCLKME | CLKSM | Input Clock For Sample Rate Generator |  |

|--------|-------|---------------------------------------|--|

| 0      | 0     | Signal on CLKS pin                    |  |

| 0      | 1     | ASP internal input clock              |  |

| 1      | 0     | Signal on CLKR pin                    |  |

| 1      | 1     | Signal on CLKX pin                    |  |

#### 2.3.3.2 Sample Rate Generator Data Bit Clock Rate: CLKGDV

The first divider stage generates the serial data bit clock from the input clock. This divider stage uses a counter that is preloaded by CLKGDV and that contains the divide ratio value. The output of this stage is the data bit clock that is output on the sample rate generator output, CLKG, and that serves as the input for the second and third divider stages.

CLKG has a frequency equal to 1/(CLKGDV + 1) of the sample rate generator input clock. Thus, the sample rate generator input clock frequency is divided by a value between 1 to 256. The CLKGDV value chosen must result in a clock that meets the timing requirements/limitations specified in the device-specific data manual.

When CLKGDV is an odd value or equal to 0, the CLKG duty cycle is 50%. Note that an odd CLKGDV value means an even divide down of the source clock and an even CLKGDV value means an odd divide down of the source clock. When CLKGDV is an even value (2p), the high state duration is p + 1 cycles and the low state duration is p cycles. This is illustrated in Example 1, Example 2, and Example 3.

In the following examples:

S<sub>IN</sub> = sample generator input clock period

f<sub>IN</sub> = sample generator input clock frequency

S<sub>G</sub> = CLKG period

f<sub>G</sub> = CLKG frequency

The following equation is given above:  $f_G = f_{IN}/(CLKGDV + 1)$ ; therefore,  $S_G = (CLKGDV + 1) \ _1S_{IN}$ .

#### Example 1. CLKGDV = 0

$$CLKGDV = 0$$

$$S_G = (CLKGDV + 1) \ _1S_{IN} = (0 + 1) \ _1S_{IN} = S_{IN}$$

Pulse width high =  $S_{IN} \ 1 (CLKGDV + 1)/2 = S_{IN} \ 1 (0 + 1)/2 = 0.5 \ 1 S_{IN}$

Pulse width low =  $S_{IN} (CLKGDV + 1)/2 = S_{IN} (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5 (0+1)/2 = 0.5$

#### Example 2. CLKGDV = 1

$$CLKGDV = 1$$

$$S_G = (CLKGDV + 1) \ _1S_{IN} = (1 + 1) \ _1S_{IN} = 2 \ _1S_{IN}$$

Pulse width high =  $S_{IN} \Im(CLKGDV + 1)/2 = S_{IN} \Im(1 + 1)/2 = S_{IN}$

Pulse width low =  $S_{IN}$   $\mathfrak{I}(CLKGDV + 1)/2 = S_{IN}$   $\mathfrak{I}(1+1)/2 = S_{IN}$

#### Example 3. CLKGDV = 2

$$CLKGDV = 2$$

$$S_G = (CLKGDV + 1) \ {}_1S_{IN} = (2 + 1) \ {}_1S_{IN} = 3 \ {}_1S_{IN}$$

Pulse width high =  $S_{IN} \, {}_{1}(CLKGDV/2 + 1) = S_{IN} \, {}_{1}(2/2 + 1) = 2 \, {}_{1}S_{IN}$

Pulse width low =  $S_{IN} 3CLKGDV/2 = S_{IN} 32/2 = 1 3S_{IN}$

#### 2.3.3.3 Bit Clock Polarity: CLKSP

The external clock (CLKS) is selected to drive the sample rate generator clock divider by selecting CLKSM = 0 in the sample rate generator register (SRGR) and SCLKME = 0 in the pin control register (PCR). In this case, the CLKSP bit in SRGR selects the edge of CLKS on which sample rate generator data bit clock (CLKG) and frame sync signal (FSG) are generated. Since the rising edge of CLKSRG generates CLKG and FSG, the rising edge of CLKS when CLKSP = 0 or the falling edge of CLKS when CLKSP = 1 causes the transition on CLKG and FSG.

#### 2.3.3.4 Digital Loopback Mode: DLB

DLB mode cannot be used when the ASP is in clock stop mode (CLKSTP = 1x in SPCR). Setting DLB = 1 in SPCR enables digital loopback mode. In DLB mode, DR, FSR, and CLKR are internally connected through multiplexers to DX, FSX, and CLKX, respectively, as shown in Figure 2 and Figure 6. DLB mode allows testing of serial port code without using the external interface of the ASP. CLKX and FSX must be enabled as outputs (CLKXM = FSXM = 1) in DLB mode.

Figure 6. Digital Loopback Mode

#### 2.3.3.5 Receive Clock Selection: DLB, CLKRM

Table 3 shows how the digital loopback bit (DLB) and the CLKRM bit in PCR select the receiver clock. In digital loopback mode (DLB = 1), the transmitter clock drives the receiver. CLKRM determines whether the CLKR pin is an input or an output.

**Table 3. Receive Clock Selection**

| DLB Bit<br>in SPCR | CLKRM Bit<br>in PCR | Source of Receive Clock                                                                                   | CLKR Function                                                                           |

|--------------------|---------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 0                  | 0                   | CLKR acts as an input driven by the external clock and inverted as determined by CLKRP before being used. | Input.                                                                                  |

| 0                  | 1                   | The sample rate generator clock (CLKG) drives CLKR.                                                       | Output. CLKG inverted as determined by CLKRP before being driven out on CLKR.           |

| 1                  | 0                   | CLKX_int drives the receive clock CLKR_int as selected and is inverted.                                   | High impedance.                                                                         |

| 1                  | 1                   | CLKX_int drives CLKR_int as selected and is inverted.                                                     | Output. CLKR (same as CLKX) is inverted as determined by CLKRP before being driven out. |

#### 2.3.3.6 Transmit Clock Selection: CLKXM

Table 4 shows how the CLKXM bit in PCR selects the transmit clock and whether the CLKX pin is an input or output.

**Table 4. Transmit Clock Selection**

| CLKXM Bit<br>in PCR | Source of Transmit Clock                                                                                 | CLKX Function                                                                    |

|---------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 0                   | The external clock drives the CLKX input pin. CLKX is inverted as determined by CLKXP before being used. | Input.                                                                           |

| 1                   | The sample rate generator clock (CLKG) drives the transmit clock.                                        | Output. CLKG is inverted as determined by CLKXP before being driven out on CLKX. |

#### 2.3.3.7 Stopping Clocks

There are two methods to stop serial clocks between data transfers:

- Using the SPI CLKSTP mode where clocks are stopped between single-element transfers. This is described in Section 2.8.2.

- When the clocks are inputs to the ASP (CLKXM or CLKRM = 0 in the pin control register (PCR)) and the ASP operates in non-SPI mode (the clocks can be stopped between data transfers). If the external device stops the serial clock between data transfers, the ASP interprets it as a slowed-down serial clock. Ensure that there are no glitches on the CLK(R/X) lines as the ASP may interpret them as clock-edge transitions. Restarting the serial clock is equivalent to a normal clock transition after a slow CLK(R/X) cycle. Note that just as in normal operations, transmit under flow (XEMPTY) may occur if the DXR is not properly serviced at least three CLKX cycles before the next frame sync. Therefore, if the serial clock is stopped before DXR is properly serviced, the external device needs to restart the clock at least three CLKX cycles before the next frame sync to allow the DXR write to be properly synchronized. See Figure 26 for a graphical explanation on when DXR needs to be written to avoid underflow.

#### 2.3.4 Frame Sync Generation

Data frame synchronization is independently programmable for the receiver and the transmitter for all data delay values. When the FRST bit in the serial port control register (SPCR) is set to 1 the frame generation logic is activated to generate frame sync signals, provided that FSGM = 1 in the sample rate generator register (SRGR). The frame sync programming options are:

- A frame pulse with a programmable period between sync pulses and a programmable active width specified in SRGR.

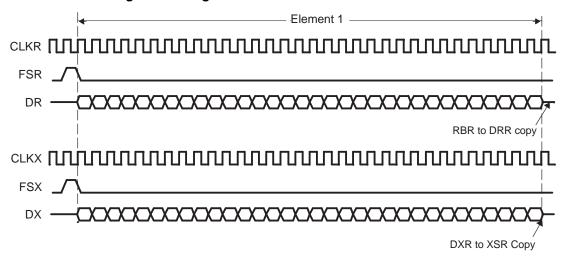

- The transmitter can trigger its own frame sync signal that is generated by a DXR-to-XSR copy. This

causes a frame sync to occur on every DXR-to-XSR copy. The data delays can be programmed as

required. However, maximum packet frequency cannot be achieved in this method for data delays of 1

and 2.

- Both the receiver and transmitter can independently select an external frame synchronization on the FSR and FSX pins, respectively.

#### 2.3.4.1 Frame Period (FPER) and Frame Width (FWID)

The FPER bits in the sample rate generator register (SRGR) are a 12-bit down-counter that can count down the generated data clocks from 4095 to 0. FPER controls the period of active frame sync pulses. The FWID bits are an 8-bit down-counter. FWID controls the active width of the frame sync pulse.

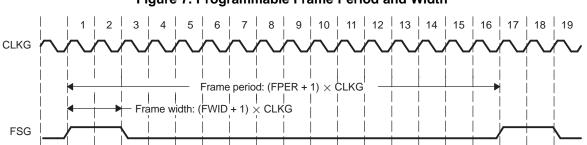

When the sample rate generator comes out of reset, FSG is in an inactive (low) state. After this, when FRST = 1 and FSGM = 1, frame sync signals are generated. The frame width value (FWID + 1) is counted down on every CLKG cycle until it reaches 0 when FSG goes low. Thus, the value of FWID + 1 determines an active frame pulse width ranging from 1 to 256 data bit clocks. At the same time, the frame period value (FPER + 1) is also counting down, and when this value reaches 0, FSG goes high again, indicating a new frame is beginning. Thus, the value of FPER + 1 determines a frame length from 1 to 4096 data bits. Figure 7 shows a frame of 16 CLKG periods (FPER = 15 or 0000 1111b). It is recommended that FWID be programmed to a value less than (R/X)WDLEN1/2."

Figure 7. Programmable Frame Period and Width

#### 2.3.4.2 Receive Frame Synchronization Selection: DLB and FSRM

Table 5 shows how you can select various sources to provide the receive frame synchronization signal. Note that in digital loopback mode (DLB = 1), the transmit frame sync signal is used as the receive frame sync signal and that DR is internally connected to DX.

**Note:** FSR\_int and FSX\_int are shown in Figure 2.

**Table 5. Receive Frame Synchronization Selection**

| DLB Bit<br>in SPCR | FSRM Bit<br>in PCR | Source of Receive Frame Synchronization                                                                                                | FSR Pin Function                                                                                                    |

|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 0                  | 0                  | External frame sync signal drives the FSR input pin, whose signal is then inverted as determined by FSRP before being used as FSR_int. | Input.                                                                                                              |

| 0                  | 1                  | Sample rate generator frame sync signal (FSG) drives FSR_int, FRST = 1.                                                                | Output. FSG is inverted as determined by FSRP before being driven out on the FSR pin.                               |

| 1                  | 0                  | FSX_int drives FSR_int. FSX is selected as shown in Table 6.                                                                           | High impedance.                                                                                                     |

| 1                  | 1                  | FSX_int drives FSR_int and is selected as shown in Table 6.                                                                            | Output. Receive (same as transmit) frame synchronization is inverted as determined by FSRP before being driven out. |

#### 2.3.4.3 Transmit Frame Synchronization Selection: FSXM and FSGM

Table 6 shows how you can select the source of the transmit frame synchronization signal. The three choices are:

- External frame sync input

- The sample rate generator frame sync signal, FSG

- A signal that indicates a DXR-to-XSR copy has been made

**Note:** FSR\_int and FSX\_int are shown in Figure 2.

**Table 6. Transmit Frame Synchronization Selection**

| FSXM Bit<br>in PCR | FSGM Bit in SRGR | Source of Transmit Frame Synchronization                                                         | FSX Pin Function                                                                               |

|--------------------|------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 0                  | Χ                | External frame sync input on the FSX pin. This is inverted by FSXP before being used as FSX_int. | Input.                                                                                         |

| 1                  | 1                | Sample rate generator frame sync signal (FSG) drives FSX_int. FRST = 1.                          | Output. FSG is inverted by FSXP before being driven out on FSX.                                |

| 1                  | 0                | A DXR-to-XSR copy activates transmit frame sync signal.                                          | Output. 1-bit-clock-wide signal inverted as determined by FSXP before being driven out on FSX. |

#### 2.3.4.4 Frame Detection

To facilitate detection of frame synchronization, the receive and transmit CPU interrupts (RINT and XINT) can be programmed to detect frame synchronization by setting RINTM = XINTM = 10b in the serial port control register (SPCR). The associated portion (receiver/transmitter) of the ASP must be out of reset.

#### 2.3.5 **Data and Frames**

#### 2.3.5.1 Frame Synchronization Phases

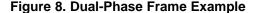

Frame synchronization indicates the beginning of a transfer on the ASP. The data stream following frame synchronization can have up to two phases, phase 1 and phase 2. The number of phases can be selected by the phase bit, (R/X)PHASE, in RCR and XCR. The number of elements per frame and bits per element can be independently selected for each phase via (R/X)FRLEN1/2 and (R/X)WDLEN1/2, respectively. Figure 8 shows a frame in which the first phase consists of two elements of 12 bits, each followed by a second phase of three elements of 8 bits each. The entire bit stream in the frame is contiguous; no gaps exist either between elements or phases. Table 7 shows the fields in the receive/transmit control registers (RCR/XCR) that control the frame length and element length for each phase for both the receiver and the transmitter. The maximum number of elements per frame is 128 for a single-phase frame and 256 elements in a dual-phase frame. The number of bits per element can be 8, 12, 16, 20, 24, or 32.

Note: For a dual-phase frame with internally generated frame synchronization, the maximum number of elements per phase depends on the word length. This is because the frame period, FPER, is only 12-bits wide and, therefore, provides 4096 bits per frame. Hence, the maximum number of 256 elements per dual- phase frame applies only when the WDLEN is 16 bits. However, any combination of element numbers and element size (defined by the FRLEN and WDLEN bits, respectively) is valid as long as their product is less than or equal to 4096 bits. This limitation does not apply for dual-phase with external frame sync.

Table 7. RCR/XCR Fields Controlling Elements per Frame and Bits per Element

|             |             | RCR/XCR Field Control |                  |  |

|-------------|-------------|-----------------------|------------------|--|

| Serial Port | Frame Phase | Elements per Frame    | Bits per Element |  |

| Receive     | 1           | RFRLEN1               | RWDLEN1          |  |

| Receive     | 2           | RFRLEN2               | RWDLEN2          |  |

| Transmit    | 1           | XFRLEN1               | XWDLEN1          |  |

| Transmit    | 2           | XFRLEN2               | XWDLEN2          |  |

#### 2.3.5.2 Frame Length: RFRLEN1/2 and XFRLEN1/2

Frame length specifies the maximum number of serial elements or logical time slots or channels that are available for transfer per frame synchronization signal. The 7-bit (R/X)FRLEN1/2 bits in (R/X)CR support up to 128 elements per phase in a frame, as shown in Table 8. (R/X)PHASE = 0 selects a single-phase data frame, and (R/X)PHASE = 1 selects a dual-phase frame for the data stream. For a single-phase frame, the value of (R/X)FRLEN2 does not matter. Program the frame length fields with (w minus 1), where w represents the number of elements per frame. For Figure 8, (R/X)FRLEN1 = 1 or 000 0001b and (R/X)FRLEN2 = 2 or 000 0010b.

Table 8. Receive/Transmit Frame Length Configuration

| (R/X)PHASE | (R/X)FRLEN1         | (R/X)FRLEN2         | Frame Length                                          |

|------------|---------------------|---------------------|-------------------------------------------------------|

| 0          | $0 \leq n \leq 127$ | x                   | Single-phase frame; (n+1) elements per frame          |

| 1          | $0 \leq n \leq 127$ | $0 \leq m \leq 127$ | Dual-phase frame; (n+1) plus (m+1) elements per frame |

#### 2.3.5.3 Element Length: RWDLEN1/2 and XWDLEN1/2

The (R/X)WDLEN1/2 fields in the receive/transmit control register (RCR and XCR) determine the element length in bits per element for the receiver and the transmitter for each phase of the frame, as indicated in Table 7. Table 9 shows how the value of these fields selects particular element lengths in bits. For the example in Figure 8, (R/X)WDLEN1 = 001b and (R/X)WDLEN2 = 000b. If (R/X)PHASE = 0, indicating a single-phase frame, (R/X)WDLEN2 is not used by the ASP and its value does not matter.

Table 9. Receive/Transmit Element Length Configuration

| (R/X)WDLEN1/2 | Element Length (Bits) |

|---------------|-----------------------|

| 000           | 8                     |

| 001           | 12                    |

| 010           | 16                    |

| 011           | 20                    |

| 100           | 24                    |

| 101           | 32                    |

| 110           | Reserved              |

| 111           | Reserved              |

#### 2.3.5.4 Data Packing Using Frame Length and Element Length

The frame length and element length can be manipulated to effectively pack data. For example, consider a situation in which four 8-bit elements are transferred in a single-phase frame, as shown in Figure 9. In this case:

- (R/X)PHASE = 0, indicating a single-phase frame

- (R/X)FRLEN1 = 000 0011b, indicating a 4-element frame

- (R/X)WDLEN1 = 000b, indicating 8-bit elements

In this example, four 8-bit data elements are transferred to and from the ASP by the CPU or the EDMA controller. Four reads of DRR and four writes of DXR are necessary for each frame.

Figure 9. Single-Phase Frame of Four 8-Bit Elements

The example in Figure 9 can also be viewed as a data stream of a single-phase frame of one 32-bit data element, as shown in Figure 10. In this case:

- (R/X)PHASE = 0, indicating a single phase frame

- (R/X)FRLEN1 = 0, indicating a 1-element frame

- (R/X)WDLEN1 = 101b, indicating 32-bit elements

In this example, one 32-bit data element is transferred to and from the ASP by the CPU or the EDMA controller. Thus, one read of DRR and one write of DXR is necessary for each frame. As a result, the number of transfers is one-fourth that of the previous example (Figure 9). This manipulation reduces the percentage of bus time required for serial port data movement.

Figure 10. Single-Phase Frame of One 32-Bit Element

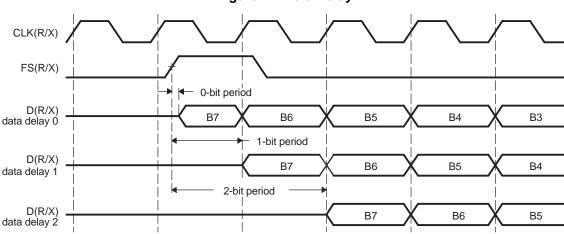

#### 2.3.5.5 Data Delay: RDATDLY and XDATDLY

The start of a frame is defined by the first clock cycle in which frame synchronization is active. The beginning of actual data reception or transmission with respect to the start of the frame can be delayed if required. This delay is called data delay. RDATDLY (in RCR) and XDATDLY (in XCR) specify the data delay for reception and transmission, respectively. The range of programmable data delay is zero to two bit clocks ((R/X)DATDLY = 00b to10b), as shown in Figure 11. Typically, a 1-bit delay is selected because data often follows a 1-cycle active frame sync pulse.

Figure 11. Data Delay

Normally a frame sync pulse is detected or sampled with respect to an edge of serial clock CLK(R/X). Thus, on a subsequent cycle (depending on data delay value), data can be received or transmitted. However, in the case of a 0-bit data delay, the data must be ready for reception and/or transmission on the same serial clock cycle. For reception, this problem is solved by receive data being sampled on the first falling edge of CLKR when an active (high) FSR is detected. However, data transmission must begin on the rising edge of CLKX that generated the frame synchronization. Therefore, the first data bit is assumed to be in the XSR and DX. The transmitter then asynchronously detects the frame synchronization, FSX goes active, and it immediately starts driving the first bit to be transmitted on the DX pin.

#### 2.3.5.6 Receive Data Justification and Sign Extension: RJUST

RJUST in SPCR selects whether data in RBR is right- or left-justified (with respect to the MSB) in the DRR. If right justification is selected, RJUST further selects whether the data is sign-extended or zero-filled. Table 10 summarizes the effect that various values of RJUST have on an example 12-bit receive data value ABCh.

|                  |               | •                |              |  |  |

|------------------|---------------|------------------|--------------|--|--|

| RJUST Bits Value | Justification | Extension        | Value in DRR |  |  |

| 00               | Right         | Zero-fill MSBs   | 0000 0ABCh   |  |  |

| 01               | Right         | Sign-extend MSBs | FFFF FABCh   |  |  |

| 10               | Left          | Zero-fill LSBs   | ABC0 0000h   |  |  |

| 11               | Reserved      | Reserved         | Reserved     |  |  |

Table 10. Effect of RJUST Bit Values With 12-Bit Example Data ABCh

Table 11. Effect of RJUST Bit Values With 20-Bit Example Data ABCDEh

| RJUST Bit<br>in SPCR | Justification | Extension        | Value in DRR |

|----------------------|---------------|------------------|--------------|

| 00                   | Right         | Zero-fill MSBs   | 000A BCDEh   |

| 01                   | Right         | Sign-extend MSBs | FFFA BCDEh   |

| 10                   | Left          | Zero-fill LSBs   | ABCD E000h   |

| 11                   | Reserved      | Reserved         | Reserved     |

#### 2.3.5.7 32-Bit Bit Reversal: RWDREVRS, XWDREVRS

Normally all transfers are sent and received with the MSB first; however, you can reverse the receive/transmit bit ordering of a 32-bit element (LSB first) using the 32-bit reversal feature of the ASP by setting all of the following:

- (R/X)WDREVRS = 1 in the receive/transmit control register (RCR/XCR).

- (R/X)COMPAND = 01b in RCR/XCR.

- (R/X)WDLEN(1/2) = 101b in RCR/XCR to indicate 32-bit elements.

When you set the register fields as above, the bit ordering of the 32-bit element is reversed before being received by or sent from the serial port. If the (R/W)WDREVRS and (R/X)COMPAND fields are set as above, but the element size is not set to 32-bit, operation is undefined.

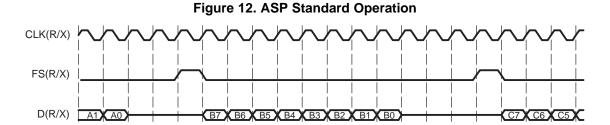

#### 2.4 ASP Standard Operation

During a serial transfer, there are typically periods of serial port inactivity between packets or transfers. The receive and transmit frame synchronization pulse occurs for every serial transfer. When the ASP is not in the reset state and has been configured for the desired operation, a serial transfer can be initiated by programming (R/X)PHASE = 0 for a single-phase frame with the required number of elements programmed in (R/X)FRLEN1. The number of elements can range from 1 to 128 ((R/X)FRLEN1 = 00h to 7Fh). The required serial element length is set in the (R/X)WDLEN1 field in the (R/X)CR. If a dual-phase frame is required for the transfer, RPHASE = 1 and each (R/X)FRLEN1/2 can be set to any value between 0h and 7Fh.

Figure 12 shows a single-phase data frame of one 8-bit element. Since the transfer is configured for a 1-bit data delay, the data on the DX and DR pins are available one bit clock after FS(R/X) goes active. This figure, as well as all others in this section, use the following assumptions:

- (R/X)PHASE = 0, specifying a single-phase frame

- (R/X)FRLEN1 = 0b, specifying one element per frame

- (R/X)WDLEN1 = 000b, specifying eight bits per element

- (R/X)FRLEN2 = (R/X)WDLEN2 = Value is ignored

- CLK(R/X)P = 0, specifying that the receive data is clocked on the falling edge and that transmit data is clocked on the rising edge

- FS(R/X)P = 0, specifying that active (high) frame sync signals are used

- (R/X)DATDLY = 01b, specifying a 1-bit data delay

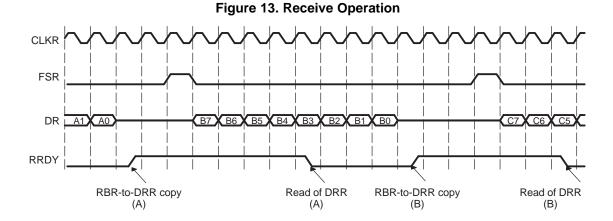

#### 2.4.1 Receive Operation

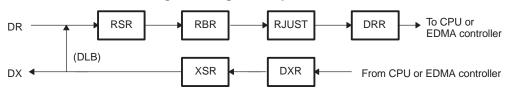

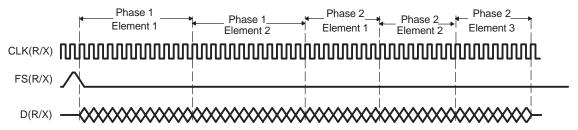

Figure 13 shows serial reception. Once the receive frame synchronization signal (FSR) transitions to its active state, it is detected on the first falling edge of the receivers CLKR. The data on the DR pin is then shifted into the receive shift register (RSR) after the appropriate data delay as set by RDATDLY. The contents of RSR is copied to RBR at the end of every element on the rising edge of the clock, provided RBR is not full with the previous data. Then, an RBR-to-DRR copy activates the RRDY status bit to 1 on the following falling edge of CLKR. This indicates that the receive data register (DRR) is ready with the data to be read by the CPU or the EDMA controller. RRDY is deactivated when the DRR is read by the CPU or the EDMA controller. See also Section 2.9.1.2 and Section 2.10.1.

### 2.4.2 Transmit Operation

Once transmit frame synchronization occurs, the value in the transmit shift register (XSR) is shifted out and driven on the DX pin after the appropriate data delay as set by XDATDLY. XRDY is activated after every DXR-to-XSR copy on the following falling edge of CLKX, indicating that the data transmit register (DXR) can be written with the next data to be transmitted. XRDY is deactivated when the DXR is written by the CPU or the EDMA controller. Figure 14 illustrates serial transmission. See Section 2.4.5.4 for information on transmit operation when the transmitter is pulled out of reset (XRST = 1). See also Section 2.9.1.3 and Section 2.10.2.

#### 2.4.3 Maximum Frame Frequency

The frame frequency is determined by the following equation, which calculates the period between frame synchronization signals:

Frame frequency =

$$\frac{Bit\text{-}clock frequency}{Number of bit clocks between frame sync signals}$$

The frame frequency may be increased by decreasing the time between frame synchronization signals in bit clocks (which is limited only by the number of bits per frame). As the frame transmit frequency is increased, the inactivity period between the data frames for adjacent transfers decreases to 0. The minimum time between frame synchronization pulses is the number of bits transferred per frame. This time also defines the maximum frame frequency, which is calculated by the following equation:

Maximum frame frequency =

$$\frac{Bit\text{-}clock frequency}{Number of bits per frame}$$

Figure 15 shows the ASP operating at maximum frame frequency. The data bits in consecutive frames are transmitted continuously with no inactivity between bits. If there is a 1-bit data delay, as shown, the frame synchronization pulse overlaps the last bit transmitted in the previous frame.

Figure 15. Maximum Frame Frequency for Transmit and Receive

**Note:** For (R/X)DATDLY = 0, the first bit of data transmitted is asynchronous to CLKX, as shown in Figure 11.

**Note:** Maximum frame frequency may not be possible when the word length is 8-bits, depending on the the clock divide value CLKGDV. The CPU or EDMA may not be able to service serial port requests that occur as frequently as every 8 bit clocks. This situation can be resolved by allowing additional space between words or choosing a slower bit clock (larger CLKGDV value).

#### 2.4.4 Frame Synchronization Ignore

The ASP can be configured to ignore transmit and receive frame synchronization pulses. The (R/X)FIG bit in (R/X)CR can be cleared to 0 to recognize frame sync pulses, or it can be set to 1 to ignore frame sync pulses. In this way, you can use (R/X)FIG either to pack data, if operating at maximum frame frequency, or to ignore unexpected frame sync pulses.

#### 2.4.4.1 Frame Sync Ignore and Unexpected Frame Sync Pulses

RFIG and XFIG are used to ignore unexpected internal or external frame sync pulses. Any frame sync pulse is considered unexpected if it occurs one or more bit clocks earlier than the programmed data delay from the end of the previous frame specified by ((R/X)DATDLY). Setting the frame ignore bits to 1 causes the serial port to ignore these unexpected frame sync signals.

In reception, if not ignored (RFIG = 0), an unexpected FSR pulse discards the contents of RSR in favor of the incoming data. Therefore, if RFIG = 0, an unexpected frame synchronization pulse aborts the current data transfer, sets RSYNCERR in SPCR to 1, and begins the reception of a new data element. When RFIG = 1, the unexpected frame sync pulses are ignored.

In transmission, if not ignored (XFIG = 0), an unexpected FSX pulse aborts the ongoing transmission, sets the XSYNCERR bit in SPCR to 1, and reinitiates transmission of the current element that was aborted. When XFIG = 1, unexpected frame sync signals are ignored.

Figure 16 shows that element B is interrupted by an unexpected frame sync pulse when (R/X)FIG = 0. The reception of B is aborted (B is lost), and a new data element ) is received after the appropriate data delay. This condition causes a receive synchronization error and thus sets the RSYNCERR bit. However, for transmission, the transmission of B is aborted and the same data (B) is retransmitted after the appropriate data delay. This condition is a transmit synchronization error and thus sets the XSYNCERR bit. Synchronization errors are discussed in Section 2.4.5.2 and Section 2.4.5.5.

Figure 16. Unexpected Frame Synchronization With (R/X)FIG = 0

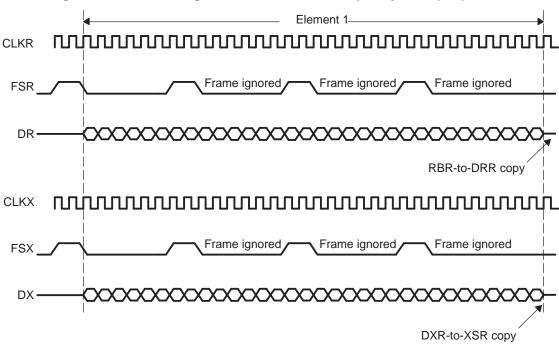

Figure 17 shows ASP operation when unexpected internal or external frame synchronization signals are ignored by setting (R/X)FIG = 1. Here, the transfer of element B is not affected by an unexpected frame synchronization.

Figure 17. Unexpected Frame Synchronization With (R/X)FIG = 1

#### 2.4.4.2 Data Packing using Frame Sync Ignore Bits

Section 2.3.5.4 describes one method of changing the element length and frame length to simulate 32-bit serial element transfers, thus requiring much less bus bandwidth than four 8-bit transfers require. This example works when there are multiple elements per frame.

Now consider the case of the ASP operating at maximum packet frequency, as shown in Figure 18. Here, each frame has only a single 8-bit element. This stream takes one read transfer and one write transfer for each 8-bit element. Figure 19 shows the ASP configured to treat this stream as a continuous stream of 32-bit elements. In this example, (R/X)FIG is set to 1 to ignore unexpected subsequent frames. Only one read transfer and one write transfer is needed every 32-bits. This configuration effectively reduces the required bus bandwidth to one-fourth of the bandwidth needed to transfer four 8-bit blocks.

Figure 18. Maximum Frame Frequency Operation With 8-Bit Data

Figure 19. Data Packing at Maximum Frame Frequency With (R/X)FIG = 1

#### 2.4.5 Serial Port Exception Conditions

There are five serial port events that can constitute a system error:

- Receive overrun (RFULL = 1)

- Unexpected receive frame synchronization (RSYNCERR = 1)

- · Transmit data overwrite

- Transmit empty (XEMPTY = 0)

- Unexpected transmit frame synchronization (XSYNCERR = 1)

#### 2.4.5.1 Receive Overrun: RFULL

RFULL = 1 in the serial port control register (SPCR) indicates that the receiver has experienced overrun and is in an error condition. RFULL is set when the following conditions are met:

- DRR has not been read since the last RBR-to-DRR transfer.

- RBR is full and an RBR-to-DRR copy has not occurred.

- RSR is full and an RSR-to-RBR transfer has not occurred.

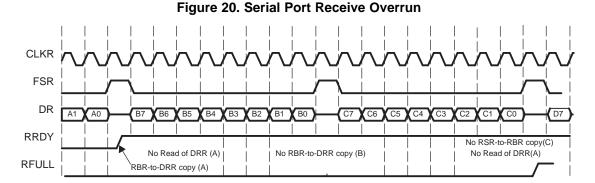

The data arriving on DR is continuously shifted into RSR (Figure 20). Once a complete element is shifted into RSR, an RSR-to-RBR transfer can occur only if an RBR-to-DRR copy is complete. Therefore, if DRR has not been read by the CPU or the EDMA controller since the last RBR-to-DRR transfer (RRDY = 1), an RBR-to-DRR copy does not take place until RRDY = 0. This prevents an RSR-to-RBR copy. New data arriving on the DR pin is shifted into RSR, and the previous contents of RSR are lost. After the receiver starts running from reset, a minimum of three elements must be received before RFULL can be set, because there was no last RBR-to-DRR transfer before the first element.

This data loss can be avoided if DRR is read no later than two and a half CLKR cycles before the end of the third element (data C) in RSR, as shown in Figure 21.

Either of the following events clears the RFULL bit to 0 and allows subsequent transfers to be read properly:

- Reading DRR

- Resetting the receiver (RRST = 0) or the device

CLKR FSR

DR

**RRDY**

**RFULL**

Α1

Another frame synchronization is required to restart the receiver.

No Read of DRR (A)

RBR-to-DRR copy (A)

Figure 20 shows the receive overrun condition. Because element A is not read before the reception of element B is complete, B is not transferred to DRR yet. Another element, C, arrives and fills RSR. DRR is finally read, but not earlier than two and one half cycles before the end of element C. New data D overwrites the previous element C in RSR. If RFULL is still set after the DRR is read, the next element can overwrite D if DRR is not read in time.

Figure 21 shows the case in which RFULL is set but the overrun condition is averted by reading the contents of DRR at least two and a half cycles before the next element, C, is completely shifted into RSR. This ensures that a RBR-to-DRR copy of data B occurs before the next element is transferred from RSR to RBR.

Figure 21. Serial Port Receive Overrun Avoided

A0 B7 X B6 X B5 X B4 X B3 X B2 X B1 X B0 C7 X C6 X C5 X C4 X C3 X C2 X C1 X C0

No RBR-to-DRR copy (B)

Read of DRR (A)

RBR-to-DRR (B)

#### 2.4.5.2 Unexpected Receive Frame Synchronization: RSYNCERR

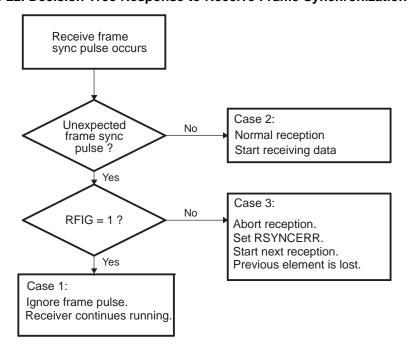

Figure 22 shows the decision tree that the receiver uses to handle all incoming frame synchronization pulses. The diagram assumes that the receiver has been activated (RRST = 1). Unexpected frame sync pulses can originate from an external source or from the internal sample rate generator. An unexpected frame sync pulse is defined as a sync pulse which occurs RDATDLY bit clocks earlier than the last transmitted bit of the previous frame. Any one of three cases can occur:

- Case 1: Unexpected FSR pulses with RFIG = 1. This case is discussed in Section 2.4.4.1 and shown

in Figure 17. Here, receive frame sync pulses are ignored and the reception continues.

- Case 2: Normal serial port reception. There are three reasons for a receive not to be in progress:

- This FSR is the first after RRST = 1.

- This FSR is the first after DRR has been read clearing an RFULL condition.

- The serial port is in the inter-packet intervals. The programmed data delay (RDATDLY) for reception may start during these inter-packet intervals for the first bit of the next element to be received. Thus, at maximum frame frequency, frame synchronization can still be received RDATDLY bit clocks before the first bit of the associated element.

For this case, reception continues normally, because these are not unexpected frame sync pulses.

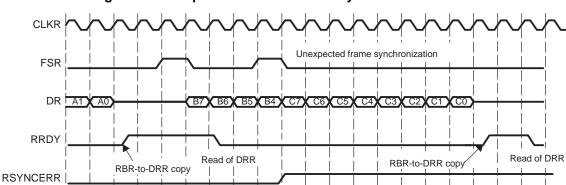

• Case 3: Unexpected receive frame synchronization with RFIG = 0 (unexpected frame not ignored). This case was shown in Figure 16 for maximum packet frequency. Figure 23 shows this case during normal operation of the serial port with time intervals between packets. Unexpected frame sync pulses are detected when they occur the value in RDATDLY bit clocks before the last bit of the previous element is received on DR. In both cases, RSYNCERR in SPCR is set. RSYNCERR can be cleared only by receiver reset or by writing a 0 to this bit in SPCR. If RINTM = 11b in SPCR, RSYNCERR drives the receive interrupt (RINT) to the CPU.

**Note:** Note that the RSYNCERR bit in SPCR is a read/write bit, so writing a 1 to it sets the error condition. Typically, writing a 0 is expected.

Figure 22. Decision Tree Response to Receive Frame Synchronization Pulse

Figure 23. Unexpected Receive Frame Synchronization Pulse

#### 2.4.5.3 Transmit With Data Overwrite

Figure 24 shows what happens if the data in DXR is overwritten before it is transmitted. Suppose you load the DXR with data C. A subsequent write to the DXR overwrites C with D before C is copied to the XSR. Thus, C is never transmitted on DX. The CPU can avoid overwriting data by polling XRDY before writing to DXR or by waiting for a programmed XINT to be triggered by XRDY (XINTM = 00b). The EDMA controller can avoid overwriting by synchronizing data writes with XEVT. See also Section 2.9.1.3.

Figure 24. Transmit With Data Overwrite

#### 2.4.5.4 Transmit Empty: XEMPTY

XEMPTY indicates whether the transmitter has experienced underflow. Either of the following conditions causes XEMPTY to become active (XEMPTY = 0):

- During transmission, DXR has not been loaded since the last DXR-to-XSR copy, and all bits of the data element in XSR have been shifted out on DX.

- The transmitter is reset (XRST = 0 or the device is reset), and then restarted.

During underflow condition, the transmitter continues to transmit the old data in DXR for every new frame sync signal FSX (generated by an external device, or by the internal sample rate generator) until a new element is loaded into DXR by the CPU or the EDMA controller. XEMPTY is deactivated (XEMPTY = 1) when this new element in DXR is transferred to XSR. In the case when the FSX is generated by a DXR-to-XSR copy (FSXM = 1 in PCR and FSGM = 0 in SRGR), the ASP does not generate any new frame sync until new data is written to the DXR and a DXR-to-XSR copy occurs.

When the transmitter is taken out of reset (XRST = 1), it is in a transmit ready (XRDY = 1) and transmit empty (XEMPTY = 0) condition. If DXR is loaded by the CPU or the EDMA controller before FSX goes active, a valid DXR-to-XSR transfer occurs. This allows for the first element of the first frame to be valid even before the transmit frame sync pulse is generated or detected. Alternatively, if a transmit frame sync is detected before DXR is loaded, 0s are output on DX.

Figure 25 shows a transmit underflow condition. After B is transmitted, B is retransmitted on DX if you fail to reload the DXR before the subsequent frame synchronization. Figure 26 shows the case of writing to DXR just before a transmit underflow condition that would otherwise occur. After B is transmitted, C is written to DXR before the next transmit frame sync pulse occurs.

#### 2.4.5.5 Unexpected Transmit Frame Synchronization: XSYNCERR

A transmit frame sync error (XSYNCERR) may occur the first time the transmitter is enabled (XRST = 1) after a device reset. To avoid this, after enabling the transmitter for the first time, the following procedure must be followed:

- 1. Wait for two CLKG cycles. The unexpected frame sync error (XSYNCERR), if any, occurs within this time period.

- 2. Disable the transmitter (XRST = 0). This clears any XSYNCERR.

- 3. Re-enable the transmitter (XRST = 1).

See also Section 2.7 for details on initialization procedure.

Figure 27 shows the decision tree that the transmitter uses to handle all incoming frame synchronization signals. The diagram assumes that the transmitter has been started (XRST = 1). An unexpected transmit frame sync pulse is defined as a sync pulse that occurs XDATDLY bit clocks earlier than the last transmitted bit of the previous frame. Any one of three cases can occur:

- Case 1: Unexpected FSX pulses with XFIG = 1. This case is discussed in Section 2.4.4.1 and shown in Figure 17. In this case, unexpected FSX pulses are ignored, and the transmission continues.

- Case 2: FSX pulses with normal serial port transmission. This situation is discussed in Section 2.4.2.

There are two possible reasons for a transmit not to be in progress:

- This FSX pulse is the first one to occur after XRST = 1.

- The serial port is in the interpacket intervals. The programmed data delay (XDATDLY) may start during these interpacket intervals before the first bit of the next element is transmitted. Thus, if operating at maximum packet frequency, frame synchronization can still be received XDATDLY bit clocks before the first bit of the associated element.

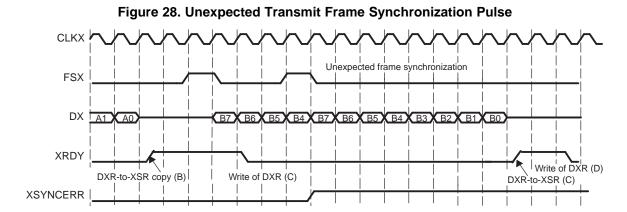

- Case 3: Unexpected transmit frame synchronization with XFIG = 0. The case was shown in Figure 16 for frame synchronization with XFIG = 0 at maximum packet frequency. Figure 28 shows the case for normal operation of the serial port with interpacket intervals. In both cases, XSYNCERR in SPCR is set. XSYNCERR can be cleared only by transmitter reset or by writing a 0 to this bit in SPCR. If XINTM = 11b in SPCR, XSYNCERR drives the receive interrupt (XINT) to the CPU.

**Note:** The XSYNCERR bit in SPCR is a read/write bit, so writing a 1 to it sets the error condition. Typically, writing a 0 is expected.

Figure 27. Decision Tree Response to Transmit Frame Synchronization Pulse

Audio Serial Port (ASP) Interface

## 2.5 -Law/A-Law Companding Hardware Operation

Companding (compressing and expanding) hardware allows compression and expansion of data in either -law or A-law format. The specification for -law and A-law log PCM is part of the CCITT G.711 recommendation. The companding standard employed in the United States and Japan is -law and allows 14 bits of dynamic range. The European companding standard is A-law and allows 13 bits of dynamic range. Any values outside these ranges are set to the most positive or most negative value. Thus, for companding to work best here, the data transferred to and from the ASP via the CPU or the EDMA controller must be at least 16 bits wide.

The -law and A-law formats encode data into 8-bit code elements. Companded data is always 8-bits-wide, so the appropriate (R/X)WDLEN1/2 must be cleared to 0, indicating an 8-bit serial data stream. If companding is enabled and either phase of the frame does not have an 8-bit element length, companding continues as if the element length is eight bits.

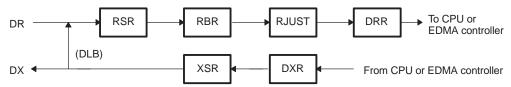

When companding is used, transmit data is encoded according to the specified companding law, and receive data is decoded to 2s-complement format. Companding is enabled and the desired format is selected by appropriately setting (R/X)COMPAND in the (R/X)CR. Compression occurs during the process of copying data from DXR to XSR and expansion occurs from RBR to DRR, as shown in Figure 29.

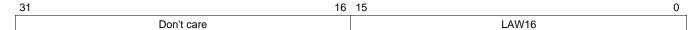

For transmit data to be compressed, it should be 16-bit, left-justified data, such as LAW16, as shown in Figure 30. The value can be either 13 or 14 bits wide, depending on the companding law. This 16-bit data is aligned in DXR, as shown in Figure 31.

For reception, the 8-bit compressed data in RBR is expanded to a left-justified 16-bit data, LAW16. This can be further justified to 32-bit data by programming the RJUST bits in SPCR, as shown in Table 12.

RSR RBR /8 Expand /16 RJUST /32 DRR To CPU/DMA

DX XSR 8 Compress DXR From CPU/DMA

Figure 29. Companding Flow

Figure 30. Companding Data Formats

| LAW16 | 15    | 2 | 1 | 0 |

|-------|-------|---|---|---|

| -Law  | Value |   | 0 | 0 |

| LAW16 | 15 3  | 2 | 1 | 0 |

| A-Law | Value | 0 | 0 | 0 |

Figure 31. Transmit Data Companding Format in DXR

Table 12. Justification of Expanded Data in DRR

| _     |     | DRR | R Bits |     |

|-------|-----|-----|--------|-----|

| RJUST | 31  | 16  | 15     | 0   |

| 00    | (   | 0   | LA     | W16 |

| 01    | si  | gn  | LA     | W16 |

| 10    | LAV | N16 |        | 0   |

| 11    |     | Res | erved  |     |

### 2.5.1 Companding Internal Data

If the ASP is unused, the companding hardware can compand internal data. This hardware can be used to:

- Convert linear data to the appropriate -law or A-law format.

- · Convert -law or A-law data to the linear format.

- Observe the quantization effects in companding by transmitting linear data and compressing and re-expanding this data. This is useful only if both XCOMPAND and RCOMPAND enable the same companding format.

Figure 32 shows two methods by which the ASP can compand internal data. Data paths for these two methods are indicated by (DLB) and (non-DLB) arrows.

- Non-DLB: When both the transmit and receive sections of the serial port are reset, DRR and DXR are internally connected through the companding logic. Values from DXR are compressed as determined by the XCOMPAND bits and then expanded as determined by the RCOMPAND bits. RRDY and XRDY bits are not set. However, data is available in DRR four internal ASP clocks after being written to DXR. The advantage of this method is its speed. The disadvantage is that there is no synchronization available to the CPU and the EDMA controller to control the flow of data.

- **DLB:** The ASP is enabled in digital loopback (DLB) mode with companding appropriately enabled by the RCOMPAND and XCOMPAND bits. Receive and transmit interrupts (RINT when RINTM = 0 and XINT when XINTM = 0) or synchronization events (REVT and XEVT) allow synchronization of the CPU or the EDMA controller to these conversions, respectively. Here, the time for this companding depends on the serial bit rate selected.

Figure 32. Companding of Internal Data

## 2.5.2 Bit Ordering

Normally, all transfers on the ASP are sent and received with the MSB first. However, certain 8-bit data protocols (that do not use companded data) require the LSB to be transferred first. By setting the (R/X)COMPAND = 01b in (R/X)CR, the bit ordering of 8-bit elements is reversed (LSB first) before being sent to the serial port. Like the companding feature, this feature is enabled only if the appropriate (R/X)WDLEN1/2 bit is cleared to 0, indicating that 8-bit elements are to be serially transferred.

**Note:** A 32-bit reversal feature is also available. See Section 2.3.5.7.

## 2.6 Resetting the Serial Port: RRST, XRST, GRST, and RESET