# TMS320DM646x DMSoC Universal Asynchronous Receiver/Transmitter (UART)

# **User's Guide**

Literature Number: SPRUER6D May 2009

## Contents

| Pref | ace     |                                           | 9         |

|------|---------|-------------------------------------------|-----------|

| 1    | Introdu | ction                                     | 10        |

|      | 1.1     | Purpose of the Peripheral                 | 10        |

|      | 1.2     | Features                                  | 10        |

|      | 1.3     | Functional Block Diagram                  | 11        |

|      | 1.4     | Application Example                       | 12        |

|      | 1.5     | Industry Standard Compatibility Statement | 12        |

| 2    | Archite | cture                                     | 13        |

|      | 2.1     | Clock Control                             | 13        |

|      | 2.2     | Signal Descriptions                       | 13        |

|      | 2.3     | Pin Multiplexing                          | 14        |

|      | 2.4     | Modes of Operation                        | 14        |

|      | 2.5     | Functional Description                    | 23        |

|      | 2.6     | Interrupt and EDMA Event Assignment       | 35        |

|      | 2.7     | UART Bootloader                           | 35        |

|      | 2.8     | Power Management                          | 36        |

|      | 2.9     | Programming Examples                      | 36        |

|      | 2.10    | Reset Considerations                      | 38        |

|      | 2.11    | Emulation Considerations                  | 38        |

| 3    | Registe | ers                                       | 38        |

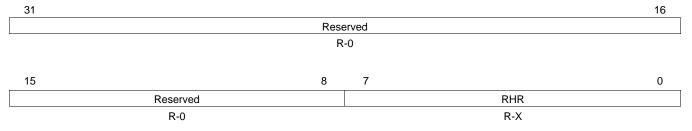

|      | 3.1     | Receive Holding Register (RHR)            | 41        |

|      | 3.2     | Transmit Holding Register (THR)           | 42        |

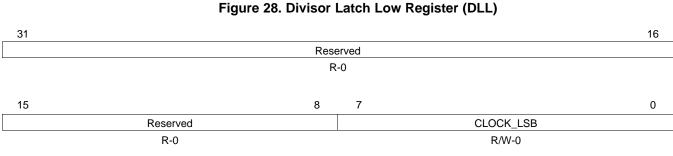

|      | 3.3     | Divisor Latch Low Register (DLL)          | 43        |

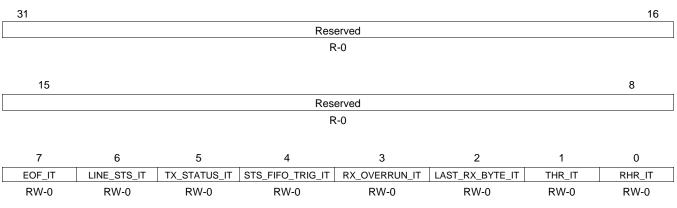

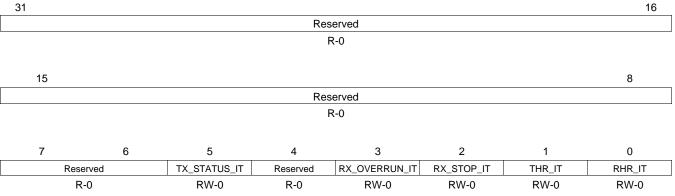

|      | 3.4     | Interrupt Enable Register (IER)           | 44        |

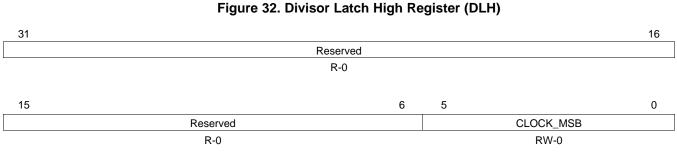

|      | 3.5     | Divisor Latch High Register (DLH)         | 49        |

|      | 3.6     | Interrupt Identification Register (IIR)   | 50        |

|      | 3.7     | FIFO Control Register (FCR)               | 54        |

|      | 3.8     | Enhanced Feature Register (EFR)           | 56        |

|      | 3.9     | Line Control Register (LCR)               | <b>58</b> |

|      | 3.10    | Modem Control Register (MCR)              | 59        |

|      | 3.11    | XON1 Character Register (XON1)            | <b>60</b> |

|      | 3.12    | Line Status Register (LSR)                | 61        |

|      | 3.13    | XON2 Character Register (XON2)            |           |

|      | 3.14    | Modem Status Register (MSR)               |           |

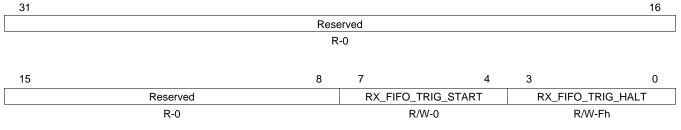

|      | 3.15    | Transmission Control Register (TCR)       |           |

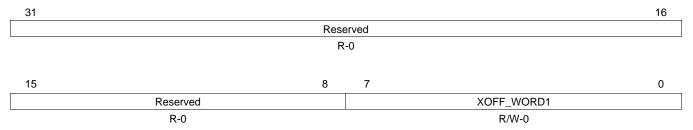

|      | 3.16    | XOFF1 Character Register (XOFF1)          | 68        |

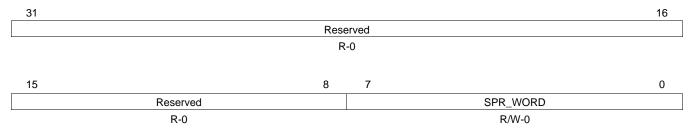

|      | 3.17    | Scratchpad Register (SPR)                 |           |

|      | 3.18    | Trigger Level Register (TLR)              |           |

|      | 3.19    | XOFF2 Character Register (XOFF2)          |           |

|      | 3.20    | Mode Definition Register 1 (MDR1)         |           |

|      | 3.21    | Mode Definition Register 2 (MDR2)         | 73        |

| 3.22       | Status FIFO Line Status Register (SFLSR)    | 74 |

|------------|---------------------------------------------|----|

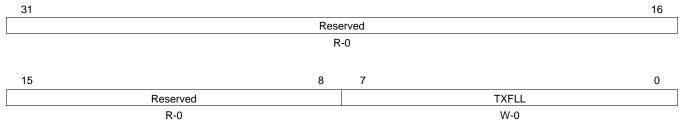

| 3.23       | Transmit Frame Length Low Register (TXFLL)  | 75 |

| 3.24       | RESUME Register (RESUME)                    | 76 |

| 3.25       | Transmit Frame Length High Register (TXFLH) | 77 |

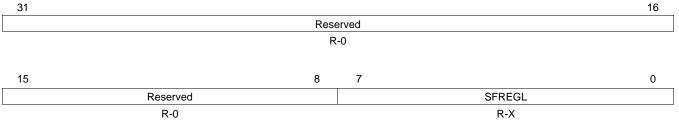

| 3.26       | Status FIFO Low Register (SFREGL)           | 78 |

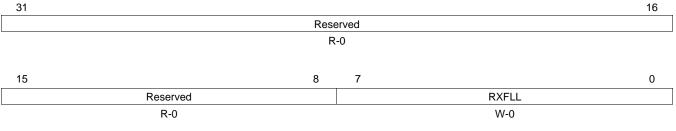

| 3.27       | Receive Frame Length Low Register (RXFLL)   | 79 |

| 3.28       | Status FIFO High Register (SFREGH)          | 80 |

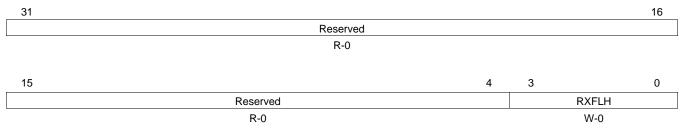

| 3.29       | Receive Frame Length High Register (RXFLH)  | 81 |

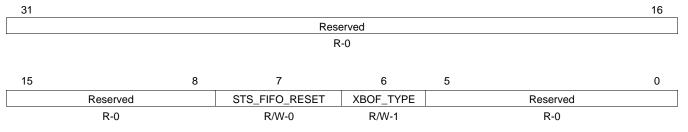

| 3.30       | Begin Of Frame Control Register (BLR)       | 82 |

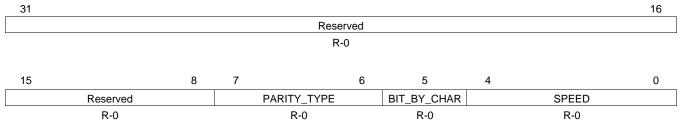

| 3.31       | UART Autobauding Status Register (UASR)     | 83 |

| 3.32       | Auxiliary Control Register (ACREG)          | 85 |

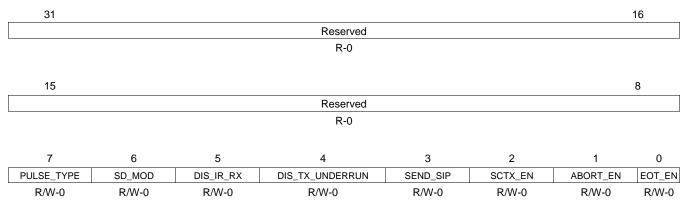

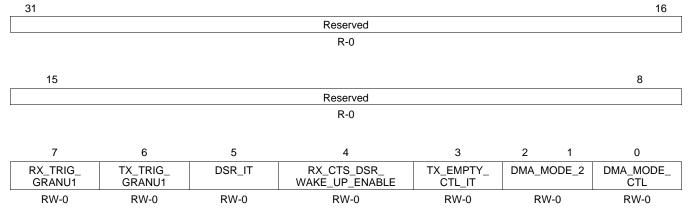

| 3.33       | Supplementary Control Register (SCR)        | 86 |

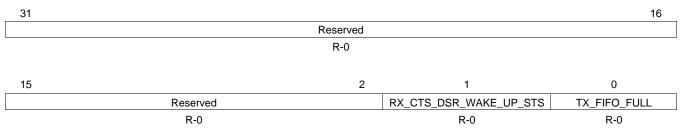

| 3.34       | Supplementary Status Register (SSR)         | 87 |

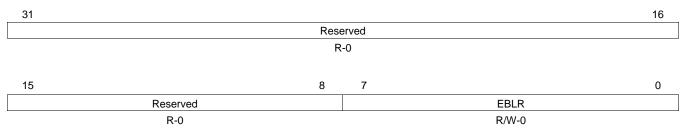

| 3.35       | Begin Of Frame Length Register (EBLR)       | 88 |

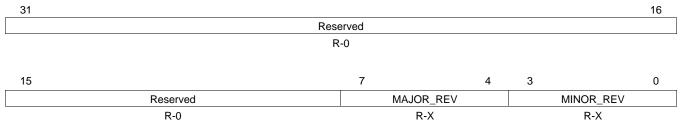

| 3.36       | Module Version Register (MVR)               | 89 |

| 3.37       | System Configuration Register (SYSC)        | 90 |

| 3.38       | System Status Register (SYSS)               | 91 |

| 3.39       | Wake-Up Enable Register (WER)               | 92 |

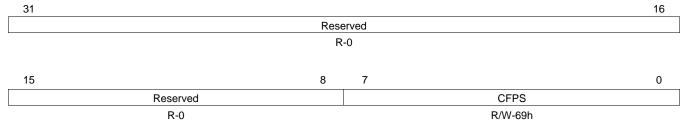

| 3.40       | Carrier Frequency Prescaler Register (CFPS) |    |

| Appendix A | Revision History                            | 94 |

|            |                                             |    |

## List of Figures

| 1        | UART Block Diagram                                          |    |

|----------|-------------------------------------------------------------|----|

| 2        | UART Modem Application Example                              | 12 |

| 3        | UART IrDA Application Example                               | 12 |

| 4        | UART CIR Application Example                                |    |

| 5        | UART Data Format                                            | 14 |

| 6        | IrDA SIR Frame Format                                       | 15 |

| 7        | SIR Free Format Mode                                        | 16 |

| 8        | MIR Transmit Frame Format                                   | 17 |

| 9        | SIP Pulse                                                   | 17 |

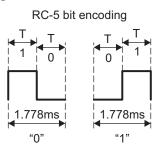

| 10       | RC-5 Bit Encoding                                           | 18 |

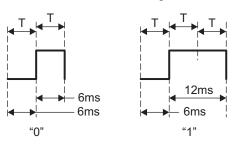

| 11       | SIRC Bit Encoding                                           | 18 |

| 12       | RC-5 Standard Packet Format                                 | 19 |

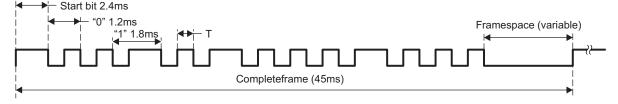

| 13       | SIRC Packet Format                                          | 19 |

| 14       | SIRC BIT Transmission Example                               | 19 |

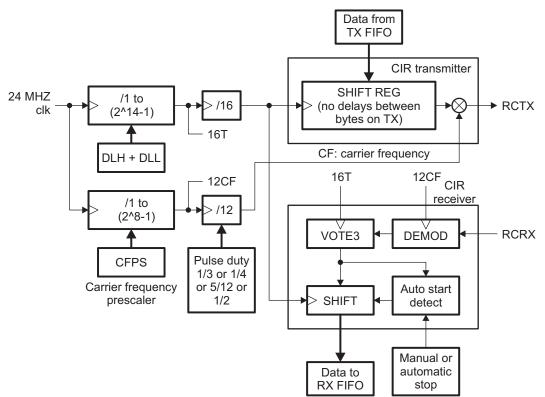

| 15       | CIR Mode Block Components                                   | 20 |

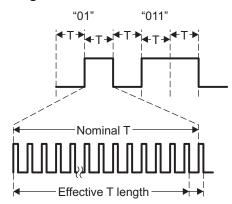

| 16       | CIR Pulse Modulation                                        | 21 |

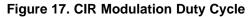

| 17       | CIR Modulation Duty Cycle                                   | 22 |

| 18       | Variable Pulse Duration Definitions                         |    |

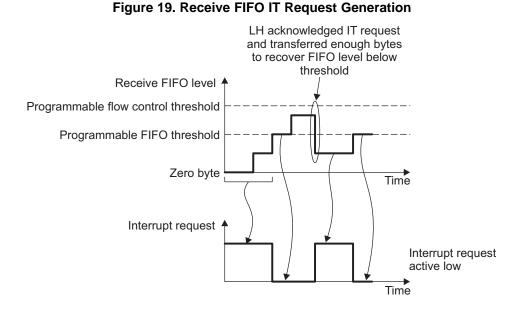

| 19       | Receive FIFO IT Request Generation                          |    |

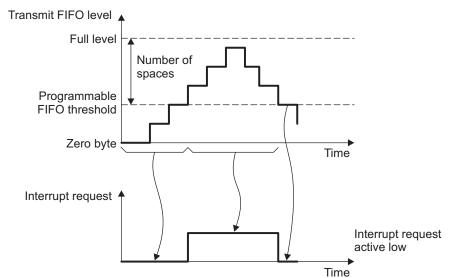

| 20       | Transmit FIFO IT Request Generation                         |    |

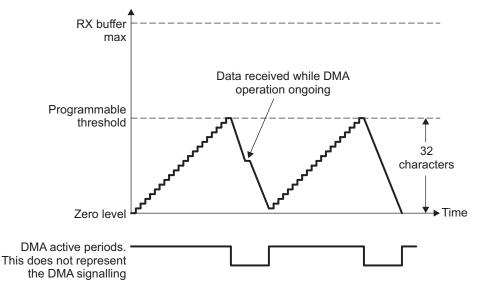

| 21       | Receive FIFO DMA Request Generation (32 chars)              |    |

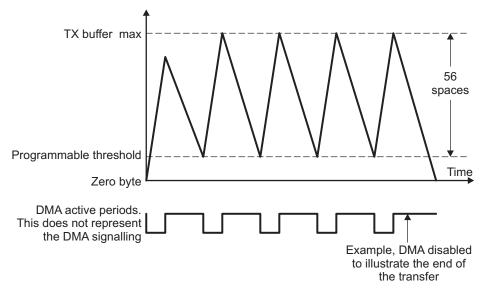

| 22       | Transmit FIFO DMA Request Generation (56 spaces)            |    |

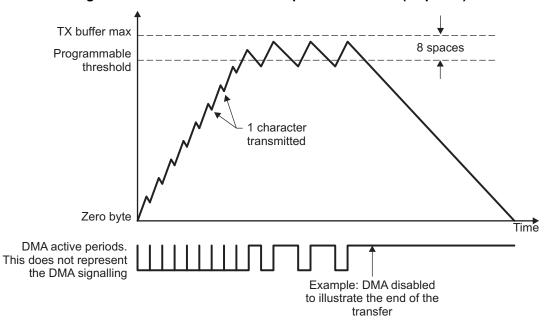

| 23       | Transmit FIFO DMA Request Generation (8 spaces)             |    |

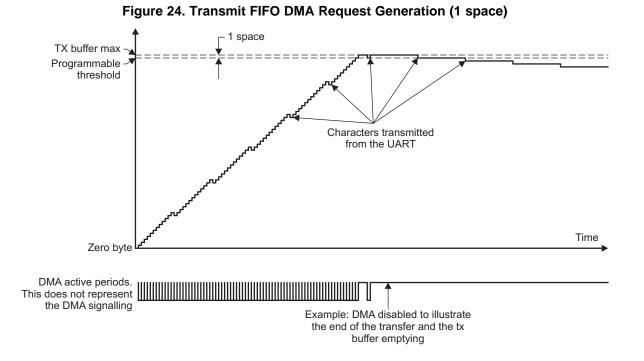

| 24       | Transmit FIFO DMA Request Generation (1 space)              |    |

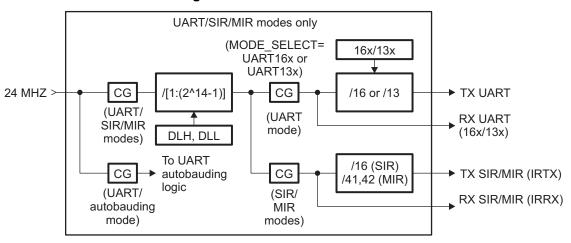

| 25       | BAUD Rate Generator                                         |    |

| 26       | Receive Holding Register (RHR)                              |    |

| 27       | Transmit Holding Register (THR)                             |    |

| 28       | Divisor Latch Low Register (DLL)                            |    |

| 29       | Interrupt Enable Register UART Mode (IER-UART Mode)         |    |

| 30       | Interrupt Enable Register IrDA Mode (IER-IrDA Mode)         |    |

| 31       | Interrupt Enable Register CIR Mode (IER-CIR Mode)           |    |

| 32       | Divisor Latch High Register (DLH)                           |    |

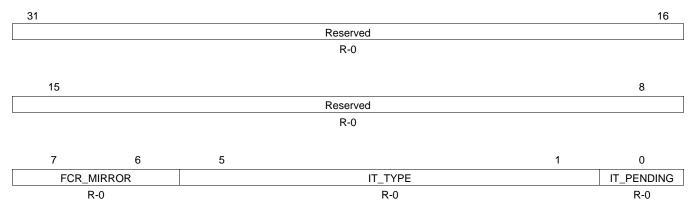

| 33       | Interrupt Identification Register UART Mode (IIR-UART Mode) |    |

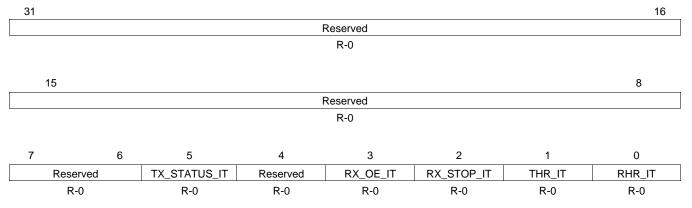

| 34       | Interrupt Identification Register IrDA Mode (IIR-IrDA mode) |    |

| 35       | Interrupt Identification Register CIR Mode (IIR-CIR mode)   |    |

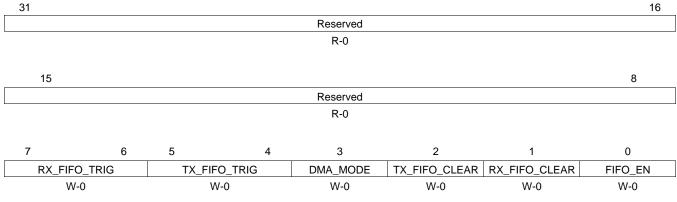

| 36       | FIFO Control Register (FCR)                                 |    |

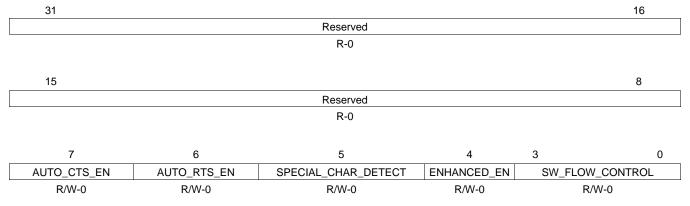

| 37       | Enhanced Feature Register (EFR)                             |    |

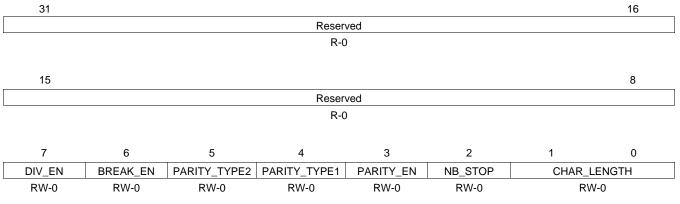

| 38       | Line Control Register (LCR)                                 |    |

| 39       | Modem Control Register (MCR)                                |    |

| 40       | XON1 Character Register (XON1)                              |    |

| 41       | Line Status Register UART Mode (LSR-UART Mode)              |    |

| 42       | Line Status Register IrDA Mode (LSR-IrDA Mode)              |    |

| 43       | Line Status Register CIR Mode (LSR-CIR Mode)                |    |

| 44       | XON2 Character Register (XON2)                              |    |

| 45       | Modem Status Register (MSR)                                 |    |

| 46       | Transmission Control Register (TCR)                         |    |

| 40<br>47 | XOFF1 Character Register (XOFF1)                            |    |

| 48       | Scratchpad Register (SPR)                                   |    |

| 40<br>49 | Trigger Level Register (TLR)                                |    |

| 49<br>50 | XOFF2 Character Register (XOFF2)                            |    |

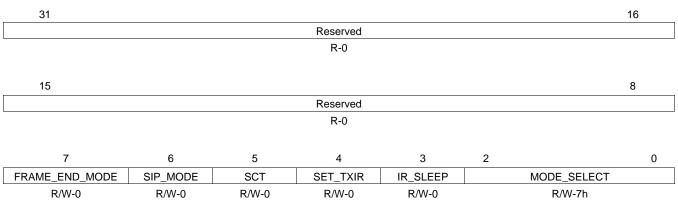

| 50<br>51 | Mode Definition Register 1 (MDR1)                           |    |

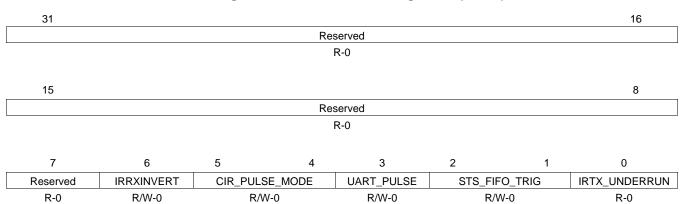

| 52       | Mode Definition Register 2 (MDR2).                          |    |

| 52       |                                                             | 13 |

| 53 | Status FIFO Line Status Register (SFLSR)    | 74 |

|----|---------------------------------------------|----|

| 54 | Transmit Frame Length Low Register (TXFLL)  | 75 |

| 55 | RESUME Register (RESUME)                    |    |

| 56 | Transmit Frame Length High Register (TXFLH) |    |

| 57 | Status FIFO Low Register (SFREGL)           |    |

| 58 | Receive Frame Length Low Register (RXFLL)   |    |

| 59 | Status FIFO High Register (SFREGH)          |    |

| 60 | Receive Frame Length High Register (RXFLH)  |    |

| 61 | Begin Of Frame Control Register (BLR)       | 82 |

| 62 | UART Autobauding Status Register (UASR)     |    |

| 63 | Auxiliary Control Register (ACREG)          | 85 |

| 64 | Supplementary Control Register (SCR)        | 86 |

| 65 | Supplementary Status Register (SSR)         | 87 |

| 66 | Begin Of Frame Length Register (EBLR)       | 88 |

| 67 | Module Version Register (MVR)               |    |

| 68 | System Configuration Register (SYSC)        | 90 |

| 69 | System Status Register (SYSS)               |    |

| 70 | Wake-Up Enable Register (WER)               |    |

| 71 | Carrier Frequency Prescaler Register (CFPS) | 93 |

|    |                                             |    |

TEXAS INSTRUMENTS

#### www.ti.com

## List of Tables

| 1        | Signal Descriptions                                          |    |

|----------|--------------------------------------------------------------|----|

| 2        | CIR Modulation Duty Cycle                                    | 21 |

| 3        | UART Mode Interrupts                                         | 23 |

| 4        | IrDA Mode Interrupts                                         | 24 |

| 5        | CIR Mode Interrupts                                          | 24 |

| 6        | UART BAUD Rate Settings (24 MHz clock)                       | 32 |

| 7        | IrDA BAUD Rate Settings (24 MHz clock)                       | 32 |

| 8        | UART Interrupts                                              | 35 |

| 9        | UART EDMA Events                                             | 35 |

| 10       | UART Reset                                                   | 36 |

| 11       | UART FIFO Configuration                                      | 36 |

| 12       | UART Baud Rate Configuration - Modem Mode                    | 37 |

| 13       | UART Baud Rate Configuration - SIR Mode                      | 37 |

| 14       | UART Baud Rate Configuration - CIR Mode                      | 37 |

| 15       | Universal Asynchronous Receiver/Transmitter (UART) Registers | 38 |

| 16       | UART/IrDA/CIR Register Program                               |    |

| 17       | Receive Holding Register (RHR)                               | 41 |

| 18       | Transmit Holding Register (THR)                              |    |

| 19       | Divisor Latch Low Register (DLL)                             |    |

| 20       | Interrupt Enable Register UART Mode (IER-UART Mode)          |    |

| 21       | Interrupt Enable Register IrDA Mode (IER-IrDA Mode)          |    |

| 22       | Interrupt Enable Register CIR Mode (IER-CIR Mode)            |    |

| 23       | Divisor Latch High Register (DLH)                            |    |

| 24       | Interrupt Identification Register UART Mode (IIR-UART Mode)  |    |

| 25       | Interrupt Identification Register IrDA Mode (IIR-IrDA mode)  |    |

| 26       | Interrupt Identification Register CIR Mode (IIR-CIR mode)    |    |

| 27       | FIFO Control Register (FCR)                                  |    |

| 28       | Enhanced Feature Register (EFR)                              |    |

| 29       | Software Flow Control Options                                |    |

| 30       | Line Control Register (LCR)                                  |    |

| 31       | Modem Control Register (MCR)                                 |    |

| 32       | XON1 Character Register (XON1)                               |    |

| 33       | Line Status Register UART Mode (LSR-UART Mode)               |    |

| 34       | Line Status Register IrDA Mode (LSR-IrDA Mode)               |    |

| 35       | Line Status Register CIR Mode (LSR-CIR Mode)                 |    |

| 36       | XON2 Character Register (XON2)                               |    |

| 37       | Modem Status Register (MSR)                                  |    |

| 38       | Transmission Control Register (TCR)                          |    |

| 39       | XOFF1 Character Register (XOFF1)                             |    |

| 40       | Scratchpad Register (SPR)                                    |    |

| 41       | Trigger Level Register (TLR)                                 |    |

| 42       | TX FIFO Trigger Level Setting Summary                        |    |

| 43       | RX FIFO Trigger Level Setting Summary                        |    |

| 44       | XOFF2 Character Register (XOFF2)                             |    |

| 45       | Mode Definition Register 1 (MDR1)                            |    |

| 46       | Mode Definition Register 2 (MDR2)                            |    |

| 47       | Status FIFO Line Status Register (SFLSR)                     |    |

| 48       | Transmit Frame Length Low Register (TXFLL)                   |    |

| 40<br>49 | RESUME Register (RESUME)                                     |    |

| 10       |                                                              | .0 |

| 50  | Transmit Frame Length High Register (TXFLH) | 77 |

|-----|---------------------------------------------|----|

| 51  | Status FIFO Low Register (SFREGL)           | 78 |

| 52  | Receive Frame Length Low Register (RXFLL)   | 79 |

| 53  | Status FIFO High Register (SFREGH)          | 80 |

| 54  | Receive Frame Length High Register (RXFLH)  | 81 |

| 55  | Begin Of Frame Control Register (BLR)       | 82 |

| 56  | UART Autobauding Status Register (UASR)     | 83 |

| 57  | Auxiliary Control Register (ACREG)          | 85 |

| 58  | Supplementary Control Register (SCR)        | 86 |

| 59  | Supplementary Status Register (SSR)         | 87 |

| 60  | Begin Of Frame Length Register (EBLR)       | 88 |

| 61  | Module Version Register (MVR)               | 89 |

| 62  | System Configuration Register (SYSC)        | 90 |

| 63  | System Status Register (SYSS)               | 91 |

| 64  | Wake-Up Enable Register (WER)               | 92 |

| 65  | Carrier Frequency Prescaler Register (CFPS) | 93 |

| 66  | (CFPS) Values                               | 93 |

| A-1 | Document Revision History                   | 94 |

|     |                                             |    |

Preface SPRUER6D-May 2009

## About This Manual

Describes the operation of the universal asynchronous receiver/transmitter (UART) in the TMS320DM646x Digital Media System-on-Chip (DMSoC).

## **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

## **Related Documentation From Texas Instruments**

The following documents describe the TMS320DM646x Digital Media System-on-Chip (DMSoC). Copies of these documents are available on the Internet at <u>www.ti.com</u>. *Tip:* Enter the literature number in the search box provided at www.ti.com.

The current documentation that describes the DM646x DMSoC, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <u>www.ti.com/c6000</u>.

<u>SPRUEP8</u> — *TMS320DM646x DMSoC DSP Subsystem Reference Guide.* Describes the digital signal processor (DSP) subsystem in the TMS320DM646x Digital Media System-on-Chip (DMSoC).

- SPRUEP9 TMS320DM646x DMSoC ARM Subsystem Reference Guide. Describes the ARM subsystem in the TMS320DM646x Digital Media System-on-Chip (DMSoC). The ARM subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In general, the ARM is responsible for configuration and control of the device; including the DSP subsystem and a majority of the peripherals and external memories.

- <u>SPRUEQ0</u> *TMS320DM646x DMSoC Peripherals Overview Reference Guide.* Provides an overview and briefly describes the peripherals available on the TMS320DM646x Digital Media System-on-Chip (DMSoC).

- SPRAA84 TMS320C64x to TMS320C64x+ CPU Migration Guide. Describes migrating from the Texas Instruments TMS320C64x digital signal processor (DSP) to the TMS320C64x+ DSP. The objective of this document is to indicate differences between the two cores. Functionality in the devices that is identical is not included.

- SPRU732 TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of the C64x DSP with added functionality and an expanded instruction set.

- <u>SPRU871</u> *TMS320C64x+ DSP Megamodule Reference Guide.* Describes the TMS320C64x+ digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

## Universal Asynchronous Receiver/Transmitter (UART)

## 1 Introduction

This document describes the operation of the universal asynchronous receiver/transmitter (UART), infrared data association (IrDA), and consumer infrared (CIR) module in theTMS320DM646x Digital Media System-on-Chip (DMSoC). In this document, we refer to this module as the UART module with UART modem, IrDA, and CIR functionalities. There are three UART instances in DM646x: UART0, UART1, and UART2.

## 1.1 Purpose of the Peripheral

The UART peripheral is based on the industry standard TL16C550 asynchronous communications element, which in turn is a functional upgrade of the TL16C450. Functionally similar to the TL16C450 on power up (single character or TL16C450 mode), the UART can be placed in an alternate FIFO (TL16C550) mode. This relieves the CPU of excessive software overhead by buffering received and transmitted characters.

The UART performs serial-to-parallel conversions on data received from a peripheral device and parallel-to-serial conversion on data received from the CPU. The CPU can read the UART status at any time. The UART includes control capability and a processor interrupt system that can be tailored to minimize software management of the communications link.

This module is also capable of performing standard infrared communication in slow infrared mode (SIR) and medium infrared mode (MIR) defined by the Infrared Data Association (IrDA).

Moreover, this module also supports consumer infrared (CIR) communications. The CIR mode uses a variable pulse-width modulation technique to encompass the various formats of infrared encoding for remote control applications. The CIR logic is to transmit and receive data packets according to the user-definable frame structure and packet content.

## 1.2 Features

An overview of the features are:

UART consists of the following main features:

- Selectable UART/IrDA/CIR modes.

- Dual 64 entry FIFOs for received and transmitted data payload.

- Programmable and selectable transmit and receive FIFO trigger levels for DMA and interrupt generation.

- Frequency prescaler values from 0 to 16383 to generate the appropriate baud rates.

- Two DMA requests, 1 interrupt request to the system.

UART/Modem includes the following functions:

- Baud-rate up to 1.8432 Mbits/s.

- Software/Hardware flow control.

- Programmable XON/XOFF characters.

- Programmable Auto-RTS and Auto-CTS.

- Programmable serial interface characteristics.

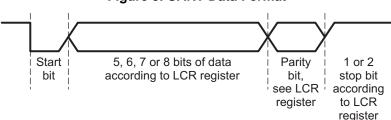

- 5, 6, 7, or 8 bit characters

- Even, odd, mark (always = 1), space (always = 0), or no parity (non parity bit frame) bit generation and detection.

- 1, 1.5, or 2 stop bit generation.

- False start bit detection.

- Line break generation and detection.

- Fully prioritized interrupt system controls.

- Internal test and loopback capabilities.

- Modem control functions (<u>CTS, RTS, DSR</u>, <u>DTR, RI</u>, and <u>DCD</u>) (<u>DCD</u>, <u>DSR</u>, <u>DTR</u>, and <u>RI</u> are only pinned out on UART0 as UDCD0, <u>UDSR0</u>, <u>UDTR0</u>, and <u>URIN0</u>).

IR-IrDA functions are listed below:

- Slow infrared (SIR, baud-rate up to 57.6 Kbits/s) and medium infrared (MIR, baud-rate up to 0.576Mbits/s) operations.

- Framing error, cyclic redundancy check (CRC) error, abort pattern (SIR, MIR) detection.

- 8-entry status FIFO (with selectable trigger levels) available to monitor frame length and frame errors.

IR-CIR functions include:

• Consumer Infrared remote control mode with programmable data encoding.

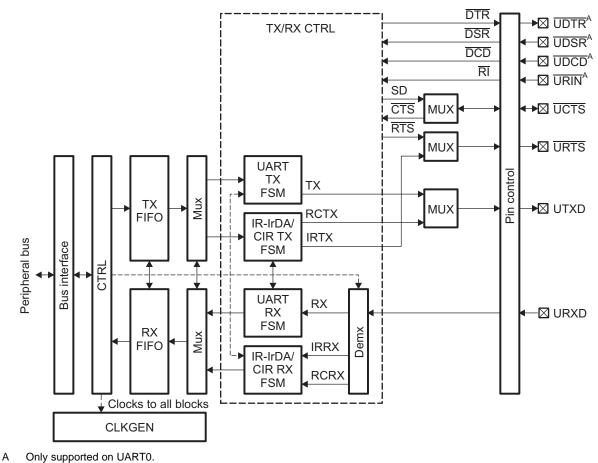

## 1.3 Functional Block Diagram

A block diagram of the UART is shown in Figure 1.

## Figure 1. UART Block Diagram

## 1.4 Application Example

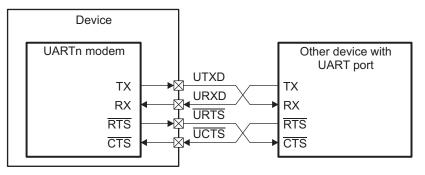

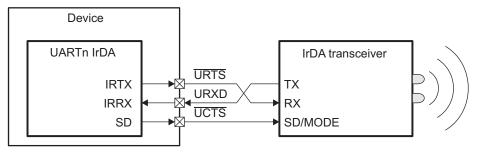

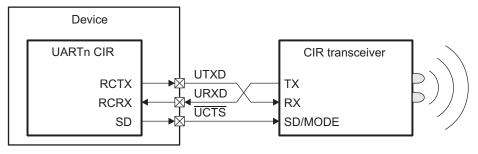

Several example applications of the UART peripheral in different operation modes are shown in Figure 2, Figure 3, and Figure 4.

Figure 2. UART Modem Application Example

Figure 3. UART IrDA Application Example

## 1.5 Industry Standard Compatibility Statement

The UART peripheral is based on the industry standard TL16C550 asynchronous communications element. It also supports IrDA modes including SIR and MIR. Moreover, it supports the flexible CIR mode.

## 2 Architecture

This section describes the architecture of the UART.

## 2.1 Clock Control

The UART bit clock is derived from the 24-MHz clock, AUX\_CLKIN (the AUX\_CLKIN clock is provided through either an on-chip oscillator with external crystal or an external 1.8V LYCMOS-compatible clock input). Several functionalities (FIR and autobaud) require the default 48-MHz clock, and they are not supported. The UART internal system clock is derived from SYSCLK3, which is the PLL0 clock divided by 4. For detailed information on the PLLs and clock distribution on the processor, see the *TMS320DM646x DMSoC ARM Subsystem Reference Guide* (SPRUEP9).

Before using UART, X1AUX must be enabled by clearing the OSCDIS bit in the Clock and Oscillator Control register to 0 (CLKCTL[24] = 0). The CLKCTL is a System Module register at address 01C4 005Ch. For more information about CLKCTL, see the *TMS320DM646x DMSoC ARM Subsystem Reference Guide* (SPRUEP9).

## 2.2 Signal Descriptions

UART signals are described in Table 1.

| Signal | Pin                  | Туре | Description                                                                                                                                                                                                                                                                            | Default |  |  |  |

|--------|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|

| RX     | URXD                 | I    | Serial data input for all modes.                                                                                                                                                                                                                                                       | Unknown |  |  |  |

| ТΧ     | UTXD                 | 0    | Serial data output in UART modes. In other modes, this pin is set to the reset value (inactive state).                                                                                                                                                                                 | 1       |  |  |  |

| IRTX   | URTS                 | 0    | Serial data output in IrDA modes. In other modes, this pin is set to the reset value (inactive state). Pin multiplexed with RTS at the pin-out.                                                                                                                                        | 0       |  |  |  |

| RCTX   | UTXD                 | 0    | Serial data output in CIR mode. In other modes, this pin is set to the reset value (inactive state). Pin multiplexed with TX at the pin-out.                                                                                                                                           |         |  |  |  |

| CTS    | UCTS                 | I    | Clear To Send.                                                                                                                                                                                                                                                                         | Unknown |  |  |  |

|        |                      |      | Active low modem status signal. Reading $MSR[4]$ checks the condition of $\overline{CTS}$ .<br>Reading $MSR[0]$ checks a change of state of $\overline{CTS}$ since the last read of MSR. $\overline{CTS}$ is used in auto- $\overline{CTS}$ mode to control the transmitter.           |         |  |  |  |

| RTS    | URTS                 | 0    | Request To Send.                                                                                                                                                                                                                                                                       | 1       |  |  |  |

|        |                      |      | When active (low), the module is ready to receive data. Setting MCR[1] activates $\overline{\text{RTS}}$ . It becomes inactive as a result of a module reset, loop back mode or by clearing MCR[1]. In auto-RTS mode, it becomes inactive as a result of the receiver threshold logic. |         |  |  |  |

| SD     | UCTS                 | 0    | SD mode is used to configure the transceivers. The SD pin out is an inverted value of ACREG[6]. Pin multiplexed with CTS at the pin-out.                                                                                                                                               | 1       |  |  |  |

| DSR    | UDSR0 <sup>(1)</sup> | I    | Data Set Ready.                                                                                                                                                                                                                                                                        | Unknown |  |  |  |

|        |                      |      | Active-low modem status signal. Reading MSR[5] checks the condition of DSR. Reading MSR[1] checks a change of state of DSR since the last read of MSR.                                                                                                                                 |         |  |  |  |

| DTR    | UDTR0 <sup>(1)</sup> | 0    | Data Terminal Ready.                                                                                                                                                                                                                                                                   | 1       |  |  |  |

|        |                      |      | When active (low), this signal informs the modem that the module is ready to communicate. It's activated by setting MCR[0].                                                                                                                                                            |         |  |  |  |

| DCD    | UDCD0 <sup>(1)</sup> | I.   | Data Carrier Detect.                                                                                                                                                                                                                                                                   | Unknown |  |  |  |

|        |                      |      | Active-low modem status signal. The condition of $\overline{\text{DCD}}$ can be checked by reading MSR[7] and any change in its state can be detected by reading MSR[3].                                                                                                               |         |  |  |  |

| RI     | URINO (1)            | I    | Ring Indicator.                                                                                                                                                                                                                                                                        | Unknown |  |  |  |

|        |                      |      | Active-low modem status signal. The condition of $\overline{RI}$ can be checked by reading MSR[6] and any change in its state can be detected by reading MSR[2].                                                                                                                       |         |  |  |  |

## **Table 1. Signal Descriptions**

<sup>(1)</sup> Only supported on UART0.

## 2.3 Pin Multiplexing

On the DM646x DMSoC, extensive pin multiplexing is used to accommodate the largest number of peripheral functions in the smallest possible package. Pin multiplexing is controlled using a combination of hardware configuration at device reset and software programmable register settings. Refer to the device-specific data manual to determine how pin multiplexing affects the UART.

## 2.4 Modes of Operation

The UART/IrDA module can operate in five different modes:

- 1. UART 16× mode ( $\leq$  115.2 Kbits/s)

- 2. UART 13× mode (≥ 230.4 Kbits/s)

- 3. IrDA SIR mode ( $\leq$  57.6 Kbits/s)

- 4. IrDA MIR mode (0.576 Mbits/s)

- 5. CIR mode (programmable modulation rates specific to remote control applications)

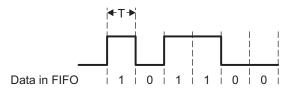

The module performs serial-to-parallel conversion on received data characters and parallel-to-serial conversion on transmitted data characters by the processor. The complete status of each channel of the module and each received character/frame can be read at any time during functional operation via the line status register (LSR).

The module can be placed in an alternate mode (FIFO mode) relieving the processor of excessive software overhead by buffering the received/transmitted characters. Both receiver and transmitter FIFOs can store up to 64 bytes of data (plus three additional bits of error status per byte for the receiver FIFO) and have selectable trigger levels.

Both interrupts and DMA are available to control the data-flow between the system (LH) and the module.

## 2.4.1 UART Modes

The UART uses a wired interface for serial communication with a remote device.

The UART module is functionally compatible with the TL16C750 UART and is also functionally compatible to earlier designs such as the TL16C550.

This module can use hardware or software flow control to manage transmission/reception. Hardware flow control significantly reduces software overhead and increases system efficiency by automatically controlling serial data flow using the RTS output and CTS input signals. Software flow control automatically controls data flow by using programmable XON/XOFF characters.

#### Figure 5. UART Data Format

## 2.4.2 SIR Mode

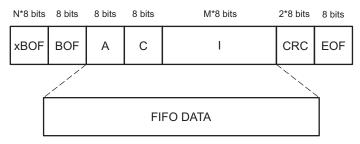

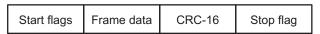

In slow infrared (SIR) mode, data transfer takes place between the LH and the peripheral devices at speeds of up to 57600 bauds. A SIR transmit frame starts with start flags (either a single C0h, multiple C0h, or a single C0h preceded by a number of FFh flags), followed by frame data, CRC-16 and ends with a stop flag (C1h). The bit format for a single word uses a single start bit, eight data bits and one stop bit and is unaffected by the use and settings of the LCR register.

When multiple start flags are required, XBOF\_TYPE in the BLR register is used to select whether C0h or FFh start patterns are used.

The SIR transmit state machine attaches start flags, CRC-16, and stop flags. It checks the outgoing data to establish if data transparency is required.

SIR transparency is carried out if the outgoing data, between the start and stop flags, contains C0h, C1h or 7Dh. If one of these is about to be transmitted, then the SIR state machine sends an escape character (7Dh) first, then inverts the fifth bit of the real data to be sent, and sends this data immediately after the 7Dh character.

The SIR receive state machine recovers the receive clock, removes the start flags, removes any transparency from the incoming data, and determines frame boundary with reception of the stop flag. It also checks for errors such as: frame abort (7Dh character followed immediately by a C1h stop flag, without transparency), CRC error, and frame-length error. At the end of a frame reception, the LH reads the line status register (LSR) to find out possible errors of the received frame.

Data can be transferred both ways by the module but when the device is transmitting, the IRRX circuitry is automatically disabled by hardware. Refer to the DIS\_IR\_RX in the ACREG register for a description of the logical operation. This applies to both SIR and MIR.

The infrared output in SIR mode can either be  $1.6\mu$ s or 3/16 encoding, selected by PULSE\_TYPE in the ACREG register. In  $1.6\mu$ s encoding, the infrared pulse width is  $1.6\mu$ s and in 3/16 encoding the infrared pulse width is 3/16 of a bit duration (1/baud-rate).

The transmitting device must send at least two start flags at the start of each frame for back-to-back frames. Reception does support variable-length stop bits.

#### 2.4.2.1 Frame Format

Figure 6. IrDA SIR Frame Format

The CRC is applied on the address (A), control (C) and information (I) bytes. The two words of CRC are written in the FIFO in reception.

#### 2.4.2.2 Asynchronous Transparency

Before transmitting a byte, the UART IrDA controller examines each byte of the payload and the CRC field (between BOF and EOF). The following occurs with each byte equal to C0h (BOF), C1h (EOF), or 7Dh (control escape).

In transmission:

- 1. Insert a control escape (CE) byte preceding the byte.

- 2. Complements bit 5 of the byte (that is, exclusive-OR's the byte with 20h).

The byte sent for the CRC computation is the initial byte written in the TX FIFO (before the XOR with 20h).

In reception, for the A, C, I, CRC field:

- 1. Compare the byte with CE byte, if not equal send it to the CRC detector and store it in the RX FIFO.

- 2. If equal to CE, discard the CE byte.

- 3. Complements the bit 5 of the byte following the CE.

- 4. Send the complemented byte to the CRC detector and store it in the RX FIFO.

Architecture

#### 2.4.2.3 Abort Sequence

The transmitter may decide to prematurely close a frame. The transmitter aborts by sending the following sequence: 7DC1h. The abort pattern closes the frame without a CRC field or an ending flag.

It is possible to abort a transmission frame by programming the ACREG[1].

When this bit is set to 1, 7Dh and C1h are transmitted and the frame is not terminated with CRC or stop flags.

The receiver treats a frame as an aborted frame when a 70Dh character followed immediately by a C1h character have been received without transparency.

## 2.4.2.4 Pulse Shaping

In SIR mode both the 3/16th and the  $1.6\mu$ s pulse duration methods are supported. PULSE\_TYPE in the ACREG register selects the pulse width method in transmit mode.

#### 2.4.2.5 IR Address Checking

In all IR modes, if address checking has been enabled, only frames intended for the device are written to the RX FIFO. This is to avoid receiving frames not meant for this device in a multi-point infrared environment. It is possible to program two frame addresses that the UART IrDA receives with XON1/ADDR1 and XON2/ADDR2 registers.

Selecting address1 checking is done by setting EFR[0] to 1. And address2 checking is done by setting EFR[1] to 1. Setting EFR[1:0] to 0 disables all address checking operations. If both bits are set, then the incoming frame is checked for both private and public addresses.

If address checking is disabled, then all received frames are written into the reception FIFO.

## 2.4.2.6 SIR Free Format Mode

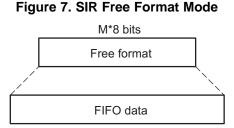

To allow complete software flexibility in the transmission and reception of Infrared data packets, the SIR Free Format mode is a sub function of the existing SIR mode such that all frames going to and from the FIFO buffers are untouched with respect to appending and removing control characters and CRC values. In transmission phase, it uses the IRTX pin as in SIR mode.

This mode corresponds to a UART mode with a pulse modulation of 3/16 of baud-rate pulse width.

For example, a normal SIR packet has BOF control and CRC error checking data appended (transmitting) or removed (receiving) from the data going to and from the FIFOs. In SIR FF (Free Format) mode only the data termed the FIFO DATA area shown in Figure 7 (and shown in Figure 6) would be transmitted and received.

In this mode, the entire FIFO data packet is constructed (encoded and decoded) by the LH software.

The SIR Free Format mode is selected by setting the module in UART mode (MODE\_SELECT in the MDR1 register = 0) and UART\_PULSE in the MDR2 register to 1 to allow the pulse shaping.

Because the bit format is to remain the same, some UART mode configuration register bits need to be set to a specific value:

• LCR[1:0] = 3h (8 data bits)

- LCR[2] = 0 (1 stop bit)

- LCR[3] = 0 (no parity)

- ACREG[7] = 0 (3/16 of baud-rate pulse width)

The features defined through IRRXINVERT in the MDR2 register and DIS\_IR\_RX in the ACREG register are also supported.

**Note:** All other configuration registers need to be at the reset value.

The UART mode interrupts are used for the SIR FF mode.

## 2.4.3 MIR Mode

In medium infrared (MIR) mode, data transfer takes place between LH and peripheral devices at 0.576 Mbits/s speed. A MIR transmit frame starts with start flags (at least two), followed by frame data, then CRC-16, and ends with a stop flag. See Figure 8.

Figure 8. MIR Transmit Frame Format

On transmit, the MIR state machine attaches start flags, CRC-16, and stop flags. It also looks for 5 consecutive 1s in the frame data and automatically inserts 0 after 5 consecutive 1s (this is called bit stuffing).

On receive, the MIR receive state machine recovers the receive clock, removes the start flags, de-stuffs the incoming data, and determines frame boundary with reception of the stop flag. It also checks for errors such as: frame abort, CRC error, or frame-length error. At the end of a frame reception, the LH reads the line status register (LSR) to find out possible errors of received frame.

Data can be transferred both ways by the module but when the device is transmitting, the IR RX circuitry is automatically disabled by hardware. Refer to DIS\_IR\_RX in the ACREG register for a description of the logical operation. This applies to both SIR and MIR.

## 2.4.3.1 Serial Infrared Interaction Pulse Generation (SIP)

In MIR mode, the transmitter needs to send a serial infrared interaction pulse (SIP) at least once every 500 ms. The purpose of the SIP is to let slow devices (operating in SIR mode) know that the medium is currently occupied.

The SIP pulse is shown in Figure 9.

Figure 9. SIP Pulse

When MDR1[6] equals 1, the TX state machine will always send one SIP at the end of a transmission frame. But when MDR1[6] equals 0, the transmission of the SIP depends on ACREG[3]. The system (LH) can set ACREG[3] at least once every 500ms. The advantage of this approach over the default approach is that the TX state machine does not need to send the SIP at the end of each frame which may reduce the overhead required.

## 2.4.4 CIR Mode

In consumer infrared mode, the infrared operation is designed to function as a programmable (universal) remote control. By setting the MDR1 register, the UART can be set to CIR mode in the same way as the other IrDA modes are set using the MDR1 register.

The CIR mode uses a variable pulse width modulation technique (based on multiples of a programmable T period) to encompass the various formats of infrared encoding for remote control applications. The CIR logic is designed to transmit and receive data packets according to the user definable frame structure and packet content.

## 2.4.4.1 Consumer IR Encoding

There are two distinct methods of encoding for remote control applications. The first uses time extended bit forms, that is, a variable pulse distance (or duration) whereby the difference between a logic 1 and logic 0 is the length of the pulse width; and the second is the use of a bi-phase where the encoding of the logic 0 and logic 1 is in the change of signal level from  $1 \ge 0$  or  $0 \ge 1$ , respectively.

The CIR mode is designed to use a completely flexible free format encoding where a digit 1 from the TX/RX FIFO is transmitted/received as a modulated pulse with duration T. Equally, 0 is transmitted/received as a blank duration T. The protocol of the data is constructed and deciphered by the host CPU. For example, the RC-5 protocol using Manchester encoding can be emulated as using a 01 pair for 1 and a 10 pair for 0. RC-5 bit encoding is shown in Figure 10.

Figure 10. RC-5 Bit Encoding

Since the CIR mode logic does not impose a fixed format for infrared packets of data, the CPU software is at liberty to define the format through the use of simple data structures that will then be modulated into an industry standard such as RC-5, SIRC, and so on. To send a sequence of 0101 in RC-5, the host software must write an eight bit binary character of 1001 1001 to the data TX FIFO of the UART.

For SIRC, the modulation length (multiples of T) is the method used to distinguish between a 1 or a 0. The following SIRC digits show the difference in encoding between this and RC-5 (see Figure 11). The pulse width is extended for 1 digits.

SIRC bit encoding

To construct comprehensive packets that constitute remote control commands, the host software must combine a number of eight bit data characters in a sequence that follows one of the universally accepted formats. For illustrative purposes, a standard RC-5 frame is shown in Figure 12 (the SIRC format follows this). Each of the above fields in RC-5 can be considered as two T pulses (digital bits) from the TX and RX FIFOs.

The standard RC-5 format as seen by the UART\_IrDA in CIR mode.

| Figure 12 | RC-5 | Standard | Packet | Format |

|-----------|------|----------|--------|--------|

|-----------|------|----------|--------|--------|

| S1 | S2 | Т | A4 | A3 | A2 | A1 | A0 | C5 | C4 | C3 | C2 | C1 | C0 |

|----|----|---|----|----|----|----|----|----|----|----|----|----|----|

|----|----|---|----|----|----|----|----|----|----|----|----|----|----|

Where S1, S2: Start bits (always 1) T: Toggle Bit A4..A0: Address (or system) bits C5..C0: Command bits

The toggle bit T changes each time a new command is transmitted to allow detection of pressing the same key twice (or to detect receiving the same data from the host consecutively). Since a code is being sent as long as the CPU transmits characters to the UART for transmission, a brief delay in the transmission of the same command would be detected by the use of the toggle bit. The address bits define the machine or device that the Infrared transmission is intended for and the command defines the operation.

To accommodate an extended RC-5 format, the S2 bit is replaced by a further command bit (C6) that allows the command range to increase to 7-bits. This format is known as the extended RC-5 format.

The SIRC encoding uses the duration of modulation for mark and space; hence the duration of data bits inside the standard frame length will vary depending upon the logic 1 content. The packet format is shown in Figure 13 and bit encoding is illustrated in Figure 14. There is one start bit of two milliseconds and control codes followed by data that constitute the whole frame.

#### Figure 13. SIRC Packet Format

| S | C0 | C1 | C2 | C3 | C4 | C5 | C6 | D0 | D1 | D2 | D3 | D4 |

|---|----|----|----|----|----|----|----|----|----|----|----|----|

|---|----|----|----|----|----|----|----|----|----|----|----|----|

It should be noted that the encoding must take a standard duration but the contents of the data may vary. This implies that the control software for emitting and receiving data packets must exercise a scheme of inter-packet delay, where the emission of successive packets can only be done after a real time delay has expired.

## 2.4.4.2 CIR Mode Operation

As explain below, depending on the encoding method (variable pulse distance/bi-phase), the LH should develop a data structure that combines the 1 and 0 with a T period in order to encode the complete frame to transmit. This can then be transmitted to the infrared output with a method of modulation shown in Figure 15.

## Figure 15. CIR Mode Block Components

In transmission, the LH software must exercise an element of real time control for transmitting data packets; they must each be emitted at a constant delay from the start bits of each of the individual packets which means when sending a series of packets, the packet to packet delay must respect a specific delay. To control this delay, two methods can be used:

• By filling the TX FIFO with a number of zero bits that are transmitted with a T period,

- By using an external system timer that controls the delay either between each start of a frame or between the end of a frame and the start of the next one. This can be performed by the following methods:

- controlling the start of the frame through the configuration register SCT bit in MDR1 and SCTX\_EN bit in ACREG depending on the timer status.

- using the TX\_STATUS interrupt (TX\_STATUS\_IT bit in IIR register) to pre-load the next frame in the TX FIFO and to control the start of the timer (in case of control delay between the end of one frame and the start of the next frame).

In reception, there are two ways to stop it :

- The LH can disable the reception by setting the DIS\_IR\_RX in the ACREG register to 1 when it considers that the reception is finished because a large number of 0 has been received. To receive a new frame, the DIS\_IR\_RX in the ACREG register must be cleared to 0.

- A specific mechanism, depending on the value set in the BOF length register (EBLR), allows stopping automatically the reception. If the value set in the EBLR register is different than 0, this feature is enabled and will count the number of bits received at 0. When the counter achieved the value defined in the EBLR register, the reception is automatically stopped and RX\_STOP\_IT (IIR[2]) is set. When a 1 is detected on the RCRX pin, the reception is automatically enabled.

## 2.4.4.3 Carrier Modulation

Looking more closely at the actual modulation pulses of the infrared data stream, it should be noted that each modulated pulse that constitutes a digit is a series of on/off pulses. CIR pulse modulation is shown in Figure 16.

## Figure 16. CIR Pulse Modulation

A minimum of 4 modulation pulses per bit is required by the module.

Based on the requested modulation frequency, the CFPS register must be set with the correct dividing value to provide the more accurate pulse frequency:

Dividing value = (FCLK/12)/MODfreq.

Where FCLK = System bit clock frequency (24 MHz). 12 = real value of BAUD multiple. MODfreq = Effective frequency of the modulation (MHz).

For a targeted modulation frequency of 18 KHz, the CFPS value must be set to 111 (decimal) that provides a modulation frequency of 18.02 KHz.

The duty cycle of these pulses is user-defined by the pulse duty register bits in the MDR2 configuration register, see Table 2 and Figure 17.

The transmission logic ensures that all pulses are transmitted completely. There is no cut off of any pulses during transmission. Furthermore, while transmitting continuous bytes back to back, no delay is inserted between 2 transmitted bytes.

| Duty cycle (high level) |  |  |  |  |  |  |

|-------------------------|--|--|--|--|--|--|

| 1/4                     |  |  |  |  |  |  |

| 1/3                     |  |  |  |  |  |  |

| 5/12                    |  |  |  |  |  |  |

| 1/2                     |  |  |  |  |  |  |

|                         |  |  |  |  |  |  |

| Table 2 | CIR | Modulation | Duty Cycle |

|---------|-----|------------|------------|

|---------|-----|------------|------------|

## 2.4.4.4 Frequency Divider Values

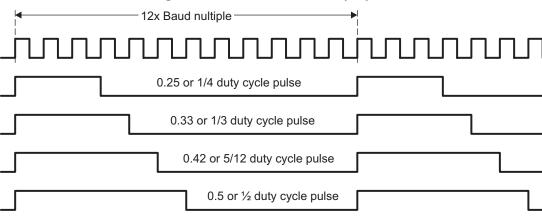

As previously explained, the data transferred is a succession of pulse with a T period.

Depending on the standards used, the T period is defined through the DLL and DLH registers that defined the value to divide the functional clock (24 MHz):

Dividing value = (FCLK/16)/Tfreq. Where FCLK = System bit clock frequency (24 MHz). 16 = real value of BAUD multiple. Tfreq = Effective frequency of the T pulse (MHz).

## Figure 18. Variable Pulse Duration Definitions

For a logical 1, the pulse duration is equal to 2T and for a logical 0, it is equal to 4T. If T = 1.12 ms, the value coded into the DLH and DLL register must be 1680 in decimal.

## 2.4.4.5 CIR Demodulator Bypass Mode

Note: The demodulator bypass function is supported only on silicon revision 3.0 and later revisions.

In certain applications, the on-board CIR receivers have built-in demodulators. In this case, the demodulator in the CIR receiver can be optionally disabled. As a result, data coming from the RCRX pin directly enters the VOTE3 block. No other operation of the CIR module is effected when the it enters the demodulator bypass mode.

To enter the demodulator bypass mode, the following register setup is needed:

- 1. MDR1[2:0] = 6h

- 2. LCR[3] = 0h

- 3. LCR[4] = 1h

## 2.5 Functional Description

This subsection describes the functions of the peripheral.

## 2.5.1 Trigger Levels

The UART provides programmable trigger levels for both receiver and transmitter DMA and Interrupt generation. After reset, both transmitter and receiver FIFOs are disabled. In effect, the trigger level is the default value of one byte. The programmable trigger levels are an enhanced feature available via the trigger level register (TLR).

## 2.5.2 Interrupts

The UART IrDA CIR module generates interrupts. All interrupts can be enabled/disabled by writing to the appropriate bit in the interrupt enable register (IER). The interrupt status of the device can be checked at any time by reading the interrupt identification register (IIR).

The UART, IrDA, and CIR modes have different interrupts in the UART IrDA CIR module and therefore different IER and IIR mappings according to the selected mode.

## 2.5.2.1 UART Mode Interrupts

In UART modes, there are seven possible interrupts (Table 3). These interrupts are prioritized to six different levels.

When an interrupt is generated, the interrupt identification register (IIR) indicates that an interrupt is pending by bringing IIR[0] to 0 and provides the type of interrupt through IIR[5:1]. summarizes the interrupt control functions.

| Priority<br>Level | IIR[5-0] | Interrupt Type                                      | Interrupt Source                                                                                                                           | Interrupt Reset Method                                                                          |

|-------------------|----------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| None              | 1h       | None                                                | None                                                                                                                                       | None                                                                                            |

| 1                 | 6h       | Receiver line status                                | OE, FE, PE, or BI errors occur in characters in the RX FIFO                                                                                | FE, PE, BI: Read RHR. OE: Read LSR                                                              |

| 2                 | Ch       | RX Timeout                                          | Stale data in RX FIFO                                                                                                                      | Read RHR                                                                                        |

| 2                 | 4h       | RHR interrupt                                       | DRDY (data ready) (FIFO disable) RX FIFO above trigger level (FIFO enable)                                                                 | Read RHR until interrupt condition disappears.                                                  |

| 3                 | 2h       | THR interrupt                                       | TFE (THR empty) (FIFO disable) TX FIFO<br>below trigger level (FIFO enable)                                                                | Write to THR until interrupt condition disappears.                                              |

| 4                 | 0        | Modem status                                        | MSR[1:0] /= 0                                                                                                                              | Read MSR                                                                                        |

| 5                 | 10h      | XOFF<br>interrupt/special<br>character<br>interrupt | Receive XOFF characters(s)/special character                                                                                               | Receive XON character(s), if XOFF<br>interrupt / Read of IIR, if special<br>character interrupt |

| 6                 | 20h      | CTS, RTS, DSR                                       | $\overline{\text{RTS}}$ pin, $\overline{\text{CTS}}$ pin or $\overline{\text{DSR}}$ pin change state from active (low) to inactive (high). | Read IIR                                                                                        |

#### **Table 3. UART Mode Interrupts**

It is important to note that for the receiver line status interrupt, LSR[7] generates the interrupt.

For the XOFF interrupt, if a XOFF flow character detection caused the interrupt, the interrupt is cleared by a XON flow character detection. If special character detection caused the interrupt, the interrupt is cleared by a read of the IIR.

## 2.5.2.2 IrDA Mode Interrupts

In the IrDA modes there are eight possible interrupts (Table 4). The interrupt line is activated when any of the eight interrupts is generated (there is no priority). For TX\_STATUS\_IT bit in IIR register, interrupt source 1 is used with interrupt reset method 1 and interrupt source 2 is used with interrupt reset method 2.

| IIR Bit | Interrupt Type                 | Interrupt Source                                                                                                    | Interrupt Reset Method                                         |

|---------|--------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 0       | RHR interrupt                  | DRDY (data ready) (FIFO disable RX FIFO above trigger level (FIFO enable).                                          | Read RHR until interrupt condition disappears.                 |

| 1       | THR interrupt                  | TFE (THR empty) (FIFO disable) TX FIFO below trigger level (FIFO enable).                                           | Write to THR until interrupt condition disappears.             |

| 2       | Last byte in<br>RX FIFO        | Last byte of frame in RX FIFO is available to be read at the RHR port.                                              | Read RHR.                                                      |

| 3       | RX overrun                     | Write to RHR when RX FIFO full.                                                                                     | Read RESUME register.                                          |

| 4       | Status FIFO<br>interrupt       | Status FIFO triggers level reached.                                                                                 | Read STATUS1 FIFO.                                             |

| 5       | TX Status                      | 1.THR empty before EOF sent. Last bit of transmission of the IrDA frame has occurred but with an underrun error. OR | 1.Read RESUME register.<br>OR                                  |

|         |                                | 2. Transmission of the last bit of the IrDA frame is finished successfully.                                         | 2.Read IIR                                                     |

| 6       | Receiver line status interrupt | CRC, ABORT or Frame-length error is written into<br>STATUS FIFO.                                                    | Read STATUS FIFO. [read until<br>empty - max 8 reads required] |

| 7       | Received EOF                   | Received end-of -frame.                                                                                             | Read IIR.                                                      |

#### Table 4. IrDA Mode Interrupts

Note: The meaning of TX Status is indicated by IRTX\_UNDERRUN bit in MDR2.

## 2.5.2.3 CIR Mode interrupts

The CIR mode uses a subset of the existing IrDA mode interrupts. The following table illustrates the interrupt modes that are to be maintained. In CIR mode, TX\_STATUS\_IT bit in IIR-CIR mode register has a sole purpose of indicating that the last bit of infrared data has been passed to the IR TX pin.

| IIR Bit | Interrupt Type | Interrupt Source                                                                  | Interrupt Reset Method                             |

|---------|----------------|-----------------------------------------------------------------------------------|----------------------------------------------------|

| 0       | RHR interrupt  | DRDY (data ready) (FIFO disable) RX FIFO above trigger level (FIFO enable)        | Read RHR until interrupt condition disappears.     |

| 1       | THR interrupt  | TFE (THR empty) (FIFO disable) TX FIFO below trigger level (FIFO enable)          | Write to THR until interrupt condition disappears. |

| 2       | RX_STOP_IT     | Receive stop interrupt (depending on value set in the BOF Length register (EBLR)) | Read IIR                                           |

| 3       | RX overrun     | Write to RHR when RX FIFO full.                                                   | Read RESUME register.                              |

| 4       | N/A for CIR    | N/A for CIR                                                                       | N/A for CIR                                        |

| 5       | TX Status      | Transmission of the last bit of the frame is finished successfully.               | Read IIR                                           |

| 6       | N/A for CIR    | N/A for CIR                                                                       | N/A for CIR                                        |

| 7       | N/A for CIR    | N/A for CIR                                                                       | N/A for CIR                                        |

#### **Table 5. CIR Mode Interrupts**

#### 2.5.3 FIFO Interrupt Mode Operation

In FIFO interrupt mode (FIFO\_EN bit in FCR = 1, relevant interrupts are enabled by IER), the processor is informed of the status of the receiver and transmitter by an interrupt signal. These interrupts are raised when receive/transmit FIFO threshold (respectively TLR[7:4] and TLR[3:0] or RX\_FIFO\_TRIG bit in FCR and TX\_FIFO\_TRIG bit in FCR) are reached; the interrupt signals instruct the Local Host to transfer data to the destination (from the UART module in receive mode and/or from any source to the UART FIFO in transmit mode).

In the case of the UART flow control being enabled along with the interrupt capabilities, the user must ensure that the UART flow control FIFO threshold (RX\_FIFO\_TRIG\_HALT bit in TCR) is greater than or equal to the receive FIFO threshold.

In receive, no interrupt is generated until receive FIFO reaches its threshold. Once low the interrupt can only be de-asserted when the Local Host has handled enough bytes to make the FIFO level below threshold. The flow control threshold is set at a higher value than FIFO threshold. Receive FIFO IT request generation is shown in Figure 19.

In transmit mode, an interrupt request is automatically asserted when TX FIFO is empty. This request is de-asserted when the TX FIFO crossed the threshold level. The interrupt line is de-asserted until a sufficient number of elements have been transmitted to go below TX FIFO threshold. Transmit FIFO IT request generation is shown in Figure 20.

## 2.5.4 FIFO Polled Mode Operation

In FIFO polled mode (FIFO\_EN bit in FCR= 0, relevant interrupts disabled via interrupt enable register (IER)) the status of the receiver and transmitter can then be checked by polling the line status register (LSR). This mode is an alternative to the FIFO interrupt mode of operation where the status of the receiver and transmitter is automatically known by means of interrupts sent to the LH.

## 2.5.5 FIFO DMA Mode Operation

When the EDMA is used to service data to the UART, the following guidelines must be followed:

- EDMA transfer size per event should be the same as UART receive FIFO trigger level (EDMA empties the UART receive FIFO for each event it receives).

- EDMA transfer size per event should be the same as UART transmit FIFO trigger level (EDMA fills the UART transmit FIFO for each event it receives).

For example, the receive FIFO trigger level is chosen to be 20 bytes (when there are 20 bytes in the RX FIFO, an RX EDMA event is generated) and the transmit FIFO trigger level is chosen to be 52 bytes (when there are 52 byte-spaces left, a TX EDMA event is generated). When servicing the receive FIFO, the following EDMA setup is needed: Acnt = 1, Bcnt = 20, Ccnt = number of 20-byte transfers. When servicing the transmit FIFO, the following setup is needed: Acnt = 1, Bcnt = 52, Ccnt = number of 52-byte transfers. For details on the setup of the EDMA, see the *TMS320DM646x DMSoC Enhanced Direct Memory Access (EDMA3) Controller User's Guide* (SPRUEQ5).

## 2.5.5.1 DMA Signaling

There are four modes of DMA operation, DMA mode 0/1/2/3. They can be selected as follows.

| When $SCR[0] = 0$ : | Setting DMA_MODE to 0 enables DMA mode 0.                                                          |

|---------------------|----------------------------------------------------------------------------------------------------|

|                     | Setting DMA_MODE to 1 enables DMA mode 1.                                                          |

| When SCR[0] = 1:    | SCR[2:1] determines DMA mode 0 to 3 according to supplementary control register (SCR) description. |

## For instance:

- if no DMA operation is desired: set SCR[0] to 1 and SCR[2:1] to 00 (DMA\_MODE bit in FCR is discarded);

- if DMA mode 1 is desired: either set SCR[0] to 0 and DMA\_MODE bit in FCR to 1 or set SCR[0] to 1 SCR[2:1] to 01 (DMA\_MODE bit in FCR is discarded).

If the FIFOs are disabled (FIFO\_EN bit in FCR = 0), DMA occurs in single character transfers.

When DMA Mode 0 has been programmed, the signals associated with DMA operation are not active.

## 2.5.5.2 DMA Transfers (DMA Mode 1, 2, or 3)

Figure 21, Figure 22, Figure 23, and Figure 24 show the supported DMA operations.

In receive mode (Figure 21), a DMA request is generated as soon as the receive FIFO reaches its threshold level defined in the Trigger Level Register (refer to Table 43). This request is de-asserted when the number of bytes defined by the threshold level has been read by the system DMA.

Figure 21. Receive FIFO DMA Request Generation (32 chars)

In transmit mode (Figure 22), a DMA request is automatically asserted when the transmit FIFO is empty. This request is de-asserted when the number of bytes defined by the number of spaces in the Trigger Level Register (TLR) has been written by the system DMA. If an insufficient number of characters are written, then the DMA request will remain active.

The DMA request is again asserted if the FIFO is able to receive the number of bytes defined by the TLR register (refer to Table 42).

There are a number of ways the threshold can be programmed. Figure 22 shows a DMA transfer that operates with a space setting of 56 which could arise from the use of the auto settings in TX\_FIFO\_TRIG bit in FCR or the use of the TLR[3:0] concatenated with the TX\_FIFO\_TRIG bit in FCR. The setting of 56 spaces in the UART IrDA CIR module should correlate with settings of the system DMA so that the buffer does not overflow (program the DMA request size of the Local Host controller to be equal to the number of spaces value in the UART IrDA CIR module).

Figure 23 shows another example with 8 spaces to illustrate the buffer level crossing the space threshold. Again, the Local Host DMA controller settings should correspond with that of the UART IrDA CIR module.

Figure 23. Transmit FIFO DMA Request Generation (8 spaces)

The final example, Figure 24, illustrates the setting of 1 space that uses the DMA for each transfer of one character to the transmit buffer. The buffer is filled at a faster rate than the BAUD rate transmits data to the TX pin. Eventually, the buffer is completely full and the DMA operations stop transferring data to the transmit buffer.

There are two occasions where the buffer holds the maximum amount of data words, shortly after this, the DMA is disabled to illustrate the slower transmission of the data words to the TX pin. Eventually, the buffer will be emptied at the rate specified by the BAUD Rate Settings of the DLL and DLH registers.

Again, the DMA settings should correspond to the system's Local Host DMA controller settings in order to ensure the correct operation of this logic.

## 2.5.6 Sleep Mode

#### 2.5.6.1 UART Modes

In UART modes, sleep mode is enabled by writing a 1 to SLEEP\_MODE (when ENHANCED\_EN bit in EFR = 1).

Sleep mode is entered when:

- The serial data input line, RX is idle.

- The TX FIFO and TX shift register are empty.

- The RX FIFO is empty.

- There are no interrupts pending except THR interrupts.

Sleep mode is a good way to lower power consumption of UART but this state can be achieved only when the UART is set in modem mode. Therefore, even if the UART has no functional key role, it must be initialized in a functional mode to take advantage of sleep mode.

In sleep mode the module clock and baud rate clock are stopped internally. Because most registers are clocked using these clocks the power consumption is greatly reduced. The module wakes up when any change is detected on the RX line, if data is written to the TX FIFO, when there is any change in the state of the modem input pins. An interrupt can be generated on a wake up event by setting RX\_CTS\_DSR\_WAKE\_UP\_ENABLE in the SCR register to 1. See Section 2.5.2 to know how to manage it.

**Note:** Writing to the divisor latch registers (DLL and DLH) to set the baud clock (BCLK) must not be done during sleep mode; it is advisable to disable sleep mode using IER[4] before writing to DLL or DLH.

Architecture

## 2.5.6.2 IR-IrDA and IR-CIR Modes

In IrDA/CIR modes, sleep mode is enabled by writing a 1 to MDR1[3].

Sleep mode is entered when:

- The serial data input line, RX is idle.

- The TX FIFO and TX shift register are empty.

- The RX FIFO is empty.

- There are no interrupts pending except THR interrupts.

The module wakes up when any change is detected on the RX line or if data is written to the TX FIFO.

## 2.5.7 Idle Modes

Sleep and AutoIdle modes are embedded power saving features. At the system level, power reduction techniques can be applied by shutting down certain internal clock and power domains of the device.

- The UART supports an idle req idle ack handshaking protocol. This protocol is used at system level to shut down clocks of the UART in a clean and controlled manner and to switch the UART from the interrupt generation mode to a wakeup generation mode for unmasked events (Refer to SYSC[2] and WER).

- In the wakeup generation mode, interrupt request generation and DMA request generation are disabled.

## 2.5.8 Break and Time-Out Conditions

## 2.5.8.1 Time-Out Counter

An RX idle condition is detected when the receiver line, RX, has been high for a time equivalent to 4X programmed word length + 12 bits. The receiver line is sampled midway through each bit.

For sleep mode the counter is reset when there is activity on the RX line.

For the timeout interrupt, the counter only counts when there is data in the RX FIFO and the count is reset when there is activity on the RX line or when the RHR is read.

## 2.5.8.2 Break Condition

When a break condition occurs the TX line is pulled low. A break condition is activated by setting BREAK\_EN in the LCR register. Be aware that the break condition is not aligned on word stream; that is, a break condition can occur in the middle of a character. The only way to send a break condition on a full character, is:

- Reset transmit FIFO (if enabled).

- Wait for transmit shift register becomes empty (LSR[6] = 1).

- Take a guard time according to stop bit definition.

- Set BREAK\_EN in the LCR register to 1.

Break condition is asserted as long as BREAK\_EN in the LCR register is set to 1.

The above functionality (timeout counter and break condition) will only apply to the UART Modem operation and does not extend to the IrDA/CIR modes of operation.

## 2.5.9 Programmable Baud Rate Generator

The UART IrDA CIR module contains a programmable baud generator and a set of fixed divider that takes the 48 MHz clock input and divides it down to the expected baud-rate.

Architecture

The baud rate generator and associated controls is depicted in Figure 25. For CIR mode information, see Figure 15.

### Figure 25. BAUD Rate Generator

## CAUTION

It is recommended to clear the set MODE\_SELECT bit in the MDR1 register to 0 before attempting to initialize or modify the clock parameter controls (DLH, DLL). Nonobservance to this rule may result in an unpredictable behavior of the module.

Choosing the appropriate divisor value:

- UART 16× mode: Divisor value = Operating Frequency / (16× baud rate).

- UART 13× mode: Divisor value = Operating Frequency / (13× baud rate).

- SIR mode: Divisor value = Operating Frequency / (16× baud-rate).

- MIR mode: Divisor value = Operating Frequency / (41×/42× baud-rate).

## 2.5.9.1 UART Baud Rates (24 MHz clock):

| Baud Rate   | Baud Multiple | DLH,DLL (Decimal) | DLH,DLL (Hex) | Actual Baud Rate | Error (%) <sup>(1)</sup> |

|-------------|---------------|-------------------|---------------|------------------|--------------------------|

| 0.3 Kb/s    | 16x           | 5000              | 13h, 88h      | 0.3 Kb/s         | 0                        |

| 1.2 Kb/s    | 16x           | 1250              | 4h, E2h       | 1.2 Kb/s         | 0                        |

| 2.4 Kb/s    | 16x           | 625               | 2h, 71h       | 2.4 Kb/s         | 0                        |

| 14.4 Kb/s   | 16x           | 104               | 0, 68h        | 14.423 Kb/s      | +0.16                    |

| 28.8 Kb/s   | 16x           | 52                | 0, 34h        | 28.846Kb/s       | +0.16                    |

| 57.6 Kb/s   | 16x           | 26                | 0, 1Ah        | 57.692 Kb/s      | +0.16                    |

| 115.2 Kb/s  | 16x           | 13                | 0, Dh         | 115.38 Kb/s      | +0.16                    |

| 230.4 Kb/s  | 13x           | 8                 | 0, 8h         | 230.77 Kb/s      | +0.16                    |

| 460.8 Kb/s  | 13x           | 4                 | 0, 4h         | 461.54 Kb/s      | +0.16                    |

| 921.6 Mb/s  | 13x           | 2                 | 0, 2h         | 923.08 Mb/s      | +0.16                    |

| 1.8432 Mb/s | 13x           | 1                 | 0, 1h         | 1.8462 Mb/s      | +0.16                    |

Table 6. UART BAUD Rate Settings (24 MHz clock)

<sup>(1)</sup> Baud rate error and source jitter table values do not include 24MHz reference clock error and jitter.

## 2.5.9.2 IR Baud Rates (24 MHz clock):

| Baud Rate  | IR Mode | Baud Multiple | Encoding | DLH,DLL | Actual Baud<br>Rate (*= Avg) | Error (%) <sup>(1)</sup> |

|------------|---------|---------------|----------|---------|------------------------------|--------------------------|

| 2.4 Kb/s   | SIR     | 16x           | 3/16     | 625     | 2.4 Kb/s                     | 0                        |

| 9.6 Kb/s   | SIR     | 16x           | 3/16     | 156     | 9.6153 Kb/s                  | +0.16                    |

| 19.2 Kb/s  | SIR     | 16x           | 3/16     | 78      | 19.231 Kb/s                  | +0.16                    |

| 57.6 Kb/s  | SIR     | 16x           | 3/16     | 26      | 57.692 Kb/s                  | +0.16                    |

| 0.576 Mb/s | MIR     | 41x/ 42x      | 1/4      | 1       | 0.5756 Mb/s                  | 0                        |

## Table 7. IrDA BAUD Rate Settings (24 MHz clock)

<sup>(1)</sup> Baud rate error and source jitter table values do not include 24MHz reference clock error and jitter.

## 2.5.10 Hardware Flow Control

Hardware flow control is composed of auto-CTS and auto-RTS. Auto-CTS and auto-RTS can be enabled/disabled independently by programming EFR[7:6].

With auto- $\overline{\text{CTS}}$ ,  $\overline{\text{CTS}}$  must be active before the module can transmit data.

Auto-RTS only activates the RTS output when there is enough room in the RX FIFO to receive data and de-activates the RTS output when the RX FIFO is sufficiently full. The HALT and RESTORE trigger levels in the TCR determine the levels at which RTS is activated/de-activated.

If both auto-CTS and auto-RTS are enabled, data transmission does not occur unless the receiver FIFO has empty space. Thus, overrun errors are eliminated during hardware flow control. If not enabled, overrun errors occur if the transmit data rate exceeds the receive FIFO latency.

www.ti.com

## 2.5.10.1 Auto-RTS