## TMS320DM335 Digital Media System-on-Chip (DMSoC) Universal Serial Bus (USB)

# **Reference Guide**

Literature Number: SPRUFY9 July 2008

## Contents

| Prefa | ace     |                                                   | 11 |

|-------|---------|---------------------------------------------------|----|

| 1     | Introdu | ction                                             | 14 |

|       | 1.1     | Purpose of the Peripheral                         | 14 |

|       | 1.2     | Features                                          | 14 |

|       | 1.3     | Functional Block Diagram                          | 15 |

|       | 1.4     | Supported Use Case Examples                       | 16 |

|       | 1.5     | Industry Standard(s) Compliance Statement         | 22 |

| 2     | Periphe | eral Architecture                                 | 23 |

|       | 2.1     | Clock Control                                     | 23 |

|       | 2.2     | Signal Descriptions                               | 23 |

|       | 2.3     | USB_DP / USB_DM Polarity Inversion                | 24 |

|       | 2.4     | Indexed and Non-Indexed Registers                 |    |

|       | 2.5     | USB PHY Initialization                            | 24 |

|       | 2.6     | VBUS Voltage Sourcing Control                     | 24 |

|       | 2.7     | Dynamic FIFO Sizing                               | 25 |

| 3     | USB Co  | ontroller Host and Peripheral Modes Operation     | 25 |

|       | 3.1     | USB Controller Peripheral Mode Operation          | 27 |

|       | 3.2     | USB Controller Host Mode Operation                | 45 |

|       | 3.3     | DMA Operation                                     | 58 |

|       | 3.4     | Interrupt Handling                                | 69 |

|       | 3.5     | Test Modes                                        | 70 |

|       | 3.6     | Reset Considerations                              | 72 |

|       | 3.7     | Interrupt Support                                 | 72 |

|       | 3.8     | DMA Event Support                                 | 72 |

|       | 3.9     | Power Management                                  | 72 |

| 4     | Registe | ers                                               | 73 |

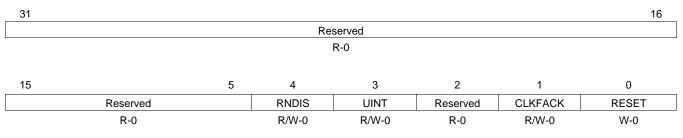

|       | 4.1     | Control Register (CTRLR)                          | 80 |

|       | 4.2     | Status Register (STATR)                           | 80 |

|       | 4.3     | RNDIS Register (RNDISR)                           | 81 |

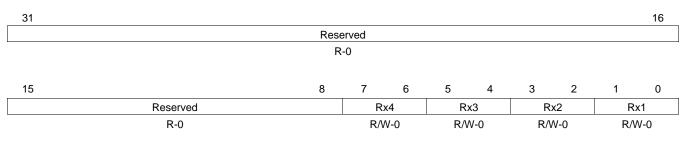

|       | 4.4     | Auto Request Register (AUTOREQ)                   | 82 |

|       | 4.5     | USB Interrupt Source Register (INTSRCR)           | 83 |

|       | 4.6     | USB Interrupt Source Set Register (INTSETR)       | 84 |

|       | 4.7     | USB Interrupt Source Clear Register (INTCLRR)     | 85 |

|       | 4.8     | USB Interrupt Mask Register (INTMSKR)             | 86 |

|       | 4.9     | USB Interrupt Mask Set Register (INTMSKSETR)      | 87 |

|       | 4.10    | USB Interrupt Mask Clear Register (INTMSKCLRR)    |    |

|       | 4.11    | USB Interrupt Source Masked Register (INTMASKEDR) | 89 |

|       | 4.12    | USB End of Interrupt Register (EOIR)              |    |

|       | 4.13    | USB Interrupt Vector Register (INTVECTR)          |    |

|       | 4.14    | Transmit CPPI Control Register (TCPPICR)          |    |

|       | 4.15    | Transmit CPPI Teardown Register (TCPPITDR)        | 91 |

| 4.16 | Transmit CPPI DMA Controller End of Interrupt Register (TCPPIEOIR)             | 92  |

|------|--------------------------------------------------------------------------------|-----|

| 4.17 | Transmit CPPI DMA Controller Interrupt Vector Register (TCPPIIVECTR)           | 92  |

| 4.18 | Transmit CPPI Masked Status Register (TCPPIMSKSR)                              | 93  |

| 4.19 | Transmit CPPI Raw Status Register (TCPPIRAWSR)                                 | 93  |

| 4.20 | Transmit CPPI Interrupt Enable Set Register (TCPPIIENSETR)                     |     |

| 4.21 | Transmit CPPI Interrupt Enable Clear Register (TCPPIIENCLRR)                   |     |

| 4.22 | Receive CPPI Control Register (RCPPICR)                                        |     |

| 4.23 | Receive CPPI Masked Status Register (RCPPIMSKSR)                               |     |

| 4.24 | Receive CPPI Raw Status Register (RCPPIRAWSR)                                  |     |

| 4.25 | Receive CPPI Interrupt Enable Set Register (RCPPIENSETR)                       |     |

| 4.26 | Receive CPPI Interrupt Enable Clear Register (RCPPIIENCLRR)                    |     |

| 4.27 | Receive Buffer Count 0 Register (RBUFCNT0)                                     |     |

| 4.28 | Receive Buffer Count 1 Register (RBUFCNT1)                                     |     |

| 4.29 | Receive Buffer Count 2 Register (RBUFCNT2)                                     |     |

| 4.30 | Receive Buffer Count 3 Register (RBUFCNT3)                                     |     |

| 4.31 | Transmit CPPI DMA State Word 0 (TCPPIDMASTATEW0)                               |     |

| 4.32 | Transmit CPPI DMA State Word 1 (TCPPIDMASTATEW1)                               |     |

| 4.33 | Transmit CPPI DMA State Word 2 (TCPPIDMASTATEW2)                               |     |

| 4.34 | Transmit CPPI DMA State Word 3 (TCPPIDMASTATEW3)                               |     |

| 4.35 | Transmit CPPI DMA State Word 4 (TCPPIDMASTATEW4)                               |     |

| 4.36 | Transmit CPPI DMA State Word 5 (TCPPIDMASTATEW5)                               |     |

| 4.37 | Transmit CPPI Completion Pointer (TCPPICOMPPTR)                                |     |

| 4.38 | Receive CPPI DMA State Word 0 (RCPPIDMASTATEW0)                                |     |

| 4.39 | Receive CPPI DMA State Word 1 (RCPPIDMASTATEW1)                                |     |

| 4.40 | Receive CPPI DMA State Word 2 (RCPPIDMASTATEW2)                                |     |

| 4.41 | Receive CPPI DMA State Word 3 (RCPPIDMASTATEW3)                                |     |

| 4.42 | Receive CPPI DMA State Word 4 (RCPPIDMASTATEW4)                                |     |

| 4.43 | Receive CPPI DMA State Word 5 (RCPPIDMASTATEW5)                                |     |

| 4.44 | Receive CPPI DMA State Word 6 (RCPPIDMASTATEW6)                                |     |

| 4.45 | Receive CPPI Completion Pointer (RCPPICOMPPTR)                                 |     |

| 4.46 | Function Address Register (FADDR)                                              |     |

| 4.47 | Power Management Register (POWER)                                              |     |

| 4.48 | Interrupt Register for Endpoint 0 Plus Transmit Endpoints 1 to 4 (INTRTX)      |     |

| 4.49 | Interrupt Register for Receive Endpoints 1 to 4 (INTRRX)                       |     |

| 4.50 | Interrupt Enable Register for INTRTX (INTRTXE)                                 |     |

| 4.51 | Interrupt Enable Register for INTRRX (INTRRXE)                                 |     |

| 4.52 | Interrupt Register for Common USB Interrupts (INTRUSB)                         |     |

| 4.53 | Interrupt Enable Register for INTRUSB (INTRUSBE)                               |     |

| 4.54 | Frame Number Register (FRAME)                                                  |     |

| 4.55 | Index Register for Selecting the Endpoint Status and Control Registers (INDEX) |     |

| 4.56 | Register to Enable the USB 2.0 Test Modes (TESTMODE)                           |     |

| 4.57 | Maximum Packet Size for Peripheral/Host Transmit Endpoint (TXMAXP)             |     |

| 4.58 | Control Status Register for Endpoint 0 in Peripheral Mode (PERI_CSR0)          |     |

| 4.59 | Control Status Register for Endpoint 0 in Host Mode (HOST_CSR0)                |     |

| 4.60 | Control Status Register for Peripheral Transmit Endpoint (PERI_TXCSR)          |     |

| 4.61 | Control Status Register for Host Transmit Endpoint (HOST_TXCSR)                |     |

| 4.62 | Maximum Packet Size for Peripheral Host Receive Endpoint (RXMAXP)              |     |

| 4.63 | Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR)           |     |

| 4.64 | Control Status Register for Host Receive Endpoint (HOST_RXCSR)                 | 124 |

| Count 0 Register (COUNT0)                                     | 125                       |

|---------------------------------------------------------------|---------------------------|

|                                                               |                           |

| Type Register (Host mode only) (HOST_TYPE0)                   | 126                       |

| Transmit Type Register (Host mode only) (HOST_TXTYPE)         | 126                       |

| NAKLimit0 Register (Host mode only) (HOST_NAKLIMIT0)          | 127                       |

| Transmit Interval Register (Host mode only) (HOST_TXINTERVAL) | 127                       |

| Receive Type Register (Host mode only) (HOST_RXTYPE)          | 128                       |

| Receive Interval Register (Host mode only) (HOST_RXINTERVAL)  | 129                       |

| Configuration Data Register (CONFIGDATA)                      | 130                       |

| Transmit and Receive FIFO Register for Endpoint 0 (FIFO0)     | 131                       |

| Transmit and Receive FIFO Register for Endpoint 1 (FIFO1)     | 132                       |

| Transmit and Receive FIFO Register for Endpoint 2 (FIFO2)     | 132                       |

| Transmit and Receive FIFO Register for Endpoint 3 (FIFO3)     | 133                       |

| Transmit and Receive FIFO Register for Endpoint 4 (FIFO4)     | 133                       |

| OTG Device Control Register (DEVCTL)                          | 134                       |

| Transmit Endpoint FIFO Size (TXFIFOSZ)                        | 135                       |

| Receive Endpoint FIFO Size (RXFIFOSZ)                         | 135                       |

| Transmit Endpoint FIFO Address (TXFIFOADDR)                   | 136                       |

| Receive Endpoint FIFO Address (RXFIFOADDR)                    | 136                       |

| Transmit Function Address (TXFUNCADDR)                        | 137                       |

| Transmit Hub Address (TXHUBADDR)                              | 137                       |

| Transmit Hub Port (TXHUBPORT)                                 | 137                       |

| Receive Function Address (RXFUNCADDR)                         | 138                       |

| Receive Hub Address (RXHUBADDR)                               | 138                       |

| Receive Hub Port (RXHUBPORT)                                  | 138                       |

|                                                               | Count 0 Register (COUNT0) |

## List of Figures

| 1  | Functional Block Diagram                                             | 15  |  |  |

|----|----------------------------------------------------------------------|-----|--|--|

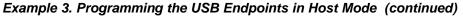

| 2  | Interrupt Service Routine Flow Chart                                 |     |  |  |

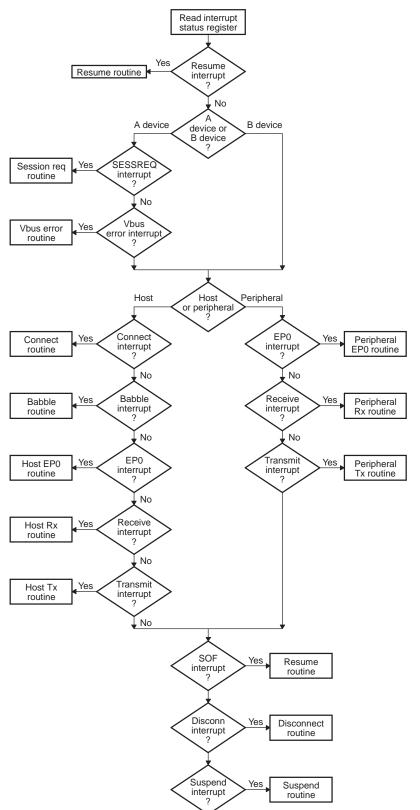

| 3  | CPU Actions at Transfer Phases                                       |     |  |  |

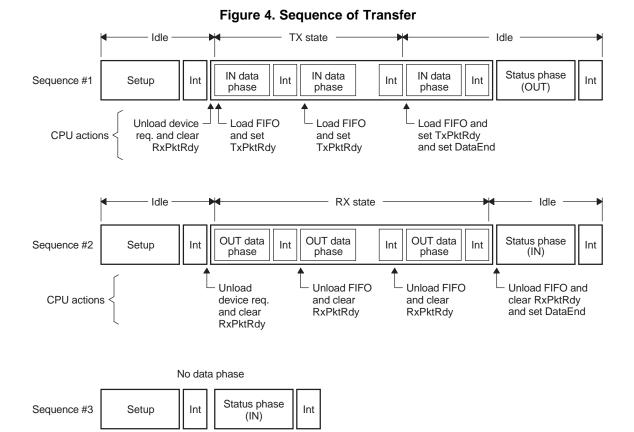

| 4  | Sequence of Transfer                                                 | 31  |  |  |

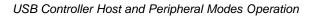

| 5  | Service Endpoint 0 Flow Chart                                        |     |  |  |

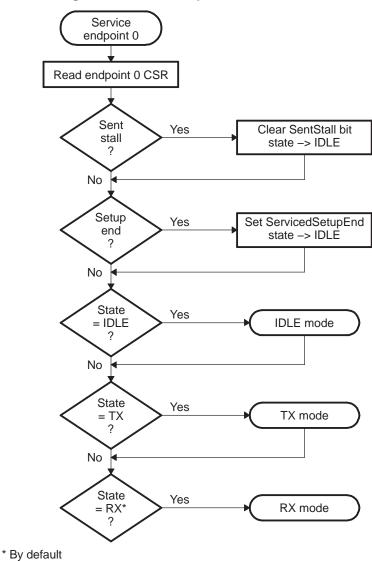

| 6  | IDLE Mode Flow Chart                                                 |     |  |  |

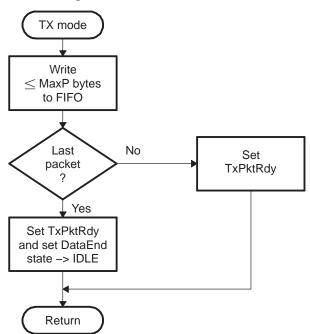

| 7  | TX Mode Flow Chart                                                   |     |  |  |

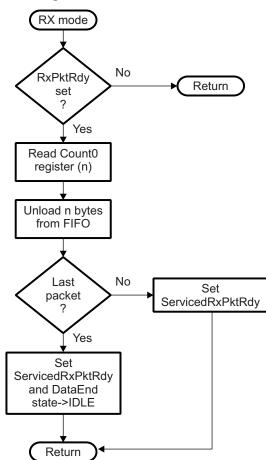

| 8  | RX Mode Flow Chart                                                   |     |  |  |

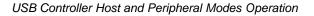

| 9  | Setup Phase of a Control Transaction Flow Chart                      |     |  |  |

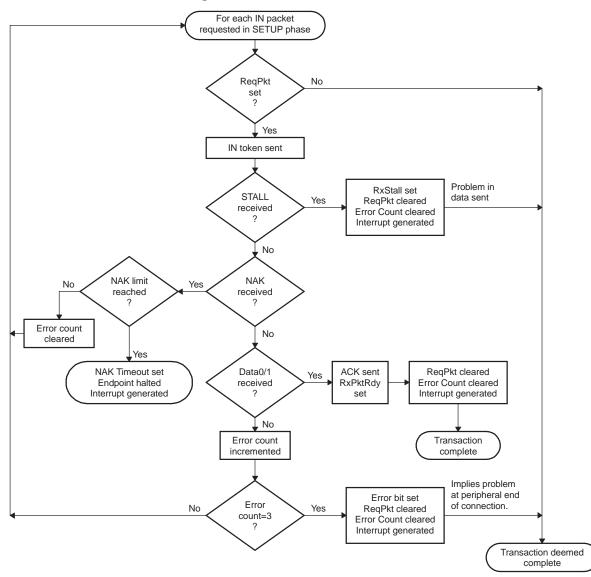

| 10 | IN Data Phase Flow Chart                                             |     |  |  |

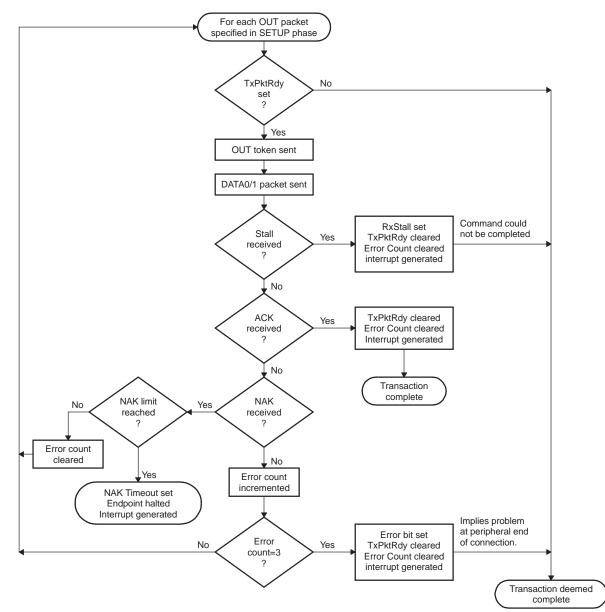

| 11 | OUT Data Phase Flow Chart                                            |     |  |  |

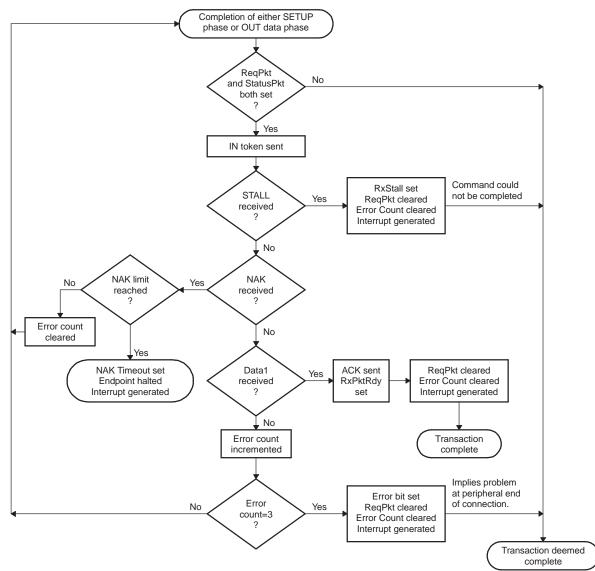

| 12 | Completion of SETUP or OUT Data Phase Flow Chart                     |     |  |  |

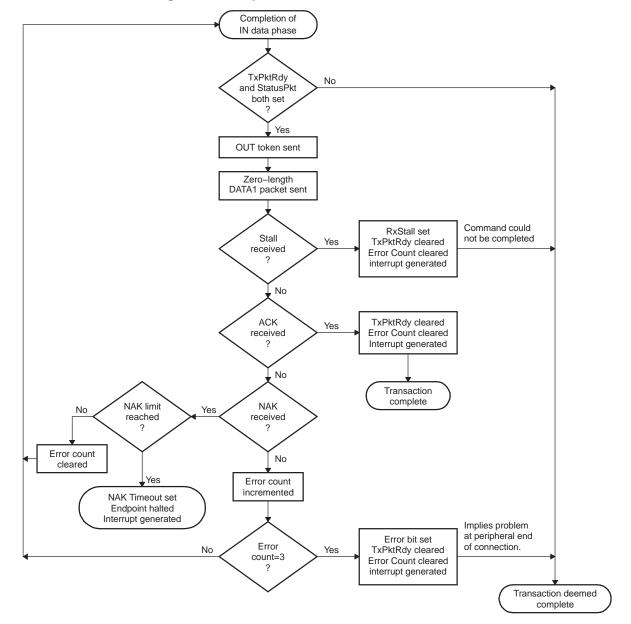

| 13 | Completion of IN Data Phase Flow Chart                               |     |  |  |

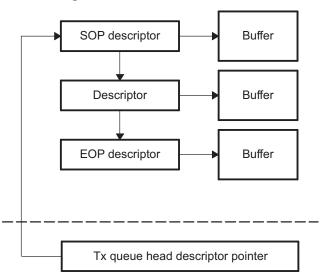

| 14 | Tx Queue Flow Chart                                                  |     |  |  |

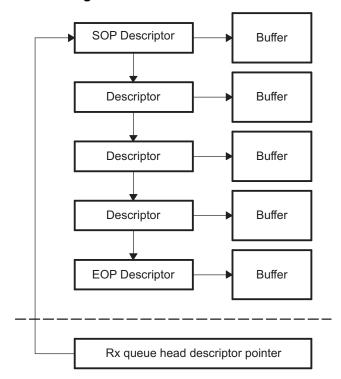

| 15 | Rx Queue Flow Chart                                                  | 66  |  |  |

| 16 | Control Register (CTRLR)                                             | 80  |  |  |

| 17 | Status Register (STATR).                                             |     |  |  |

| 18 | RNDIS Register (RNDISR)                                              |     |  |  |

| 19 | Auto Request Register (AUTOREQ)                                      | 82  |  |  |

| 20 | USB Interrupt Source Register (INTSRCR)                              |     |  |  |

| 21 | USB Interrupt Source Set Register (INTSETR)                          |     |  |  |

| 22 | USB Interrupt Source Clear Register (INTCLRR)                        |     |  |  |

| 23 | USB Interrupt Mask Register (INTMSKR)                                |     |  |  |

| 24 | USB Interrupt Mask Set Register (INTMSKSETR)                         |     |  |  |

| 25 | USB Interrupt Mask Clear Register (INTMSKCLRR)                       | 88  |  |  |

| 26 | USB Interrupt Source Masked Register (INTMASKEDR)                    | 89  |  |  |

| 27 | USB End of Interrupt Register (EOIR)                                 |     |  |  |

| 28 | USB Interrupt Vector Register (INTVECTR)                             | 90  |  |  |

| 29 | Transmit CPPI Control Register (TCPPICR)                             | 91  |  |  |

| 30 | Transmit CPPI Teardown Register (TCPPITDR)                           | 91  |  |  |

| 31 | Transmit CPPI DMA Controller End of Interrupt Register (TCPPIEOIR)   | 92  |  |  |

| 32 | Transmit CPPI DMA Controller Interrupt Vector Register (TCPPIIVECTR) | 92  |  |  |

| 33 | Transmit CPPI Masked Status Register (TCPPIMSKSR)                    | 93  |  |  |

| 34 | Transmit CPPI Raw Status Register (TCPPIRAWSR)                       | 93  |  |  |

| 35 | Transmit CPPI Interrupt Enable Set Register (TCPPIIENSETR)           | 94  |  |  |

| 36 | Transmit CPPI Interrupt Enable Clear Register (TCPPIIENCLRR)         | 94  |  |  |

| 37 | Receive CPPI Control Register (RCPPICR)                              | 95  |  |  |

| 38 | Receive CPPI Masked Status Register (RCPPIMSKSR)                     | 95  |  |  |

| 39 | Receive CPPI Raw Status Register (RCPPIRAWSR)                        | 96  |  |  |

| 40 | Receive CPPI Interrupt Enable Set Register (RCPPIENSETR)             | 96  |  |  |

| 41 | Receive CPPI Interrupt Enable Clear Register (RCPPIIENCLRR)          | 97  |  |  |

| 42 | Receive Buffer Count 0 Register (RBUFCNT0)                           |     |  |  |

| 43 | Receive Buffer Count 1 Register (RBUFCNT1)                           | 98  |  |  |

| 44 | Receive Buffer Count 2 Register (RBUFCNT2)                           | 98  |  |  |

| 45 | Receive Buffer Count 3 Register (RBUFCNT3)                           |     |  |  |

| 46 | Transmit CPPI DMA State Word 0 (TCPPIDMASTATEW0)                     | 99  |  |  |

| 47 | Transmit CPPI DMA State Word 1 (TCPPIDMASTATEW1)                     |     |  |  |

| 48 | Transmit CPPI DMA State Word 2 (TCPPIDMASTATEW2)                     |     |  |  |

| 49 | Transmit CPPI DMA State Word 3 (TCPPIDMASTATEW3)                     |     |  |  |

| 50 | Transmit CPPI DMA State Word 4 (TCPPIDMASTATEW4)                     |     |  |  |

| 51 | Transmit CPPI DMA State Word 5 (TCPPIDMASTATEW5)                     |     |  |  |

| 52 | Transmit CPPI Completion Pointer (TCPPICOMPPTR)                      | 104 |  |  |

| <b>F</b> 0 |                                                                                |  |  |  |  |  |

|------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| 53         | Receive CPPI DMA State Word 0 (RCPPIDMASTATEW0)                                |  |  |  |  |  |

| 54         | Receive CPPI DMA State Word 1 (RCPPIDMASTATEW1) 1                              |  |  |  |  |  |

| 55         | Receive CPPI DMA State Word 2 (RCPPIDMASTATEW2) 1                              |  |  |  |  |  |

| 56         | Receive CPPI DMA State Word 3 (RCPPIDMASTATEW3)                                |  |  |  |  |  |

| 57         | Receive CPPI DMA State Word 4 (RCPPIDMASTATEW4)                                |  |  |  |  |  |

| 58         | Receive CPPI DMA State Word 5 (RCPPIDMASTATEW5)                                |  |  |  |  |  |

| 59         | Receive CPPI DMA State Word 6 (RCPPIDMASTATEW6)                                |  |  |  |  |  |

| 60         | Receive CPPI Completion Pointer (RCPPICOMPPTR)                                 |  |  |  |  |  |

| 61         | Function Address Register (FADDR)                                              |  |  |  |  |  |

| 62         | Power Management Register (POWER)                                              |  |  |  |  |  |

| 63         | Interrupt Register for Endpoint 0 Plus Tx Endpoints 1 to 4 (INTRTX)            |  |  |  |  |  |

| 64         | Interrupt Register for Receive Endpoints 1 to 4 (INTRRX)                       |  |  |  |  |  |

| 65         | Interrupt Enable Register for INTRTX (INTRTXE)                                 |  |  |  |  |  |

| 66         | Interrupt Enable Register for INTRRX (INTRRXE)                                 |  |  |  |  |  |

| 67         | Interrupt Register for Common USB Interrupts (INTRUSB)                         |  |  |  |  |  |

| 68         | Interrupt Enable Register for INTRUSB (INTRUSBE)                               |  |  |  |  |  |

| 69         | Frame Number Register (FRAME)                                                  |  |  |  |  |  |

| 70         | Index Register for Selecting the Endpoint Status and Control Registers (INDEX) |  |  |  |  |  |

| 71         | Register to Enable the USB 2.0 Test Modes (TESTMODE)                           |  |  |  |  |  |

| 72         | Maximum Packet Size for Peripheral/Host Transmit Endpoint (TXMAXP)             |  |  |  |  |  |

| 73         | Control Status Register for Endpoint 0 in Peripheral Mode (PERI_CSR0)          |  |  |  |  |  |

|            |                                                                                |  |  |  |  |  |

| 74<br>75   | Control Status Register for Endpoint 0 in Host Mode (HOST_CSR0)                |  |  |  |  |  |

| 75         | Control Status Register for Peripheral Transmit Endpoint (PERI_TXCSR)          |  |  |  |  |  |

| 76         | Control Status Register for Host Transmit Endpoint (HOST_TXCSR)                |  |  |  |  |  |

| 77         | Maximum Packet Size for Peripheral Host Receive Endpoint (RXMAXP)              |  |  |  |  |  |

| 78         | Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR) 1         |  |  |  |  |  |

| 79         | Control Status Register for Host Receive Endpoint (HOST_RXCSR)                 |  |  |  |  |  |

| 80         | Count 0 Register (COUNT0) 1                                                    |  |  |  |  |  |

| 81         | Receive Count Register (RXCOUNT)                                               |  |  |  |  |  |

| 82         | Type Register (Host mode only) (HOST_TYPE0)                                    |  |  |  |  |  |

| 83         | Transmit Type Register (Host mode only) (HOST_TXTYPE)                          |  |  |  |  |  |

| 84         | NAKLimit0 Register (Host mode only) (HOST_NAKLIMIT0)                           |  |  |  |  |  |

| 85         | Transmit Interval Register (Host mode only) (HOST_TXINTERVAL)                  |  |  |  |  |  |

| 86         | Receive Type Register (Host mode only) (HOST_RXTYPE)                           |  |  |  |  |  |

| 87         | Receive Interval Register (Host mode only) (HOST_RXINTERVAL)                   |  |  |  |  |  |

| 88         | Configuration Data Register (CONFIGDATA)                                       |  |  |  |  |  |

| 89         | Transmit and Receive FIFO Register for Endpoint 0 (FIFO0)                      |  |  |  |  |  |

| 90         | Transmit and Receive FIFO Register for Endpoint 1 (FIFO1)                      |  |  |  |  |  |

| 91         | Transmit and Receive FIFO Register for Endpoint 2 (FIFO2)                      |  |  |  |  |  |

| 92         | Transmit and Receive FIFO Register for Endpoint 3 (FIFO3)                      |  |  |  |  |  |

| 93         | Transmit and Receive FIFO Register for Endpoint 4 (FIFO4)                      |  |  |  |  |  |

| 94         | OTG Device Control Register (DEVCTL).                                          |  |  |  |  |  |

| 95         | OTG Device Control Register (DEVCTL)<br>Transmit Endpoint FIFO Size (TXFIFOSZ) |  |  |  |  |  |

| 96         |                                                                                |  |  |  |  |  |

|            | Receive Endpoint FIFO Size (RXFIFOSZ)                                          |  |  |  |  |  |

| 97<br>08   | Transmit Endpoint FIFO Address (TXFIFOADDR)                                    |  |  |  |  |  |

| 98         | Receive Endpoint FIFO Address (RXFIFOADDR)                                     |  |  |  |  |  |

| 99         | Transmit Function Address (TXFUNCADDR)                                         |  |  |  |  |  |

| 100        | Transmit Hub Address (TXHUBADDR)                                               |  |  |  |  |  |

| 101        | Transmit Hub Port (TXHUBPORT) 1                                                |  |  |  |  |  |

| 102        | Receive Function Address (RXFUNCADDR)                                          |  |  |  |  |  |

| 103        | Receive Hub Address (RXHUBADDR)                                                |  |  |  |  |  |

## List of Tables

| 1  | USB Terminal Functions                                                                  | 23  |

|----|-----------------------------------------------------------------------------------------|-----|

| 2  | PERI_TXCSR Register Bit Configuration for Bulk IN Transactions                          |     |

| 3  | PERI_RXCSR Register Bit Configuration for Bulk OUT Transactions                         |     |

| 4  | PERI_TXCSR Register Bit Configuration for Isochronous IN Transactions                   |     |

| 5  | PERI_RXCSR Register Bit Configuration for Isochronous OUT Transactions                  |     |

| 6  | Transmit Buffer Descriptor Word 0                                                       |     |

| 7  | Transmit Buffer Descriptor Word 1                                                       |     |

| 8  | Transmit Buffer Descriptor Word 2                                                       |     |

| 9  | Transmit Buffer Descriptor Word 3                                                       |     |

| 10 | Receive Buffer Descriptor Word 0                                                        |     |

| 11 | Receive Buffer Descriptor Word 1                                                        |     |

| 12 | Receive Buffer Descriptor Word 2                                                        |     |

| 13 | Receive Buffer Descriptor Word 3                                                        |     |

| 14 | Interrupts Generated by the USB Controller                                              |     |

| 15 | USB Interrupt Conditions                                                                |     |

| 16 | Universal Serial Bus (USB) Registers                                                    |     |

| 17 | Control Register (CTRLR) Field Descriptions                                             |     |

| 18 | Status Register (STATR) Field Descriptions                                              |     |

| 19 | RNDIS Register (RNDISR) Field Descriptions                                              |     |

| 20 | Auto Request Register (AUTOREQ) Field Descriptions                                      |     |

| 21 | USB Interrupt Source Register (INTSRCR) Field Descriptions                              |     |

| 22 | USB Interrupt Source Set Register (INTSETR) Field Descriptions                          | 84  |

| 23 | USB Interrupt Source Clear Register (INTCLRR) Field Descriptions                        | 85  |

| 24 | USB Interrupt Mask Register (INTMSKR) Field Descriptions                                | 86  |

| 25 | USB Interrupt Mask Set Register (INTMSKSETR) Field Descriptions                         | 87  |

| 26 | USB Interrupt Mask Clear Register (INTMSKCLRR) Field Descriptions                       | 88  |

| 27 | USB Interrupt Source Masked Register (INTMASKEDR) Field Descriptions                    | 89  |

| 28 | USB End of Interrupt Register (EOIR) Field Descriptions                                 | 90  |

| 29 | USB Interrupt Vector Register (INTVECTR) Field Descriptions                             | 90  |

| 30 | Transmit CPPI Control Register (TCPPICR) Field Descriptions                             | 91  |

| 31 | Transmit CPPI Teardown Register (TCPPITDR) Field Descriptions                           | 91  |

| 32 | Transmit CPPI DMA Controller End of Interrupt Register (TCPPIEOIR) Field Descriptions   | 92  |

| 33 | Transmit CPPI DMA Controller Interrupt Vector Register (TCPPIIVECTR) Field Descriptions | 92  |

| 34 | Transmit CPPI Masked Status Register (TCPPIMSKSR) Field Descriptions                    | 93  |

| 35 | Transmit CPPI Raw Status Register (TCPPIRAWSR) Field Descriptions                       | 93  |

| 36 | Transmit CPPI Interrupt Enable Set Register (TCPPIIENSETR) Field Descriptions           | 94  |

| 37 | Transmit CPPI Interrupt Enable Clear Register (TCPPIIENCLRR) Field Descriptions         | 94  |

| 38 | Receive CPPI Control Register (RCPPICR) Field Descriptions                              |     |

| 39 | Receive CPPI Masked Status Register (RCPPIMSKSR) Field Descriptions                     | 95  |

| 40 | Receive CPPI Raw Status Register (RCPPIRAWSR) Field Descriptions                        |     |

| 41 | Receive CPPI Interrupt Enable Set Register (RCPPIENSETR) Field Descriptions             | 96  |

| 42 | Receive CPPI Interrupt Enable Clear Register (RCPPIIENCLRR) Field Descriptions          | 97  |

| 43 | Receive Buffer Count 0 Register (RBUFCNT0) Field Descriptions                           | 97  |

| 44 | Receive Buffer Count 1 Register (RBUFCNT1) Field Descriptions                           | 98  |

| 45 | Receive Buffer Count 2 Register (RBUFCNT2) Field Descriptions                           | 98  |

| 46 | Receive Buffer Count 3 Register (RBUFCNT3) Field Descriptions                           |     |

| 47 | Transmit CPPI DMA State Word 0 (TCPPIDMASTATEW0) Field Descriptions                     |     |

| 48 | Transmit CPPI DMA State Word 1 (TCPPIDMASTATEW1) Field Descriptions                     |     |

| 49 | Transmit CPPI DMA State Word 2 (TCPPIDMASTATEW2) Field Descriptions                     | 101 |

| 50       | Transmit CPPI DMA State Word 3 (TCPPIDMASTATEW3) Field Descriptions                                                                      | 1 |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|

| 50<br>51 | Transmit CPPI DMA State Word 3 (TCPPIDMASTATEW3) Field Descriptions                                                                      |   |  |  |  |

| 52       | Transmit CPPI DMA State Word 5 (TCPPIDMASTATEW4) Field Descriptions                                                                      |   |  |  |  |

| 52<br>53 | Transmit CPPI Completion Pointer (TCPPICOMPPTR) Field Descriptions                                                                       |   |  |  |  |

| 53<br>54 | Receive CPPI DMA State Word 0 (RCPPIDMASTATEW0) Field Descriptions                                                                       |   |  |  |  |

| 55       | Receive CPPI DMA State Word 1 (RCPPIDMASTATEWO) Field Descriptions                                                                       |   |  |  |  |

| 56       |                                                                                                                                          |   |  |  |  |

| 50<br>57 | Receive CPPI DMA State Word 2 (RCPPIDMASTATEW2) Field Descriptions                                                                       |   |  |  |  |

| 58       | Receive CPPI DMA State Word 3 (RCPPIDMASTATEW3) Field Descriptions<br>Receive CPPI DMA State Word 4 (RCPPIDMASTATEW4) Field Descriptions |   |  |  |  |

| 59       | Receive CPPI DMA State Word 5 (RCPPIDMASTATEW5) Field Descriptions                                                                       |   |  |  |  |

| 60       | Receive CPPI DMA State Word 6 (RCPPIDMASTATEW6) Field Descriptions                                                                       |   |  |  |  |

| 61       | Receive CPPI Completion Pointer (RCPPICOMPPTR) Field Descriptions                                                                        |   |  |  |  |

| 62       | Function Address Register (FADDR) Field Descriptions                                                                                     |   |  |  |  |

| 62<br>63 | Power Management Register (POWER) Field Descriptions                                                                                     |   |  |  |  |

| 64       | Interrupt Register for Endpoint 0 Plus Transmit Endpoints 1 to 4 (INTRTX) Field Descriptions                                             |   |  |  |  |

|          |                                                                                                                                          |   |  |  |  |

| 65<br>66 | Interrupt Register for Receive Endpoints 1 to 4 (INTRRX) Field Descriptions                                                              |   |  |  |  |

|          | Interrupt Enable Register for INTRTX (INTRTXE) Field Descriptions                                                                        |   |  |  |  |

| 67<br>68 | Interrupt Enable Register for INTRRX (INTRRXE) Field Descriptions                                                                        |   |  |  |  |

| 68<br>60 | Interrupt Register for Common USB Interrupts (INTRUSB) Field Descriptions                                                                |   |  |  |  |

| 69<br>70 | Interrupt Enable Register for INTRUSB (INTRUSBE) Field Descriptions                                                                      |   |  |  |  |

| 70       | Frame Number Register (FRAME) Field Descriptions                                                                                         |   |  |  |  |

| 71<br>72 | Index Register for Selecting the Endpoint Status and Control Registers (INDEX) Field Descriptions                                        |   |  |  |  |

| 72<br>72 | Register to Enable the USB 2.0 Test Modes (TESTMODE) Field Descriptions                                                                  |   |  |  |  |

| 73       | Maximum Packet Size for Peripheral/Host Transmit Endpoint (TXMAXP) Field Descriptions                                                    |   |  |  |  |

| 74<br>75 | Control Status Register for Endpoint 0 in Peripheral Mode (PERI_CSR0) Field Descriptions                                                 |   |  |  |  |

| 75       | Control Status Register for Endpoint 0 in Host Mode (HOST_CSR0) Field Descriptions                                                       |   |  |  |  |

| 76       | Control Status Register for Peripheral Transmit Endpoint (PERI_TXCSR) Field Descriptions                                                 |   |  |  |  |

| 77       | Control Status Register for Host Transmit Endpoint (HOST_TXCSR) Field Descriptions                                                       |   |  |  |  |

| 78       | Maximum Packet Size for Peripheral Host Receive Endpoint (RXMAXP) Field Descriptions                                                     |   |  |  |  |

| 79       | Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR) Field Descriptions                                                  |   |  |  |  |

| 80       | Control Status Register for Host Receive Endpoint (HOST_RXCSR) Field Descriptions                                                        |   |  |  |  |

| 81       | Count 0 Register (COUNT0) Field Descriptions                                                                                             |   |  |  |  |

| 82       | Receive Count Register (RXCOUNT) Field Descriptions                                                                                      |   |  |  |  |

| 83       | Type Register (Host mode only) (HOST_TYPE0) Field Descriptions                                                                           |   |  |  |  |

| 84       | Transmit Type Register (Host mode only) (HOST_TXTYPE) Field Descriptions                                                                 |   |  |  |  |

| 85       | NAKLimit0 Register (Host mode only) (HOST_NAKLIMIT0) Field Descriptions                                                                  |   |  |  |  |

| 86       | Transmit Interval Register (Host mode only) (HOST_TXINTERVAL) Field Descriptions                                                         |   |  |  |  |

| 87       | Receive Type Register (Host mode only) (HOST_RXTYPE) Field Descriptions                                                                  |   |  |  |  |

| 88       | Receive Interval Register (Host mode only) (HOST_RXINTERVAL) Field Descriptions                                                          |   |  |  |  |

| 89       | Configuration Data Register (CONFIGDATA) Field Descriptions                                                                              |   |  |  |  |

| 90       | Transmit and Receive FIFO Register for Endpoint 0 (FIFO0) Field Descriptions                                                             |   |  |  |  |

| 91       | Transmit and Receive FIFO Register for Endpoint 1 (FIFO1) Field Descriptions                                                             |   |  |  |  |

| 92       | Transmit and Receive FIFO Register for Endpoint 2 (FIFO2) Field Descriptions                                                             |   |  |  |  |

| 93       | Transmit and Receive FIFO Register for Endpoint 3 (FIFO3) Field Descriptions                                                             |   |  |  |  |

| 94       | Transmit and Receive FIFO Register for Endpoint 4 (FIFO4) Field Descriptions                                                             |   |  |  |  |

| 95       | OTG Device Control Register (DEVCTL) Field Descriptions                                                                                  |   |  |  |  |

| 96       | Transmit Endpoint FIFO Size (TXFIFOSZ) Field Descriptions                                                                                |   |  |  |  |

| 97       | Receive Endpoint FIFO Size (RXFIFOSZ) Field Descriptions                                                                                 |   |  |  |  |

| 98       | Transmit Endpoint FIFO Address (TXFIFOADDR) Field Descriptions                                                                           |   |  |  |  |

| 99       | Receive Endpoint FIFO Address (RXFIFOADDR) Field Descriptions                                                                            | 1 |  |  |  |

| 100      | Transmit Function Address (TXFUNCADDR) Field Descriptions                                                                                |   |  |  |  |

| 101 | Transmit Hub Address (TXHUBADDR) Field Descriptions      | 137 |

|-----|----------------------------------------------------------|-----|

| 102 | Transmit Hub Port (TXHUBPORT) Field Descriptions         | 137 |

| 103 | Receive Function Address (RXFUNCADDR) Field Descriptions | 138 |

| 104 | Receive Hub Address (RXHUBADDR) Field Descriptions       | 138 |

| 105 | Receive Hub Port (RXHUBPORT) Field Descriptions          | 138 |

Preface SPRUFY9–July 2008

This document describes the Universal Serial Bus (USB) on the TMS320DM335 Digital Media System-on-Chip (DMSoC).

## Notational Conventions

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

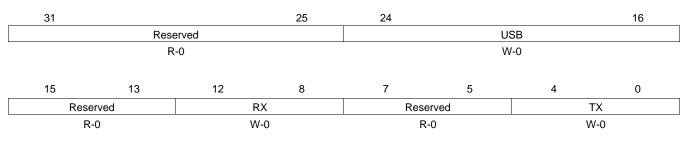

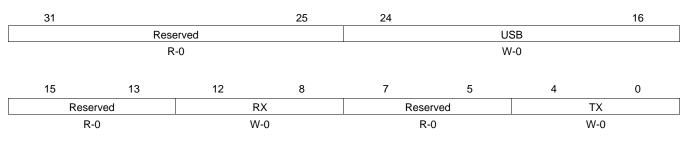

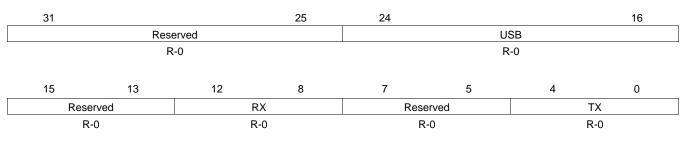

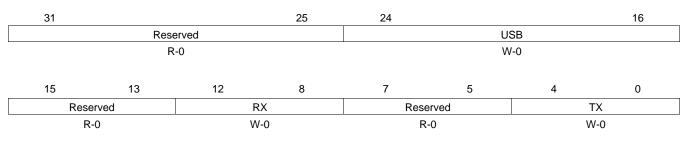

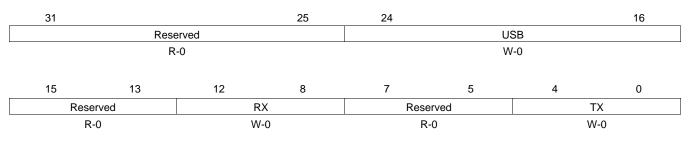

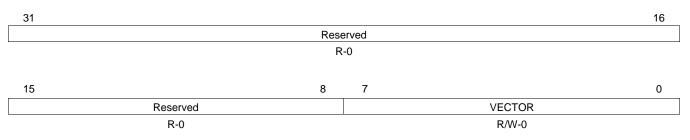

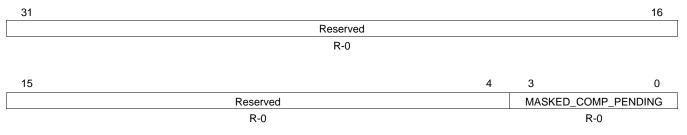

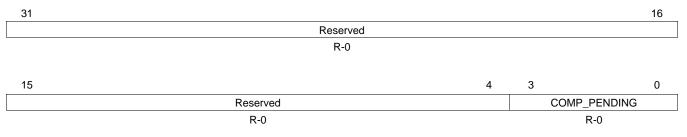

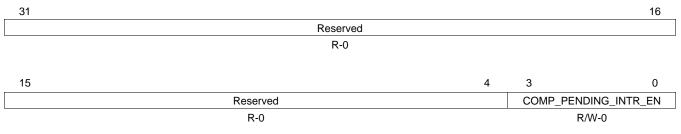

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

## **Related Documentation from Texas Instruments**

The following documents describe the TMS320DM335 Digital Media System-on-Chip (DMSoC). Copies of these documents are available on the internet at <u>www.ti.com</u>.

- SPRUFX7 TMS320DM335 Digital Media System-on-Chip (DMSoC) ARM Subsystem Reference Guide This document describes the ARM Subsystem in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The ARM subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In general, the ARM is responsible for configuration and control of the device; including the components of the ARM Subsystem, the peripherals, and the external memories.

- <u>SPRUFX8</u> TMS320DM335 Digital Media System-on-Chip (DMSoC) Video Processing Front End (VPFE) Reference Guide This document describes the Video Processing Front End (VPFE) in the TMS320DM335 Digital Media System-on-Chip (DMSoC).

- SPRUFX9 TMS320DM335 Digital Media System-on-Chip (DMSoC) Video Processing Back End (VPBE) Reference Guide This document describes the Video Processing Back End (VPBE) in the TMS320DM335 Digital Media System-on-Chip (DMSoC).

- SPRUFYO TMS320DM335 Digital Media System-on-Chip (DMSoC) 64-bit Timer Reference Guide This document describes the operation of the software-programmable 64-bit timers in the TMS320DM335 Digital Media System-on-Chip (DMSoC). Timer 0, Timer 1, and Timer 3 are used as general-purpose (GP) timers and can be programmed in 64-bit mode, dual 32-bit unchained mode, or dual 32-bit chained mode; Timer 2 is used only as a watchdog timer. The GP timer modes can be used to generate periodic interrupts or enhanced direct memory access (EDMA) synchronization events and Real Time Output (RTO) events (Timer 3 only). The watchdog timer mode is used to provide a recovery mechanism for the device in the event of a fault condition, such as a non-exiting code loop.

SPRUFY1 — TMS320DM335 Digital Media System-on-Chip (DMSoC) Serial Peripheral Interface (SPI) Reference Guide This document describes the serial peripheral interface (SPI) in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The SPI is a high-speed synchronous serial input/output port that allows a serial bit stream of programmed length (1 to 16 bits) to be shifted into and out of the device at a programmed bit-transfer rate. The SPI is normally used for communication between the DMSoC and external peripherals. Typical applications include an interface to external I/O or peripheral expansion via devices such as shift registers, display drivers, SPI EPROMs and analog-to-digital converters.

SPRUFY2 — TMS320DM335 Digital Media System-on-Chip (DMSoC) Universal Asynchronous Receiver/Transmitter (UART) Reference Guide This document describes the universal asynchronous receiver/transmitter (UART) peripheral in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The UART peripheral performs serial-to-parallel conversion on data received from a peripheral device, and parallel-to-serial conversion on data received from the CPU.

SPRUFY3 — TMS320DM335 Digital Media System-on-Chip (DMSoC) Inter-Integrated Circuit (I2C) Peripheral Reference Guide This document describes the inter-integrated circuit (I2C) peripheral in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The I2C peripheral provides an interface between the DMSoC and other devices compliant with the I2C-bus specification and connected by way of an I2C-bus. External components attached to this 2-wire serial bus can transmit and receive up to 8-bit wide data to and from the DMSoC through the I2C peripheral. This document assumes the reader is familiar with the I2C-bus specification.

- <u>SPRUFY5</u> TMS320DM335 Digital Media System-on-Chip (DMSoC) Multimedia Card (MMC)/Secure Digital (SD) Card Controller Reference Guide This document describes the multimedia card (MMC)/secure digital (SD) card controller in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The MMC/SD card is used in a number of applications to provide removable data storage. The MMC/SD controller provides an interface to external MMC and SD cards. The communication between the MMC/SD controller and MMC/SD card(s) is performed by the MMC/SD protocol.

- SPRUFY6 TMS320DM335 Digital Media System-on-Chip (DMSoC) Pulse-Width Modulator (PWM) Reference Guide This document describes the pulse-width modulator (PWM) peripheral in the TMS320DM335 Digital Media System-on-Chip (DMSoC).

- SPRUFY7 TMS320DM335 Digital Media System-on-Chip (DMSoC) Real-Time Out (RTO) Controller Reference Guide This document describes the Real Time Out (RTO) controller in the TMS320DM335 Digital Media System-on-Chip (DMSoC).

- <u>SPRUFY8</u> TMS320DM335 Digital Media System-on-Chip (DMSoC) General-Purpose Input/Output (GPIO) Reference Guide This document describes the general-purpose input/output (GPIO) peripheral in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The GPIO peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an input, you can detect the state of the input by reading the state of an internal register. When configured as an output, you can write to an internal register to control the state driven on the output pin.

- SPRUFY9 TMS320DM335 Digital Media System-on-Chip (DMSoC) Universal Serial Bus (USB) Controller Reference Guide This document describes the universal serial bus (USB) controller in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The USB controller supports data throughput rates up to 480 Mbps. It provides a mechanism for data transfer between USB devices and also supports host negotiation.

- SPRUFZ0 TMS320DM335 Digital Media System-on-Chip (DMSoC) Enhanced Direct Memory Access (EDMA) Controller Reference Guide This document describes the operation of the enhanced direct memory access (EDMA3) controller in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The EDMA controller's primary purpose is to service user-programmed data transfers between two memory-mapped slave endpoints on the DMSoC.

SPRUFZ1 — TMS320DM335 Digital Media System-on-Chip (DMSoC) Asynchronous External Memory Interface (EMIF) Reference Guide This document describes the asynchronous external memory interface (EMIF) in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The EMIF supports a glueless interface to a variety of external devices.

SPRUFZ2 — TMS320DM335 Digital Media System-on-Chip (DMSoC) DDR2/Mobile DDR (DDR2/mDDR) Memory Controller Reference Guide This document describes the DDR2/mDDR memory controller in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The DDR2/mDDR memory controller is used to interface with JESD79D-2A standard compliant DDR2 SDRAM and mobile DDR devices.

SPRUFZ3 — TMS320DM335 Digital Media System-on-Chip (DMSoC) Audio Serial Port (ASP) Reference Guide This document describes the operation of the audio serial port (ASP) audio interface in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The primary audio modes that are supported by the ASP are the AC97 and IIS modes. In addition to the primary audio modes, the ASP supports general serial port receive and transmit operation, but is not intended to be used as a high-speed interface.

Trademarks

## Universal Serial Bus (USB) Controller

## 1 Introduction

This document describes the universal serial bus (USB) controller in the TMS320DM335 Digital Media System-on-Chip (DMSoC). The controller complies with the USB 2.0 standard high-speed and full-speed functions and low-speed, full-speed, and high-speed limited host mode operations. It also includes support for the Session Request and Host Negotiation Protocols used in point-to-point communications, details of which are given in the USB On-The-Go supplement to the USB 2.0 specification. In addition, the four test modes for high-speed operation described in the USB 2.0 specification. It also allows options that allow it to be forced into full-speed mode, high-speed mode, or host mode which may be used in helping debug PHY problems in hardware.

## 1.1 Purpose of the Peripheral

The USB controller supports data throughput rates up to 480 Mbps. It provides a mechanism for data transfer between USB devices and also supports host negotiation.

## 1.2 Features

The USB has the following features:

- Supports USB 2.0 peripheral at High Speed (480 Mbps) and Full Speed (12 Mbps)

- Supports USB 2.0 host at High Speed (480 Mbps), Full Speed (12 Mbps), and Low Speed (1.5 Mbps)

- Supports 4 simultaneous RX and TX endpoints, more can be supported by dynamically switching

- Each endpoint can support all transfer types (control, bulk, interrupt, and isochronous)

- Supports USB extensions for Session Request (SRP) and Host Negotiation (HNP)

- Includes a 4K endpoint FIFO RAM, and supports programmable FIFO sizes

- External 5V power supply for VBUS can be controlled through I2C

- Includes a DMA controller that supports 4 TX and 4 RX DMA channels

- Includes RNDIS mode of DMA for accelerating RNDIS type protocols using short packet termination over USB

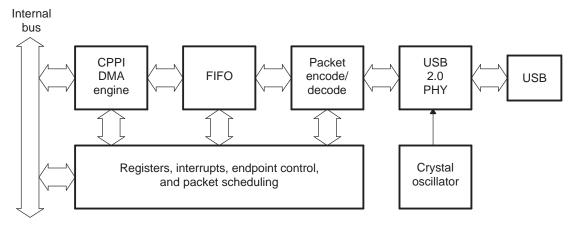

## 1.3 Functional Block Diagram

The USB functional block diagram is shown in Figure 1.

## Figure 1. Functional Block Diagram

## 1.4 Supported Use Case Examples

The USB supports the following user cases:

Detailed information about the architecture and operation of the USB controller follows in Section 2. Programming examples are also provided for each of the operational modes of the controller.

User Case 1: An example of how to initialize the USB controller

Example 1. Initializing the USB Controller

```

// Routine to initialize USB controller

void usb_init()

{

// local loop variable

int I;

// VBUS must be controlled externally. The following routine

// should perform whatever actions are required (if any) to

// turn off VBUS in the system.

vbus_off();

// Reset the USB controller

usbRegs->CTRLR = 0x0000001;

// Power on PHY and oscillator by clearing bits 2, 1, and 0 of USB_PHY_CTL

sysRegs->USB_PHY_CTRL = 0x00000D0;

//Clear all pending interrupts

usbRegs->INTCLRR = usbRegs->INTSRCR;

// Initialize CPPI DMA

usbReqs->RCPPICR = 0;

//Disable the RX DMA

usbRegs->TCPPICR = 0;

//Disable the TX DMA

// Initialize CPPI DMA state

for(I = 0; i<4; I++) {</pre>

usbRegs->CHANNEL[i].TCPPIDMASTATEW0 = 0;

usbRegs->CHANNEL[i].TCPPIDMASTATEW1 = 0;

usbRegs->CHANNEL[i].TCPPIDMASTATEW2 = 0;

usbRegs->CHANNEL[i].TCPPIDMASTATEW3 = 0;

usbRegs->CHANNEL[i].TCPPIDMASTATEW4 = 0;

usbReqs->CHANNEL[i].TCPPIDMASTATEW5 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW0 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW1 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW2 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW3 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW4 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW5 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW6 = 0;

}

}

```

User Case 2: An example of how to program the USB Endpoints in peripheral mode

#### Example 2. Programming the USB Endpoints in Peripheral Mode

```

// DMA channel number. Valid values are 0, 1, 2, or 3.

int CHAN NUM = 0;

// Fifo sizes: uncomment the desired size.

// This example uses 64-byte fifo.

// 8 bytes

// int fifosize = 0;

// 16 bytes

// 32 bytes

// int fifosize = 1;

// int fifosize = 2;

int fifosize = 3;

// 64 bytes

// 128 bytes

// int fifosize = 4;

// int fifosize = 5;

// 256 bytes

// int fifosize = 6;

// 512 bytes

// int fifosize = 7;

// 1024 bytes

// int fifosize = 8;

// 2048 bytes

// int fifosize = 9;

// 4096 bytes

// FIFO address. Leave 64-bytes for endpoint 0.

int fifo_start_address = 8;

// Uncomment the desired buffering. If double-buffer is selected, actual

// FIFO space will be twice the value listed above for fifosize.

// This example uses single buffer.

int double_buffer = 0; // Single-buffer

// int double_buffer = 1; // Double-buffer

// For maximum packet size this formula will usually work, but it can also be

// set to another value if needed. If non power of 2 value is needed (such as

// 1023) set it explicitly.

#define FIFO_MAXP 8*(1<<fifosize);</pre>

// Set the following variable to the device address.

int device address = 0;

// The following code should be run after receiving a USB reset from the host.

// Initialize the endpoint FIFO. RX and TX will be allocated the same sizes.

usbRegs->INDEX = CHAN_NUM+1;

usbRegs->RXFIFOSZ = fifosize | ((double_buffer & 1)<<4);

usbRegs->RXFIFOADDR = fifo_start_address;

fifosize | ((double_buffer & 1)<<4);</pre>

usbRegs->TXFIFOSZ =

usbRegs->TXFIFOADDR = fifo_start_address + (1<<(fifosize+double_buffer));

usbRegs->RXMAXP = FIFO_MAXP;

usbRegs->TXMAXP = FIFO_MAXP;

// Force Data Toggle is optional for interrupt traffic. Uncomment if needed.

// CSL_FINS(usbRegs->PERI_TXCSR,USB_PERI_TXCSR_FRCDATATOG,1);

// Uncomment below to configure the endpoint for ISO and not respond with a

// handshake packet.

// CSL_FINS(usbRegs->PERI_RXCSR,USB_PERI_RXCSR_ISO,1);

// CSL_FINS(usbRegs->PERI_TXCSR,USB_PERI_TXCSR_ISO,1);

// After receiving a successful set-address command, set the following register

// to the specified address immediately following the status stage.

USBREGS->FADDR = device_address;

```

```

Introduction

```

TEXAS INSTRUMENTS

www.ti.com

#### User Case 3: An example of how to program the USB endpoints in host mode

#### Example 3. Programming the USB Endpoints in Host Mode

```

// DMA channel number. Valid values are 0, 1, 2, or 3.

int CHAN NUM = 0;

// Fifo sizes: uncomment the desired size.

// This example uses 64-byte fifo.

// 8 bytes

// int fifosize = 0;

// 16 bytes

// 32 bytes

// int fifosize = 1;

// int fifosize = 2;

// 64 bytes

int fifosize = 3;

// 128 bytes

// int fifosize = 4;

// int fifosize = 5;

// 256 bytes

// int fifosize = 6;

// 512 bytes

// int fifosize = 7;

// 1024 bytes

// int fifosize = 8;

// 2048 bytes

// int fifosize = 9;

// 4096 bytes

// FIFO address. Leave 64-bytes for endpoint 0.

int fifo_start_address = 8;

// Uncomment the desired buffering. If double-buffer is selected, actual

// FIFO space will be twice the value listed above for fifosize.

// This example uses single buffer.

int double_buffer = 0; // Single-buffer

// int double_buffer = 1; // Double-buffer

// Set the following variable to the device endpoint type: CONTROL ISO BULK or IN

int device_protocol = BULK;

//int device_protocol = ISO;

//int device_protocol = INT;

// USB speeds

#define LOW SPEED 0

#define FULL_SPEED 1

#define HIGH_SPEED 2

// TXTYPE protocol

#define CONTROL 0

#define ISO 1

#define BULK 2

#define INT 3

// For maximum packet size this formula will usually work, but it can also be

// set to another value if needed. If non power of 2 value is needed (such as

// 1023) set it explicitly.

#define FIFO_MAXP 8*(1<<fifosize);</pre>

\ensuremath{{\prime}}\xspace // Set the following variable to the device address.

int device_address = 1;

// Set the following variable to the device endpoint number.

int device_ep = 1;

// Variable used for endpoint configuration

Uint8 type = 0;

// Variable to keep track of errors

int error = 0;

// The following code should be run after resetting the attached device

// Initialize the endpoint FIFO. RX and TX will be allocated the same sizes.

usbRegs->INDEX = CHAN_NUM+1;

usbRegs->RXFIFOSZ = fifosize | ((double_buffer & 1)<<4);

usbRegs->RXFIFOADDR = fifo_start_address;

usbRegs->TXFIFOSZ =

fifosize | ((double_buffer & 1)<<4);</pre>

usbRegs->TXFIFOADDR = fifo_start_address + (1<<(fifosize+double_buffer));

```

```

usbRegs->RXMAXP = FIFO_MAXP;

usbRegs->TXMAXP = FIFO_MAXP;

//Configure the endpoint

switch (device_speed) {

case LOW_SPEED : type = (3<<6) | ((device_protocol & 3) << 4) | (device_ep & 0xf); break;

case FULL_SPEED: type = (2<<6) | ((device_protocol & 3) << 4) | (device_ep & 0xf); break;

case HIGH_SPEED: type = (1<<6) | ((device_protocol & 3) << 4) | (device_ep & 0xf); break;</pre>

default:error++;

}

usbRegs->EPCSR[CHAN_NUM+1].HOST_TYPE0 = type; // TXTYPE

usbRegs->EPCSR[CHAN_NUM+1].HOST_RXTYPE = type;

// Set NAK limit / Polling interval (Interrupt & Iso protocols)

if ((device_protocol == INT) || (device_protocol == ISO)) {

// TX Polling interval

usbRegs->EPCSR[CHAN_NUM+1].HOST_NAKLIMIT0 = TXINTERVAL;

usbRegs->EPCSR[CHAN_NUM+1].HOST_RXINTERVAL = RXINTERVAL;

// RX Polling interval

} else {

usbRegs->EPCSR[CHAN_NUM+1].HOST_NAKLIMIT0 = 2;

// Frames to timeout from NAKs

usbRegs->EPCSR[CHAN_NUM+1].HOST_RXINTERVAL = 2;

// Frames to timeout from NAKs

}

//Set the address for transactions after SET ADDRESS successfully completed

usbRegs->EPTRG[CHAN_NUM+1].TXFUNCADDR = device_address;

usbRegs->EPTRG[CHAN_NUM+1].RXFUNCADDR = device_address;

```

Introduction

www.ti.com

User Case 4: An example of how to do host negotiation to support USB

If the HOSTREQ bit in the DEVCTL register is set, host negotiation is performed by the hardware when the device enters suspend mode. The bit is cleared when host negotiation is complete.

User Case 5: An example of how to program the USB DMA controller

#### Example 4. Programming the USB DMA Controller

```

// Number of DMA channels

#define NUM_CHANNEL 4

// Number of DMA buffers to allocate

#define RX BUFFERS 32

#define TX_BUFFERS 32

\ensuremath{{\prime}}\xspace // Memory region to place DMA buffers and descriptors

#define MEMORY_TARGET ".DDREMIF_0_BUF

// DMA defines

#define SOP

(Uint32) (1<<31)

#define EOP

(Uint32) (1<<30)

#define OWNER

(Uint32) (1<<29)

#define EOQ

(Uint32) (1<<28)

#define ZERO_BYTE (Uint32) (1<<23)</pre>

#define RX_ABORT (Uint32) (1<<19)</pre>

/ DMA channel configuration

#define CHO 0

#define CH1 1

#define CH2 2

#define CH3 3

// Loop variable

int I;

// Variable to keep track of errors

int error = 0i

// Variable to keep track of the number of descriptors built

int tx_desc[NUM_CHANNEL]; // Current TX Buffer descriptor[channel number]

int rx_desc[NUM_CHANNEL];

// Current RX Buffer descriptor[channel number]

// Separate data section for bufferDesc. NOTE: CPPI buffers MUST be aligned to 16-byte

boundaries.

#pragma DATA_SECTION(rx_bufferDesc, MEMORY_TARGET)

Uint32 rx_bufferDesc[NUM_CHANNEL][RX_BUFFERS];

#pragma DATA_SECTION(tx_bufferDesc, MEMORY_TARGET)

Uint32 tx_bufferDesc[NUM_CHANNEL][TX_BUFFERS];

\ensuremath{\prime\prime}\xspace Initialize CPPI DMA. This code is also included in the controller initialization.

usbRegs->RCPPICR = 0; //Disable the RX DMA

usbRegs->TCPPICR = 0;

//Disable the TX DMA

for(I = 0; i<NUM_CHANNEL;i++) { // Initialize CPPI DMA state</pre>

usbRegs->CHANNEL[i].TCPPIDMASTATEW0 = 0;

usbRegs->CHANNEL[i].TCPPIDMASTATEW1 = 0;

usbRegs->CHANNEL[i].TCPPIDMASTATEW2 = 0;

usbRegs->CHANNEL[i].TCPPIDMASTATEW3 = 0;

usbRegs->CHANNEL[i].TCPPIDMASTATEW4 = 0;

usbRegs -> CHANNEL[i].TCPPIDMASTATEW5 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW0 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW1 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW2 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW3 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW4 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW5 = 0;

usbRegs->CHANNEL[i].RCPPIDMASTATEW6 = 0;

tx_desc[i] = 0;

rx_desc[i] = 0;

```

}

www.ti.com

## Example 4. Programming the USB DMA Controller (continued)

```

// Routine to flush TX fifo.

\ensuremath{{//}} Must call this routine twice for double-buffered FIFO

void flush_tx_fifo(int ep) {

int index_save;

int status;

index_save = usbRegs->INDEX;

// Save the index to restore later

usbRegs->INDEX = ep;

// Set the index to the desired endpoint

status = usbRegs->PERI_TXCSR & 3; // Isolate the TxPktRdy and FIFONotEmpty bits

if (!(status)) {

// Nothing showing in FIFO

usbRegs->PERI_TXCSR |= 1;

// Set TxPktRdy in case there is a partial

packet already in FIFO

}

usbRegs->PERI_TXCSR = ((usbRegs->PERI_TXCSR & 0xFFFC) | 8); // Write TXCSR with flush

bit set, FIFONotEmpty=0, and TxPktRdy=0.

while (usbRegs->PERI_TXCSR & 8);

// Keep looping until the flush bit clears

usbRegs->INDEX = index_save;

// Restore the index to previous value

}

// Routine to start the TX DMA for a given channel

void start_tx_dma(int ch) {

// Must have at least one descriptor before turning on TX DMA

if (rx_desc[ch] < 1) {error++;} else {</pre>

//Flush FIFO (2 times in case it is double-buffered)

flush_tx_fifo(ch+1);

flush_tx_fifo(ch+1);

// Start the DMA

usbRegs->TCPPICR = 1; //Enable Tx CPPI DMA

usbReqs->CHANNEL[ch].TCPPIDMASTATEW0 = (Uint32)(&tx bufferDesc[ch][0]);

CSL_FINS(usbRegs->PERI_TXCSR,USB_PERI_TXCSR_DMAEN,1); // TXCSR, bit DMAReqEnab

}

}

// Routine to add a TX descriptor

void add_tx_descriptor(int ch, unsigned char * inBuf, int bytes) {

if ((bytes < 0) || (bytes >65535)) {bytes = 64; error++;}

// Link previous buffer to this one if this is not the first descriptor of the channel

if (tx_desc[ch] > 0) tx_bufferDesc[ch][4*(tx_desc[ch]-1)] =

(Uint32)(&tx_bufferDesc[ch][4*tx_desc[ch]]);

// Set up DMA buffer descriptors

tx_bufferDesc[ch][4*tx_desc[ch]+0] = (Uint32)(0x0000000);

// Next Descriptor pointer

// Buffer pointer

tx_bufferDesc[ch][4*tx_desc[ch]+2] = (0x0000 << 16) | bytes;</pre>

// [31:16] Buffer offset

[15:0] Buffer length

if (bytes == 0) bytes = ZERO_BYTE | 1;

// Set the ZERO_BYTE bit and size 1 byte

tx_bufferDesc[ch][4*tx_desc[ch]+3] = SOP | EOP | OWNER | bytes;

// [31]=SOP, [30]=EOP,

[29]=owner, [28]=EOQ, [23]=zero-byte, [19] = rxabort, [15:0]=packet length

// If DMA already enabled and has stopped, write this to the TX Queue head pointer

if ((usbRegs->TCPPICR == 1) && (usbRegs->CHANNEL[ch].TCPPIDMASTATEW0 == 0))

usbRegs->CHANNEL[ch].TCPPIDMASTATEW0 = (Uint32)(&tx_bufferDesc[ch][4*tx_desc[ch]+0]);

// Increment descriptor counter

tx_desc[ch]++;

```

### Example 4. Programming the USB DMA Controller (continued)

```

// Routine to start the RX DMA for a given channel

void start_rx_dma(int ch) {

int index_save;

index_save = usbRegs->INDEX;

// Save the index to restore later

// Must have at least 3 descriptors to receive anything

if (rx_desc[ch] < 2) {error++;} else {</pre>

usbRegs->INDEX = ch+1;

usbReqs->RCPPICR = 1; //Enable Rx CPPI DMA

usbRegs->CHANNEL[ch].RCPPIDMASTATEW1 = (Uint32)(&rx_bufferDesc[ch][0]);

CSL_FINS(usbRegs->PERI_RXCSR,USB_PERI_RXCSR_DMAEN,1);

// Update the buffer count register. This ADDS to the existing value, does not

overwrite.

switch (ch) {

case 0: usbRegs->RBUFCNT0 = rx_desc[ch]; break;

case 1: usbRegs->RBUFCNT1 = rx_desc[ch]; break;

case 2: usbRegs->RBUFCNT2 = rx_desc[ch]; break;

case 3: usbRegs->RBUFCNT3 = rx_desc[ch]; break;

}

usbRegs->INDEX = index_save;

// Restore the index to previous value

}

//Function to build Rx DMA descriptors

void add_rx_descriptor(int ch, unsigned char * outBuf, int bytes) {

int index_save;

index_save = usbRegs->INDEX;

// Save the index to restore later

if (bytes < 1) {bytes = 64; error++;}

usbRegs->INDEX = ch+1;

// Link previous buffer to this one if this is not the first descriptor of the channel

if (rx_desc[ch] > 0) rx_bufferDesc[ch][4*(rx_desc[ch]-1)] =

(Uint32)(&rx_bufferDesc[ch][4*rx_desc[ch]]);

rx_bufferDesc[ch][4*rx_desc[ch]+0] = (Uint32)(0x0000000);

// Next descriptor

// Buffer address

rx_bufferDesc[ch][4*rx_desc[ch]+1] = (Uint32)outBuf;

rx_bufferDesc[ch][4*rx_desc[ch]+2] = (0x0000 << 16) | bytes;</pre>

// Rx buffer size in bytes

rx_bufferDesc[ch][4*rx_desc[ch]+3] = OWNER | 0;

// OWNER

rx_desc[ch]++;

usbRegs->INDEX = index_save;

// Restore the index to previous value

}

```

## 1.5 Industry Standard(s) Compliance Statement

This device conforms to USB 2.0 Specification and On-The-Go Supplement to the USB 2.0 Specification Rev 1.0a.

## 2 Peripheral Architecture

## 2.1 Clock Control

The USB controller is driven by two clocks: an output clock of PLL1 (SYSCLK2) which is ARM CPU clock divided by 3, and an output clock of the USB PHY. For proper USB function, SYSCLK2 must be greater than 60 MHZ.

The USB PHY takes an input clock that is configurable by the USB PHY clock source bits (PHYCLKSRC) in the USB PHY control register (USB\_PHY\_CTL) in the System Control Module. When a 24 MHZ crystal is used at MXI1/MXO1, set PHYCLKSRC to 0. This will present a 24 MHZ clock to the USB PHY. When a 36 MHZ crystal is used at MXI1/MXO1, set PHYCLKSRC to 1. This will present a 12 MHZ clock (36 MHZ divided internally by three) to the USB PHY. The USB PHY is capable of accepting only 24 MHZ and 12 MHZ; thus you must use either a 24 MHZ or 36 MHZ crystal at MXI1/MXO1. For detailed information on device clocking and the USB\_PHY\_CTL register, see the *TMS320DM335 Digital Media System-on-Chip (DMSoC) ARM Subsystem Reference Guide* (SPRUFX7).

## 2.2 Signal Descriptions

The USB controller provides the following I/O signals. Table 1 shows the USB port pins used in each mode. For additional information, see the device-specific data manual.

| NAME                       | I/O <sup>(1)</sup> | OTHER                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------|--------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB_DP                     | A I/O/Z            | V <sub>DDA33_USB</sub> | USB D+ (differential signal pair)                                                                                                                                                                                                                                                                                                                                              |

| USB_DM                     | A I/O/Z            | V <sub>DDA33_USB</sub> | USB D- (differential signal pair)                                                                                                                                                                                                                                                                                                                                              |

| USB_R1                     | A I/O/Z            |                        | USB reference current output                                                                                                                                                                                                                                                                                                                                                   |

| USB_ID                     | A I/O/Z            | V <sub>DDA33_USB</sub> | USB operating mode identification pin For Device mode operation<br>only, pull up this pin to VDD with a 1.5K ohm resistor. For Host mode<br>operation only, pull down this pin to ground (VSS) with a 1.5K ohm<br>resistor. If using an OTG or mini-USB connector, this pin will be set<br>properly via the cable/connector configuration.                                     |

| USB_VBUS                   | A I/O/Z            | V <sub>DD</sub>        | Five volt input that signifies that VBUS is connected. The OTG section of the PHY can also pull up/down on this signal for HNP and SRP. For device or host mode operation only, pull up this pin to 5v with a 1K ohm resistor. For host mode operation, tie USB power signal on USB connector to 5v also. For mixed host / device mode operation, tie this to the charge pump. |

| USB_DRVVBUS                | I/O/Z              | V <sub>DD</sub>        | Digital output to control external 5-V supply                                                                                                                                                                                                                                                                                                                                  |

| V <sub>SS_USB</sub>        | GND                | V <sub>DD</sub>        | Ground for USB reference voltage                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DDA33_USB</sub>     | I/O/Z              | V <sub>DD</sub>        | Analog 3.3 V power USBPHY                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>SS_USB</sub>        | GND                | V <sub>DD</sub>        | Ground for USB reference voltage                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DDA33_USB_PLL</sub> | I/O/Z              | V <sub>DD</sub>        | Common mode 3.3 V power for USB PHY (PLL)                                                                                                                                                                                                                                                                                                                                      |

| V <sub>SS_USB</sub>        | GND                | V <sub>DD</sub>        | Ground for USB reference voltage                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DDA13_USB</sub>     | I/O/Z              | V <sub>DD</sub>        | Analog 1.3 V power for USB PHY                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>SS_USB</sub>        | GND                | V <sub>DD</sub>        | Ground for USB reference voltage                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DDD13_USB</sub>     |                    | V <sub>DD</sub>        | Digital 1.3 V power for USB PHY                                                                                                                                                                                                                                                                                                                                                |

| V <sub>SS_USB</sub>        | GND                | V <sub>DD</sub>        | Ground for USB reference voltage                                                                                                                                                                                                                                                                                                                                               |

#### Table 1. USB Terminal Functions

<sup>(1)</sup> I = Input, O = Output, Z = High Impedance, S = Supply voltage, GND = Ground, A = Analog Signal

## 2.3 USB\_DP / USB\_DM Polarity Inversion

You may invert the polarity of the of the USB data pin (USB\_DP and USB\_DM). Since USB\_DP is equal to the inverse of USB\_DM (they form a differential pair), inverting these pins allows you to effectively swap their function. This allows flexibility in board design by allowing different USB connector configurations. In particular, this allows for mounting the connector on either side of the board and for arranging the USB\_DP/USB\_DM signals so they do not physically cross over each other (so they can be routed completely on the one surface trace).

To invert USB\_DP/USB\_DM use the bit DATAPOL in the USB\_PHY\_CTRL register in the system control module. For more information on the USB\_PHY\_CTL register, see the *TMS320DM335 Digital Media System-on-Chip (DMSoC) ARM Subsystem Reference Guide* (<u>SPRUFX7</u>).

## 2.4 Indexed and Non-Indexed Registers

USB controller provides two mechanism of accessing the endpoint control and status registers:

- Indexed Endpoint Control/Status Registers These registers are memory-mapped at offset 410h to 41Fh. The endpoint is selected by programming the INDEX register of the controller.

- Non-indexed Endpoint Control/Status Registers These registers are memory-mapped at offset 500h to 54Fh. Registers at offset 500h-50Fh map to Endpoint 0; offset 510h-51Fh map to Endpoint 1, and so on.

For detailed information about the USB controller registers, see Section 4.

## 2.5 USB PHY Initialization

The default state of the USB PHY in powered down state. The external PHY clock frequency should be determined (it is either 24 MHZ or 36 MHZ) prior to initialization. The USB\_PHY\_CTL register has all the bit fields necessary to configure and control the PHY. For more information on the USB\_PHY\_CTL register, see the *TMS320DM335 Digital Media System-on-Chip (DMSoC) ARM Subsystem Reference Guide* (SPRUFX7).

The following is the recommended step for configuring the USB PHY (note that the entire initialization can be performed at using single or multiple steps).

- Identify the external input PHY Clock Frequency: Clear USB\_PHY\_CTL:PHYCLKSRC to 0 for a 24 MHZ clock source in use and set for 36 MHZ clock use.

- Identify if the D+ and D- lines connection matches normal polarity or inverted: Clear USB\_PHY\_CTL:DATAPOL to 0 for normal connection and for inverted connection set it to 1.

- Power up PHY: Clear all of the following fields: USB\_ PHY\_CTL:PHYPDWN, OTGPDWN, VPSS\_OSCPDWN

- Enable Voltage Comparators and set PLL Operation for normal: USB\_PHY\_CTL:SESNDEN, VBDTCTEN, PHYPLLON

- Power up PHY and Clock: Clear USB\_PHY\_CTL:PHYPDWN, OTGPDWN, VPSS\_OSCPDWN

- Wait for PHY PLL to lock: USB\_PHY\_CTL:PHYCLKGD will be set to 1 by the controller when PHY PLL locks.

## 2.6 VBUS Voltage Sourcing Control

When the USB Controller assumes the role of a host, it is required to supply a 5V Power to an attached device through its VBUS line. In order to achieve this task, the USB Controller requires the use of an external logic (or charge pump) capable of sourcing a 5V power. A USB\_DRVVBUS is used as a control signal to enable/disable the external logic to either source or disable power on the VBUS line. This control is automatic and is handled by the controller. The USB Controller drives the USB\_DRVVBUS signal high when it assumes the role of a host while the controller is in Session. When assuming the role of a device, the controller drives USB\_DRVVBUS low disabling the external charge pump; hence no power is driven on the VBUS line.

## 2.7 Dynamic FIFO Sizing

The USB controller supports a total of 4K RAM to dynamically allocate FIFO to all endpoints. The allocation of FIFO space to the different endpoints requires the specification for each Tx and Rx endpoint of:

- The start address of the FIFO within the RAM block

- The maximum size of packet to be supported

- Whether double-buffering is required.

These details are specified through four registers, which are added to the indexed area of the memory map. That is, the registers for the desired endpoint are accessed after programming the INDEX register with the desired endpoint value. Section 4.80, Section 4.81, Section 4.82, and Section 4.83 provide details of these registers.

**Note:** The option of setting FIFO sizes dynamically only applies to Endpoints 1 ... 4. Endpoint 0 FIFO has a fixed size (64 bytes) and a fixed location (start address 0).

It is the responsibility of the firmware to ensure that all the Tx and Rx endpoints that are active in the current USB configuration have a block of RAM assigned exclusively to that endpoint that is at least as large as the maximum packet size set for that endpoint.

## 3 USB Controller Host and Peripheral Modes Operation

The USB controller can be used in a range of different environments. It can be used as either a high-speed or a full-speed USB peripheral device attached to a conventional USB host (such as a PC). It can be used as either host or peripheral device in point-to-point data transfers with another peripheral device - or, if the other device also contains a Dual-Role Controller, the two devices can switch roles as required. (This second device may be either a high-speed, full-speed or low-speed USB function.) Or the controller can be used as the host to a range of such peripheral devices in a multi-point setup.

Whether the controller expects to behave as a host or as a peripheral device depends on the way the devices are cabled together. Each USB cable has an A end and a B end. If the A end of the cable is plugged into the controller, it will take the role of the Host device and go into host mode. If the B end of the cable is plugged in, the controller will go instead into peripheral mode.

The USB controller interrupts the ARM on completion of the data transfer on any of the endpoints or on detecting reset, resume, suspend, connect, disconnect, or SOF on the bus.