# Digital Front End (DFE) User Guide for Keystone II Devices

# **User's Guide**

Literature Number: SPRUHX8A July 2014–Revised April 2015

### Contents

| 1 |      | duction                                                                           |    |

|---|------|-----------------------------------------------------------------------------------|----|

|   | 1.1  | Overview                                                                          |    |

|   | 1.2  | Features                                                                          |    |

|   | 1.3  | Connectivity                                                                      |    |

|   | 1.4  | System Overview and Use Cases                                                     |    |

|   | 1.5  | Use Case Examples                                                                 |    |

|   |      | 1.5.1 DFE with RF Transceiver (DAC+ADC with Integrated RF Front-End)              | 17 |

|   |      | 1.5.2 Discrete DAC and ADC                                                        | 17 |

|   |      | 1.5.3 Discrete ADC with DFE Bypass                                                | 18 |

|   | 1.6  | DFE TX Signal Processing and Frequency Translation                                | 19 |

|   |      | 1.6.1 TX Frequency Translation Based on a Channel or Carrier                      |    |

|   |      | 1.6.2 TX Frequency Translation Based on a Stream or Antenna                       |    |

|   |      | 1.6.3 TX Frequency Translation after DFE (Inside the DAC/RF Front-End)            |    |

|   | 1.7  | DFE RX Signal Processing and Frequency Translation                                |    |

|   |      | 1.7.1 Feedback RX Path                                                            |    |

|   | 1.8  | DFE General Input and Output Description                                          |    |

|   | 1.9  | TCI663xK2L DFE Boot Mode Considerations                                           |    |

|   | 1.10 | SYSREF Logic outside DFE                                                          |    |

|   | 1.10 | DFE Power Domains                                                                 |    |

|   | 1.11 | TCI663xK2L DFE JESD204B SerDes Lanes                                              |    |

|   | 1.12 | TCI663xK2L DFE JESD204B SelDes Lalles                                             |    |

|   | -    |                                                                                   |    |

|   | 1.14 | TCI663xK2L DFE GPIO Shared with Other SoC Functions                               |    |

|   | 1.15 | TCI663xK2L DFE Sub-Blocks and Functions                                           |    |

|   | 1.16 | DFE Sub-Block Capacity Considerations                                             |    |

|   | 1.17 | Example 2 and 4 Antenna Configurations                                            | 29 |

| 2 |      | Flow and Sub-Block Descriptions                                                   |    |

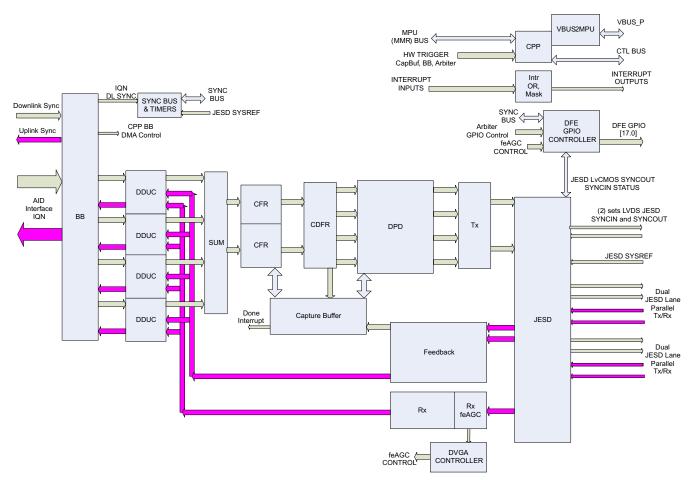

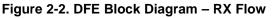

|   | 2.1  | Signal Flow                                                                       |    |

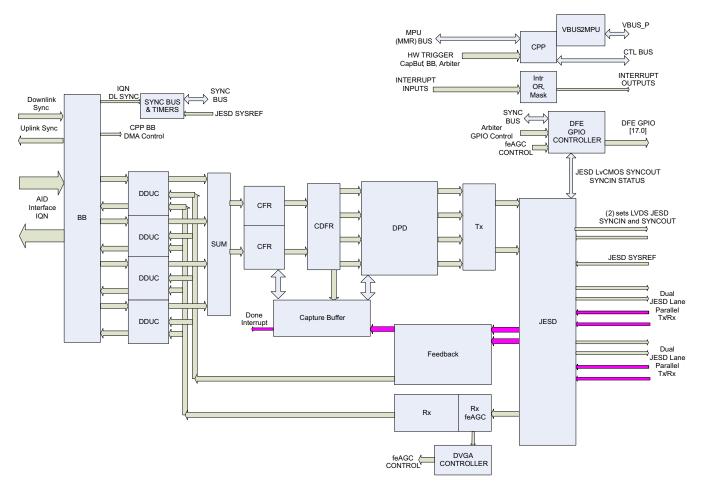

|   | 2.2  | Baseband Block (BB) in DFE                                                        |    |

|   |      | 2.2.1 Function                                                                    |    |

|   |      | 2.2.2 Inputs and Output Buses                                                     |    |

|   |      | 2.2.3 Basic Description                                                           |    |

|   |      | 2.2.3.1 BBTx                                                                      | 37 |

|   |      | 2.2.3.2 BBRx                                                                      | 38 |

|   |      | 2.2.3.3 beAGC (Adaptive BBRx Gain)                                                | 38 |

|   |      | 2.2.3.4 BBRx Formatter                                                            | 39 |

|   |      | 2.2.3.5 Power Meter                                                               | 40 |

|   |      | 2.2.4 Synchronization Events                                                      | 40 |

|   |      | 2.2.5 Software Application Interface (API) Functions                              |    |

|   |      | 2.2.6 Important Programming Concepts (or Selection from Pre-Built Configurations) |    |

|   | 2.3  | Digital Downconverter/Upconverter (DDUC) in DFE                                   |    |

|   |      | 2.3.1 Function                                                                    | 41 |

|   |      | 2.3.2 Inputs and Output Buses                                                     |    |

|   |      | 2.3.3 Basic Description                                                           |    |

|   |      | 2.3.3.1 PFIR                                                                      |    |

|   |      | 2.3.3.1 PTIK                                                                      |    |

|   |      |                                                                                   | -0 |

| www.ti.com |                                                                                  |    |

|------------|----------------------------------------------------------------------------------|----|

|            | 2.3.3.3 Cascade Integrator Comb (CIC)                                            | 47 |

|            | 2.3.3.4 Complex Numerically Controlled Oscillator (NCO)                          | 47 |

|            | 2.3.3.5 Distributor                                                              | 48 |

|            | 2.3.4 Synchronization Events                                                     | 48 |

|            | 2.3.5 Software Application Interface (API) Functions                             | 48 |

|            | 2.3.6 Important Programming Concepts (or Selection from Prebuilt Configurations) | 49 |

| 2.4        | Sum Chain                                                                        | 49 |

|            | 2.4.1 Function                                                                   | 49 |

|            | 2.4.2 Inputs/Outputs                                                             | 50 |

|            |                                                                                  | 50 |

|            | ·                                                                                | 51 |

|            | 2.4.5 Software Application Interfaces                                            | 51 |

|            |                                                                                  | 51 |

| 2.5        |                                                                                  | 51 |

|            |                                                                                  | 52 |

|            | 2.5.2 Inputs/Outputs                                                             | 55 |

|            |                                                                                  |    |

|            | 2.5.3.1 PreCFR Processing                                                        |    |

|            |                                                                                  | 56 |

|            |                                                                                  | 58 |

|            | 5                                                                                | 59 |

|            | -                                                                                | 59 |

|            | 2.5.6 Important Programming Concepts                                             | 59 |

| 2.6        |                                                                                  | 60 |

| 2.0        |                                                                                  | 60 |

|            |                                                                                  | 61 |

|            | 2.6.3 CDFR Basic Description                                                     | 61 |

|            | ·                                                                                | 62 |

|            |                                                                                  | 62 |

|            |                                                                                  | 62 |

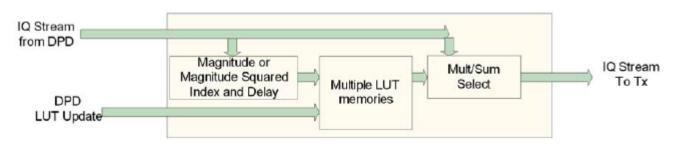

| 2.7        |                                                                                  | 62 |

| 2.1        | 2.7.1 DPD Function                                                               |    |

|            | 2.7.2 DPD Inputs and Outputs                                                     |    |

|            |                                                                                  |    |

|            | 2.7.4 DPD Synchronization Events                                                 |    |

|            | 2.7.5 DPD Software Application Interface                                         |    |

|            | 2.7.6 DPD Important Programming Concepts                                         |    |

| 2.8        |                                                                                  | 68 |

| 2.0        |                                                                                  | 69 |

|            |                                                                                  | 69 |

|            |                                                                                  | 69 |

|            |                                                                                  | 72 |

|            | •                                                                                | 72 |

|            | 2.8.6 TX Sub-Block Important Programming Concepts                                |    |

| 2.9        |                                                                                  |    |

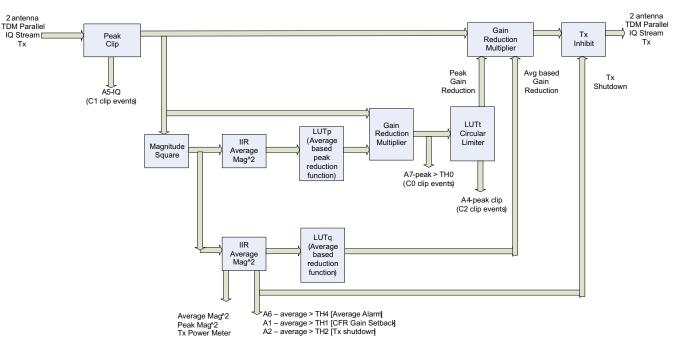

| 2.9        | JESD Block                                                                       | 73 |

|            |                                                                                  |    |

|            |                                                                                  |    |

|            | 2.9.3 JESD Block Basic Description                                               |    |

|            |                                                                                  |    |

|            |                                                                                  | 75 |

|            |                                                                                  | 76 |

|            | 5 11 5                                                                           | 76 |

|            | 2.9.3.5 Internal Signal Loopback                                                 | 10 |

| www.ti.com |

|------------|

|------------|

|      | 2.9.3.6    | Scrambler (TX), Descrambler (RX or Feedback)                                  |          |

|------|------------|-------------------------------------------------------------------------------|----------|

|      | 2.9.3.7    | TX Alignment Block                                                            |          |

|      | 2.9.3.8    | TX Encode                                                                     |          |

|      | 2.9.3.9    | Test Generator                                                                |          |

|      | 2.9.3.10   | Lane loopback                                                                 |          |

|      | 2.9.3.11   | Decoder                                                                       |          |

|      | 2.9.3.12   | RX Lane Align                                                                 |          |

|      | 2.9.3.13   | RX Frame Align                                                                |          |

|      | 2.9.3.14   | Frame Buffer                                                                  |          |

|      |            | RX/Fdbk Formatter – Loopback Selector                                         |          |

|      |            | D Block Synchronization Events                                                |          |

|      |            | D Block Software Application Interface                                        |          |

| 0.40 |            | D Block Important Programming Concepts                                        |          |

| 2.10 |            |                                                                               |          |

|      |            | Sub-Block Functions                                                           |          |

|      |            | Sub-Block Inputs and Outputs                                                  |          |

|      |            | Sub-Block Basic Description                                                   |          |

|      |            | RX-R2C                                                                        |          |

|      |            | RX-Switch                                                                     |          |

|      |            | RX NCO                                                                        |          |

|      | 2.10.3.4   | RX Decimating Filter                                                          |          |

|      | 2.10.3.5   | RX Equalizer                                                                  |          |

|      | 2.10.3.6   | RX IQ Imbalance Correction.                                                   |          |

|      | 2.10.3.7   | RX Output Formatter                                                           |          |

|      | 2.10.3.8   | RX Power Meter                                                                |          |

|      |            | Sub-Block Synchronization Events                                              |          |

|      |            | Sub-Block Software Application Interface                                      |          |

| 0.44 |            | Sub-Block Important Programming Concepts                                      |          |

| 2.11 |            | lock                                                                          |          |

|      |            | dback Block Functions                                                         |          |

|      |            | dback Block Inputs and Outputs                                                |          |

|      |            | dback Block Basic Description                                                 |          |

|      |            | dback Block Synchronization Events                                            |          |

|      |            | back Block Software Application Interface                                     |          |

| 0.40 |            | dback Block Important Programming Concepts                                    |          |

| 2.12 | •          | fer Sub-Block                                                                 | 90<br>90 |

|      | -          |                                                                               |          |

|      |            | oture Buffer Block Inputs and Outputs                                         |          |

|      | -          | oture Buffer Block Basic Descriptionoture Buffer Block Synchronization Events | 93       |

|      |            | oture Buffer Block Synchronization Events                                     | 93<br>93 |

|      |            | oture Buffer Block Important Programming Concepts                             | 93<br>94 |

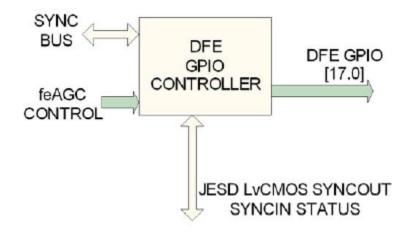

| 2.13 | •          | GPIO) Block                                                                   | 94<br>95 |

| 2.15 | -          | C GPIO Block Functions                                                        | 95<br>95 |

|      |            | C GPIO Block Functions                                                        | 95<br>95 |

|      |            | C GPIO Block Inputs and Outputs                                               |          |

|      |            | C GPIO Block Basic Description                                                |          |

|      |            | -                                                                             |          |

|      |            | C GPIO Block Software Application Interface                                   |          |

| 214  |            | C GPIO Block Important Programming Concepts                                   |          |

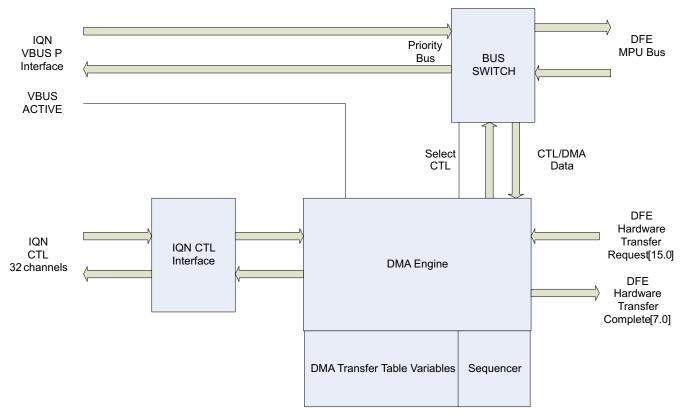

| 2.14 |            | C CPP Block Functions                                                         |          |

|      |            |                                                                               |          |

|      |            |                                                                               | 97       |

|      | 2.14.3 MIS | C CPP Block Basic Description                                                 | 98       |

| www.ti.c | com   |         |                                                  |     |

|----------|-------|---------|--------------------------------------------------|-----|

|          |       | 2.14.4  | MISC CPP Block Synchronization Events            | 98  |

|          |       | 2.14.5  | MISC (CPP ) Block Software Application Interface | 98  |

|          |       | 2.14.6  | MISC (CPP ) Block Important Programming Concepts | 98  |

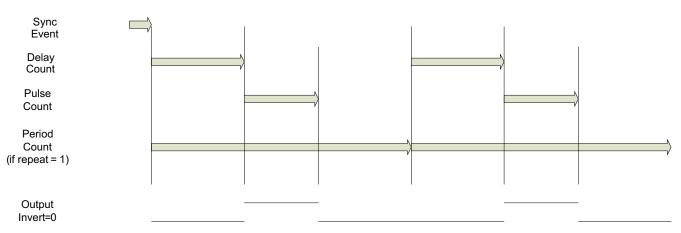

| :        | 2.15  | Sync Bu | us and Sync Counter                              | 98  |

|          |       | 2.15.1  | Sync Bus Functions                               | 98  |

|          |       | 2.15.2  | Sync Bus Input and Outputs                       | 99  |

|          |       | 2.15.3  | Basic Description                                | 99  |

|          |       | 2.15.4  | Synchronization Events                           | 100 |

|          |       | 2.15.5  | Software API                                     | 100 |

|          |       | 2.15.6  | Important Programming Considerations             | 100 |

| :        | 2.16  | 2-Level | Interrupt Description                            | 100 |

|          |       | 2.16.1  | Interrupt Function                               | 100 |

|          |       | 2.16.2  | Interrupt Inputs and Outputs                     | 100 |

|          |       |         | Basic Description                                |     |

|          |       | 2.16.4  | Synchronization                                  | 101 |

|          |       | 2.16.5  | API Interface                                    | 101 |

|          |       | 2.16.6  | Special Programming Concerns                     | 101 |

| 3        | Refer | ences   |                                                  | 103 |

| Revisi   | on Hi | story   | ······                                           | 105 |

#### List of Figures

| 1-1.  | DFE Context Diagram                                                              | 12 |

|-------|----------------------------------------------------------------------------------|----|

| 1-2.  | DFE Block Diagram                                                                | 14 |

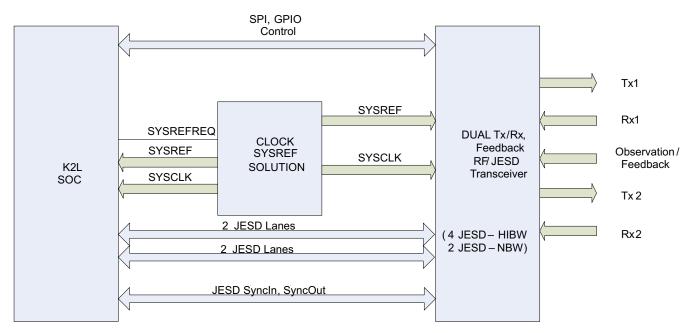

| 1-3.  | DSP SoC to JESD Transceiver SoC Flow and Control Diagram                         | 15 |

| 1-4.  | DFE TX Signal Processing                                                         | 16 |

| 1-5.  | DFE RX Signal Processing                                                         | 16 |

| 1-6.  | DFE with RF Transceiver                                                          | 17 |

| 1-7.  | DFE with Discrete DAC and ADC                                                    | 18 |

| 1-8.  | DFE RX Bypass                                                                    | 18 |

| 1-9.  | DFE TX Channel Processing                                                        | 19 |

| 1-10. | DFE TX Stream Processing                                                         | 20 |

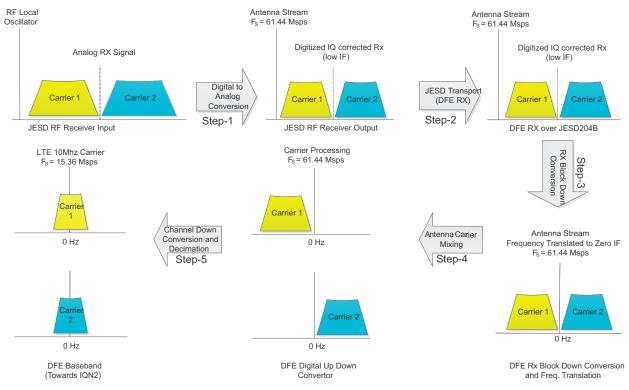

| 1-11. | DFE RX Processing                                                                | 21 |

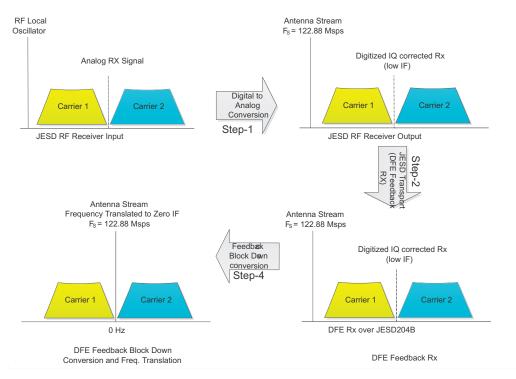

| 1-12. | DFE Feedback RX Processing                                                       | 22 |

| 1-13. | Boot Mode Shared Data Multiplexers IQNet and DFE                                 | 24 |

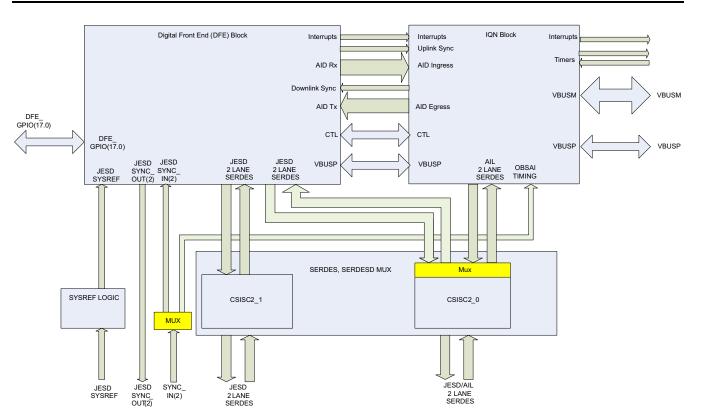

| 1-14. | TCI663xK2L DFE to Two Antenna JESD Transceiver Block Diagram                     | 25 |

| 1-15. | TCI663xK2L DFE to Four Antenna JESD Transceiver Block Diagram                    | 26 |

| 1-16. | TCI663xK2L DFE Block Diagram                                                     | 28 |

| 2-1.  | DFE Block Diagram – TX Flow                                                      | 33 |

| 2-2.  | DFE Block Diagram – RX Flow                                                      | 34 |

| 2-3.  | DFE Block Diagram – Feedback Flow                                                | 35 |

| 2-4.  | BB Block Diagram                                                                 |    |

| 2-5.  | beAGC Block Diagram                                                              |    |

| 2-6.  | BB Power Meter Cycle                                                             | 40 |

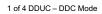

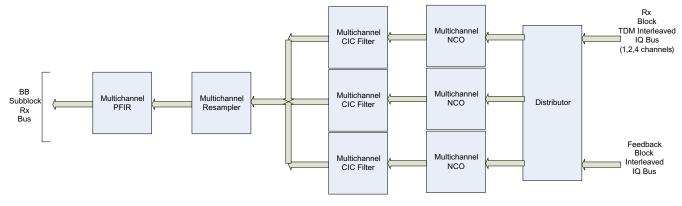

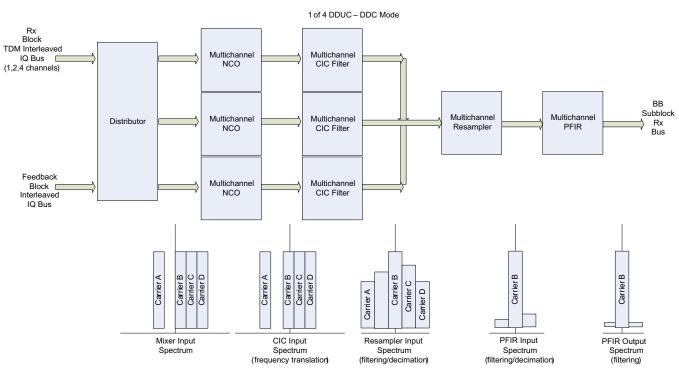

| 2-7.  | DDUC Block Diagram                                                               |    |

| 2-8.  | DDUC as a Digital Up Converter (1 Carrier Shown) Block Diagram                   |    |

| 2-9.  | DDUC as a Digital Down Converter (Multicarrier Shown) Block Diagram              |    |

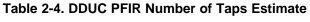

| 2-10. | Example 79 Tap – Low Pass Filter Used for LTE20 Application                      | 45 |

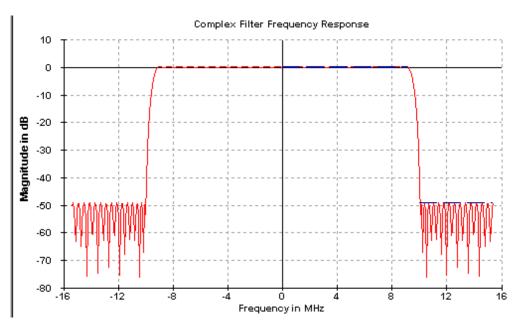

| 2-11. | Example 79 Tap – Low Pass Filter Used for LTE10, with CIC Droop Compensation     |    |

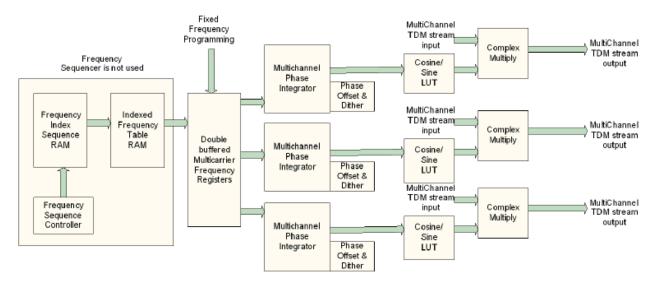

| 2-12. | Multichannel Complex Mixer (3 Sections Shown)                                    |    |

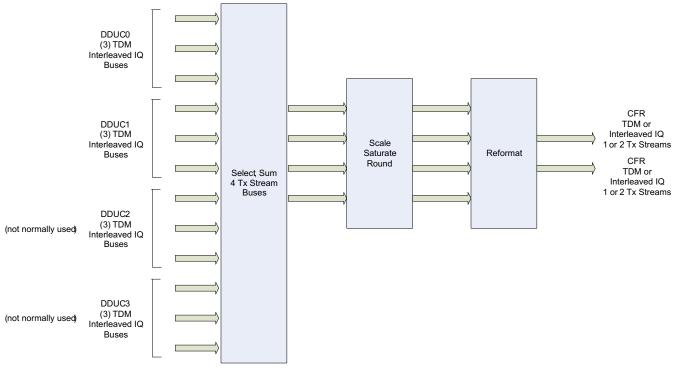

| 2-13. | Sum Chain                                                                        |    |

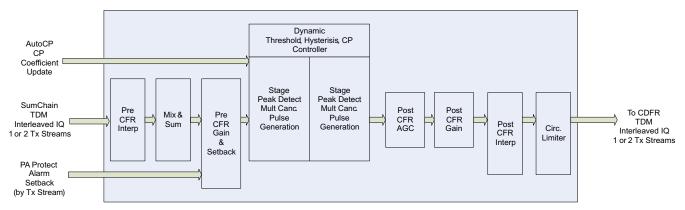

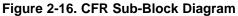

| 2-14. | CFR Sub-Block Diagram                                                            |    |

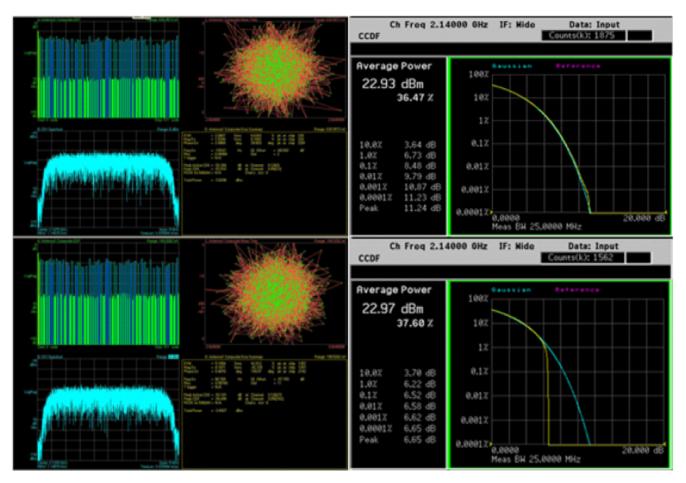

| 2-15. | Effect of CFR on TX Antenna Carrier Signal (Upper-Before CFR/ Below after CFR)   |    |

| 2-16. | CFR Sub-Block Diagram                                                            |    |

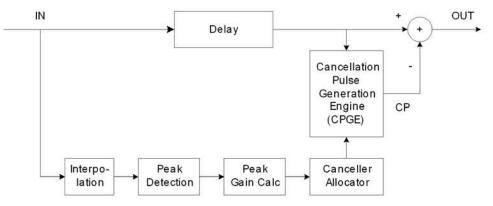

| 2-17. | Cancellation Logic Diagram for CFR                                               |    |

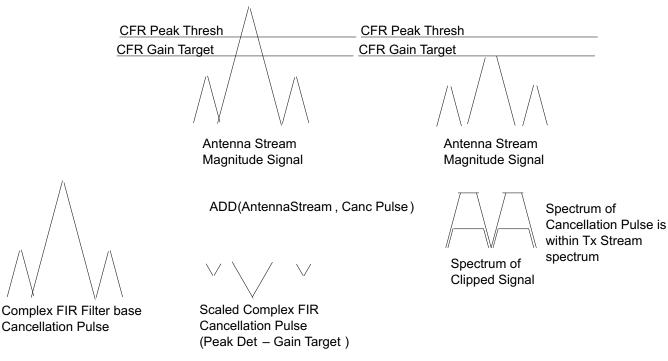

| 2-18. | Example TimeSeries, Spectrum of Peak Clipping                                    |    |

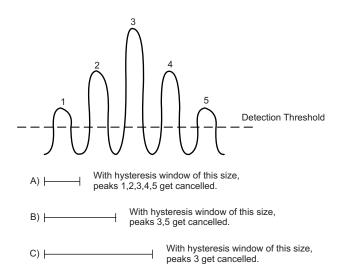

| 2-19. | Example Hysterisis Control Related to Multiple Peak Cancellation                 |    |

| 2-20. | Circular Limiter Diagram                                                         | 59 |

| 2-21. | CDFR Block Diagram                                                               | 60 |

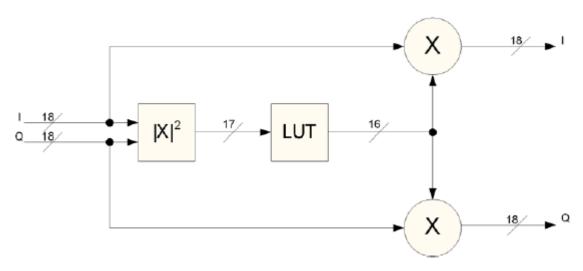

| 2-22. | DPD (1 of 4 streams) Block Diagram                                               | 62 |

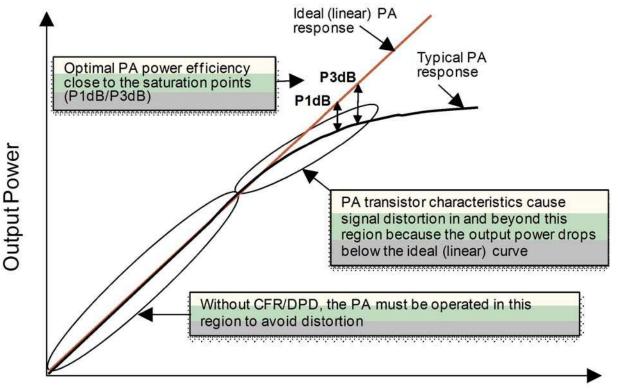

| 2-23. | DPD Correction for AM-AM Distortion                                              |    |

| 2-24. | DPD Correction Showing TX Before Correction, Predistortion, and Post PA Response |    |

| 2-25. | Transmit Bandwidth and DPD Expansion Bandwidth Example.                          |    |

| 2-26. | DPD Correction Showing Spectral Emission Mask Improvement                        |    |

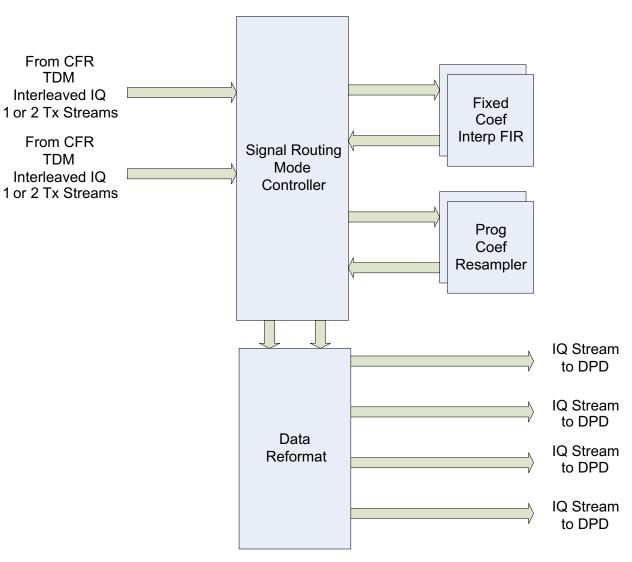

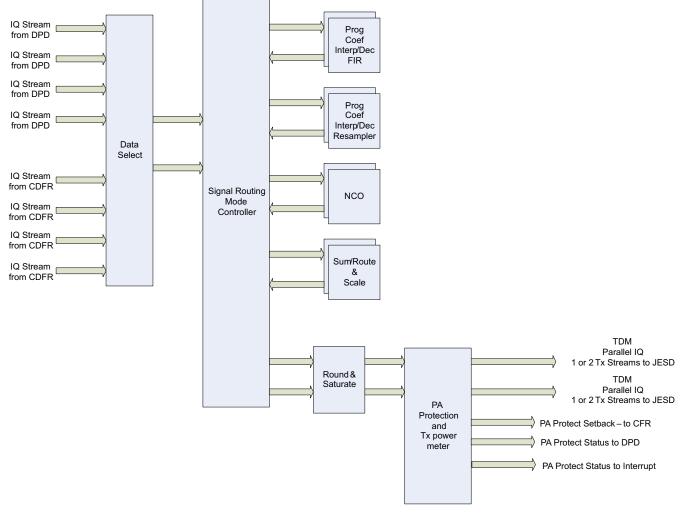

| 2-27. | TX Sub-Block Block Diagram                                                       |    |

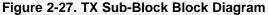

| 2-28. | TX Sub-Block PA Protection (1 of 2) Diagram                                      | 71 |

| 2-29. | JESD Block Diagram                                                               |    |

| 2-30. | JESD Clock, Synchronization, and SerDes Data Diagram                             |    |

| 2-31. | DFE Block Diagram for RX                                                         | 79 |

| www.ti.com |                                                                   |     |

|------------|-------------------------------------------------------------------|-----|

| 2-32.      | RX Sub-Block Diagram                                              | 80  |

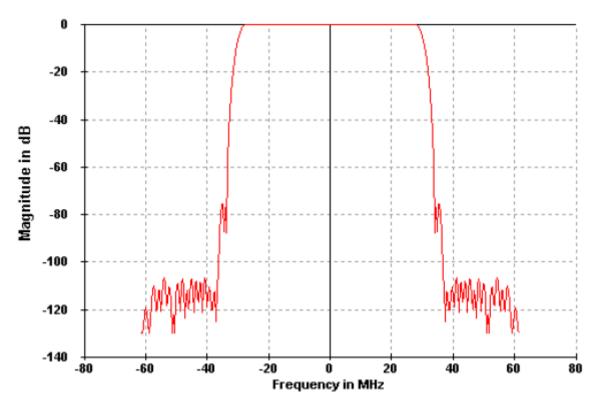

| 2-33.      | Example F2 Filter Decimate-by-Two Response, Sampled at 122.88 Mhz | 83  |

| 2-34.      | RX Sub-Block Power Meter Diagram                                  | 84  |

| 2-35.      | DFE Block Diagram for Feedback                                    | 86  |

| 2-36.      | Feedback Sub-Block Diagram                                        | 86  |

| 2-37.      | Capture Buffer Block Diagram                                      | 90  |

| 2-38.      | Capture Buffer Static Collection with Delay                       | 92  |

| 2-39.      | Capture Buffer Qualified Collection with Delay                    | 93  |

| 2-40.      | DFE GPIO Block Diagram                                            | 95  |

| 2-41.      | VBUSP2MPU CPP Sub-Block Diagram                                   | 97  |

| 2-42.      | Sync Counter Operation                                            | 100 |

#### List of Tables

| 1-1.  | Power Domains in DFE                                                            | 24 |

|-------|---------------------------------------------------------------------------------|----|

| 1-2.  | Example Tx-Fdbk, Rx IQ Rates with JESD 204B Transport                           | 25 |

| 1-3.  | DFE Sub-Block Functions                                                         | 27 |

| 1-4.  | Example TCI663xK2L JESD Transceiver IQ Rates, Num Antennas and Carriers/Antenna | 30 |

| 2-1.  | BB Inputs and Outputs                                                           | 37 |

| 2-2.  | BB Signal Groups                                                                | 37 |

| 2-3.  | DDUC Inputs and Outputs                                                         | 44 |

| 2-4.  | DDUC PFIR Number of Taps Estimate                                               | 45 |

| 2-5.  | DDUC Number of Channels, Relationship to DFE Clock, and CIC Rate                | 47 |

| 2-6.  | SumChain Inputs and Outputs                                                     | 50 |

| 2-7.  | Example Number of Carriers per CIC/Mixer and Number DFE Clock Cycles            | 50 |

| 2-8.  | CFR Operating Modes, Interpolation, and DFE Clock Rates                         | 53 |

| 2-9.  | CFR Inputs and Outputs                                                          | 55 |

| 2-10. | CDFR Inputs and Outputs                                                         | 61 |

| 2-11. | CDFR Common Operating Modes                                                     | 61 |

| 2-12. | DPD Inputs and Outputs                                                          | 63 |

| 2-13. | DPD Memory Taps Based on Number of TX Antennas/Number LUT-Solution Sets         | 63 |

| 2-14. | TX Sub-Block Inputs and Outputs                                                 | 69 |

| 2-15. | TX Sub-Block Common Operating Modes                                             | 70 |

| 2-16. | JESD Block Inputs and Outputs                                                   | 74 |

| 2-17. | JESD Signal Mapping Based on JESD Transceiver Mode                              | 76 |

| 2-18. | JESD Signal Transfer and Number of Clocks                                       | 76 |

| 2-19. | JESD RX Number of RX Input Antenna Streams and Number of Clocks                 | 80 |

| 2-20. | JESD RX Number of RX Output Antenna Streams and Number of Clocks                | 80 |

| 2-21. | RX Sub-Block Inputs and Outputs                                                 | 81 |

| 2-22. | RX Sub-Block Decimation Input and Output RX Streams                             | 81 |

| 2-23. | RX Sub-Block Decimation F1 and F2 Filter Ratios                                 | 82 |

| 2-24. | Feedback Block Inputs and Outputs                                               | 87 |

| 2-25. | RX Sub-Block and Feedback Block Decimation for RX DDUC Usage (Continued)        | 88 |

| 2-26. | Capture Buffer Inputs and Outputs                                               | 91 |

| 2-27. | MISC GPIO Inputs and Outputs                                                    | 95 |

| 2-28. | GPIO Mux Controls                                                               | 95 |

| 2-29. | MISC CPP Inputs and Outputs                                                     | 97 |

| 2-30. | Sync Bus                                                                        | 99 |

| Abbreviations |                                                            |  |  |  |  |

|---------------|------------------------------------------------------------|--|--|--|--|

| 3GPP          | 3 <sup>rd</sup> generation Partnership Project             |  |  |  |  |

| ACLR          | Adjacent Channel Leakage Ratio                             |  |  |  |  |

| ACPR          | Adjacent Channel Power Ratio                               |  |  |  |  |

| ADC           | Analog to Digital Convertor                                |  |  |  |  |

| AGC           | Automatic Gain Control                                     |  |  |  |  |

| AID           | Bus interface connecting IQN2 with DFE                     |  |  |  |  |

| AIL           | Antenna Interface Lanes                                    |  |  |  |  |

| AxC           | Antenna Container                                          |  |  |  |  |

| BB            | Baseband sub-block in DFE                                  |  |  |  |  |

| BDC           | Bulk Down Conversion                                       |  |  |  |  |

| Be-AGC        | Back end AGC                                               |  |  |  |  |

| BPF           | Band Pass Filter                                           |  |  |  |  |

| СВ            | Capture Buffer                                             |  |  |  |  |

| CCDF          | Complimentary Cumulative Distribution Function             |  |  |  |  |

| CFR           | Crest Factor Reduction                                     |  |  |  |  |

| CDFR          | CFR DPD Fractional Re-sampler                              |  |  |  |  |

| CIC           | Cascaded Integrator-Comb (Filter)                          |  |  |  |  |

| CMOS          | Complementary Metal-oxide Semiconductor                    |  |  |  |  |

| DAC           | Digital to Analog Convertor                                |  |  |  |  |

| DDC           | Digital Down Conversion                                    |  |  |  |  |

| DUC           | Digital Up Conversion                                      |  |  |  |  |

| DDUC          | Digital Down Convertor and Up Convertor (Block within DFE) |  |  |  |  |

| DFE           | Digital Front End                                          |  |  |  |  |

| DL            | Downlink                                                   |  |  |  |  |

| DPD           | Digital Pre-Distortion                                     |  |  |  |  |

| EVM           | Error Vector Magnitude                                     |  |  |  |  |

| Fe-AGC        | Front End AGC                                              |  |  |  |  |

| FIR           | Finite Impulse Response                                    |  |  |  |  |

| FPGA          | Field Programmable Gate Array                              |  |  |  |  |

| GPIO          | General Purpose Input Output                               |  |  |  |  |

| IF            | Intermediate Frequency                                     |  |  |  |  |

| IMD           | Inter Modulation Distortion                                |  |  |  |  |

| IQN2          | IQ Net 2 Block within the 66AK2L SoC                       |  |  |  |  |

| JESD          | JEDEC Serial Interface for Data Convertors                 |  |  |  |  |

| LTE           | Long Term Evolution                                        |  |  |  |  |

| LVCMOS        | Low Voltage Complementary Metal Oxide Semiconductor        |  |  |  |  |

| LVDS          | Low Voltage Differential Signaling                         |  |  |  |  |

| LNA           | Low Noise Amplifier                                        |  |  |  |  |

| MSPS          | Mega-Samples Per Second                                    |  |  |  |  |

| NCO           | Numerically Controlled Oscillator                          |  |  |  |  |

| PA            | Power Amplifier                                            |  |  |  |  |

| PAP           | PA protection sub-block within DFE                         |  |  |  |  |

| PAR           | Peak to Average Ratio                                      |  |  |  |  |

| PFIR          | Programmable FIR (Filter)                                  |  |  |  |  |

| RF            | Radio Frequency                                            |  |  |  |  |

| RRC           | Root Raised Cosine (Filter)                                |  |  |  |  |

| RX            | Roceive/Receiver                                           |  |  |  |  |

| SC SC         | Sum Chain                                                  |  |  |  |  |

| SEM           |                                                            |  |  |  |  |

|               | Spectral Emission Mask                                     |  |  |  |  |

#### Abbreviations

#### Abbreviations (continued)

| SoC    | System on Chip                         |

|--------|----------------------------------------|

| SERDES | Serializer DeSerializer                |

| SPI    | Serial Peripheral Interface            |

| TX     | Transmit/Transmitter                   |

| UL     | Uplink                                 |

| WCDMA  | Wideband Code Division Multiple Access |

## Introduction

#### 1.1 Overview

The Digital Front End (DFE) is a programmable peripheral integrated into Texas Instruments Keystone II SOCs to perform transmit and receive signal processing. The DFE provides a JESD204B SerDes interface to connect with analog-to-digital and digital-to-analog convertors. The DFE provides for transmit and receive digital signal processing, JESD204B transport, and includes digital down/up convertors (DDUC), Transmit, Receive, and Capture buffer blocks. The DFE connects to the rest of the SOC through the IQN2 module.

DFE signal processing is performed on the transmit path (TX) and the receive path (RX). The transmit path includes channel-based and stream-based up conversion. Specific versions targeted towards wireless base-station markets also include crest factor reduction (CFR) and digital pre-distortion (DPD). The receive path includes functionality for wideband and narrowband automatic gain control (AGC), complex equalization, decimation, filtering, and down conversion. The DFE also includes a feedback path to capture samples from transmit side. This data is utilized for DPD to linearize the power amplifier output. This path can also act as an additional receive path to add extra receive capacity (or for network listening modes for 3GPP applications).

On the transmit side, DFE aggregates multiple real or complex digital data channels into signal streams. On the receive side, DFE receives JESD204B-formatted signal streams containing time-division multiplexed data for multiple ADC channels, and separates them into individual real or complex data channels.

The DFE performs signal processing operations applicable to both individual channels, such as gain, interpolation, decimation, and those which apply to the signal streams, such as filtering, frequency translations, channel combining, crest factor reduction, and digital pre-distortion.

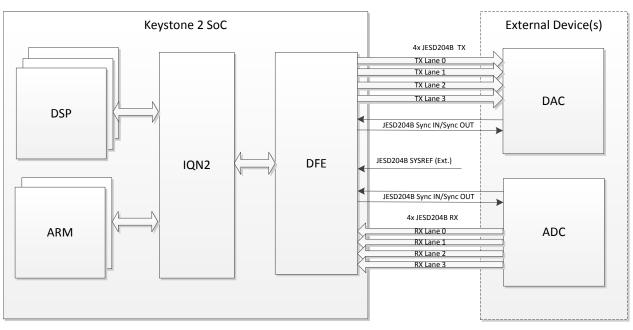

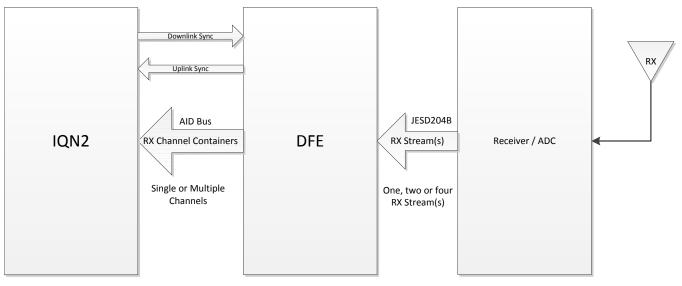

Figure 1-1. DFE Context Diagram

#### 1.2 Features

- 4 JESD SERDES lanes, each supporting up to 7.37 Gbps

- Support for up to 4TX, 4 RX, and 2 feedback RX streams.

- 4 DDUCs, each capable of being used as and up or down convertor.

- Each DDUC supports 1 to 12 channels for a total of up to 48 channels.

- Programmable FIR filters (PFIRs) inside the DDUCs allow for varying tap lengths and storage of multiple filters.

- Transmit Functionality

- TX includes DUC, CFR, DPD, and Bulk up conversion.

- TX and RX power meters to support power monitoring

- PA protection logic built into the TX block to limit RMS or peak power

- Crest factor reduction to limit the signal peak to average power ratio

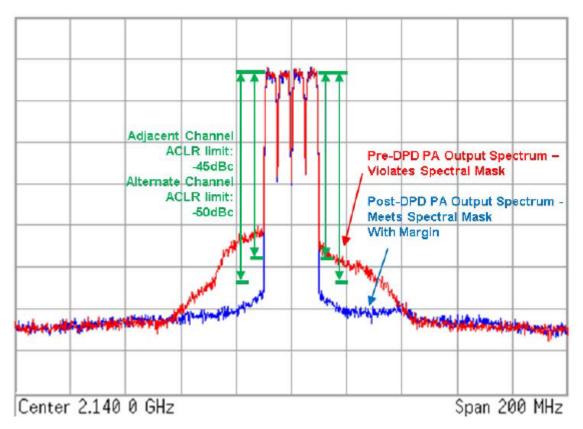

- Digital pre-distortion to improve system linearity by allowing PAs to operate more efficiently

- Provides post-DPD fractional resampling, mixing and summing options

- Programmable 55 tap filter to ease TX IF filtering requirements

- Fractional re-sampler to allow DPD and JESD sample rates to differ

- 48 bit mixer and NCO

- Switching, summing options

- Interfaces to the JESD module

- Receive Functionality

- Provides receiver functionality prior to digital down-conversion to baseband

- RX includes DC-offset cancellation, front-end and back-end AGC, decimation, bulk down conversion, RX equalizer and I/Q imbalance correction.

- Provides 90-dB stops and 80% BW optional real to complex filtering and programmable decimation (supported decimation rates: 1x, 2x, 4x, 8x, and 16x).

- 16 tap complex equalizer for linear distortion compensation or calibrated frequency-dependent IQ imbalance correction

- Flexible mixing, switching, and summing options

- Interfaces to the JESD module

- Tuning and channel aggregation and distribution

- Supports bypass capability to deliver data from JESD straight to the baseband block for JESD attach applications

- GPIOs to control external data convertors and transceivers

Figure 1-2. DFE Block Diagram

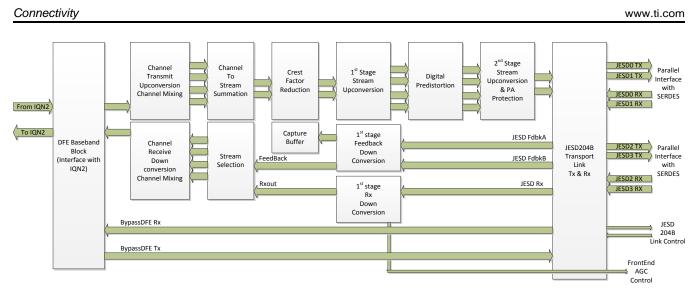

#### 1.3 Connectivity

The DFE block has the following interfaces:

IQNET2 (interface towards the SoC)

- A 128-bit wide AID bus for streaming channel IQ data between DFE and IQN2.

- A 128-bit control port for transferring DPD capture data and coefficients between the DFE and the DSP/ARM cores (PktDMA-based).

- A 32-bit VBUSP slave interface for configuration

- Two interrupt strobes (all of the DFE interrupts get aggregared into 2 interrupts signals Additional register reads are needed to determine the source of DFE interrupts).

IOs (Data and control interfaces towards data convertors)

- SERDES: 4 lanes

- (a) 2 lanes directly connected to JESD module in DFE

- (b) 2 lanes connected through muxes to allow JESD or AIL usage.

- LVDS (3 inputs and 2 outputs)

- (a) 2 JESD sync inputs and 2 sync outputs (supports connecting up to 2 devices)

- (b) 1 SYSREF input (from clock generator)

- CMOS (18 GPIOs, most important ones listed below)

- (a) 1 SYSREF request output per clock generator (from JESD)

- (b) 2 JESD sync inputs and 2 sync outputs for interfacing to data converters which do not support LVDS sync.

- (c) Several other GPIOs used for control and interrupt signalling with the external data convertors.

#### 1.4 System Overview and Use Cases

This section provides a system-level functional overview of the DFE and lists the typical use case scenarios.

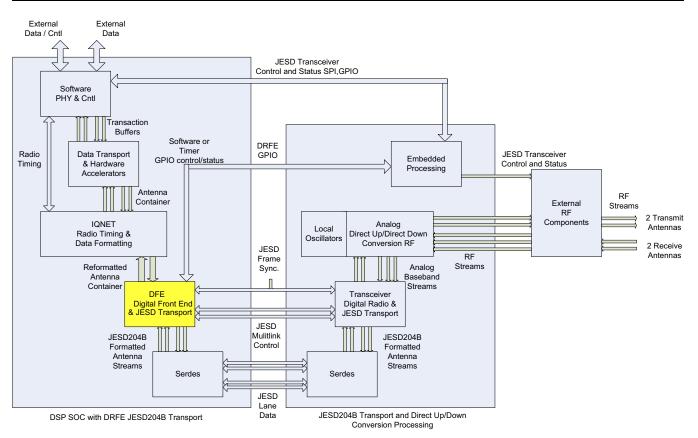

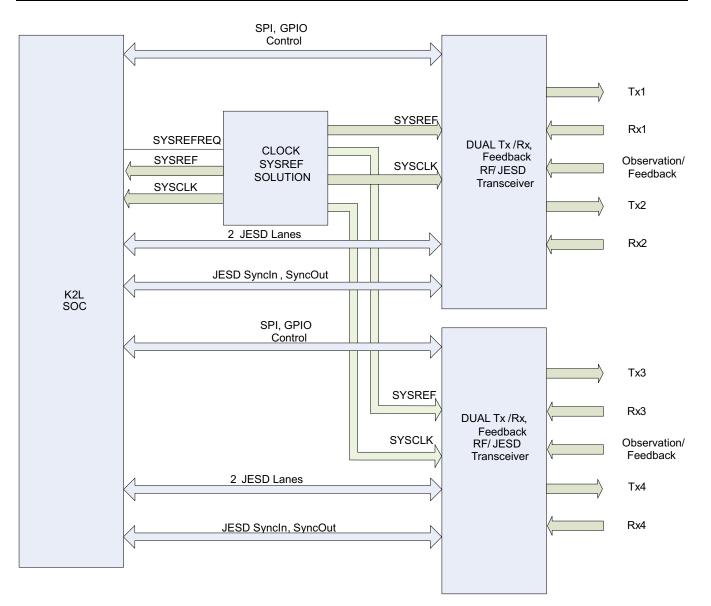

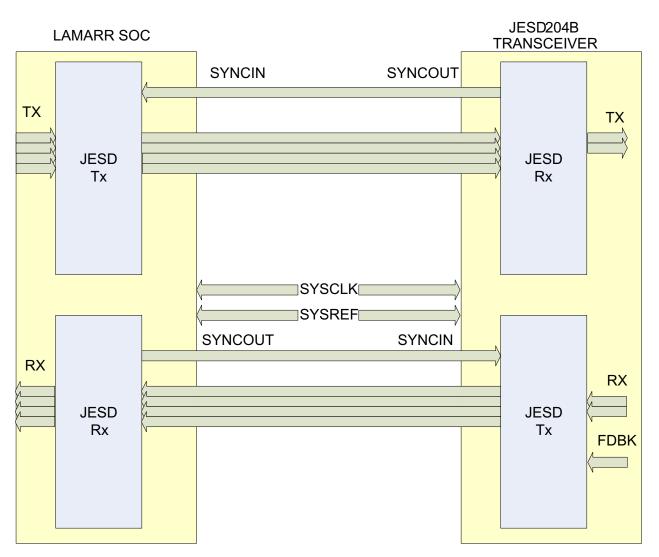

Figure 1-3. DSP SoC to JESD Transceiver SoC Flow and Control Diagram

Figure 1-3 illustrates the connections between the TCI663xK2L SoC blocks and the external transceiver or data convertor. Refer to the TCI663xK2L SoC data manual (<u>SPRS893</u>) for a general overview of the various SoC Blocks shown above.

DFE interfaces with the SoC through the IQN2 module using the AID bus. DFE RX receives JESDformatted digital channel streams from ADCs over SERDES, and unpacks them into channel containers which are sent to SoC through the IQN2 module. On the TX side, DSP sends digital channel data packed into channel containers to the DFE through the IQN2 block. DFE processes these channel containers into TX streams and after JESD formatting, sends them out to the DAC over SERDES.

DFE TX path provides additional signal processing for TX streams. JESD204B processing is used to synchronize and transport the TX streams across the JESD204B serial data interface to the external transmitter or DAC, which converts it into analog stream for RF up conversion or direct transmission.

Figure 1-4. DFE TX Signal Processing

DFE RX receives RX streams containing digital (real or complex) RX channel data from ADC sources over JESD204B transport. The received RX streams are processed and converted to the IQNet channel data container format for DSP processing.

Figure 1-5. DFE RX Signal Processing

The JESD transceiver can provide additional RX signals for wideband monitoring or additional RX capacity. DFE feedback path receives these additional RX streams, which can be used either for TX signal capture for DPD processing, or for added RX capacity. The feedback signal is treated like a JESD204B RX stream, but at the JESD204B TX stream sample rate.

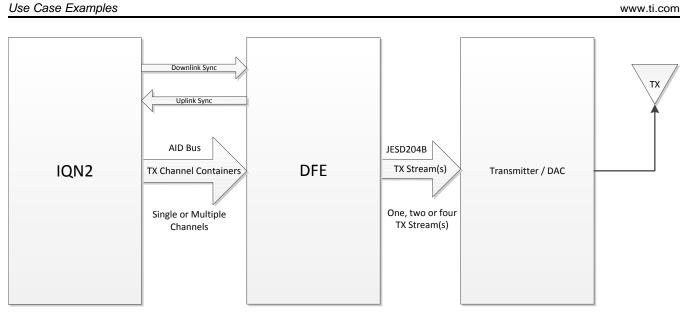

#### 1.5 Use Case Examples

The following sections present typical DFE use case scenarios.

#### 1.5.1 DFE with RF Transceiver (DAC+ADC with Integrated RF Front-End)

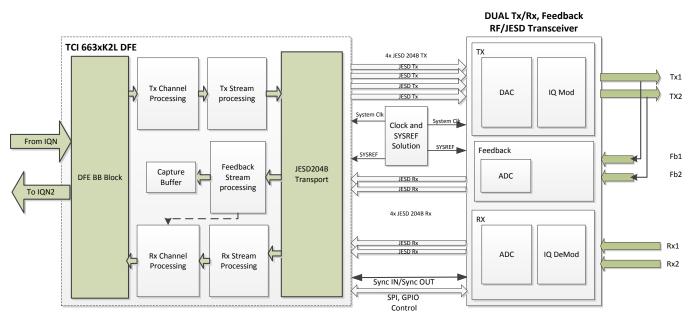

Figure 1-6. DFE with RF Transceiver

DFE can be interfaced directly with Analog Front-End (AFE) devices with integrated RF up/down conversion, for example, in wireless small cell base-stations. In such applications, TX and RX channel data is mapped to antenna streams and antenna carriers:

- Antenna Stream: An antenna stream represents a physical antenna and contains TX or RX sample data for a physical antenna. Antenna streams are the equivalent of TX or RX streams referred to in this document.

- Antenna carrier: An antenna carrier represents TX or RX sample data for a particular carrier frequency. One or more antenna carriers can be transmitted or received over the same physical antenna; in other words, an antenna stream can contain multiple antenna carriers. Antenna carriers are the equivalent of channel containers referred to in this document.

In DFE TX processing, the antenna carriers are gain corrected, filtered, interpolated, frequency translated, and combined with other antenna carriers into an antenna stream. There are additional DFE processes for each TX antenna stream including CFR, DPD, IF frequency translation, and JESD204B data transport.

In RX side, the JESD transceiver down-converts, digitizes, and processes the RF signal, then formats and outputs the JESD204B complex stream. DFE receives the RX stream (antenna stream) and applies further signal processing, including digital block down conversion and channel down conversion. The down conversion process includes frequency translation, switching, IQ rate reduction, filtering, and RX complex equalization. The RX channel data is then sent to IQNet for conversion to an antenna container. The RX processing rate for UL is the same as the TX rate, or ½ the JESD TX equivalent rate.

The DFE feedback RX path captures samples from the transmit side. This data is utilized for DPD to linearize the power amplifier output. This path can also be used as an additional receive path to add extra receive capacity (shown by a dotted line in Figure 1-6). More details about DFE TX and RX signal processing are given in further sections.

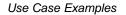

#### 1.5.2 Discrete DAC and ADC

DFE can connect to discrete JESD204B analog-to-digital and digital-to-analog data convertors which are synchronized using the two sets of JESD sync signals provided by the DFE. The clock and SYSREF solution provides phase-aligned system clock and SYSREF to the DFE (SoC), ADC, and DAC. Typically, the feedback RX stream adds additional RX capacity in this case, so the feedback RX stream processing output is sent to DDUC for RX channel processing as shown.

Figure 1-7. DFE with Discrete DAC and ADC

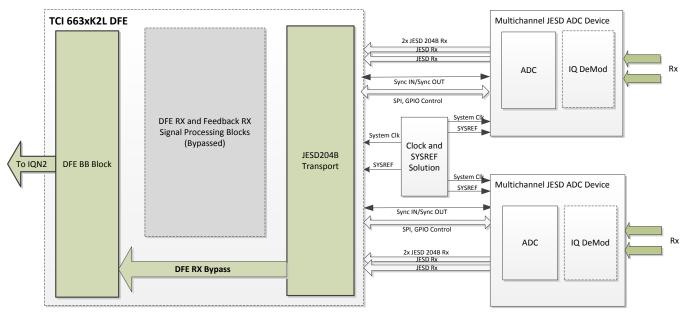

#### 1.5.3 Discrete ADC with DFE Bypass

The various signal processing blocks inside the DFE can be bypassed as shown in Figure 1-8. This allows the DFE to interface with JESD204B-based data convertors in applications involving specialized signal processing, which may be performed on DSP and other accelerators such as FFTC. These applications usually include signal acquisition over a wide bandwidth, such as medical imaging (ultra sound probes) and sonar. Two multichannel ADC devices can be connected using the two sets of JESD sync signals.

Figure 1-8. DFE RX Bypass

The ADC packs real or complex samples for multiple channels into JESD-formatted RX streams, which are received by the DFE JESD transport block. The JESD transport block unpacks (de-interleaves and decimates if needed) the samples into individual channel containers, which are sent straight to the DFE BB (baseband) block which sends them to IQN2. IQN2 then copies the samples to internal (L2SRAM or MSMCSRAM) or external (DDR3) memory for application processing.

#### **1.6 DFE TX Signal Processing and Frequency Translation**

This section shows the DFE frequency translation and processing of antenna containers into antenna streams. The antenna carriers are gain corrected, filtered, interpolated, frequency translated, and combined with other carriers into an antenna stream.

There are additional DFE processes for each TX antenna stream CFR, DPD, IF frequency translation, and JESD204B data transport.

The transmit side frequency translation can be divided into three stages.

#### 1.6.1 TX Frequency Translation Based on a Channel or Carrier

DFE contains 4 DDUC (digital down/up conversion) blocks, each of which can be programmed for transmit (up conversion) or receive (down-conversion) operations and one ratio for interpolation or decimation. In TX operation, the BB block delivers time-interleaved IQ samples to the DUC block, which interpolates the carriers and translates them to individual offset frequencies. The interpolated and frequency-translated carriers are sent to the DFE sum chain, which combines the carriers into a TX stream.

Figure 1-9 shows the frequency translation and combining on a per-channel basis inside the DFE DUC and sum chain blocks.

- 1. Individual carriers are received for DFE processing. Antenna containers from IQNet are converted to antenna carriers.

- 2. The individual carriers are interpolated and frequency-translated to an offset frequency. The offset frequency is zero for a single-carrier case.

- 3. The DFE sum chain combines the individual antenna carriers into an antenna stream.

Figure 1-9. DFE TX Channel Processing

The channel processing inside DUC consists of a programmable FIR filter, re-sampler, cascade integrator comb filter (CIC), and a channel complex mixer. The processing has several ratio rules which are based on the number of transmit or receive streams and the number of channels inside the DDUC. These ratio rules are used to define the stream IQ rate.

| Number of Transmit or Receive Streams | IQ Rate   |

|---------------------------------------|-----------|

| 1                                     | DFE Clk/2 |

| 2                                     | DFE Clk/4 |

| 4                                     | DFE Clk/8 |

DFE TX Signal Processing and Frequency Translation

www.ti.com

#### 1.6.2 TX Frequency Translation Based on a Stream or Antenna

On specific versions targeted towards wireless infrastructure applications (such as small cell basestations), DFE supports additional stream-based functions such as CFR, TX stream bulk up conversion, and DPD. Check the data sheet of your device to find out if these functions are supported.

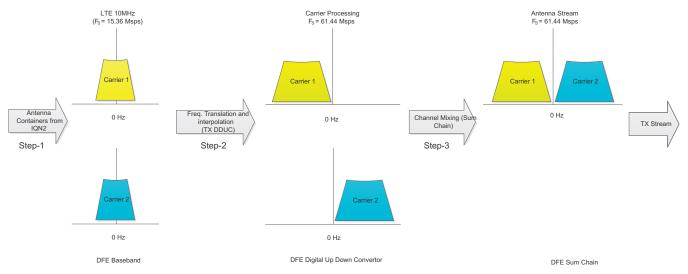

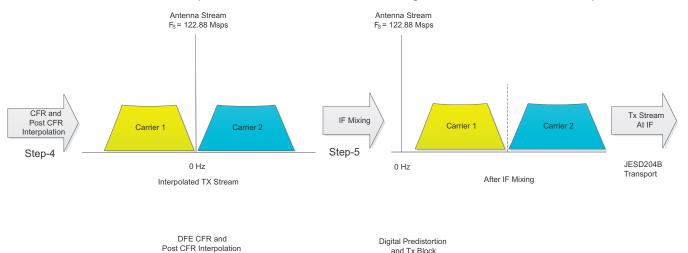

Figure 1-10 shows the interpolation and frequency translation, as applied after the channel-based frequency translation described in Section 1.5.1, and also shows at what stages CFR and DPD functionality is applied (These modules are described in Chapter 2).

- The output from DFE sum chain (combined frequency-translated channels) goes through the CFR block, which applies crest factor reduction and then interpolates to the stream rate (post CFR interpolation), as shown in Steps 4 and 5. CFR clips the peaks of the transmit signal to reduce the peak-to-average ratio (PAR), and maintain the desired spectral emission mask (SEM) and adjacent channel power ratio (ACPR).

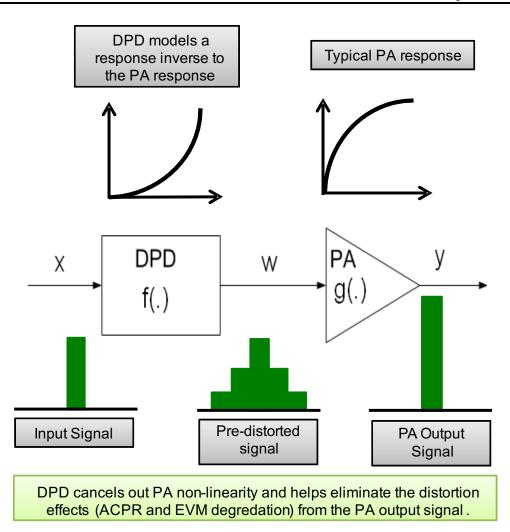

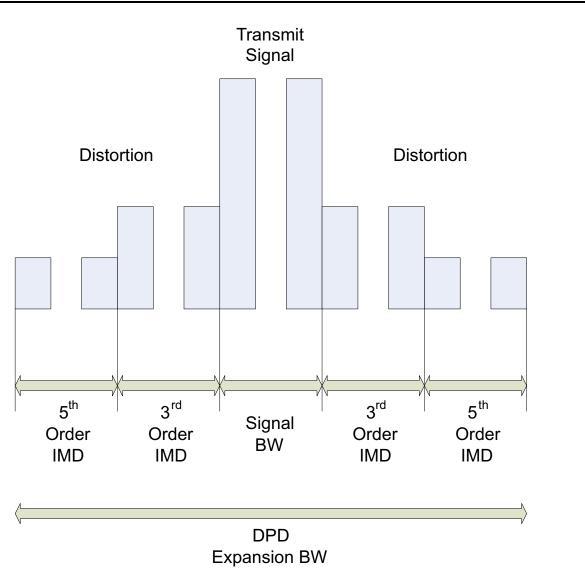

- The interpolated TX stream goes through the DPD block and IF frequency translation, then is transported over JESD204B to the JESD transceiver. DPD pre-distorts the TX signal to reduce the intermodulation distortion (IMD) from the power amplifier after the JESD transceiver.

- **NOTE:** On versions that do not support CFR and DPD, the output from the SUM chain is directly interpolated to the stream rate and transported over JESD204B.

Additionally, the DFE TX path also includes PA protection, which limits the peak power or RMS power of each TX stream. The PA protection can also set back the TX gain or inhibit a TX stream output.

#### 1.6.3 TX Frequency Translation after DFE (Inside the DAC/RF Front-End)

The last step in the TX chain is the digital-to-analog conversion and direct IQ modulation of the TX stream to the local oscillator frequency. This process is performed in the external DAC or transceiver.

- 1. The TX stream is transported over JESD204B from DFE to the JESD transceiver.

- 2. The transceiver performs digital-to-analog conversion of the TX stream and mixes it with the local oscillator frequency (direct IQ modulation).

NOTE: RF Transmit Frequency = Carrier Frequency + IF Frequency + Transmit Local Oscillator

#### 1.7 DFE RX Signal Processing and Frequency Translation

This section shows the DFE frequency translation and processing of antenna streams into antenna carriers. The analog signal is received by the external JESD transceiver, which down-converts, digitizes, and processes the RF signal, then outputs the JESD204B complex stream.

DFE receives the digital RX antenna stream over JESD204B and applies further signal processing, including digital block down conversion and channel down conversion. The down conversion process includes frequency translation, switching, IQ rate reduction, filtering, and RX complex equalization. The RX channel data is then sent to IQNet for conversion to an antenna container.

Figure 1-11. DFE RX Processing

Figure 1-11 shows the steps in RX antenna stream processing and frequency translation.

- RF analog input is received by the external JESD transceiver and frequency translated to low or zero IF (intermediate frequency). The IF is digitized, signal processed, and transported over JESD204B to the DFE.

- 2. The digital antenna RX stream is received by DFE over JESD204B.

- 3. DFE translates the intermediate frequency RX stream to zero IF and performs block down conversion.

- 4. The RX DDUC separates the carriers from the RX stream to individual offset frequencies, and decimates the carriers to the channel baseband sampling rate.

- 5. The filtered and decimated antenna carriers are gain-normalized and converted to antenna container format to be sent to IQN2, which delivers the RX channel data to the application.

**NOTE:** RF Receive Frequency = Carrier Frequency + IF Frequency + Receive Local Oscillator

There is an advanced feature in the DFE RX not discussed in the above sections: the JESD-decoded and mapped RX streams are block down converted in the RX sub-block. The block down conversion includes frequency translation, switching, IQ rate reduction and filtering, and RX complex equalization.

#### 1.7.1 Feedback RX Path

The DFE feedback RX path captures samples from the transmit side. This data is utilized for DPD calculations to linearize the power amplifier output. This path can also add additional RX capacity.

Similar to the RX path, the feedback RX stream processing starts with the external JESD transceiver, which down-converts, digitizes, and processes the RF signal, then outputs the JESD204B complex stream. The feedback stream is received over JESD204B by the DFE, which performs block down-conversion and frequency translation. The feedback data is then sent to the DFE capture buffer. However, when used as an additional RX path, the output of the feedback RX path is sent to the RX DDUC instead for channel down-conversion and decimation.

Figure 1-12. DFE Feedback RX Processing

Figure 1-12 shows the steps in feedback RX antenna stream processing and frequency translation.

- RF analog input is received by the external JESD transceiver and frequency-translated to low or zero IF (intermediate frequency). The IF is digitized, signal processed, and transported over JESD204B to the DFE.

- 2. The digital antenna RX stream is received by DFE over JESD204B.

- 3. DFE translates the intermediate frequency RX stream to zero IF, and performs equalization and gain correction. The processed output is captured in the capture buffer.

**NOTE:** RF Feedback Frequency = IF Frequency + Transmit Local Oscillator

The following additional steps apply when feedback RX is used as an additional RX Path.

- 1. The feedback RX output from step-3 is sent to RX DDUC, which performs channel down-conversion and decimation.

- 2. The filtered and decimated antenna carriers are gain-normalized and converted to antenna container format to be sent to IQN2, which delivers the RX channel data to the application.

NOTE: RF Receive Frequency = Carrier Frequency + IF Frequency + Feedback Local Oscillator

#### 1.8 DFE General Input and Output Description

Figure 1-1 shows the interfaces to DFE, and the interconnection to IQNet and SerDes blocks:

- 1. VBUSP register programming 32-bit register and memory programming interface (see IQNet Reference 2 Chapter 3)

- 2. CTL 32/64-bit DMA data interface from IQNet to DFE, used to stream DFE status, and have a higher BW interface rate to specific DFE registers and memories (see IQNet Reference 2 Chapter 3)

- 3. 2 level Interrupt 2 interrupt signals to IQNet to signal a selected DFE interrupt event (see IQNet Reference 2 Chapter 3)

- AID Bus The main baseband interface for TX and RX BB antenna carriers. The AID bus interfaces between the DFE baseband block, and the IQNet. There are separate single direction flow TX and RX synchronous buses. (see IQNet Reference 2 - Chapter 3)

- 5. DFE PLL Clock The DFE and IQNet share a common PLL clock for synchronous operation.

- SYSREF A JESD204B frame clock input sourced external to Lamar. SYSREF is distributed from the clock solution to all JESD 204B devices, to align the data frames. (see JESD204B Reference 1 -Chapter 3)

- SYNCIN There are one or two JESD204B links in TCI663xK2L DFE. These inputs monitor the JESD204B receiver status from the external JESD204B transceiver (see JESD 204B Reference 1 -Chapter 3).

- SYNCOUT There are one or two JESD204B links in TCI663xK2L DFE. These outputs indicate the status of the TCI663xK2L DFE JESD RX devices. (see JESD 204b Reference 1 - Chapter 3)

- [4] DFE JESD TX Outputs The DFE has up to 4 TX JESD204B outputs. These TX output buses go to the SerDes for parallel to serial conversion. The 4 JESD204B lanes can be used for 1, 2, or 4 TX antenna streams.

- 10. [4] DFE JESD RX Inputs The DFE has up to 4 RX JESD204B inputs. These RX input buses come from the SerDes after serial to parallel conversion. The four JESD204B lanes can be used for 1, 2, or 4 RX antenna streams. The RX antenna streams include the feedback signal.

#### 1.9 TCI663xK2L DFE Boot Mode Considerations

There are two SerDes macros on the TCI663xK2L device, CSISC2\_0 and CSISC2\_1, and each macro provides two SerDes lanes, making for a total of 4 lanes on the device. DFE shares SerDes resources with IQNet AIL (antenna interface lanes). The SerDes lanes corresponding to CSISC2\_0 are multiplexed between IQN2 AIL (used for CPRI interface in wireless base-station applications) and DFE JESD lanes 0 and 1, as shown in Figure 1-13.

The multiplexing of these lanes between IQN2 AIL and DFE is controlled at using a Boot Mode control.

Additionally, TCI663xK2L DFE has two LVDS inputs normally associated with the JESD204B SYNCIN signals. When IQN2 is configured for AIL usage (CPRI), these two LVDS signals can be repurposed to IQN sync signals using pin mux Control.

The BOOT MODE multiplexers for DFE and IQNet are shown in Figure 1-13. The Boot Mode and pin mux controls are discussed in the TCI663xK2L SoC Data Manual (<u>SPRS893</u>).

Figure 1-13. Boot Mode Shared Data Multiplexers IQNet and DFE

#### 1.10 SYSREF Logic outside DFE

In Figure 1-13 the SYSREF Logic is used to sample the external LVDS SYSREF signal with SYSCLK, and provide this signal to DFE. The SYSREF logic can also generate a test SYSREF signal used for factory tests.

The SYSREF logic register programming is discussed in the TCI663xK2L SoC Data Manual, Reference 4 (Chapter 20).

#### 1.11 DFE Power Domains

The DFE has three power domains as shown in Table 1-1. The numbers shown in the table are for listing purpose only; the actual power domain numbers are device-dependent. Check the device-specific data manual.

| Table 1-1. | Power | Domains | in | DFE |

|------------|-------|---------|----|-----|

|------------|-------|---------|----|-----|

| Power Domain | DFE Sub-blocks Serviced                 |

|--------------|-----------------------------------------|

| PD1          | Baseband; (4) DDUC; SumChain; CFR; CDFR |

| PD2          | DPD                                     |

| PD3          | TX; JESD; RX; Feedback                  |

Normally all three power domains are powered up. If DPD is not used, PD2 can be turned off, in which case the TX block is configured accordingly.

The power domain controllers are discussed in the device data manual.

#### 1.12 TCI663xK2L DFE JESD204B SerDes Lanes

The TCI663xK2L and JESD 204B transceivers can be used in two antenna or four antenna configurations. Figure 1-14 shows the two antenna configuration, while Figure 1-15 shows the four antenna configuration with multiple JESD 204B transceivers. Table 1-2 shows the number of SerDes lanes for a specific transfer rate and the number of antennas supported for the rates.

The SYSREF and SYSCLK provide the frame synchronization and clocking. The JESD SyncIn and SyncOut also are used for JESD204B synchronization and error notification. See Reference 1 in Chapter 3 for the JESD204B requirements for SYSCLK, SYSREF, SYNCIN, and SYNCOUT functions.

The TCI663xK2L DFE processes parallel IQ data. The data is passed to the SoC SerDes modules for serialization and other processing. The SoC SerDes has its own PLL and IQ transfer logic. The SerDes configuration must match the intended DFE SerDes rates.

The two antenna configuration can use two or four SerDes lanes. The four antenna configuration uses four SerDes lanes. The SerDes SoC blocks are discussed in the SerDes User Guide, Reference 3 (Chapter 3).

| Number Tx/Rx Antennas | Number SerDes Lanes | SerDes Rate | Equiv. Tx/Fdbk IQ Rate | Equiv. Rx IQ Rate |  |

|-----------------------|---------------------|-------------|------------------------|-------------------|--|

| 2                     | 2,3(w/Fdbk)         | 2.4576G     | 61.44M                 | 61.44M            |  |

| 2                     | 2,3(w/Fdbk)         | 3.6864G     | 92.16M                 | 92.16M            |  |

| 2                     | 2                   | 4.9152G     | 122.88M                | 61.44M            |  |

| 2                     | 2,3(w/Fdbk)         | 4.9152G     | 122.88M                | 122.88M           |  |

| 2                     | 2                   | 7.3728G     | 184.32M                | 92.16M            |  |

| 2                     | 4                   | 3.6864G     | 184.32M                | 92.16M            |  |

| 2                     | 4                   | 4.9152G     | 245.76M                | 122.88M           |  |

| 2                     | 4                   | 7.3728G     | 368.64M                | 184.32M           |  |

| 4                     | 4                   | 4.9152G     | 122.88M                | 61.44M            |  |

| 4                     | 4                   | 7.3728G     | 184.32M                | 92.16M            |  |

#### Table 1-2. Example Tx-Fdbk, Rx IQ Rates with JESD 204B Transport

Figure 1-14. TCI663xK2L DFE to Two Antenna JESD Transceiver Block Diagram

Figure 1-15. TCI663xK2L DFE to Four Antenna JESD Transceiver Block Diagram

#### 1.13 TCI663xK2L DFE and IQNet Clock

The DFE block operates synchronously with the IQNet block, and both blocks share the DFE PLL. The DFE block must be programmed for the appropriate clock output. The PLL is operated at either 245.76 MHz or 368.64 MHz. The DFE and IQNet configurations must be compatible to the selected DFE PLL value.

The DFE PLL for TCI663xK2L is described in the TCI663xK2L Data Manual (SPRS893).

#### 1.14 TCI663xK2L DFE GPIO Shared with Other SoC Functions

The TCI663xK2L DFE GPIO signals are shared with other TCI663xK2L SoC GPIO signals. The selection of GPIO controls is discussed in the TCI663xK2L Data Manual, Reference 4. The programming details of the TCI663xK2L DFE GPIO signals are found in the MMR tables in . The TCI663xK2L GPIO pins are also multifunctional within DFE. They are discussed later in Section 2.12.

There are additional TCI663xK2L SoC counter timer and GPIO pins that can also be used for control. The timer control and GPIO selection are discussed in Reference 4. The two general uses are:

- DFE\_GPIO, SoC\_GPIO JESD transceiver hardware trigger signal

- SoC\_Counter\_Timer JESD transceiver hardware real time trigger signal

#### 1.15 TCI663xK2L DFE Sub-Blocks and Functions

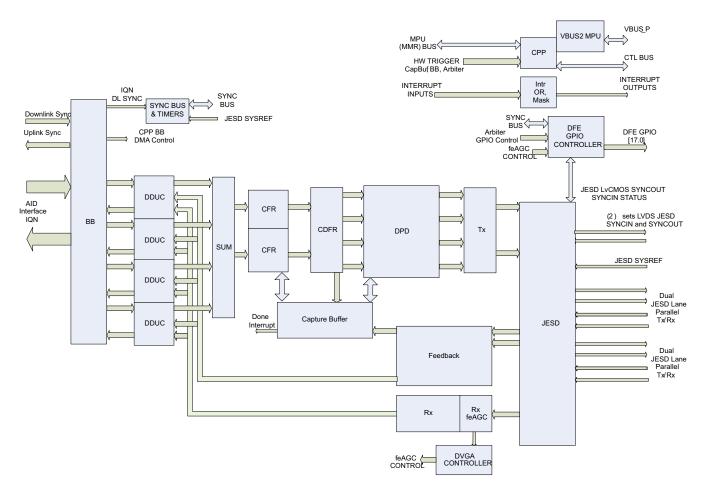

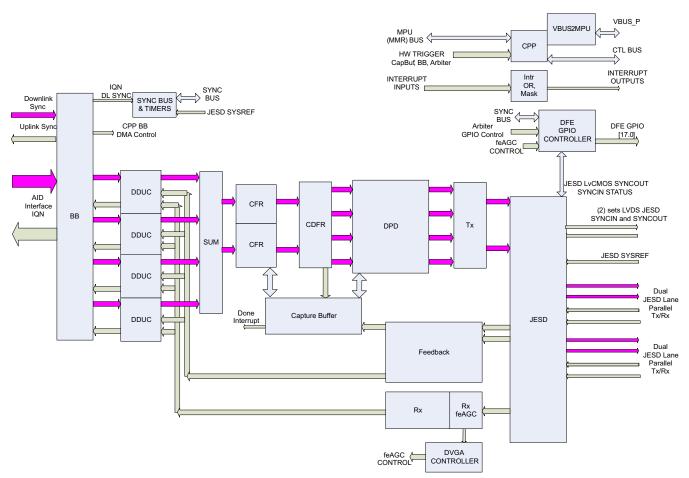

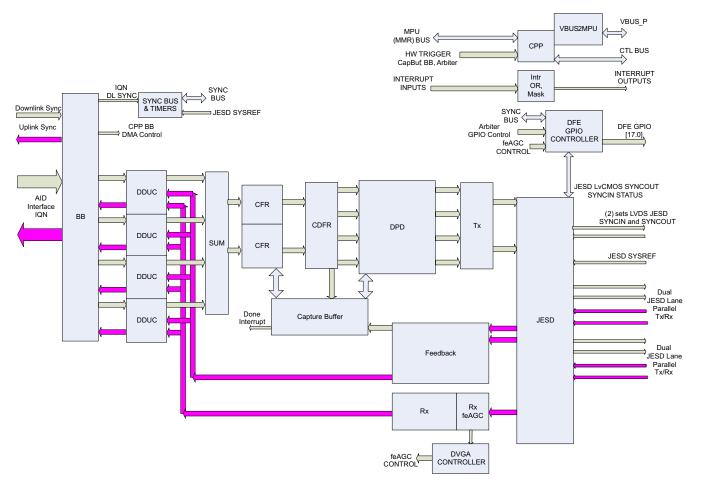

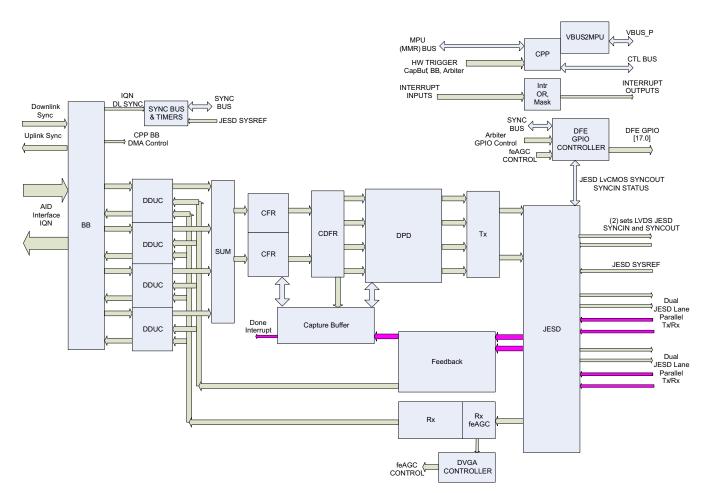

Chapter 2 has sub block data flow (TX, RX, and feedback), and discussions of each DFE sub block. The DFE block diagram is shown in Figure 1-16. Table 1-3 lists the DFE sub block abbreviation, name, and function.

| DFE Sub-Block<br>Abbrev. (xxxx – DFE<br>Main Flow<br>Tx,Rx,Fdbk) | DFE Sub-Block Name                      | DFE Sub-Block Function                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BB (Tx,Rx)                                                       | BaseBand                                | Receives and transmits the AID bus, antenna container (Axc) data to/from IQN. Formats the BB antenna carrier data for the DDUCs. Provides antenna carrier fine gain control.                                                                                                                                                                                      |

| DDUC (Tx,Rx)                                                     | Digital Down Up Converter               | Provides antenna carrier frequency translation; provides IQ filtering and rate conversion from the baseband rate to the antenna stream rate; there are 4 DDUCs; 2 Tx and 2Rx                                                                                                                                                                                      |

| SC (Tx)                                                          | SumChain                                | Combines the Tx DDUC antenna carriers into an antenna stream; provides 6db step gain control of the Tx antenna stream                                                                                                                                                                                                                                             |

| CFR (Tx)                                                         | Crest Factor Reduction                  | Provides peak clipping of each Tx antenna stream, interpolation, and circular clipping (final limiter) from the SC to the CDFR rate. Provides for Tx antenna stream fractional gain before CFR; provides for Tx antenna stream fractional gain after CFR                                                                                                          |

| CDFR (Tx)                                                        | CFR DPD Fractional<br>Resampler         | Resamples the CFR output to the DPD IQ rate of each Tx antenna stream                                                                                                                                                                                                                                                                                             |

| DPD (Tx)                                                         | Digital PreDistortion                   | Applies per Tx antenna stream, a nonlinear feed forward correction to the Tx Each Tx can have a unique set of DPD correction coefficients.                                                                                                                                                                                                                        |

| Tx (Tx)                                                          | Transmit                                | Provides Tx antenna stream IF frequency translation, provides a PA protection function for each Tx antenna stream                                                                                                                                                                                                                                                 |

| JESD (Tx,Rx,Fdbk)                                                | JESD204B Tx, Rx transport               | Provides the multilane, multilink JESD 204B transport from digital IQ for Tx and Rx/Fdbk, provides for local lane loopback for testing, provides separate Rx block and Fdbk block outputs                                                                                                                                                                         |

| Rx (Rx)                                                          | Receive                                 | Receives Rx streams from JESD performs Rx block down conversion, IF frequency translation, stream switching, decimation filtering, equalization and formatting for Rx DDUC                                                                                                                                                                                        |

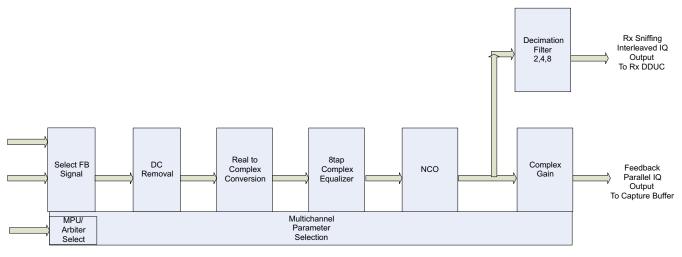

| Fdbk (Fdbk)                                                      | Feedback                                | The feedback block provides different parameters for a selected feedback signal. The feedback block has signal selection, equalization, frequency translation, and gain normalization for the capture buffer wideband output. The Feedback block has an additional decimation filter and signal formatter to send data to the Rx DDUC for Network Listening Mode. |

| CB (Fdbk,other)                                                  | Capture Buffer                          | Capture buffer collects 1 to 4 sets of signals based on timed delay, and signal statistic information. The capture buffer can also source data to specific DFE sub blocks.                                                                                                                                                                                        |

| MISC (other)                                                     | Miscellaneous – GPIO,<br>CPP, VBUSP2MPU | The CPP provides the DMA interface to and from the DFE. The VBUS2MPU provides the programmation interface to the DFE sub blocks. The GPIO logic, and counter timers are used to provide control GPIO outputs depending on user application. The DFE GPIO pins can also be used as generic SoC GPIO pins.                                                          |

Table 1-3. DFE Sub-Block Functions

DFE Sub-Block Capacity Considerations

www.ti.com

Figure 1-16. TCI663xK2L DFE Block Diagram

#### 1.16 DFE Sub-Block Capacity Considerations

The DFE capacity can be divided into several sections (See Figure 1-9):

- Antenna capacity The TCI663xK2L DFE supports one, two, or four TX and RX antennas. The feedback can be one or two antenna inputs. The antenna data is transported over JESD204B lanes. The number of SerDes lanes and the SerDes rate for each antenna can change the JESD204B SerDes usage.

- The antenna data is transported over JESD204B TX and RX SerDes links. Table 1-2 lists the most common SerDes data rates. The JESD transceiver and TCI663xK2L must be programmed for the same data interleaving and SerDes rates. The most common IQ rate for TX is 122.88 or 245.76 Mhz. The Fdbk IQ rate matches the TX IQ rate. The RX IQ rate either matches the TX IQ rate, or is ½ the TX IQ rate.

- There are 4 DDUCs within the TCI663xK2L DFE. Typically, two are used for TX and two are used for RX. Each DDUC can have from 1 to 12 carriers, but the TX output must conform to a common IQ rate, and the RX input must have a common IQ rate. Typical DDUC configuration has 1 to 6 channels with a DFE clock/4 IQ interface rate to the sum chain or RX block. Another typical configuration is a DDUC with 8 or 12 channels, with a DFE clock/8 IQ interface rate to the sum chain or RX block. Each DDUC for TX or RX must have a common interpolation (BB -> SumChain) or decimation (RX block out -> BB) ratio. The DDUC output to the sum chain has individual carriers, frequency translated. The DDUC input from the RX block has an RX, or Fdbk (NLM) has an RX stream of one or multiple carriers. The signal bandwidth (BW) is usually limited to 80% of the IQ interface rates listed above.

- The DDUC contains a PFIR (Programmable FIR Filter), re-sampler, CIC filter, and channel mixer. The PFIR has programmable coefficients. Each DDUC has a filter memory that can have one or more

filters, and an index for each channel. There are limitations to the PFIR coefficient size, depending on the number of filters stored, the number of channels in the DDUC, the IQ rate of the channel, and the DFE PLL rate. This can limit the number of DDUC channels, if a specific number of PFIR taps are desired.

- The BB to DDUC interface can support one or two signal IQ rates, where each DDUC has a common IQ rate. The number of channels and the IQ rate per channel must satisfy the following:

(2 × Number of Channels × Channel IQ Rate) ≤ DFE PLL clock.

- After the TX sumchain, the CFR block provides interpolation, peak clipping in multiple stages, and post-CFR interpolation. After CFR interpolation, the IQ rate DFE Clock/2 for two antennas and DFE Clock/4 for four antennas. A typical post CFR interpolation factor of 2 translates to up to 40% bandwidth after post CFR interpolation.

- CFR clipping is normally based on four successive peak clipping stages. The amount of CFR clipping is based on the introduced EVM in subtracting the in-band signal from the TX antenna stream. Once the EVM target is determined and the EVM budget is assigned to the digital TX stream, the amount of CFR clipping can be adjusted, during run time, by adjusting the sum shift gain, preCFR gain, and monitoring the Tx power meter.

- The CDFR block fractionally interpolates the CFR output to the desired DPD rate. The desired DPD rate is typically equal to DFE clock, DFE clock \* 2/3, or DFE clock/2. Since the interpolation after CFR and CDFR is done to provide the DPD IQ rate, the CDFR output rate is typically ≥ 3 × the signal BW. If DPD is not used, the CDFR can operate the DPD block at a lower IQ rate. The DPD expansion ratio (≥ 3) \* signal BW must fit to the DFE clock ratios available. Operating the DFE PLL at 368.64 vs. 245.76 provides more DPD IQ rate (which is used for DPD with a higher signal BW).

- There are four discrete sections for DPD, so each TX stream can have a unique nonlinear correction. Within DPD, the number of calculated solutions and memory taps can be optimized for specific system usage. The most common setup is three calculated solutions (different functions at the same time) and up to six memory taps for four antenna, or 12 memory taps for two antenna. Typically the hardware configuration is for the maximum solution and memory size, while the software adaptation can choose to update a smaller portion of the available resources.

- The TX block fractionally decimates or filters the DPD nonlinear processed signal to the desired JESD rate. See Table 1-2 for the equivalent IQ rates for the JESD204B antenna streams.

- The TX block has a PA protection logic that must be set for the desired rms or peak limiting mode. The block can be bypassed.

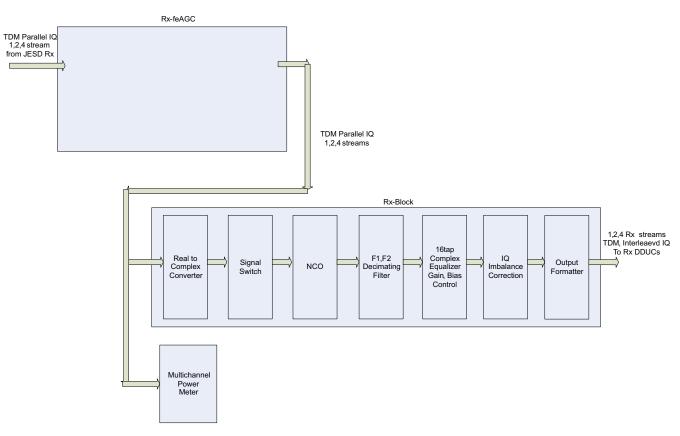

- The RX block takes the RX antenna streams, provides IF mixing, and provides decimation filtering to

match the RX DDUC interface rate (DFE Clk/4 for 2 antenna, DFE Clk/8 for 4 antenna). The signal BW

can be at most 80% BW after the decimation filtering. The RX block receives the JESD 204B

reformatted RX streams, at the TX IQ rate, or TX/2 IQ rate (when two RX streams are interleaved

within one JESD204B stream). The RX decimation matches the desired output format for the RX

DDUC to the JESD RX rate.

- The Fdbk block takes the Fdbk antenna stream from the JESD block, provides equalization, IF mixing, and gain for the wideband capture in the capture buffer. The capture buffer length and the TX = Fdbk IQ rate determine the amount of time that the software can sample the TX path for DPD adaption. Typically, the capture buffer collects the DPD input and feedback, or DPD output and feedback, to synchronously capture the DPD signal and the delayed in-time feedback.

#### 1.17 Example 2 and 4 Antenna Configurations

The RFSDK user guide discusses the configuration selection and API modification of DFE variables. Table 1-4 discusses some specific 2 and 4 antenna configurations based on wireless applications for typical LTE channels and bandwidths. The carrier types listed are per antenna values.

#### Example 2 and 4 Antenna Configurations

www.ti.com

#### Table 1-4. Example TCI663xK2L JESD Transceiver IQ Rates, Num Antennas and Carriers/Antenna

| Num Antenna |         |                      |                      |                      |                      |                                 |                                |

|-------------|---------|----------------------|----------------------|----------------------|----------------------|---------------------------------|--------------------------------|

| Tx/Rx       | BB Mode | LTE20                | LTE10                | LTE5                 | WCDMA                | TxIQ Rate                       | RxIQ Rate                      |

| 2           | Single  | 1                    |                      |                      |                      | 122.88                          | 61.44                          |

| 2           | Single  |                      | 2                    |                      |                      | 122.88                          | 61.44                          |

| 2           | Single  |                      |                      | 4-5                  |                      | 122.88                          | 61.44                          |

| 2           | Single  |                      |                      |                      | 4-5                  | 122.88                          | 61.44                          |

| 2           | Single  | 2 <sup>(1)</sup>     |                      |                      |                      | 245.76<br>184.32 <sup>(1)</sup> | 122.88<br>92.16 <sup>(1)</sup> |

| 2           | Single  |                      | 4-5                  |                      |                      | 245.76<br>184.32 <sup>(1)</sup> | 122.88<br>92.16 <sup>(1)</sup> |

| 2           | Single  |                      |                      | 7-8                  |                      | 245.76<br>184.32 <sup>(1)</sup> | 122.88<br>92.16 <sup>(1)</sup> |

| 2           | Single  |                      |                      |                      | 7-8                  | 245.76<br>184.32 <sup>(1)</sup> | 122.88<br>92.16 <sup>(1)</sup> |

| 2           | Dual    | 1 <sup>(1)</sup>     | 1-2                  |                      |                      | 122.88                          | 61.44                          |

| 2           | Dual    | 1                    |                      | 2-3                  |                      | 122.88                          | 61.44                          |

| 2           | Dual    | 1                    |                      |                      | 2-3                  | 122.88                          | 61.44                          |

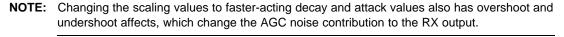

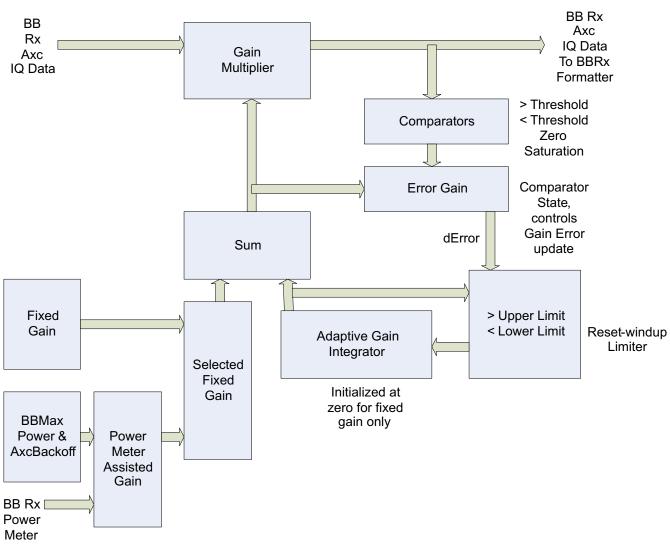

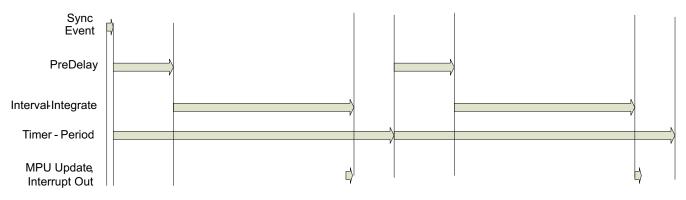

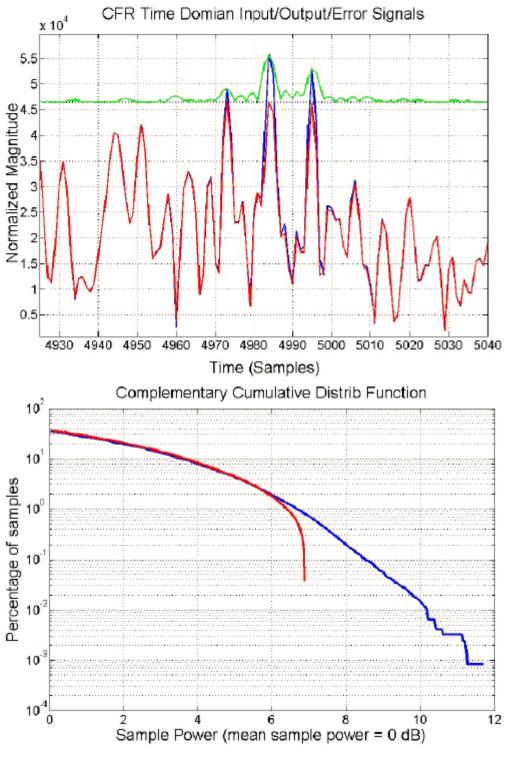

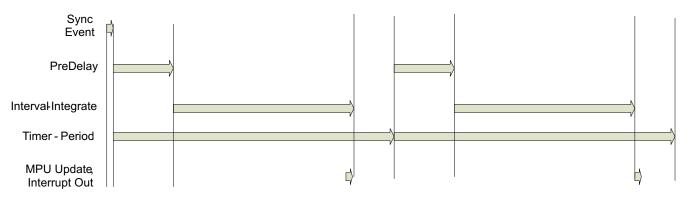

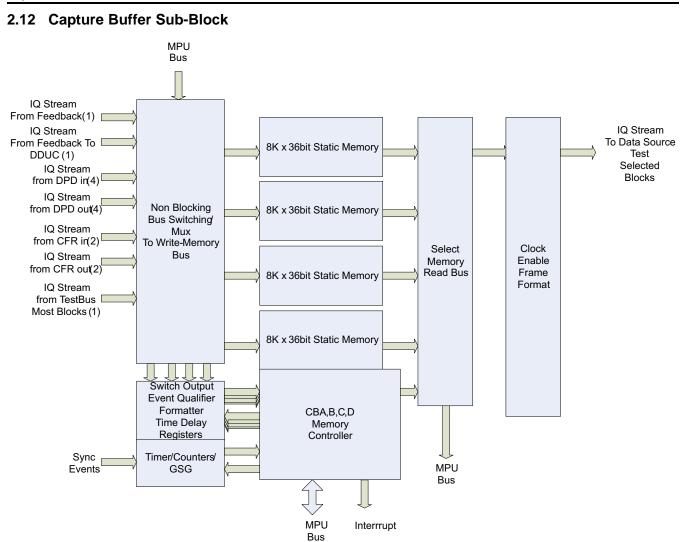

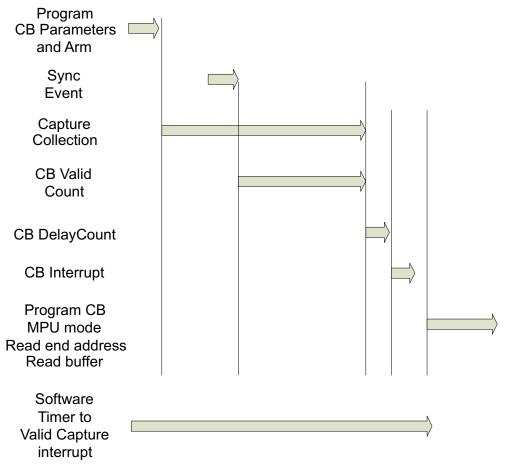

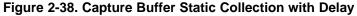

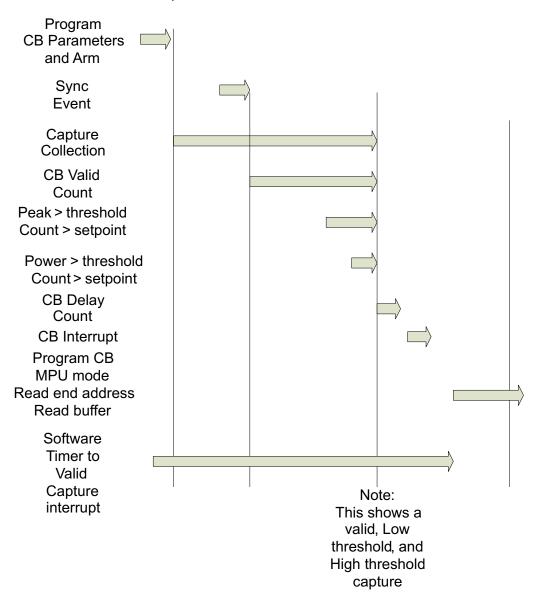

| 2           | Dual    |                      | 1-2                  | 2-3                  |                      | 122.88                          | 61.44                          |