# TMS320DM6441 Digital Media System-on-Chip Silicon Revisions 2.3, 2.1, 1.3, 1.2, and 1.1

# Silicon Errata

Literature Number: SPRZ246J September 2006-Revised August 2010

|      |            |                                                                                             | _         |

|------|------------|---------------------------------------------------------------------------------------------|-----------|

| 1    | Introdu    | ction                                                                                       | 5         |

|      | 1.1        | Device and Development Support Tool Nomenclature                                            | 5         |

|      | 1.2        | Revision Identification                                                                     | 6         |

| 2    | Silicon    | Revision 2.3 Usage Notes and Known Design Exceptions to Functional                          |           |

|      | Specifi    | cations                                                                                     | 7         |

|      | 2.1        | Usage Notes for Silicon Revision 2.3                                                        | 7         |

|      |            | 2.1.1 EDMA Transfer Request (TR) Dequeue Priority Limitation                                | 7         |

|      |            | 2.1.2 Bus Priority Inversion Can Affect DDR2 Throughput                                     | 7         |

|      |            | 2.1.3 Audio Serial Port (ASP) Transfers Should be Buffered in Internal Memory               | 8         |

|      |            | 2.1.4 DDR2 VTP I/O Calibration Must be Performed Following Device Power-up and Device Reset | 8         |

|      |            | 2.1.5 ASP: Initialization Procedure When External Device is Frame-Sync Master               | 8         |

|      |            | 2.1.6 SPI Master Mode: CSHOLD Bit Must be Initialized Twice After Reset                     | 9         |

|      |            | 2.1.7 ATA Postwrite and Pre-Fetch Do Not Provide Benefits                                   | 9         |

|      | 2.2        | Silicon Revision 2.3 Known Design Exceptions to Functional Specifications                   | 10        |

| 3    | Silicon    | Revision 2.1 Usage Notes and Known Design Exceptions to Functional                          |           |

|      | Specifi    | cations                                                                                     | 41        |

|      | 3.1        | Usage Notes for Silicon Revision 2.1                                                        | 41        |

|      | 3.2        | Silicon Revision 2.1 Known Design Exceptions to Functional Specifications                   | 41        |

| 4    | Silicon    | Revision 1.3 Usage Notes and Known Design Exceptions to Functional                          |           |

|      | Specifi    | cations                                                                                     | 42        |

|      | 4.1        | Usage Notes for Silicon Revision 1.3                                                        | 42        |

|      | 4.2        | Silicon Revision 1.3 Known Design Exceptions to Functional Specifications                   | 42        |

| 5    | Silicon    | Revision 1.2 Usage Notes and Known Design Exceptions to Functional                          |           |

|      | Specifi    | cations                                                                                     | <b>64</b> |

|      | 5.1        | Usage Notes for Silicon Revision 1.2                                                        | 64        |

|      | 5.2        | Silicon Revision 1.2 Known Design Exceptions to Functional Specifications                   | 64        |

| 6    | Silicon    | Revision 1.1 Usage Notes and Known Design Exceptions to Functional                          |           |

|      |            | cations                                                                                     | 65        |

|      | 6.1        | Usage Notes for Silicon Revision 1.1                                                        | 65        |

|      | 6.2        | Silicon Revision 1.1 Known Design Exceptions to Functional Specifications                   | 65        |

| Revi | ision Hist | ory                                                                                         | 66        |

|      |            | - ,                                                                                         | -         |

# List of Figures

| 1  | Example, Device Revision Codes for TMX320DM6441 (ZWT) and TMS320DM6441 (ZWT)    | 6  |

|----|---------------------------------------------------------------------------------|----|

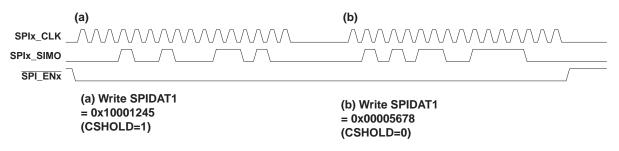

| 2  | Expected CSHOLD Behavior                                                        | 22 |

| 3  | Actual CSHOLD Behavior-32-Bit Writes to SPIDAT1                                 | 22 |

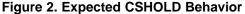

| 4  | Actual CSHOLD Behavior-Halfword Writes to SPIDAT1                               | 23 |

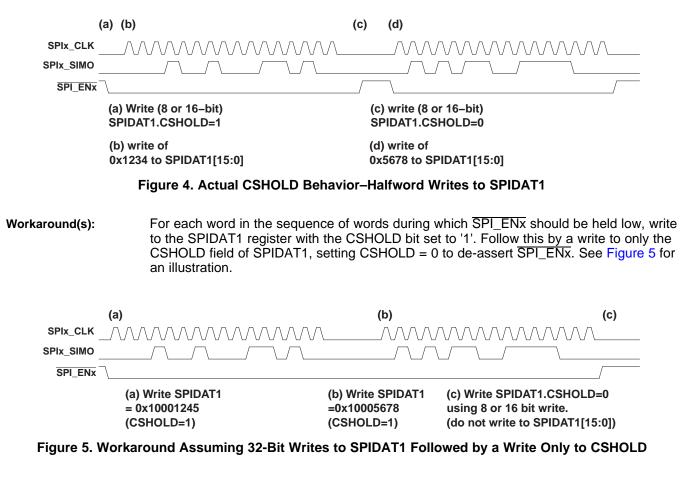

| 5  | Workaround Assuming 32-Bit Writes to SPIDAT1 Followed by a Write Only to CSHOLD | 23 |

| 6  | Workaround Assuming Halfword Writes to SPIDAT1                                  | 23 |

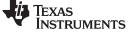

| 7  | IDMA, SDMA, MDMA Paths                                                          | 25 |

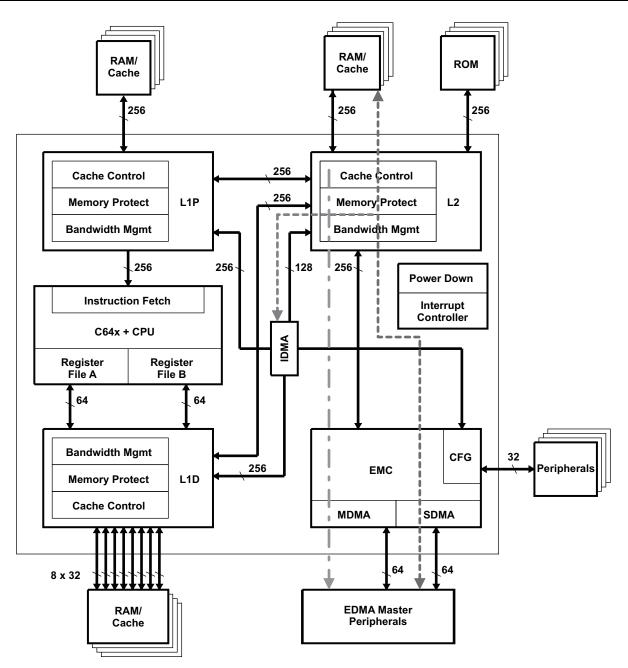

| 8  | Priority Arbitration Scheme for L2 RAM                                          | 37 |

| 9  | MSTPRI1 Register                                                                | 49 |

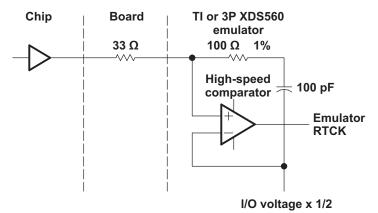

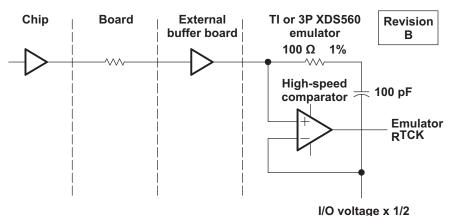

| 10 | Typical Emulation Interface Circuit                                             | 55 |

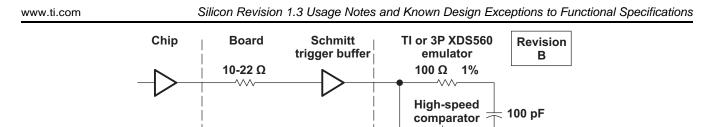

| 11 | Emulation Interface Circuit with Existing Fielded Debug Controller Pods         | 56 |

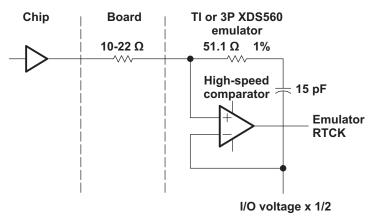

| 12 | New Target Design with Existing Fielded Debug Controller Pods                   | 57 |

| 13 | New Target Design with New Debug Controller Pods                                | 57 |

|    |                                                                                 |    |

# List of Tables

| 1  | Device Revision Codes                                                                                                                             | 6         |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 2  | Silicon Revision 2.3 Advisory List                                                                                                                | 10        |

| 3  | RBG888/RBG666 Pin Mux Options                                                                                                                     | 12        |

| 4  | USB Electrical Characteristics in Violation                                                                                                       | 17        |

| 5  | DaVinci DVSDK Software Packages, LSPs, and Patches                                                                                                | 34        |

| 6  | Allowable CPU and SDMA Priorities                                                                                                                 | 38        |

| 7  | Silicon Revision 1.3 Advisory List                                                                                                                | 42        |

| 8  | Bus Master Priority Defaults                                                                                                                      | <b>50</b> |

| 9  | RTCK Buffer Characteristics                                                                                                                       | 56        |

| 10 | Bug Summary                                                                                                                                       | 58        |

| 11 | Switching Characteristics Over Recommended Operating Conditions for VPBE Control and Data Output With Respect to PCLK and VPBECLK                 | 59        |

| 12 | Switching Characteristics Over Recommended Operating Conditions for VPBE Control and Data Output With Respect to VCLK                             | 59        |

| 13 | Switching Characteristics Over Recommended Operating Conditions for Asynchronous Memory Cycles for EMIFA Module (see Figure 6-21 and Figure 6-22) | 62        |

| 14 | Timings for ATA/CF Module — Ultra DMA AC Timing (see Figure 7-28 through Figure 7-37)                                                             | 63        |

| 15 | Silicon Revision 1.1 Advisory List                                                                                                                | 65        |

|    |                                                                                                                                                   |           |

# TMS320DM6441 DMSoC Silicon Revisions 2.3, 2.1, 1.3, 1.2, and 1.1

#### 1 Introduction

This document describes the known exceptions to the functional specifications for the TMS320DM6441 Digital Media System-on-Chip (DMSoC). [See the *TMS320DM6441 Digital Media System-on-Chip* data manual (literature number <u>SPRS359D</u> or later).] Throughout this document, TMS320DM644x and DM644x refer to the TMS320DM6441 device.

For additional information, see the latest version of the *TMS320DM644x DMSoC Peripherals Overview Reference Guide* (literature number <u>SPRUE19</u>).

The advisory numbers in this document are not sequential. Some advisory numbers have been moved to the next revision and others have been removed and documented in the user's guide. When items are moved or deleted, the remaining numbers remain the same and are not resequenced.

This document also contains Usage Notes. Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

#### 1.1 Device and Development Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all DSP devices and support tools. Each DSP commercial family member has one of three prefixes: TMX, TMP, or TMS (e.g., **TMS**320DM6441**A**ZWT). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully-qualified production devices/tools (TMS/TMDS).

Device development evolutionary flow:

- **TMX** Experimental device that is not necessarily representative of the final device's electrical specifications

- **TMP** Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

- TMS Fully-qualified production device

Support tool development evolutionary flow:

- **TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing

- **TMDS** Fully-qualified development-support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

TMS devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

All trademarks are the property of their respective owners.

5

6

Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

#### 1.2 Revision Identification

The device revision can be determined by the device revision code marked on the top of the package. The location of the device revision code for the ZWT package is shown in Figure 1. Figure 1 shows some examples of the types of DM6441 package symbolization.

Device Revision Code

Device Revision Code

A Qualified devices are marked with the letters "TMS" at the beginning of the device name, while nonqualified devices are marked with the letters "TMX" or "TMP" at the beginning of the device name.

B "#" denotes an alphanumeric character. "x" denotes an alpha character only.

#### Figure 1. Example, Device Revision Codes for TMX320DM6441 (ZWT) and TMS320DM6441 (ZWT)

Silicon revision is identified by a code on the chip. If x is "B", then the silicon is revision 2.3 for TMS devices or revision 1.3 for TMX devices. If x is "A", then the silicon is revision 2.1 for TMS devices, or revision 1.2 for TMX devices, or revision 1.1 for XDAVINCI-AZWT devices. If x is "blank", then the silicon is revision 1.3 for TMS devices. Table 1 lists the silicon revisions associated with each device revision code for the DM6441 device.

| Device Revision Code (x) | Silicon Revision | Comments                           |

|--------------------------|------------------|------------------------------------|

| В                        | 2.3              | TM <b>S</b> 320DM6441 <b>B</b> ZWT |

| A                        | 2.1              | TM <b>S</b> 320DM6441 <b>A</b> ZWT |

| (blank)                  | 1.3              | TM <b>S</b> 320DM6441ZWT           |

| В                        | 1.3              | TM <b>X</b> 320DM6441 <b>B</b> ZWT |

| A                        | 1.2              | TMX320DM6441AZWT                   |

| A                        | 1.1              | XDAVINCI – AZWT                    |

#### Table 1. Device Revision Codes

# 2 Silicon Revision 2.3 Usage Notes and Known Design Exceptions to Functional Specifications

**NOTE:** In Silicon Revision 2.3, the SPI boot mode is added as a backup to the NAND boot mode in the ROM bootloader (RBL). Additional updates have also been made to the RBL. For more information, see the *TMS320DM644x DMSoC ARM Subsystem Reference Guide* (literature number <u>SPRUE14</u>) and the *TMS320DM644x ROM Migration Guide* (literature number <u>SPRAB80</u>).

### 2.1 Usage Notes for Silicon Revision 2.3

Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes will be incorporated into future documentation updates for the device (such as the device-specific data sheet), and the behaviors they describe will not be altered in future silicon revisions.

### 2.1.1 EDMA Transfer Request (TR) Dequeue Priority Limitation

On DM6441 Silicon Revision 2.3 and earlier, if there are multiple events in both Q0 and Q1, then the transfer requests associated with events in Q0 will get submitted to TC0 prior to any transfer requests associated with events in Q1 getting submitted to TC1 — even if TC0 is busy processing earlier transfer requests and TC1 is idling. This can cause delays in submission of requests on Q1. Therefore, it is recommended to reserve the higher priority Q0/TC0 for submission of urgent, small, real-time sensitive transfers (such as audio data transferred to and from ASP) and allocate Q1/TC1 for longer, non-real-time sensitive transfers (such as block memory DDR2 to internal memory and vice versa).

### 2.1.2 Bus Priority Inversion Can Affect DDR2 Throughput

On DM6441 Silicon Revision 2.3 and earlier, under certain conditions low priority modules can occupy the bus and prevent high priority modules like the VPSS from getting the required DDR2 throughput. The DDR2 memory controller arbitration policy gives preference to accesses to open banks, regardless of the requesting modules' priorities. This is not normally an issue, but can cause a problem if a low priority module performs extremely fast, contiguous accesses. This condition can effectively lock out other modules (even with higher priorities) trying to access the DDR2 memory controller for a long period.

For example, when the ARM is executing the STM (Store Multiple) instruction with the D-cache enabled, the ARM is able to achieve a high-peak transfer rate to cache and the DDR2 burst writes from the cache can stall the OSD (On-Screen Display) subsystem from DDR2 reads to the point that the display can be unusable. This can occur even though the VPSS, by default, has the highest priority. For more details on master peripheral priorities, see the "Bandwidth Management" subsection of the *TMS320DM644x DMSoC ARM Subsystem Reference Guide* (literature number <u>SPRUE14</u>).

The DDR2 memory controller Peripheral Bus Burst Priority Register (PBBPR address 0x2000 0020) contains a user-programmable field to indicate the maximum number of 32-byte DDR2 burst transfers that can go through before the DDR2 memory controller raises the priority of the oldest request in the queue. At reset, this value defaults to 255 (0xFF), meaning that this feature is disabled and a request can remain in the queue indefinitely.

It is recommended that the value of the DDR2 memory controller Peripheral Bus Burst Priority Register (PBBPR address 0x2000 0020) be reduced to limit the length of time that a peripheral can be held off due to the policy giving preference to the open bank. There is a performance trade-off between fast, low-priority peripherals and time-critical high priority peripherals when determining a value for this parameter. A hex value of 0x20 should provide a good ARM (cache enabled) performance and still allow good utilization by the VPSS or other modules.

7

www.ti.com

Silicon Revision 2.3 Usage Notes and Known Design Exceptions to Functional Specifications

www.ti.com

#### 2.1.3 Audio Serial Port (ASP) Transfers Should be Buffered in Internal Memory

On DM6441 Silicon Revision 2.3 and earlier, Audio Serial Port (ASP) transfers may need to originate and complete from on-chip buffers, either in ARM Internal RAM (TCM) or DSP RAM. This is due to the fact that there is no tolerance for audio data dropouts that may occur due to the delays in DDR2 accesses from other masters and from unavoidable DDR2 refresh cycles; even if the Q0/TC0 is dedicated to transfers from off-chip memories. On-chip buffers might be needed to ensure immunity from DDR2 latencies are system-dependent, varying between applications, and are impacted by the amount and type of data traffic to DDR2 memories. Once completed, the data can be shuttled between the internal buffer and the DDR2 memory by using EDMA Q1/TC1.

For silicon revision 1.3 and earlier, if using on-chip buffers for ASP transfers, also see the following two advisories: 1.3.24 ARM: Concurrent Access to ARM Internal Memory May Fail, and 2.3.33 DSP SDMA/IDMA: Unexpected Stalling When Memories DSP Level 2 Memory Ports used as RAM.

#### 2.1.4 DDR2 VTP I/O Calibration Must be Performed Following Device Power-up and Device Reset

On DM6441 Silicon Revision 2.3 and earlier, the DDR2 memory controller is able to control the impedance of the output I/O. This feature allows the DDR2 memory controller to tune the output impedance of the I/O to match that of the PCB board. Control of the output impedance of the I/O is an important feature because impedance matching reduces reflections, creating a cleaner signal propagation. Calibrating the output impedance of the I/O also reduces the power consumption of the DDR2 memory controller. The calibration is performed with respect to voltage, temperature, and process (VTP). The VTP information obtained from the calibration is used to control the output impedance of the I/O.

VTP I/O calibration *must* be performed following device power-up and device reset. If the DDR2 memory controller is reset via the Power and Sleep Controller (PSC), and the VTP input clock is disabled, accesses to the DDR2 memory controller will not complete. To re-enable accesses to the DDR2 memory controller, enable the VTP input clock, then perform the VTP calibration sequence again. The VTP calibration is part of the DDR2 memory controller initialization sequence. For more information on the VTP calibration and the proper DDR2 memory controller initialization sequence, see the *TMS320DM644x DMSoC DDR2 Memory Controller User's Guide* (literature number <u>SPRUE22</u>).

#### 2.1.5 ASP: Initialization Procedure When External Device is Frame-Sync Master

On DM6441 Silicon Revision 2.3 and earlier, if the ASP transmitter expects a frame sync from an external device, care must be taken to ensure that the proper action is employed. After the transmitter comes out of reset (XRST = 1), it waits for a frame sync from the external device. If the first frame sync arrives very shortly after the transmitter is enabled, the CPU or EDMA controller may not have a chance to service the ASP data transmit register (DXR). In this case, the transmitter shifts out the default data in the transmit shift register (XSR) instead of the desired value, which has not yet arrived in the DXR. This causes problems in some applications such that the first data element in the frame is invalid. The data stream appears element-shifted (the first data word may appear in the second channel instead of the first).

To ensure proper operation when the external device is the frame master, you must make sure that the DXR is already serviced with the first word when a frame sync occurs. To do so, you can keep the transmitter in reset until the first frame sync is detected. The software is set up such that it will only take the transmitter out of reset (XRST = 1) promptly after detecting the first frame sync. This ensures that the transmitter does not begin data transfers at the data pin during the first frame-sync period. This also provides almost an entire frame period for the DM6441 device to service the DXR with the first word before the second frame sync occurs. The transmitter only begins data transfers upon receiving the second frame sync. At this point, the DXR is already serviced with the first word.

The ASP transmitter and receiver on the DM6441 device are capable of generating an interrupt upon the detection of frame synchronization. However, on the DM6441 device, the receiver and/or transmitter must be out of reset to enable this feature. Therefore, instead of directly using the ASP interrupt to detect the first frame sync, on the DM6441 device you can use the GPIO peripheral. This can be achieved by connecting the frame-sync signal to a GPIO pin. The software can either poll the GPIO pin to detect the first frame sync or program the GPIO peripheral to generate an interrupt to the CPU upon detecting the first frame-sync edge. For more information on the GPIO peripheral, see the *TMS320DM644x DMSoC General-Purpose Input/Output (GPIO) User's Guide* (SPRUE25). For details on the initialization sequence when the external device is the frame-sync master, see the *TMS320DM644x DMSoC Audio Serial Port (ASP) User's Guide* (SPRUE29).

8

#### 2.1.6 SPI Master Mode: CSHOLD Bit Must be Initialized Twice After Reset

On DM6441 Silicon Revision 2.3 and earlier, in addition to the procedure described in Advisory 2.3.32 (SPI Master Mode: Extra Step Required to Use CSHOLD), the SPIDAT1.CSHOLD bit must be initialized twice with the same value after reset and before the first SPI transfer. This is required to clear an internal pipeline stage in the CSHOLD logic.

#### 2.1.7 ATA Postwrite and Pre-Fetch Do Not Provide Benefits

On DM6441 Silicon Revision 2.3 and earlier, when the Host Controller (DM6441) is performing a Read/Write transaction onto an HDD or CF Devices via a PIO Transaction, then the CPU (ARM) is responsible for Reading and Writing the data by directly accessing the Data Register Port. Since the interface speed is slower than the ARM CPU, it is required that an Internal Wait State be generated by the Host Controller to slow down the CPU (ARM). However, this wait time is much larger than a PIO Cycle time increasing the cycle time indirectly.

This problem is a common problem with many CPUs including ARM. In order to alleviate this problem, the ATA module designer has incorporated a feature that allows the CPU to write directly to the DMA FIFO, as opposed to the Data Register, in order to perform a Burst Access and avoiding the back to back wait state issue. This feature is enabled via activating the Postwrite/Prefetch capability.

Even though this feature is activated, it is observed that the CPU is taking about the same time to offload and upload data from the FIFO when compared with accessing the Data Register, i.e., data path through the FIFO did not give us any additional leverage.

9

## 2.2 Silicon Revision 2.3 Known Design Exceptions to Functional Specifications

Table 2. Silicon Revision 2.3 Advisory List

| Title                                                                                                        | Page |

|--------------------------------------------------------------------------------------------------------------|------|

| Advisory 2.3.3 — VPFE: CCDC DC-Subtract Function Does Not Clip Luma to Zero for YUV Modes                    | 11   |

| Advisory 2.3.4 — VPFE: CCDC Register Write Shadowing Does Not Work                                           | 11   |

| Advisory 2.3.5 — VPFE: Pixel Misalignment on CCDC to Preview Engine Path                                     | 11   |

| Advisory 2.3.11 — VPBE: RGB666 Pin Mux Option Does Not Work                                                  | 12   |

| Advisory 2.3.12 — VPBE: Restriction on Horizontal Width for RGB888 Video Windows                             | 13   |

| Advisory 2.3.13 — USB: Extraneous USB Interrupts Generated                                                   | 15   |

| Advisory 2.3.18 — SPI: Receive Overrun Interrupt and Bit Error Can be Lost                                   | 16   |

| Advisory 2.3.19 — SPI: RXINTFLG Bit in SPIFLG Register May Not Get Cleared                                   | 16   |

| Advisory 2.3.20 — SPI: A Write to SPIFLG Receiver Overrun Bit Does Not Clear the Flag                        | 16   |

| Advisory 2.3.21 — SPI: The Receive Overrun Interrupt Flag is Not Set                                         | 16   |

| Advisory 2.3.27 — USB: Some Electrical Parameters Violate USB Specification                                  | 17   |

| Advisory 2.3.28 — DSP Subsystem: Back-to-Back SPLOOPs With Interrupts Can Cause Incorrect Operation on C64x+ | 18   |

| Advisory 2.3.29 — DSP Subsystem: C64x+ Incorrectly Generates False Exceptions for Multiple Writes            | 19   |

| Advisory 2.3.30 — SPI: SPIINTVECT and SPIFLG Registers are Cleared When Read in Debug Mode                   |      |

| Advisory 2.3.31 — SPI: SPI Master Receives Extra Bit When SPICLK Polarity Changes                            | 21   |

| Advisory 2.3.32 — SPI Master Mode: Extra Step Required to Use CSHOLD                                         | 22   |

| Advisory 2.3.33 — DSP SDMA/IDMA: Unexpected Stalling When Memories DSP Level 2 Memory Ports Used as RAM.     | 24   |

| Advisory 2.3.34 — VPBE: Restriction When 6/5 Vertical Expansion Filter is Enabled                            |      |

| Advisory 2.3.36 — DSP: Internal Clock Misalignment                                                           |      |

| Advisory 2.3.37 — VPFE: Preview Engine Hangs When the Video Port is Enabled in CCDC                          |      |

| Advisory 2.3.40 — VPBE: VENC Default Luma Interpolation Filter Does Not Clip to Zero                         |      |

| Advisory 2.3.41 — VLYNQ/ASP: VLYNQ and Audio Transfers Induce Noise Into the Audio Stream                    |      |

| Advisory 2.3.42 — VPBE (S/W): Linux Legacy Video Driver Causes Jittering on Video Windows                    |      |

| Advisory 2.3.43 — USB (Device Mode): Calculated CRC Value Does Not Match Host CRC Value                      |      |

| Advisory 2.3.44 — DMA Access to L2 SRAM May Stall When the C64x+ CPU Command Priority is Lower Than or       |      |

| Equal to the DMA Command Priority                                                                            | 37   |

| Advisory 2.3.45 — VPBE: Video Window 0 Corruption in RGB Mode When Video Window 1 Enabled                    | 39   |

| Advisory 2.3.46 — VPBE: Video Window Buffer Location Limitation in Multibuffer Application                   | 40   |

| www.ti.com            | Silicon Revision 2.3 Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advisory 2.3.3        | VPFE: CCDC DC-Subtract Function Does Not Clip Luma to Zero for YUV Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Details:              | The CCD Controller (CCDC) in the VPFE subsystem includes an optional Luma DC-subtract function for YUV processing. This subtract operation does not clip Luma to zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       | Note: The Optical Black Clamp/DC-subtract function for the <i>Raw Data</i> modes <i>does</i> properly clip to zero for R/G/B and Ye/Cy/G/Mg color spaces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Workaround(s):        | Do not use the DC-subtract function for YUV modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Advisory 2.3.4        | VPFE: CCDC Register Write Shadowing Does Not Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Details:              | Register write shadowing in the CCDC does not work correctly (CCDCFG.VDLC = 0).<br>Due to this bug, the CCDC PCR.ENABLE and the CCDCFG.YCINSWP fields are always<br>shadowed, regardless of the setting of CCDCFG.VDLC. The SDR_ADDR register will<br>only work correctly when CCDCFG.VDLC = 1, otherwise a delayed write to the<br>SDR_ADDR occurs, creating an unexpected delay in outputting the image to SDRAM.<br>Other registers, listed in the subsection <i>Programming the CCDC</i> under "Registering<br>Accessibility During Frame Processing" of the <i>TMS320DM644x DMSoC Video</i><br><i>Processing Front End (VPFE) User's Guide</i> (literature number <u>SPRUE38</u> ), are affected<br>such that shadowing does not occur on the next frame as specified. |

| Workaround(s):        | Set CCDCFG.VDLC = 1, such that all registers, except those noted above, are<br>Busy-Writable, which forces register writes to take effect immediately. If changes to the<br>other registers are required, the CCDC should be disabled, and the current frame should<br>be allowed to complete. Register changes can then be made, and the CCDC can then<br>be re-enabled.                                                                                                                                                                                                                                                                                                                                                                                                   |

| Advisory 2.3.5        | VPFE: Pixel Misalignment on CCDC to Preview Engine Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Details:              | There can be a timing glitch between the asynchronous VPFE input pixel clock and the internal VPFE clock that can cause pixel misalignment on the CCDC to PREV path. This misalignment is observed as causing a "pink" effect on the processed image (since the color pattern is misaligned). Once this first frame is adversely affected, the PREV hardware does not reset itself properly for subsequent frames, so the output will keep looking pink for the duration of the Preview mode. A similar issue on the end pixel can occur as well.                                                                                                                                                                                                                           |

| Workaround(s):        | Define the Preview Engine processing frame to start no earlier than the second pixel on<br>a line and to end no later than the second-to-last pixel on a line. This requires the CCDC<br>to be configured to transfer more pixels per line than is needed by the Preview Engine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Advisory 2.3.11 VPBE: RGB666 Pin Mux Option Does Not Work

Revision(s) Affected: 2.3 and earlier

Details: The intention of the RGB666 pin mux option (PINMUX0 register at 0x01C4 0000) is to allow the users to configure PWM2/B2/GPIO47 and PWM1/R2/GPIO46 pins as B2 and R2 functions, respectively. However, due to a hardware limitation, setting the RGB666 bit (PINMUX0.22) *does not* enable the B2 and R2 functions.

**Workaround(s):** Enable the RGB888 pin mux option (PINMUX0.23 = 1).

When the RGB888 pin mux option is enabled, the **B2** and **R2** pin functions are available; however, by enabling the RGB888 pin mux option, the six additional pins lose their GPIO pin function capability (see Table 3).

| PINMUX0            |                    | PIN FUNCTIONS          |                        |               |              |              |                          |                            |              |

|--------------------|--------------------|------------------------|------------------------|---------------|--------------|--------------|--------------------------|----------------------------|--------------|

| RGB888<br>(Bit 23) | RGB666<br>(Bit 22) | PWM2/<br>B2/<br>GPIO47 | PWM1/<br>R2/<br>GPIO46 | R1/<br>GPIO38 | B1/<br>GPIO6 | G1/<br>GPIO5 | C_FIELD/<br>R0/<br>GPIO4 | LCD_FIELD/<br>B0/<br>GPIO3 | G0/<br>GPIO2 |

| 0                  | 0                  | GPIO47                 | GPIO46                 | GPIO38        | GPIO6        | GPIO5        | GPIO4                    | GPIO3                      | GPIO2        |

| 0                  | 1                  | B2                     | R2                     | GPIO38        | GPIO6        | GPIO5        | GPIO4                    | GPIO3                      | GPIO2        |

| 1                  | х                  | B2                     | R2                     | R1            | B1           | G1           | R0                       | B0                         | G0           |

#### Table 3. RBG888/RBG666 Pin Mux Options

| www.ti.com            | Silicon Revision 2.3 Usage Notes and Known Design Exceptions to Functional Specification                                                                                                                                                                                       |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advisory 2.3.12       | VPBE: Restriction on Horizontal Width for RGB888 Video Windows                                                                                                                                                                                                                 |

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                |

| Details:              | When a video window is configured for RGB888 data-input mode, certain horizontal width configurations result in corrupted video windows. The problem occurs at different widths, depending on enabling horizontal zoom (1x, 2x, and 4x) and/or 9/8 horizontal expansion modes. |

| Workaround(s):        | To work around this problem, the following constraints must be met for each case:                                                                                                                                                                                              |

|                       | Case 1a: Video Window 0 (in RGB888 mode)                                                                                                                                                                                                                                       |

|                       | When 1x, 2x, 4x zoom, or 9/8 expansion is enabled, VIDWIN0 <b>XL</b> must <b>NOT</b> be inside the ranges defined below:                                                                                                                                                       |

|                       | <ul> <li>Z* (179 + 256N - 3) pixels &lt; VIDWIN0XL &lt; Z*(179 + 256N + 3) pixels</li> <li>Z*(261.5 + 256N - 5.5) pixels &lt; VIDWIN0XL &lt; Z*(261.5 + 256N + 5.5) pixels</li> </ul>                                                                                          |

|                       | for all integer values of N where:                                                                                                                                                                                                                                             |

|                       | Z = 1, 2, 4, or 9/8                                                                                                                                                                                                                                                            |

|                       | XL register is the video window's horizontal display width in pixels (window width).                                                                                                                                                                                           |

|                       | EXAMPLE:                                                                                                                                                                                                                                                                       |

|                       | When 1x zoom ( $Z = 1$ ) is enabled on video window 0, the prohibited VIDWIN0 <b>XL</b> ranges are the following:                                                                                                                                                              |

|                       | <ol> <li>(179 + 256N - 3) &lt; VIDWIN0XL &lt; (179 + 256N + 3) for all integer values of N</li> <li>(261.5 + 256N - 5.5) &lt; VIDWIN0XL &lt; (261.5 + 256N + 5.5) for all integer values of N</li> </ol>                                                                       |

|                       | <ul> <li>For example,</li> <li>VIDWIN0XL = 436 will not work because this value falls inside the first range defined above when N = 1 (432 &lt; VIDWIN0XL &lt; 438).</li> </ul>                                                                                                |

|                       | <ul> <li>VIDWIN0XL = 1026 will not work because this value falls inside the second range<br/>defined above when N = 3 (1024 &lt; VIDWIN0XL &lt; 1030).</li> </ul>                                                                                                              |

|                       | <ul> <li>VIDWIN0XL = 1024 will work because this value does not fall inside either ranges<br/>defined above for any N.</li> </ul>                                                                                                                                              |

|                       | Case 1b: Video Window 0 (in RGB888 mode)                                                                                                                                                                                                                                       |

|                       | When (2x)*(9/8) or (4x)*(9/8) is enabled, VIDWIN0 <b>XL</b> must <b>NOT</b> be inside the ranges defined below:                                                                                                                                                                |

|                       | <ul> <li>Z* (179 + 256N - 3) pixels &lt; VIDWIN0XL &lt; Z*(179 + 256N + 3) pixels</li> <li>Z*(261.5 + 256N - 5.5) pixels &lt; VIDWIN0XL &lt; Z*(261.5 + 256N + 5.5) pixels</li> <li>VIDWIN0XL = (Z/2)*(1 + 72N)</li> </ul>                                                     |

|                       | for all integer values of N where:                                                                                                                                                                                                                                             |

|                       | $Z = 2$ when $(2x)^*(9/8)$ is enabled and                                                                                                                                                                                                                                      |

|                       |                                                                                                                                                                                                                                                                                |

Z = 4 when  $(4x)^*(9/8)$  is enabled

XL register is the video window's horizontal display width in pixels (window width).

#### Case 2a: Video Window 1 (in RGB888 mode)

When 1x, 2x, 4x zoom or 9/8 expansion is enabled, VIDWIN1XL must NOT be inside the ranges defined below:

- Z\*(91.5 + 256N 5.5) pixels < VIDWIN1XL < Z\*(91.5 + 256N + 5.5) pixels

- Z\*(173.5 + 256N 3.5) pixels < VIDWIN1XL < Z\*(173.5 + 256N + 3.5) pixels

for all integer values of N where:

Z = 1, 2, 4, or 9/8

XL register is the video window's horizontal display width in pixels (window width).

#### Case 2b: Video Window 1 (in RGB888 mode)

When  $(2x)^*(9/8)$  or  $(4x)^*(9/8)$  is enabled, VIDWIN1**XL** must **NOT** be inside the ranges defined below:

- Z\*(91.5 + 256N 5.5) pixels < VIDWIN1**XL** < Z\*(91.5 + 256N + 5.5) pixels

- Z\*(173.5 + 256N 3.5) pixels < VIDWIN1XL < Z\*(173.5 + 256N + 3.5) pixels

- VIDWIN1**XL** =  $(Z/2)^*(1 + 72N)$

for all integer values of N where:

Z = 2 when  $(2x)^*(9/8)$  is enabled and

Z = 4 when  $(4x)^*(9/8)$  is enabled

XL register is the video window's horizontal display width in pixels (window width).

| www.ti.com            | Silicon Revision 2.3 Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Advisory 2.3.13       | USB: Extraneous USB Interrupts Generated                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Details:              | When the DM6441 device is in high-speed (HS) USB peripheral mode and suspended,<br>an extraneous SUSPEND interrupt can be generated if the host issues a RESET.<br>Although an extraneous SUSPEND interrupt is generated, the reset interrupt still arrives<br>as expected at the end-of-reset sequence.                                                                                  |  |  |  |  |

|                       | Also, when the DM6441 device is in peripheral mode (full-speed [FS] or high-speed [HS]) and being reset to HS mode (RESET with chirping), an extraneous RESET interrupt can be generated during the reset sequence.                                                                                                                                                                       |  |  |  |  |

| Workaround(s):        | <ol> <li>To work around the problem, the following constraints must be met:</li> <li>Software should ignore SUSPEND interrupts when already in a "suspended" state.</li> <li>Software <i>must</i> service every USB RESET interrupt. The interrupt flags <i>must</i> be cleared before doing any register reads or setups so that any following USB interrupts are not missed.</li> </ol> |  |  |  |  |

| Advisory 2.3.18       | SPI: Receive Overrun Interrupt and Bit Error Can be Lost                                                                                                                                                                                                                                                                                  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                                                                           |

| Details:              | Receive Overrun Interrupt (RXOVINT) and Bit Error interrupt (BITERRINT) can be lost if:<br>Reading of the SPIFLG register coincides with the setting of these interrupt flag bits.<br>Reading of the upper 16 bits of SPIBUF register coincides with the setting of these<br>interrupt bits.                                              |

| Workaround(s):        | Use the interrupt instead of the polling method to check the status of these interrupts.                                                                                                                                                                                                                                                  |

|                       | Access only the lower 16 bits of the SPIBUF register to read received data.                                                                                                                                                                                                                                                               |

|                       | If the polling method must be used, group the error interrupts into one Level (i.e., Level0) and the RX complete interrupt into the other Level (i.e., Level1). Use the SPIINTVECT0 and SPIINTVECT1 registers to find out the interrupt status first and then only read the SPIFLG register to decode the source of the error interrupts. |

| Advisory 2.3.19       | SPI: RXINTFLG Bit in SPIFLG Register May Not Get Cleared                                                                                                                                                                                                                                                                                  |

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                                                                           |

| Details:              | The RXINTFLG bit in the SPIFLG register may not get cleared by reading the SPIBUF register when the read coincides with the setting of the RXINTFLG bit due to new data arrival.                                                                                                                                                          |

| Workaround(s):        | When the above condition occurs, the system is at the verge of receive overrun.<br>Therefore, either optimize the SPIBUF servicing routine to avoid receive overrun or use<br>the EDMA3 to avoid the race condition from occurring.                                                                                                       |

| Advisory 2.3.20       | SPI: A Write to SPIFLG Receiver Overrun Bit Does Not Clear the Flag                                                                                                                                                                                                                                                                       |

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                                                                           |

| Details:              | A write to the SPIFLG receiver overrun (SPIFLG.OVRNINTFLG) bit does not clear the flag if the write coincides with the setting of the receive interrupt flag (SPIFLG.RXINTFLG).                                                                                                                                                           |

| Workaround(s):        | Write to the SPIFLG.OVRNINTFLG bit, then read back the value of the flag. If the flag did not clear, then write to clear the flag again.                                                                                                                                                                                                  |

| Advisory 2.3.21       | SPI: The Receive Overrun Interrupt Flag is Not Set                                                                                                                                                                                                                                                                                        |

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                                                                           |

| Details:              | The Receive Overrun Interrupt flag is not set if the overrun condition that sets the interrupt flag coincides with a read of the upper bytes (bits 31:24) of the SPIBUF register.                                                                                                                                                         |

| Workaround(s):        | None                                                                                                                                                                                                                                                                                                                                      |

| www.ti.com            | Silicon Revision 2.3 Usage Notes and Known Design Exceptions to Functional Specifications |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| Advisory 2.3.27       | USB: Some Electrical Parameters Violate USB Specification                                 |  |  |  |  |

| Revision(s) Affected: | 2.3 and earlier                                                                           |  |  |  |  |

| Details:              | Some electrical characteristics violate the USB 2.0 specification; see Table 4.           |  |  |  |  |

| Workaround(s):        | Consider this violation and design your system accordingly.                               |  |  |  |  |

|                       |                                                                                           |  |  |  |  |

|                                   |                                                                               | US<br>SPECIFI | -   | DM6 | 441 DATA MANUAL                                            | UNIT |

|-----------------------------------|-------------------------------------------------------------------------------|---------------|-----|-----|------------------------------------------------------------|------|

|                                   |                                                                               | MIN           | MAX | MIN | MAX                                                        |      |

| V <sub>HSDSC</sub> <sup>(1)</sup> | USB high-speed disconnect detection threshold (differential signal amplitude) | 525           | 625 | 525 | The lesser of:<br>1. VOD_DIS <sup>(2)</sup> - 75<br>2. 710 | mV   |

<sup>(1)</sup> V<sub>HSDSC</sub> violates the USB 2.0 specification.

<sup>(2)</sup> VOD\_DIS = High-speed differential output voltage during a disconnected state.

#### Advisory 2.3.28 DSP Subsystem: Back-to-Back SPLOOPs With Interrupts Can Cause Incorrect Operation on C64x+

Revision(s) Affected: 2.3 and earlier

Details: Back-to-back software pipeline loops (SPLOOPs) with interrupts can cause incorrect operation on C64x+. This bug occurs when the first SPLOOP is interrupted and there are less than 2 execute packets between the SPKERNEL of the first SPLOOP block (SPKERNEL instruction marks the end of the first SPLOOP block) and the SPLOOP instruction of the second SPLOOP block (SPLOOP instruction marks the beginning of the second SPLOOP block). The first SPLOOP block terminates abruptly (i.e., without completing the loop, even though the termination condition is false). The failure mechanism can be seen as a hang or by the first SPLOOP block draining for the interrupt and starting the second SPLOOP block without taking the interrupt or returning to complete the first SPLOOP block.

Workaround(s): The C6000 compiler release v6.0.6 and above detects this problem. If there are fewer than 2 execute packets between the SPKERNEL and SPLOOP instructions, the compiler will add the appropriate number of NOP instructions following the SPKERNEL instruction.

For example,

|       | • • •    |        |                                   |

|-------|----------|--------|-----------------------------------|

|       | SPKERNEL | 0, 0   |                                   |

|       | NOP      | 1      | ; SDSCM00012367 HW bug workaround |

|       | MVK .L1  | 0x1,A0 |                                   |

| [ A0] | SPLOOPW  | 3      | ;12                               |

|       | NOP      | 1      |                                   |

|       |          |        |                                   |

The assembler will detect sequences that could potentially trigger this bug, and issue a remark. For example,

"neg\_test.asm", REMARK at line 21 [R5001] SDSCM00012367 potentially triggered by this execute packet sequence. SLOOP must be at least 2 EPs away from previous SPKERNEL for safe interrupt behavior.

**Note:** The assembler tool, asm6x.exe, can be used to determine if a previous version of the compiler generated code that could potentially be affected by this silicon issue. The assembler can also be used on assembly source code to see if the source could be affected by this issue. Replace the old version of asm6x.exe with the 6.0.6 asm6x.exe in your current build setup and recompile or reassemble.

Internal Tracking Number: 4

| Advisory 2.3.29       | DSP Subsystem: C64x+ Incorrectly Generates False Exceptions for Multiple Write                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Details:              | The C64x+ CPU may generate an incorrect resource conflict exception when taking an interrupt. This only affects applications that run with exceptions enabled. Applications enable exceptions by writing 1 to the GEE bit in the Task State Register (TSR). Applications that do not enable exceptions are not affected by this errata.                                                                       |  |  |  |  |  |  |  |

|                       | The CPU generates this incorrect exception in the following scenario:                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|                       | <ol> <li>The CPU begins draining the pipeline as part of an interrupt context switch. During<br/>this time, the CPU annuls instructions in the pipeline that have not yet reached the<br/>E1 pipeline phase while it drains the pipeline.</li> </ol>                                                                                                                                                          |  |  |  |  |  |  |  |

|                       | <ol> <li>The first annulled execute packet (resident in the DC pipeline stage at the time<br/>draining begins) writes to one or more predicate registers. Because it is annulled, the<br/>writes do not occur.</li> </ol>                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                       | 3. The second annulled execute packet (resident in the DP pipeline stage at the time draining begins) has a predicated single cycle instruction that uses a predicate written by the execute packet described in item 2. Because it is annulled, the write does not occur.                                                                                                                                    |  |  |  |  |  |  |  |

|                       | <ol> <li>The value held in the predicate register would cause the instruction in the second<br/>annulled execute packet to write to some register in the same cycle as another<br/>instruction if it were not annulled. The conflicting writes would not happen if the first<br/>execute packet had not been annulled.</li> </ol>                                                                             |  |  |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                       | <ul><li>The exception is not a valid exception. If the CPU executed instructions described in items 2 and 3 above, rather than annulling them while draining the pipeline for an interrupt, the execute packet in item 2 would set the predicate(s) such that the writes in the subsequent execute packet do not conflict.</li><li>Examples of sequences that generate the incorrect exception are:</li></ul> |  |  |  |  |  |  |  |

|                       | <ul> <li>items 2 and 3 above, rather than annulling them while draining the pipeline for an interrupt, the execute packet in item 2 would set the predicate(s) such that the writes in the subsequent execute packet do not conflict.</li> <li>Examples of sequences that generate the incorrect exception are:</li> </ul>                                                                                    |  |  |  |  |  |  |  |

|                       | <ul><li>items 2 and 3 above, rather than annulling them while draining the pipeline for an interrupt, the execute packet in item 2 would set the predicate(s) such that the writes in the subsequent execute packet do not conflict.</li><li>Examples of sequences that generate the incorrect exception are:</li></ul>                                                                                       |  |  |  |  |  |  |  |

|                       | <pre>items 2 and 3 above, rather than annulling them while draining the pipeline for an<br/>interrupt, the execute packet in item 2 would set the predicate(s) such that the writes in<br/>the subsequent execute packet do not conflict.<br/>Examples of sequences that generate the incorrect exception are:<br/>ZERO A0<br/>ZERO B0<br/></pre>                                                             |  |  |  |  |  |  |  |

|                       | <pre>items 2 and 3 above, rather than annulling them while draining the pipeline for an<br/>interrupt, the execute packet in item 2 would set the predicate(s) such that the writes in<br/>the subsequent execute packet do not conflict.<br/>Examples of sequences that generate the incorrect exception are:</pre>                                                                                          |  |  |  |  |  |  |  |

|                       | <pre>items 2 and 3 above, rather than annulling them while draining the pipeline for an interrupt, the execute packet in item 2 would set the predicate(s) such that the writes in the subsequent execute packet do not conflict. Examples of sequences that generate the incorrect exception are:</pre>                                                                                                      |  |  |  |  |  |  |  |

Silicon Revision 2.3 Usage Notes and Known Design Exceptions to Functional Specifications

www.ti.com

Workaround(s): The CPU only recognizes the incorrect exception while it drains the pipeline for an interrupt. As a result, the CPU begins exception processing upon reaching the interrupt handler. The NRP (NMI Return Pointer Register) and NTSR (NMI Task State Register) will reflect the state of the machine upon arriving at the interrupt handler.

Therefore, to identify the incorrect resource conflict exception in software, verify the following conditions at the beginning of the exception handler prior to normal exception processing:

- 1. Exception occurred during an interrupt context switch.

- (a) In NTSR, verify that INT=1, SPLX=0, IB=0, CXM=00.

- (b) Verify that NRP points to an interrupt service fetch packet. That is, (NRP & 0xFFFF FE1F) == (ISTP & 0xFFFF FE1F).

- The exception is a resource conflict exception. In IERR, verify that RCX == 1 and all other IERR bits == 0.

- 3. The exception is an internal exception. In EFR, verify that IXF == 1 and all other EFR bits == 0.

Upon matching the above conditions, suppress the exception as follows:

- 1. Clear EFR.IXF by writing 2 to ECR.

- 2. Resume the interrupt handler by branching to NRP.

The above workaround identifies and suppresses all cases of the incorrect resource conflict exception. It resumes normal program execution when the incorrect exception occurs, and has minimal impact on the execution time of program code. The interrupted code sequence runs as expected when the interrupt handler returns.

The workaround also suppresses a particular valid exception case that is indistinguishable from the incorrect case. Specifically, the code will suppress the exception generated by two instructions with different delay slots (e.g., LDW and DOTP2) writing to the same register in the same cycle, where the conflicting writes occur during the interrupt context switch.

An example of a sequence with incorrectly suppressed exception is:

|           | *A0, A1 |       |      |     |       |       |    |    |      |       |

|-----------|---------|-------|------|-----|-------|-------|----|----|------|-------|

| DOTP2 A3, | A2, A1  |       |      |     |       |       |    |    |      |       |

| NOP       |         |       |      |     |       |       |    |    |      |       |

|           | > inte  | rrupt | occu | rs  |       |       |    |    |      |       |

| NOP       |         |       |      |     |       |       |    |    |      |       |

| NOP       | ;       | Both  | LDW  | and | DOTP2 | write | to | A1 | this | cycle |

The workaround will not suppress these valid resource conflict exceptions if the multiple writes occur outside an interrupt context switch. That is, the workaround will not suppress the exception generated by the code above when it executes without an interfering interrupt.

For more details, see the following sections in the *TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide* (literature number <u>SPRU732</u>).

- Interrupt Service Table Pointer Register (ISTP) describes the ISTP control register.

- Nonmaskable Interrupt (NMI) Return Pointer Register (NRP) describes the NRP control register.

- *TMS320C64x*+ *DSP Control Register File Extensions* describes the ECR, EFR, IERR, TSR and NTSR control registers.

- *Pipeline* describes the overall operation of the C64x+ pipeline, including the behavior of the E1, DC and DP pipeline phases.

- Actions Taken During Nonreset Interrupt Processing describes the operation of the C64x+ pipeline during interrupt processing, including how it annuls instructions.

- C64x+ CPU Exceptions describes exception processing.

Internal Tracking Number: 5

| www.ti.com            | Silicon Revision 2.3 Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advisory 2.3.30       | SPI: SPIINTVECT and SPIFLG Registers are Cleared When Read in Debug Mode                                                                                                                                                                                                                 |

| Revision(s) Affected: | 2.3 and earlier                                                                                                                                                                                                                                                                          |

| Details:              | Both the INTVECT and SPIFLG registers are cleared when refreshing the memory window in debug mode with CCS. These registers should be cleared only by regular CPU reads, not during debug/suspend mode.                                                                                  |

| Workaround(s):        | None                                                                                                                                                                                                                                                                                     |

| Advisory 2.3.31       | SPI: SPI Master Receives Extra Bit When SPICLK Polarity Changes                                                                                                                                                                                                                          |