# Anaren 0404 (BD2425N50200A00) balun optimized for Texas Instruments CC2420 Transceiver

Nithya R Subramanian – RF Development Engineer

Niels Kirkeby– R&D Manager

August 31st, 2007

### Introduction

Over the last few years, the drive for miniaturization and integration has intensified the challenges concerning the trade off between repeatability, cost and time to market. The design must be robust enough to get good yields, but also have the lowest possible bill of material cost. The total cost not only depends on the number and the types of parts and their associated cost, but also on the size of the PCB and enclosure.

At Anaren the focus is on developing product that addresses this trade off. Integrating 100% RF tested components increase yield and decreases size and time to market. The following application note demonstrates these objectives clearly as we present a small and simple balun solution optimized for use with the CC2420 from Texas Instruments. The CC2420 is a true single-chip 2.4 GHz ISM and IEEE 802.15.4 (ZigBee) compliant RF transceiver, designed for low-power wireless applications. The reference design presented in this application note uses only three components for the impedance matching: a 1mm square Anaren multilayer balun, a DC blocking capacitor and an inductor for final impedance matching. This results in, a design which takes up very little space and performs according to the numbers stated in the data sheet

The CC2420 is a low-cost, highly integrated solution for robust wireless communication in the 2.4 GHz unlicensed ISM band. CC2420 is designed to be compliant with SRD regulations covered by ETSI EN 300 328 and EN 300 440 class 2 (Europe), FCC CFR47 Part 15 (US) and ARIB STD-T66 (Japan). The CC2420 provides extensive hardware support for packet handling, data buffering, burst transmissions, data encryption, data authentication, clear channel assessment, link quality indication and packet timing information.

For more information about this or any other products currently available in the Anaren product portfolio, please visit our website at www.anaren.com for datasheets, S parameters and general corporate information.

Sales Desk USA: Voice: (800) 544-2414 Fax: (315) 432-9121

For more information on Low Power Wireless products from Texas Instruments please visit www.ti.com\lpw for product information. Project collateral discussed in this application note can be downloaded from the following URL: <a href="http://www.ti.com/lit/zip/SWRA155">http://www.ti.com/lit/zip/SWRA155</a>.

# **Comparisons of Different Balun Solutions**

The RF front end for the CC2420 is architecturally simple in that both receiver LNA and transmitter PA are attached to the same set of balanced pins. The transmitter is linear enough to not require any significant filtering. Hence an impedance matched, balanced to single ended transformation is all that is needed. The only complication being that the PA bias power, pin 7 on the CC2420, needs to be supplied into the balanced pin set.

A multitude of possible balun implementations exist and Texas Instruments provides two other reference designs. One uses a 180° transmission line and 4 discrete components. The other solution is a discrete lattice balun implementation that uses 7 components. The solution from Anaren, described in this document, uses a discrete balun, one capacitor and one inductor.

Below we will step through each implementation to detail the differences and benefits that each offer.

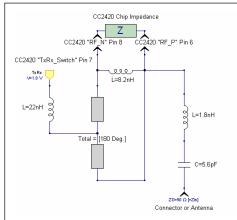

Figure 1 Schematic of transmission line implementation

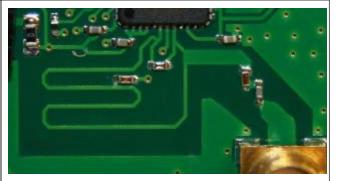

Figure 2 Layout of transmission line implementation

The transmission line implementation shown in Figure 1 and Figure 2 is straight forward and employs only four discrete components. However the PCB real estate taken up is significant and the performance is sensitive to changes of line width of the 180° transmission line, PCB thickness and variation in the PCB material.

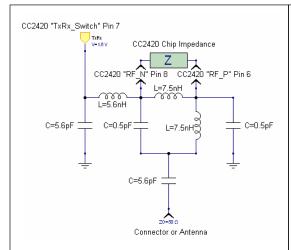

Figure 3 Schematic of the lumped element implementation

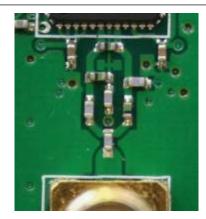

Figure 4 Layout of the lumped element implementation

The lumped element implementation shown in Figure 3 and Figure 4 is smaller in size than the transmission line version, but uses a total of 7 discrete components. This implementation is less susceptible to line width and PCB variations, but it is sensitive to discrete component tolerances.

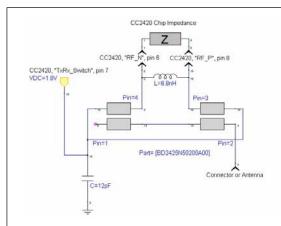

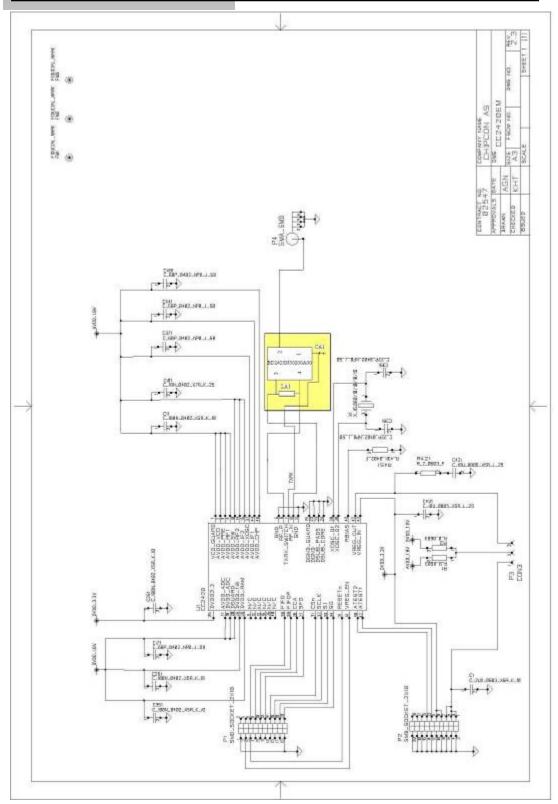

Figure 5 Schematic of the Anaren balun implementation

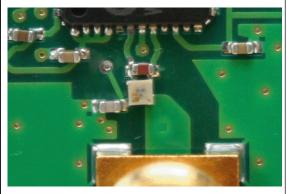

Figure 6 Layout of the Anaren balun implementation

The Anaren balun implementation shown in Figure 5 and Figure 6 has fewer components and uses less real estate than any of the other solutions

The Anaren balun implementation shown in Figure 5 and Figure 6 takes up even less PCB area and has reduced sensitivity to discrete component tolerance/variation. The recommended components are a parallel inductor of 6.8nH (Johanson L-07C6N8J) and a 12pF DC-blocking capacitor (Johanson 250R07C120JV4). Care should be taken using alternate vendors especially on the inductor as they do not have the same performance. Each vendor of inductors and capacitors has their own way of realizing the inductor/capacitor with associated differences in parasitic values, even within a single vendor, different component series are made differently with significantly different parasitic's. Even from one value to the next in the same series there can be parasitic differences, if for instance a spiral inductor requires another turn to fit in the same footprint from one value to the next then either the trace width drops, another trace layer is used or maybe a different material set – these, from a

Sales Desk USA: Voice: (800) 544-2414 Fax: (315) 432-9121

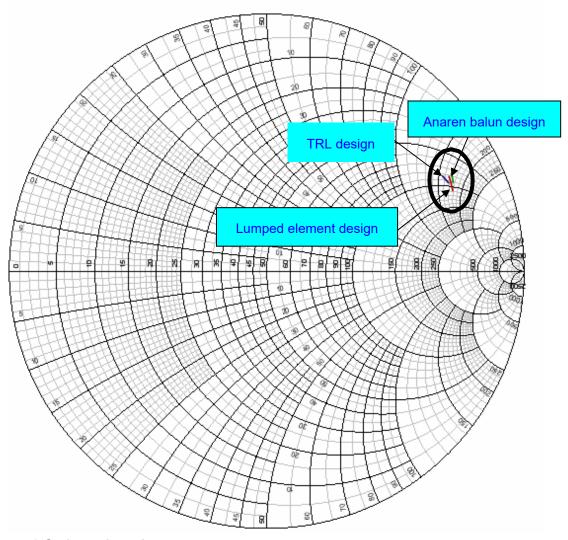

value point of view, subtle changes causes significant parasitic change. If the change in impedance cause by parasitic changes fall within the circle outlined in Figure 9 the performance will be acceptable. One way to evaluate alternate vendors is to compare sparameters of the components – however the s-parameters must be measured the same way from both vendors to be able to compare and this information is not often available. Another way is to use vendor or third party models but it is still important to know what each model represents; does it include the PCB pads, is the model valid for the PCB used etc.

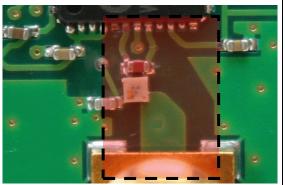

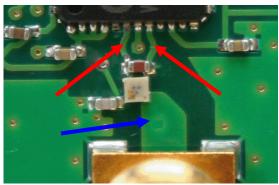

The Anaren recommended layout (can be supplied as Gerber files) is fabricated on a 39mil thick FR4 board. If a multilayer board is used it is recommended that internal power/GND planes be opened such that the effective height to GND is roughly 40mil, as illustrated in Figure 7 below,. If it is not possible in the application to open up internal GND planes then follow Table 1 for changes to the differential connecting lines, identified in Figure 8, with red arrows and the single ended connection identified in Figure 8, with a blue arrow.

Figure 7 Opening in power/GND planes below RF circuitry

Figure 8 Differential (red) connecting lines and single ended (blue) connecting line

| Distance to ground & material [mil] | Differential line width Width/Length [mil/mil] | Single ended line width Width/Length [mil/mil] |  |  |

|-------------------------------------|------------------------------------------------|------------------------------------------------|--|--|

| 5, PI                               | 8/60                                           | 8/221                                          |  |  |

| 8, Ro4350                           | 8/60                                           | 10/221                                         |  |  |

| 10, FR4                             | 10/60                                          | 15/221                                         |  |  |

| 20, FR4                             | 10/60                                          | 30/221                                         |  |  |

| 30, FR4                             | 10/60                                          | 50/221                                         |  |  |

| 39, FR4                             | 10/60                                          | 80/221                                         |  |  |

| 60, FR4                             | 10/75                                          | 80/221                                         |  |  |

Table 1 : Differential line and single ended line width/length for various substrate heights

If a SMA connector is used and GND plane spacing other than 39 mils is used then the launch area must be opened or otherwise compensated to provide proper match.

If the location of the components is changed (not recommended) then it is very important to keep the DC blocking capacitor very close to the balun (pin 1). Also the trace lines between

Sales Desk USA: Voice: (800) 544-2414 Fax: (315) 432-9121

the CC2420 chip, the parallel inductor and balun are an integral part of the matching and should not be changed in length.

Table 2 demonstrates the significant reduction in size; component count and board layout achieved with the Anaren 0404 balun solution.

| Solution                                           | Transmission line design        | Lumped element<br>design               | Anaren/TI<br>0404 internal<br>bias solution |

|----------------------------------------------------|---------------------------------|----------------------------------------|---------------------------------------------|

| Component Count and type                           | 4 Total 1 Capacitor 3 Inductors | 7 Total<br>4 Capacitors<br>3 Inductors | 3 Total 1 Balun 1 Inductor 1 Capacitor      |

| PCB Area                                           | 0.1448 sq. inch                 | 0.0423 sq. inch                        | 0.0174 sq inch                              |

| Space savings<br>based on lumped<br>element design | -242%                           | 0%                                     | 59%                                         |

### Table 2 Comparison of the three different balun implementations

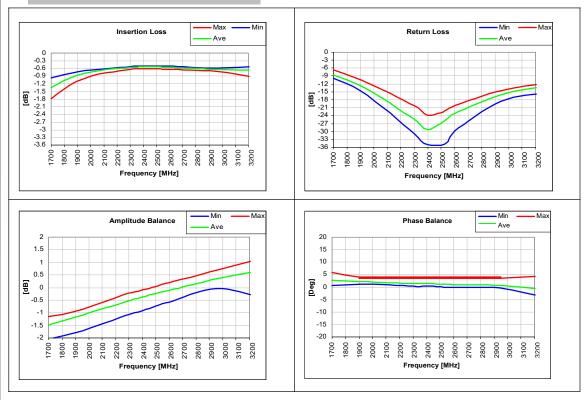

The Anaren balun performance is consistent and tolerant to PCB manufacturing tolerances. Production average and worst case RF performance data for the BD2425N50200A00 is illustrated in Table 3.

**Table 3 Balun Performance**

Figure 8 Implementation of CC2420 using Anaren balun.

Anaren

SWRA155 What'll we think of next?"

# **Application Verification**

Measurements verify that the reference designs presented in this application note has the same performance as given in the data sheet. These measurements include;

- Transmit Power

- Receive Sensitivity

- Current consumption

These measurements were performed independently by both Anaren and TI. In addition TI also performed an Error Vector Magnitude measurement. Through further testing at Anaren the optimum impedance for the CC2420 Chip is found to be inside the range (ellipse) shown in Smith chart below.

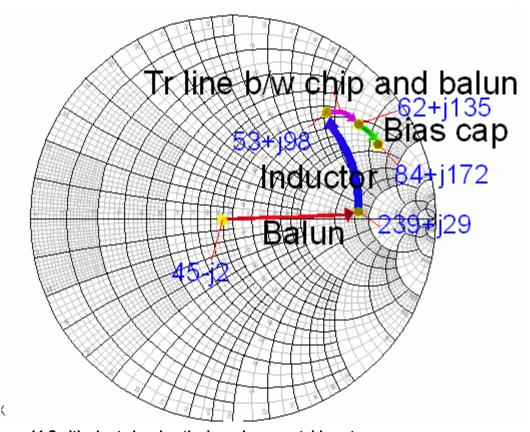

# Impedance between chip and balun

**Figure 9 Optimum Impedance**

# The Impedance Matching

The following describes the matching steps.

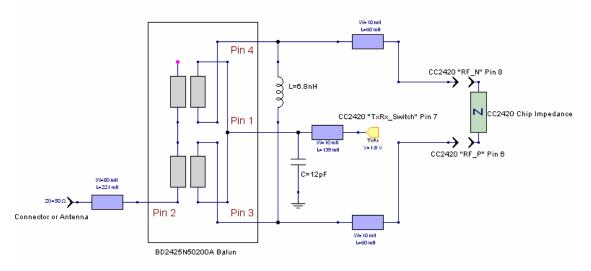

Optimum differential impedance as seen from the RF ports towards antenna is stated as 95+j187  $\Omega$  in the data sheet for the CC2420. The BD2425N50200A00 balun has 50  $\Omega$  single ended port impedance and 200  $\Omega$  balanced port impedance. A 6.8nH inductor is connected across the balanced ports for matching purposes and a 12pF capacitor is used at pin 1 as a DC block (RF GND) to allow biasing through this pin to the differential ports, pin 3 and pin 4 of the balun. This is illustrated in Figure 10.

### Figure 10 Anaren balun schematic

The impedance matching steps, with a SMA connector, illustrated in the Smith chart, Figure 11 performs the match as follows.

- The connector and the connecting line at the input transform 50  $\Omega$  to 45-j2  $\Omega$  (Note 1).

- The balun transforms 45-j2 Ω into 239+j29 Ω

- The inductor at the differential arm of the balun brings the impedance to 53+j98  $\Omega$

- The transmission line to interface the chip to the balun brings the impedance to  $62+j135~\Omega$ .

- The DC-blocking capacitor and transmission line from the Tx/Rx switch to the bias point of the balun (pin 1) transforms the impedance to  $84+j172 \Omega$

Figure 11 Smith chart showing the impedance matching steps

The value of the inductor and the capacitor also depends on the length of the transmission line used between the CC2420 chip and the balun. If the length of the transmission line between chip and the balun is increased then the inductor and the capacitor values should be decreased. If the length of the line is decreased then the inductor and capacitor should be increased.

It is strongly recommended to use the same line length, width, inductor and capacitor values as shown in the 0404 internal bias design schematic. Any change in inductor value, DC-blocking capacitor value or layout will give only similar but not exactly the same performance.

Note 1: If a SMA connector is not used then a 50  $\Omega$  transmission line should be used to connect to the balun, this change will cause a negligible shift in performance.

# References

- 1. http://focus.ti.com/docs/prod/folders/print/cc2420.html CC2420EM Reference Design

- 2. http://focus.ti.com/docs/prod/folders/print/cc2420.html CC2420 Development kit user manual

# Ultra Low Profile 0404 Balun $50\Omega$ to $200\Omega$ Balanced

### Description

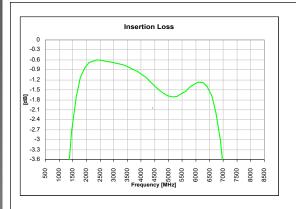

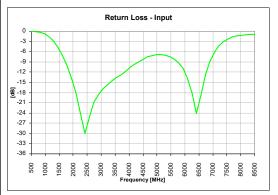

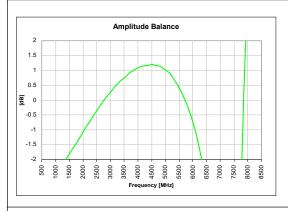

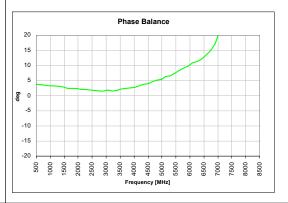

The BD2425N50200A00 is a low cost, low profile sub-miniature unbalanced to balanced transformer designed for differential inputs and output locations on modern chipsets in an easy to use surface mount package. The BD2425N50200A00 is ideal for high volume manufacturing and delivers higher performance than traditional ceramic baluns. The BD2425N50200A00 has an unbalanced port impedance of  $50\Omega$  and a  $200\Omega$  balanced port impedance. This transformation enables single ended signals to be applied to differential ports on modern integrated chipsets. The output ports have equal amplitude (-3dB) with 180 degree phase differential. The BD2425N50200A00 is available on tape and reel for pick and place high volume manufacturing.

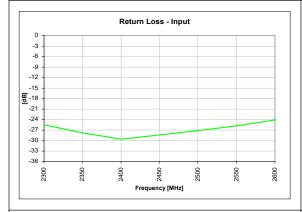

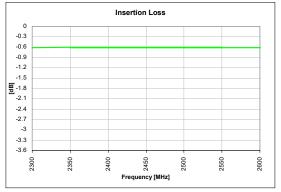

Detailed Electrical Specifications: Specifications subject to change without notice.

| Features:                                                             | Specifications subject    | ROOM (25°C) |      |      |             |

|-----------------------------------------------------------------------|---------------------------|-------------|------|------|-------------|

| • 2400 – 2500 MHz                                                     | Parameter                 | Min.        | Тур. | Max  | Unit        |

| <ul><li>0.65mm Height Profile</li><li>50 Ohm to 2 x 100 Ohm</li></ul> | Frequency                 | 2400        |      | 2500 | MHz         |

| <ul><li>Low Insertion Loss</li><li>802.11 b+g</li></ul>               | Unbalanced Port Impedance |             | 50   |      | Ω           |

| <ul><li>MIMO b+g</li><li>Bluetooth</li></ul>                          | Balanced Port Impedance   |             | 200  |      | Ω           |

| <ul><li>Zigbee</li><li>Surface Mountable</li></ul>                    | Return Loss               | 21          | 27   |      | dB          |

| Tape & Reel     Non-conductive                                        | Insertion Loss*           |             | 0.6  | 0.7  | dB          |

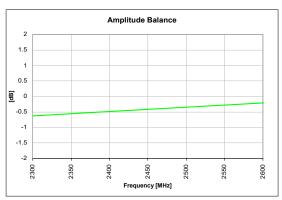

| RoHS Compliant                                                        | Amplitude Balance         |             | 0.5  | 1.0  | dB          |

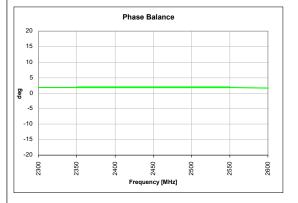

|                                                                       | Phase Balance             |             | 2    | 6    | Degree<br>s |

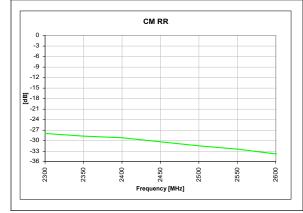

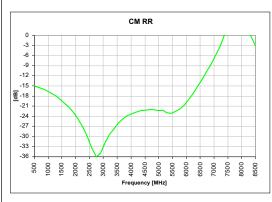

|                                                                       | CMRR                      |             | 29   |      | dB          |

|                                                                       | Power Handling            |             |      | 1    | Watts       |

|                                                                       | Operating Temperature     | -55         |      | +85  | °C          |

<sup>\*</sup> Insertion Loss stated at room temperature (Insertion Loss is approximately 0.1 dB higher at +85 °C)

Sales Desk USA: Voice: (800) 544-2414 Fax: (315) 432-9121

Sales Desk Europe: Voice: (+44) 2392 232392 Fax: (+44) 2392 251369

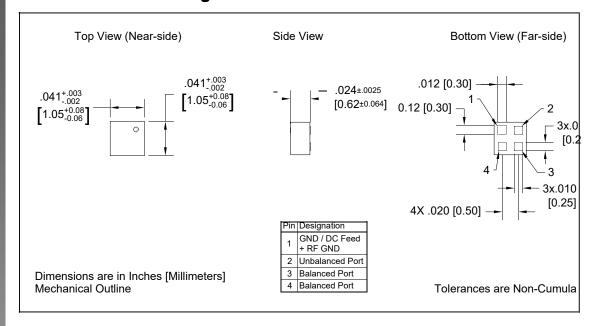

# **Outline Drawing**

### Typical Performance:2400 MHz. to 2500 MHz.

### Wide Band Performance: 500 MHz. to 8500 MHz.

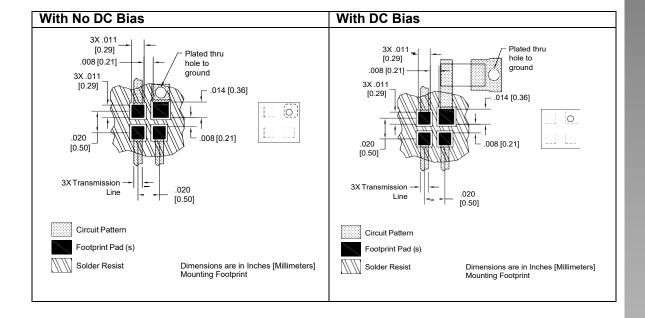

### **Mounting Configuration:**

In order for Xinger surface mount components to work optimally, the proper impedance transmission lines must be used to connect to the RF ports. If this condition is not satisfied, insertion loss, Isolation and VSWR may not meet published specifications.

All of the Xinger components are constructed from ceramic filled PTFE composites which possess excellent electrical and mechanical stability having X and Y thermal coefficient of expansion (CTE) of 17 ppm/°C.

An example of the PCB footprint used in the testing of these parts is shown below. An example of a DC-biased footprint is also shown below. In specific designs, the transmission line widths need to be adjusted to the unique dielectric coefficients and thicknesses as well as varying pick and place equipment tolerances

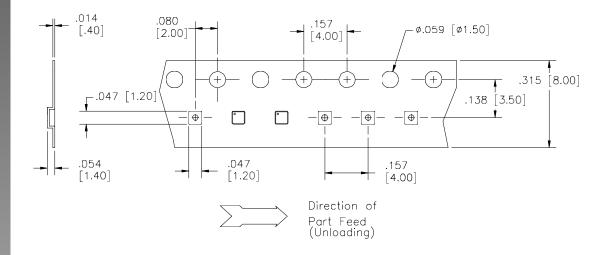

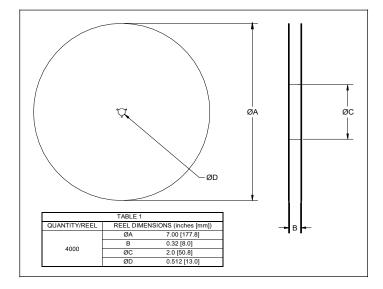

### **Packaging and Ordering Information**

Parts are available in reel and are packaged per EIA 481-2. Parts are oriented in tape and reel as shown below. Minimum order quantities are 4000 per reel. See Model Numbers below for further ordering information.

# BD 2425 J 50 100 A 00

| Function                                                                                                       | Frequency                                                                                                                                                                                                                                                                                                                                                            | Package<br>Dimensions                                                                                                                                                                     | Unbalance<br>Impedance     |                                                                                                                                                                                                                                                                 |                                                    | Codes |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------|

| B = Balun + DC F = Filter FB = Filter / Balun C = 3dB Coupler DC = Directional J = RF Jumper X = RF cross over | 0110 = 100 - 1000 MHz<br>0810 = 800 - 1000 MHz<br>0922 = 950 - 2150 MHz<br>0826 = 800 - 6200 MHz<br>1222 = 1200 - 2200 MHz<br>1416 = 1400 - 1600 MHz<br>1722 = 1700 - 2200 MHz<br>2326 = 2300 - 2600 MHz<br>2425 = 2400 - 2500 MHz<br>3150 = 3100 - 5000 MHz<br>4859 = 4800 - 3600 MHz<br>5153 = 5100 - 5900 MHz<br>5159 = 5100 - 5900 MHz<br>5759 = 5700 - 5900 MHz | A = 150 x 150 mils (4mm x 4mm) C = 120 x 120 mils (3mm x 3mm) E = 100 x 80 mils (25mm x 2mm) J = 80 x 50 mils (2mm x 125mm) L = 60 x 30 mils (15mm x 0.75mm) N = 40 x 40 mils (1mm x 1mm) | 50 = 50 Ohm<br>75 = 75 Ohm | 25 = 25 Ω Balance<br>30 = 30 Ω Balance<br>50 = 50 Ω Balance<br>75 = 75 Ω Balance<br>100 = 100 Ω Balanc<br>150 = 150 Ω Balanc<br>200 = 200 Ω Balanc<br>300 = 300 Ω Balanc<br>400 = 400 Ω Balanc<br>03 = 3dB Hybrid<br>10 = 10dB Direction<br>20 = 20dB Direction | P = Tin-Lead I I I I I I I I I I I I I I I I I I I |       |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated