## TIDA-00621 Test Report **Powering the i.MX6 Dual/Quad with TPS65911 Power Management IC**

# 🕂 Texas Instruments

#### **TI Designs**

TI Designs provide the foundation that you need including methodology, testing and design files to quickly evaluate and customize the system. TI Designs help **you** accelerate your time to market.

#### **Design Resources**

<u>TIDA-00621</u> <u>TPS65911</u> TPS65911 Designs Design Folder Product Folder Tools Folder

Ask The Analog Experts WEBENCH<sup>®</sup> Design Center

### **Report Contents**

- Block Diagram: TPS65911 / i.MX6

- Efficiency Curves

- Load Regulation Curves

- Output Ripple Voltage

- Load Transients

- <u>Start-Up Sequence</u>

- Design Considerations

### **Feature Applications**

- Factory Automation

- Motor Control

- Smart Grid

- Solar Inverters

### Description

Figure 1 - Top Side

#### Figure 2 - Bottom Side

TIDA-00621 utilizes a power management integrated circuit (PMIC) for supplying a Freescale® i.MX6 SoC in a DDR3 application. This design showcases the TPS65911 as an all-in-one IC used to supply the rails needed for powering the i.MX6 SoC, with available regulators for system peripherals. The TPS65911 offers simple, flexibile output voltages and sequencing. The voltages on the DC/DC converters can be adjusted over i2c once the device has entered the active state, allowing for individual regulator customization.

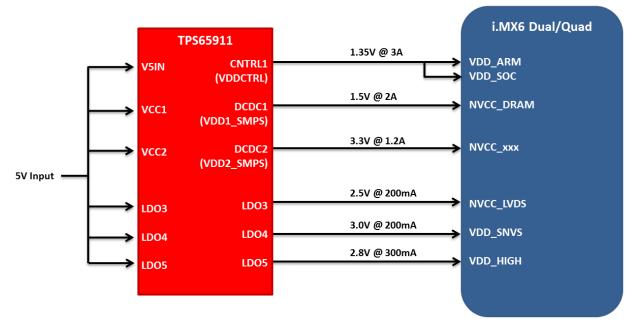

### TPS65911/i.MX6 Block Diagram (Return to Top)

### Power Supply Block Diagram

Figure 3 – IMX6 Block Diagram

#### **Typical Voltage and Current Requirements in End Applications**

Depending on the application, current consumption of the i.MX6 power rails can vary. The table below highlights the typical max currents each power output of the TPS65911 PMIC may supply to the IMX6 rails.

| IMX6 Supply Rails   | Voltage | Current Consumption<br>(mA) |

|---------------------|---------|-----------------------------|

| VDD_SNVS            | 3.0V    | 200                         |

| VDD_ARM             | 1.35V   | Component Specifie          |

| VDD_SOC             | 1.557   | Component Specific          |

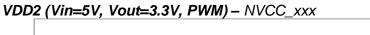

| NVCC_xxx            | 3.3V    | 1200                        |

| NVCC_LVDS           | 2.5V    | 200                         |

| VDD_HIGH            | 2.8V    | 300                         |

| NVCC_DRAM<br>(DDR3) | 1.5V    | 2000                        |

TEXAS INSTRUMENTS www.ti.com

**Note:** NVCC\_LVDS powers the pre-drivers for the DDR I/O pins, and must be powered even when LVDS is not used. The maximum current consumption of a design will vary depending on the specific application.

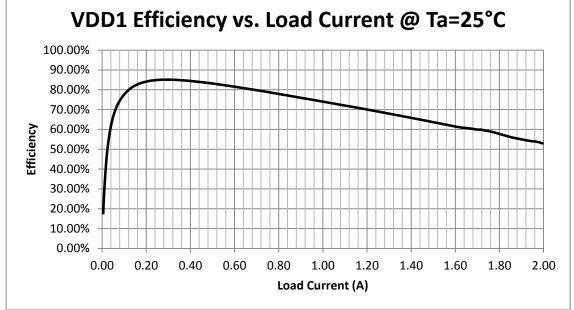

## Efficiency Curves (Return to Top)

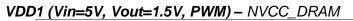

Figure 4 - DCDC1 Efficiency @ 25C

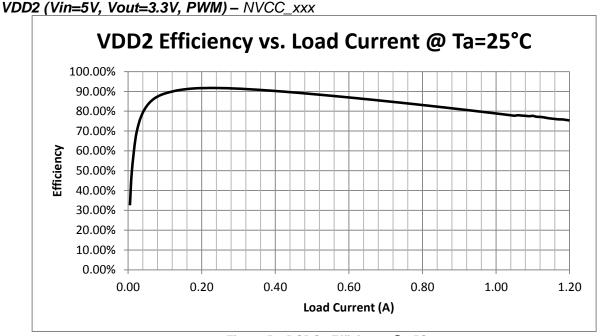

Figure 5 – DCDC2 Efficiency @ 25C

#### TIDA-00621 – Test Report Powering the i.MX6 Dual/Quad with TPS65911 Power Management IC

#### TEXAS INSTRUMENTS www.ti.com

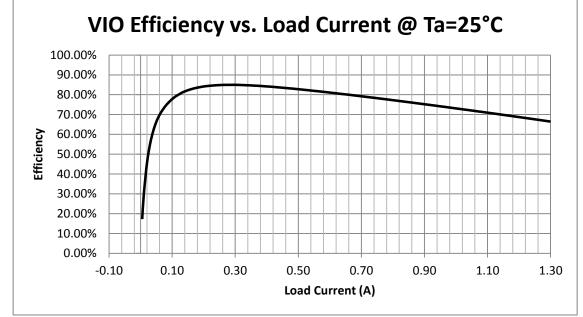

VIO (Vin=5V, Vout=1.5V, PWM) - Peripherals

Figure 6 – VIO Efficiency @ 25C

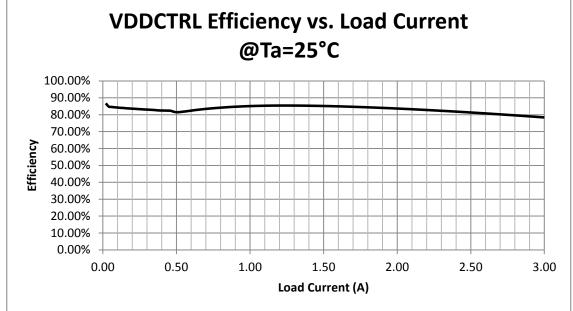

Figure 7 – CTRL1 Efficiency @ 25C

### Load Regulation (Return to Top)

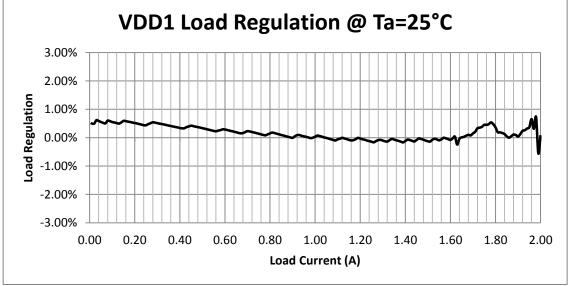

Figure 8 – DCDC1 Load Regulation @ 25C

Figure 9 – DCDC2 Load Regulation @ 25C

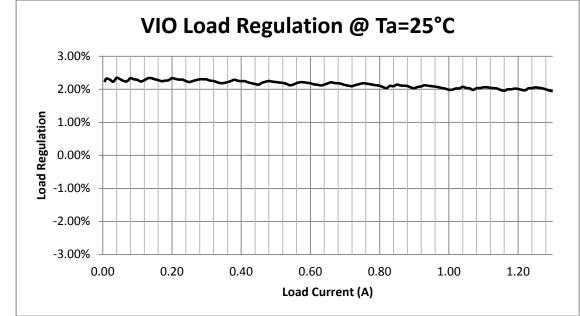

Figure 10 – VIO Load Regulation @ 25C

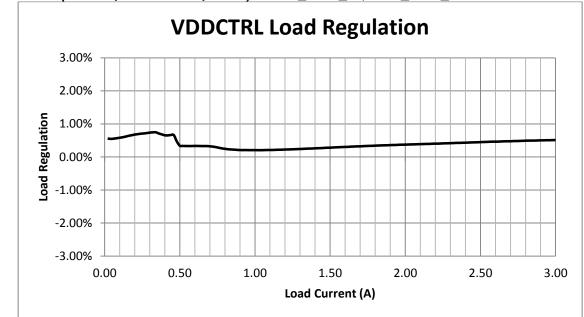

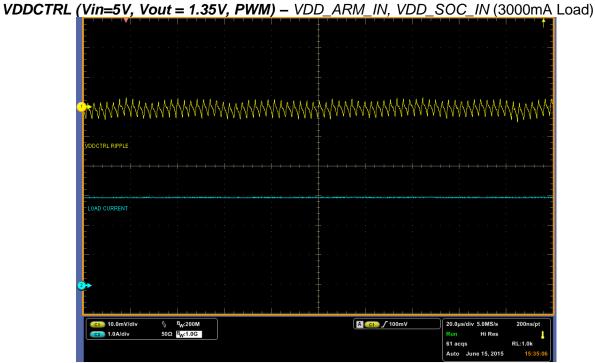

VDDCTRL (Vin=5V, Vout=1.35V, PWM) - VDD\_ARM\_IN, VDD\_SOC\_IN

Figure 11 – CTRL1 Load Regulation @ 25C

### Output Ripple Voltage (Return to Top)

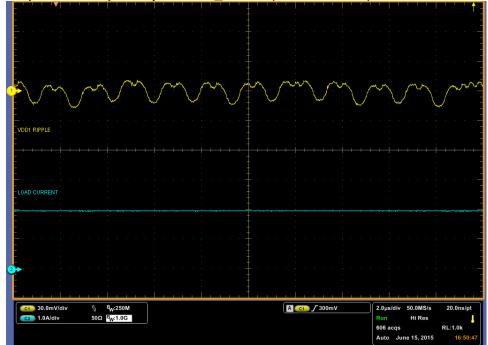

VDD1 (Vin=5V, Vout=1.5V, PWM) - NVCC\_DRAM (2000mA Load)

Figure 12 – DCDC1 Voltage Ripple @ 25C

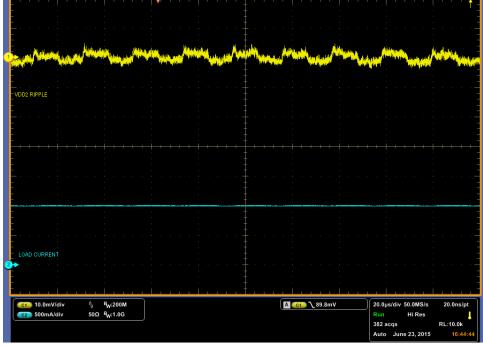

VDD2 (Vin=5V, Vout=3.3V, PWM) – NVCC\_xxx (1000mA Load)

Figure 13 – DCDC2 Voltage Ripple @ 25C

TIDA-00621 – Test Report Powering the i.MX6 Dual/Quad with TPS65911 Power Management IC

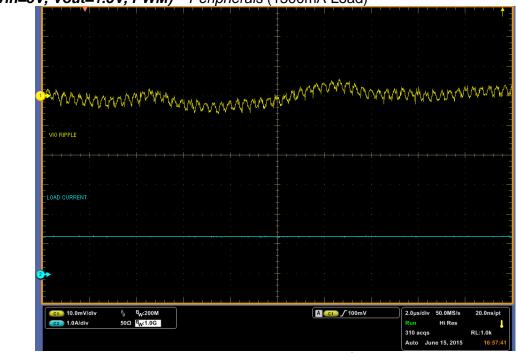

VIO (Vin=5V, Vout=1.5V, PWM) – Peripherals (1300mA Load)

Figure 14 – VIO Voltage Ripple @ 25C

Figure 15 – VDDCTRL Voltage Ripple @ 25C

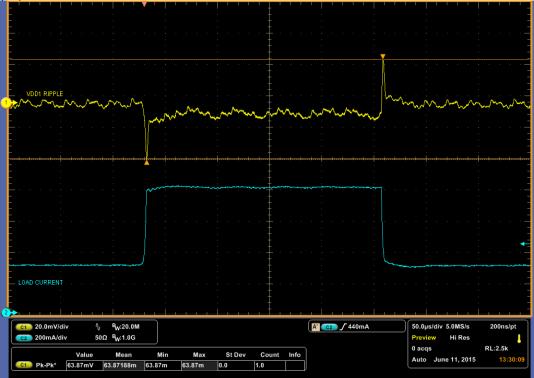

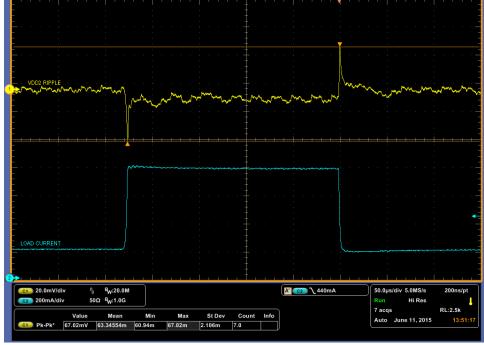

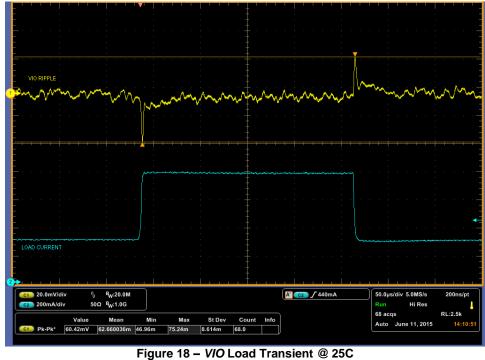

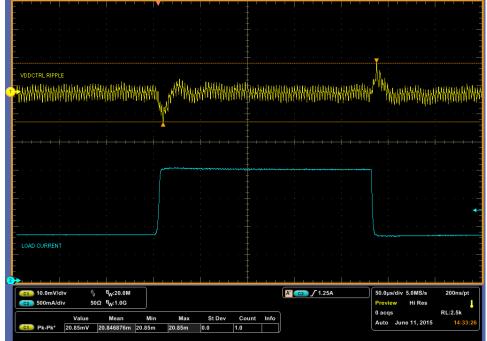

## Load Transients (Return to Top)

Load transients for each of the DC-DC converters were completed by applying a current load step of approximately 25% to 75% of the max load for the regulator under test. Rise time and fall time were both set at ~100mA/ $\mu$ S for the converters (VDD1, VDD2), and ~200mA/ $\mu$ S for the controller (VDDCTRL).

**VDD1 (Vin=5V, Vout = 1.5V, PWM)** – NVCC\_DRAM (300mA to 800mA, Rise Time: 5μS; Fall Time: 5μS)

Figure 16 – DCDC1 Load Transient @ 25C

**VDD2 (Vin=5V, Vout = 3.3V, PWM)** – NVCC\_xxx (300mA to 800mA, Rise Time: 5μS; Fall Time: 5μS)

Figure 17 – DCDC2 Load Transient @ 25C

**VIO (Vin=5V, Vout = 1.5V, PWM)** – Peripherals (300mA to 800mA, Rise Time:  $5\mu$ S; Fall Time:  $5\mu$ S)

TIDA-00621 – Test Report Powering the i.MX6 Dual/Quad with TPS65911 Power Management IC

**VDDCTRL (Vin=5V, Vout = 1.35V, PWM)** – VDD\_ARM\_IN, VDD\_SOC\_IN (800mA to 2000mA, Rise Time: 5μS; Fall Time: 5μS)

Figure 19 – VDDCTRL Load Transient @ 25C

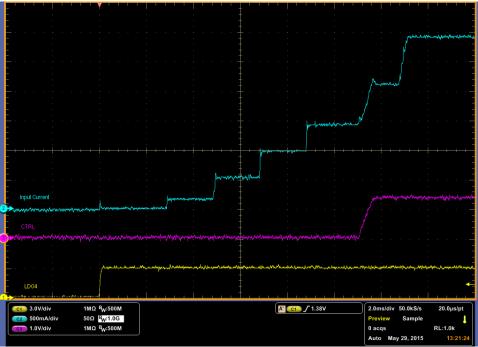

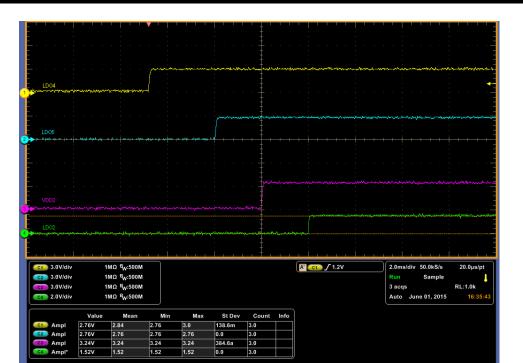

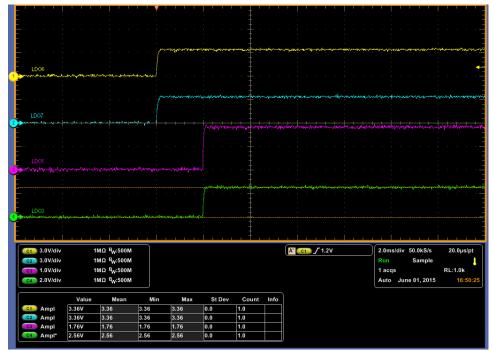

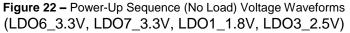

## Start-up Sequence (Return to Top)

Regulator sequencing requirements for the i.MX6 are fairly loose, therefore the primary advantage of bringing multiple supplies to their operating voltages at various times manifests in minimizing inrush currents on the input supply rail. By staggering the various voltage rails, lower capacity supplies can better maintain their output voltage during startup. Figure 20 details the complete start-up sequence of the TPS65911 PMIC configured for the IMX6, with load resistors on each rail drawing approximately half of the maximum regulator current.

Figure 20 - Power-Up Sequence (Half Max Load) Current Consumption

Figure 21 – Power-Up Sequence (No Load) Voltage Waveforms (LDO4\_3.0V, LDO5\_2.8V, VDD2\_3.3V, LDO2\_1.5V)

TEXAS

INSTRUMENTS www.ti.com

11

Figure 23 – Power-Up Sequence (No Load) Voltage Waveforms (LDO8\_3.3V, VDDCTRL\_1.35V, VDD1\_1.5V, VIO\_1.5V)

### Design Considerations (Return to Top)

Per requirements from Freescale, the supply for VDD\_SNVS\_IN must be turned on before any other supply. VDD\_SNVS\_IN can also be shorted to VDD\_HIGH\_IN, as long as the above requirement is met. There are no special restrictions for powering down the i.MX6 Dual or Quad SoCs.

VDD\_ARM\_IN and VDD\_SOC\_IN may be supplied from the same source. If VDD\_SOC\_IN and VDD\_ARM\_IN are powered by separate supplies, VDDSOC\_IN can be supplied before VDD\_ARM\_IN with a maximum delay of 1ms.

The TPS65911 can be utilized with a coin cell or LDO4 powering SNVS\_IN. The following powerup sequence demonstrates compliance of the TPS65911 PMIC with Freescale's recommendations. While the sequencing requirements for the i.MX6 SoC are lax, delaying activation time of each regulator beneficially reduces inrush currents in the overall design and mitigates demand on the system supply.

| VDD_RTC/VRTC                            |          |               |          |        |         |              |             |             |           |           |          |            |        |    |    |   |               |             |

|-----------------------------------------|----------|---------------|----------|--------|---------|--------------|-------------|-------------|-----------|-----------|----------|------------|--------|----|----|---|---------------|-------------|

| CLK32KOUT                               | TPS65911 | internal cloc | k        |        |         |              |             |             |           |           |          |            |        |    |    |   | OSCK32KOUT 32 | 2kHz Active |

| LDO4, 50mA limit                        |          |               |          |        | 3.0V (S | NVS_IN)      |             |             |           |           |          |            |        |    |    |   |               |             |

| LDO5, 300mA limit                       |          |               |          |        |         | 2.8V (VD     | DHIGH_IN    | )           |           |           |          |            |        |    |    |   |               |             |

| VDD2, 1.2A limit                        |          |               |          |        |         |              | 3.3 (NVC/   | C_xxx/GPIC  | ))        |           |          |            |        |    |    |   |               |             |

| LDO2, 320mA limit                       |          |               |          |        |         |              |             | 1.5V Per    | ipheral   |           |          |            |        |    |    |   |               |             |

| LDO6, 300mA limit                       |          |               |          |        |         |              |             | 3.3V Per    | ipheral   |           |          |            |        |    |    |   |               |             |

| LDO7, 300mA limit                       |          |               |          |        |         |              |             | 3.3V Per    | ipheral   |           |          |            |        |    |    |   |               |             |

| LDO1, 320mA limit                       |          |               |          |        |         |              |             |             | 1.8V Peri | pheral    |          |            |        |    |    |   |               |             |

| LDO3, 200mA limit                       |          |               |          |        |         |              |             |             | 2.5V (LVC | OS/etc.)  |          |            |        |    |    |   |               |             |

| LDO8, 300mA limit                       |          |               |          |        |         |              |             |             | 3.3V Peri | pheral    |          |            |        |    |    |   |               |             |

| VDDCTRL, 6A+ limit                      |          |               |          |        |         |              |             |             |           | 1.35V (AF | RM_IN, S | OC_IN)     |        |    |    |   |               |             |

| VDD1, 2A limit                          |          |               |          |        |         |              |             |             |           |           | 1.5 (NV  | CC_DRAM    | )      |    |    |   |               |             |

| VIO, 1.3A limit                         |          |               |          |        |         |              |             |             |           |           | 1.5V Pe  | ripheral c | or LDO |    |    |   |               |             |

| Event:<br>Time slot (2ms between slots) | 1        |               | 2        | 0      | 3<br>1  | 2            | 3           | 4           | 5         | 6         | 7        | 8          | 9      | 10 | 11 | : | 12            |             |

| Event Description                       | 2        | Valid press   | after de | bounce |         | ilable for D | )CDC, LDO a | activation. |           |           |          |            |        |    |    |   |               |             |

Additional regulators are intended to supply various peripherals in the full system and may be deactivated after the device has reached an active state. Excluding VRTC, each regulator is adjustable over i2c allowing for custom configurations.

For further design considerations specific to a particular application, please refer to the following Freescale documents: Dual Quad Technical Data (IMX6DQCPOPEC), Dual/Quad Hardware Design Application Note (AN4397), Dual/Quad Power Consumption Application Note (AN4509), TPS659110 Datasheet (SWCS049).

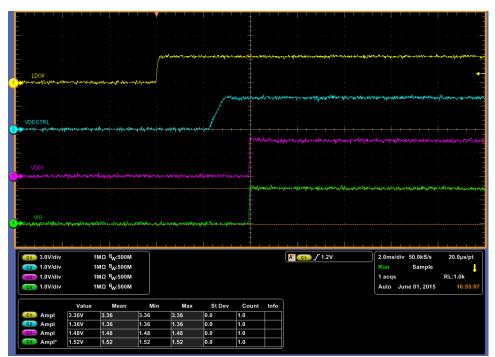

- MicroStar Junior™ BGA configuration C.

- Falls within JEDEC MO-225 D.

- E. This package is lead-free.

MicroStar Junior BGA is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated