## TI Designs Multi-Band RF Sampling Receiver Solution

# Texas Instruments

#### **TI Designs**

**Design Resources**

TI E2E

Community

TIDA-01163 ADC32RF80EVM

ADC32RF80

LMX2582

LMK04828

**A**

The RF sampling receiver captures signals directly in the radio frequency (RF) band. In a multi-band application, the desired signals do not have a very wide band, but they are spaced far apart within the spectrum. The ADC32RF80 is a dual-channel, 14-bit, 3-GSPS RF sampling telecom receiver. The 3-dB input bandwidth is 3 GHz, and it captures signals up to 4 GHz. The device includes two digital down converters (DDC) per channel. The DDC offers decimation values from 8 to 32 and includes a 16-bit numerically controlled oscillator to move the captured signal down to digital baseband. With the high sampling rate of the ADC32RF80, the device captures a large swatch of the RF spectrum, which contains signals in multiple bands and potentially undesired interferers. The DDC independently mixes the desired bands to digital baseband. Decimation reduces the output data rate to a lower level and provides digital filtering around the desired band to eliminate interference and to improve signal-to-noise ratio (SNR) performance. This feature is critical for high-end telecommunication receivers that require high dynamic range.

Design Folder

Product Folder

Product Folder

Product Folder

ASK Our E2E Experts

Tool Folder

### **Design Features**

- 3-GSPS RF Sampling Receiver Solution

- Low Noise, High Dynamic Range RF Sampling Receiver Solution

- Programmable Decimation from 8 to 32

- Dual Digital Down-Converter With Independent Numerically Controlled Oscillators

#### **Featured Applications**

- Wireless Base Station Multi-Band or Multi-Mode Receiver

- Multi-carrier GSM Receiver

- Digital Pre-Distortion Feedback Receiver •

- **Telecommunications Receiver**

- **Carrier Aggregation Receiver**

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

All trademarks are the property of their respective owners.

#### 1 System Description

This reference design implements an RF sampling receiver capable of capturing signals in multiple bands. In a wideband RF sampling implementation, the analog-to-digital converter (ADC) sampling rate dictates the maximum bandwidth captured. When dealing with multiple bands, the useful information is located within their respective bands. The spectrum outside of those bands does not contain useful information. In fact, it may contain unwanted interference that needs to be filtered out. This reference design showcases the ADC32RF80 telecom receiver, which includes two digital down converters (DDC) per channel. Each DDC includes decimation filters and a numerically controlled oscillator (NCO) to extract the useful signal in separate bands.

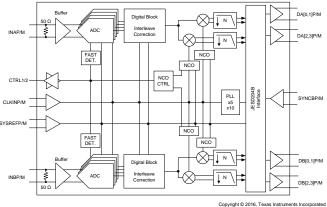

#### 1.1 ADC32RF80

The ADC32RF80 is a dual-channel telecom receiver. It includes a 14-bit, 3-GSPS ADC with built-in decimation. It has a 3-dB input bandwidth of 3 GHz and is usable up to 4 GHz. The ADC32RF80 employs two DDCs per channel. Each DDC incorporates decimation from 8 to 32 and an independent 16-bit NCO to support multi-band applications.

The ADC32RF80 supports the JESD204B serial interface with data rates up to 12.0 Gbps using up to four lanes per ADC. The device input is buffered with an on-chip 50- $\Omega$  differential termination.

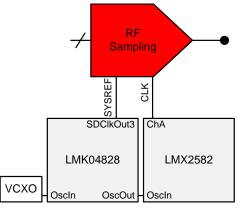

#### 1.2 LMK04828

The LMK04828 is a dual-PLL jitter cleaner and clock generator. An onboard 122.88-MHz VCXO provides the reference frequency. This can be locked to an external 10-MHz reference if desired. The LMK04828 supplies the JESD204B SYSREF clocks to the ADC and FPGA and passes the 122.88-MHz reference signal to the LMX2582 for its reference.

#### 1.3 LMX2582

The LMX2582 is a wideband RF synthesizer with a range from 20 to 5500 MHz. It has extremely lowphase noise performance, which is critical for RF sampling ADCs. The phase noise at a 3-GHz output at 1-MHz offset is –140 dBc/Hz. This performance rivals that of bench test equipment. The LMX2582 receives its reference frequency of 122.88 MHz from the LMK04828. The LMX2582 is programmed to 2949.12 MHz and its output feeds the ADC32RF80 clock input.

#### 2 Block Diagram

The block diagram of the ADC32RF80 EVM reference design is shown in Figure 1.

Copyright © 2016, Texas Instruments Incorporated

2

#### www.ti.com

#### 3 Test Setup

3.1 Test Configuration

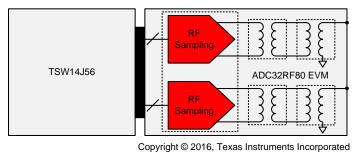

The ADC32RF80 EVM connects to the TSW14J56 EVM capture card as seen in Figure 2. The TSW14J56 interfaces with HSDC Pro software for analyzing the captured patterns.

Figure 2. ADC32RF80 EVM Test Setup

#### 3.2 Input Test Signal

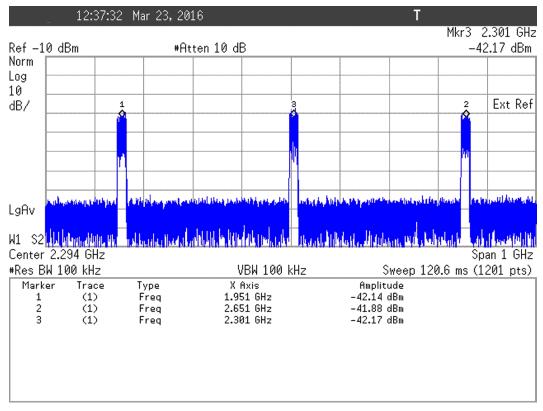

The input test signal is shown in Figure 3. The signal has one 20-MHz LTE carrier centered at 1950 MHz, which is the center of the UMTS receive band. There is a second 20-MHz LTE carrier centered at 2650 MHz. A third signal is centered at 2300 MHz. This signal represents an unwanted interferer that has similar power levels to the desired signals.

3

#### 3.3 ADC32RF80 EVM GUI Setup

The ADC32RF80 EVM is set in a decimate-by-16 mode. The clock rate is 2949.12 MHz. The output data rate is 184.32 MHz (2949.12 / 16). The complex output Nyquist rate is 184.32 MHz, which is plenty wide for a 20-MHz LTE carrier.

The LMK04828 is programmed to a clock rate of 2949.12 MHz to support the necessary SYSREF signals to the ADC32RF80. The LMX2582 is also programmed to an output frequency of 2949.12 MHz for the ADC clock. The ADC32RF80 uses the configuration file "ADC32RF80\_16xIQ\_Imfs8821" to load the registers for decimate-by-16 in a complex output.

Each NCO is set to mix the RF input signal down to the digital baseband. One NCO is set to 1950-MHz and the other is set to 2650 MHz. Note the ADC32RF80 only has a 16-bit NCO; hence, the exact desired frequency values are not achievable. For these tests, the closest achievable frequencies were used. Figure 4 illustrates the DDC tab of the ADC32RFxx GUI software where the user sets the decimation and NCO frequencies.

| ADC32RFxx EVM GUI                                                  |                                        |                             |                                     |                             |                                   | ×                 |  |

|--------------------------------------------------------------------|----------------------------------------|-----------------------------|-------------------------------------|-----------------------------|-----------------------------------|-------------------|--|

| File Debug Settings Help                                           |                                        |                             |                                     |                             |                                   |                   |  |

| ADC32RFxx EVM revD GUI                                             |                                        |                             |                                     |                             |                                   |                   |  |

| Block Diagram ADC32RFxx LMK04828                                   | B LMX2582                              | Low Level \                 | /iew                                |                             | USB Status 🔵                      | 参 Reconnect?      |  |

| ADC Configuration DDC Configuration                                | JESD204B Configurat                    |                             | n                                   |                             |                                   |                   |  |

| Sample Clock 2949.12 MHz (only used for NCO Frequency Calculation) |                                        |                             |                                     |                             |                                   |                   |  |

| DDC Channel A                                                      |                                        |                             | DDC Channel B                       |                             |                                   |                   |  |

| ChA DDC EN                                                         | ChA DDC0 6dB Gain                      |                             | ChB DDC EN                          | ChB DDC EN                  |                                   | ChB DDC0 6dB Gain |  |

| 🕼 ChA Dual Band EN                                                 | ChA DDC1 6dB G                         | GdB Gain I ChB Dual Band EN |                                     | ChB DDC1 6 dB Gain          |                                   |                   |  |

| ChA Real Out EN                                                    | ChA WBF 6dB G                          | ain                         | ChB Real Out EN                     | Real Out EN                 |                                   | ChB WBF 6dB Gain  |  |

| ChA Decim Factor ChA NCO SEL PN<br>Decim x 16 (IQ)                 |                                        | N                           | ChB Decim Factor<br>Decim x 16 (IQ) | •                           | ChB NCO SE                        | L PIN             |  |

| ChA DDC0 NCO1 ChA DDC0 NCO1 freq<br>d 43333 1949.985 MHz           | ChA NCO Select<br>DDC0 NCO 1           | •                           | d 0                                 | ChB DDC0 NCO1 freq<br>0 MHz | ChB NCO Selec<br>DDC0 NCO 1       |                   |  |

| ChA DDC0 NCO2 ChA DDC0 NCO2 freq C                                 | hA LMFC Reset Mode<br>Reset Every LMFC |                             | d 0                                 | ChB DDC0 NCO2 freq          | ChB LMFC Reset I<br>Reset Every L |                   |  |

| ChA DDC0 NC03 ChA DDC0 NC03 freq                                   |                                        |                             | d 0                                 | ChB DDC0 NCO3 freq 0 MHz    |                                   |                   |  |

| ChA.DDC1 NC0 ChA.DDC1 NC0 freq                                     |                                        |                             | d 0                                 | ChB DDC1 NCO freq 0 MHz     |                                   |                   |  |

| Idle HARDWARE CONNECTED 🌵 Texas Instruments                        |                                        |                             |                                     |                             |                                   |                   |  |

|                                                                    |                                        |                             |                                     |                             |                                   |                   |  |

Figure 4. ADC32RFxx DDC Setup Tab

4

www.ti.com

#### 3.4 HSDC Pro Setup

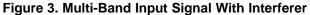

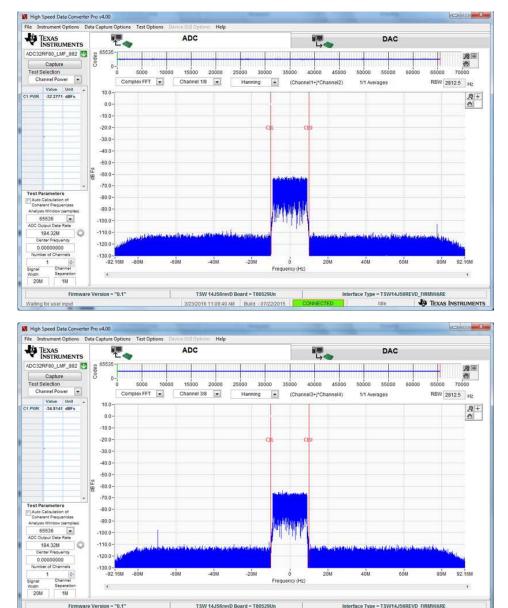

The HSDC Pro software interfaces with the TSW14J56 to capture and analyze the digital data from the ADC32RF80. Set the ini file to "ADC32RF80\_LMF\_8821" to match the ADC serialized output configuration. Since the DDC is activated, the normal ADC calculations must be modified for the digital mixing function. The gear selector next to the ADC Output Data Rate box brings up a pop-up window to input the NCO and decimation parameters. Figure 5 shows the parameter setting for each carrier. The clock rate is set to 2.94912 GHz. The ADC input frequency is set to 2.65 GHz and 1.95 GHz, respectively. The NCO is set to the same value of the NCO setting in the ADC32RFxx software. Notice the actual number is not exact because of the resolution limitation of the 16-bit NCO. The decimation value is set to 16.

| Additional Device Parameters | Additional Device Parameters |  |  |  |

|------------------------------|------------------------------|--|--|--|

| Enable?                      | ☑ Enable?                    |  |  |  |

| ADC Sampling Rate            | ADC Sampling Rate            |  |  |  |

| 2.94912G                     | 2.94912G                     |  |  |  |

| ADC Input Frequency          | ADC Input Frequency          |  |  |  |

| 2.65G                        | 1.95G                        |  |  |  |

| NCO                          | NCO                          |  |  |  |

| 2.650005G                    | 1.949985G                    |  |  |  |

| Decimation                   | Decimation                   |  |  |  |

| 16                           | 16                           |  |  |  |

| ОК                           | ОК                           |  |  |  |

Figure 5. DDC Parameter Setup in HSDC Pro

The ADC32RF80 is a dual-channel device, but because each channel contains two complex (I/Q) down converters, the number of effective converters is eight. This is why the "M" JESD204B parameter, which designates the number of converters, is set to eight. Each carrier resides on a pair (I/Q) of effective channels. In this case, the 1950-MHz carrier is on channel 1 or 2 and the 2.65-GHz carrier is on channel 3 or 4.

Test Setup

#### 4 Measured Performance

The captured patterns in each of the channels are shown in Figure 6. The 20-MHz carrier is downconverted to 0 Hz. The solution has properly captured the signals at the 1950-MHz and 2650-MHz bands. The interferer at 2300 MHz is filtered out. The power of the 1950-MHz carrier is about –30 dBFS; the power of the 2650-MHz carrier is about –35 dBFS. The difference is power level between the carriers is due partly by the roll-off of the source power and partly by the bandwidth roll-off of the ADC32RF80 input due to higher frequencies.

Notice the noise floor rolls off at the band edges. This is due to the decimation filter. The decimation filters limit usable output bandwidth to about 90% of the total available. In this example, the decimate by 16 supports a maximum signal bandwidth of about 165 MHz. The noise floor for each capture is less than –110 dBFs. Part of the noise floor contribution comes from broadband noise in the source. The decimation filter limits the out-of-band noise from folding back within the captured spectrum, so there is an improvement in overall signal-to-noise ratio (SNR). With higher decimation values, the noise contribution decreases as does the bandwidth capability.

Figure 6. DDC Outputs From 1950-MHz and 2650-MHz Bands

3/23/2016 11:07:25 AM Build - 07/22/2015

H TEXAS INSTRUMENTS

www.ti.com

#### 5 Conclusion

The ADC32RF80 operates with multi-band signals. It is effective at capturing desired signals from separate bands and filtering out unwanted interference in other parts of the spectrum. With the decimation filtering, the noise bandwidth is reduced without impacting signal level. This improves SNR performance by a factor of: 10log(Decimation). The DDC allows lower output data rate, band filtering, and improved SNR.

#### 6 Design Files

#### 6.1 Schematics

To download the schematics, see the design files at TIDA-01163.

#### 6.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01163.

#### 6.3 PCB Design Files

To download the PCB design files, see the design files at  $\underline{TIDA-01163}$ .

#### 7 Software Files

To download the software files, see the design files at TIDA-01163.

#### 8 About the Author

**RUSSELL J. HOPPENSTEIN** is the HSP-WI Application Manager at Texas Instruments. He is responsible for high speed data converters, discrete RF devices, and integrated transceivers. Russell earned his master of science in electrical engineering (MSEE) from the University of Texas at Arlington and his bachelor of science in electrical engineering (BSEE) from the University of Texas at Austin.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated