## TI Designs Dynamic Voltage Scaling Power Solution for MSP430<sup>™</sup> FRAM Devices With Single Channel LDO Reference Design

# 🥠 Texas Instruments

## **TI Designs**

TI Designs provide the foundation that you need including methodology, testing, and design files to Steps in Between quickly evaluate and customize the system. TI Designs help you accelerate your time to market.

This TI Design enables power savings for MSP430 FRAM devices or other systems that utilizes a poweron hysteresis. The design uses an adjustable LDO and a RC time delay to switch from a higher start-up voltage to the final low power operating voltage.

**ASK Our E2E Experts**

$\sim$

LDO LP3982

#### **Design Resources**

TI E2E<sup>f</sup><sup>M</sup> Community

Li-Ion Battery

| TIDA-01172   | Design Folder  |

|--------------|----------------|

| LP3982       | Product Folder |

| MSP430FR5969 | Product Folder |

## Design Features

- Low Power Dissipation

- No Additional Active Components Required

- Small Solution Size

- Cost-Optimized Solution

- Ripple-Free and Low-Noise Solution

- TIDA-01172 Provides Design Guide and Design Files of Power Solution

#### **Featured Applications**

- Single Li-Ion Battery Applications

- Power Supplies of MSP430 FRAM Devices

- Personal Electronics

- E-Meter Power Supplies

- DSP and FPGA Power Supplies

- Home or Office Security Monitoring

MSP430 is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

Dynamic Voltage Scaling Power Solution for MSP430™ FRAM Devices With Single Channel LDO Reference Design Copyright © 2016, Texas Instruments Incorporated 1

2

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

## 1 Key System Specifications

This TI Design uses the LP3982 to power MSP430 FRAM devices, and Table 1 describes the recommended operating conditions specific to power with which to configure the LP3982 device to supply power to MSP430 FRAM devices. Table 2 describes the characteristics of the LP3982 that are relevant to power MSP430 FRAM devices.

#### Table 1. Recommended Operating Conditions for MSP430FR59XX

|                 | PARAMETER                                                             | MIN                | NOM | MAX | UNIT |

|-----------------|-----------------------------------------------------------------------|--------------------|-----|-----|------|

| V <sub>cc</sub> | Supply voltage applied at all DVCC and AVCC pins <sup>(1)(2)(3)</sup> | 1.8 <sup>(4)</sup> |     | 3.6 | V    |

| $V_{\rm SS}$    | Supply voltage applied at all DVSS and AVSS pins                      |                    | 0   |     | V    |

<sup>(1)</sup> TI recommends powering AVCC and DVCC pins from the same source. At a minimum, during power up, power down, and device operation, the voltage difference between AVCC and DVCC must not exceed the limits specified in the Absolute Maximum Ratings table of the MSP430FR5969 data sheet. Exceeding the specified limits may cause malfunction of the device including erroneous writes to RAM and FRAM.

<sup>(2)</sup> See Table 5-1 in the MSP430FR5969 data sheet for additional important information.

<sup>(3)</sup> Modules may have a different supply voltage range specification. Refer to the specification of the respective module in the MSP430FR5969 data sheet.

<sup>(4)</sup> The minimum supply voltage is defined by the supervisor SVS levels. See Table 5 for the exact values.

#### Table 2. Design Parameters for LP3982

| DESIGN PARAMETER            | EXAMPLE VALUE            |

|-----------------------------|--------------------------|

| Minimum input voltage       | V <sub>OUT</sub> + 0.5 V |

| Nominal output voltage      | 3.3 V                    |

| Maximum output current      | 300 mA                   |

| RMS noise, 10 Hz to 100 kHz | 37 μV <sub>RMS</sub>     |

| PSRR at 1 kHz               | 60 dB                    |

This design is specifically targeted to be used for MSP430 FRAM devices that must operate at the lowest operating voltage range. With adjustments to the design voltage levels, this design can also be applied to other MSP430 family devices that may require similar voltage sequences in order to operate at their lowest operating voltages. Refer to the MSP430F5xxx/6xxx, MSP430G2xxx, and MSP430F4xx data sheets to see if this design is applicable and what voltage options are necessary to operate the MSP430 family devices at the lowest operating voltages.

#### 2 System Description

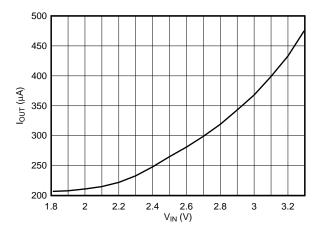

This TI Design focuses on the voltage sequence required to operate MSP430 FRAM devices at their lowest operating voltage. This design is not required for general operation of MSP430 FRAM devices or any other MSP430 devices. Figure 1 shows the current required to toggle a single pin on MSP430 FRAM devices on and off and an exponential curve of the current required based on the  $V_{cc}$  of the MSP430. This TI design leverages power savings by running MSP430 FRAM devices at the lowest voltage required. However, MSP430 FRAM devices contain a hysteresis feature, which requires it to start up with a higher voltage. Therefore, this design explains how to start the output voltage of the LDO with a higher voltage and switch to a lower voltage to ensure maximum power savings.

Figure 1. MSP430 Current Consumption Based on V<sub>cc</sub>

## 2.1 TI MSP430FR5969

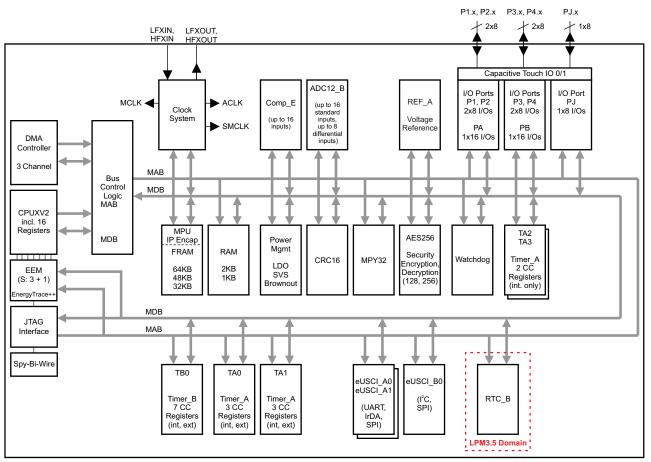

The MSP430 is an ultra-low-power microcontroller that utilizes uniquely embedded FRAM. This is allows users the speed, flexibility, and endurance of SRAM with the stability and reliability of flash at a much lower power. Some of the unique features of the MSP430FR5969 are listed below and a block diagram of these features is shown in Figure 2:

- 16-Bit RISC architecture up to 16-MHz clock

- 64 KB of non-volatile memory

- 66 KB of RAM

- 40 GPIO

- 1 I2C

- 3 SPI

- 2 UART

- 3 DMA

- 12-bit analog-to-digital converter with up to 16 external input channels

- 5 16-bit timers

- Capacitive touch I/O

Copyright © 2016, Texas Instruments Incorporated

Figure 2. Block Diagram of MSP430FR5969

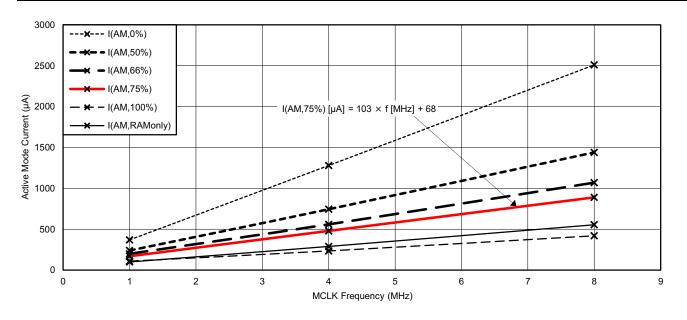

Even with all these features, MSP430 FRAM devices allow a wide supply voltage range from 1.8 V to 3.6 V and requires approximately 100  $\mu$ A/MHz in active mode. Table 3 describes the required current in detail and provides visual representation.

|                                                              |                                 |                 | FREQUENCY ( $f_{MCLK} = f_{SMCLK}$ ) |        |                           |        |                            |        |                             |        |                             |        |      |

|--------------------------------------------------------------|---------------------------------|-----------------|--------------------------------------|--------|---------------------------|--------|----------------------------|--------|-----------------------------|--------|-----------------------------|--------|------|

| PARAMETER                                                    | EXECUTION<br>MEMORY             | V <sub>cc</sub> | 1 M<br>0 wait s<br>(NWAIT)           | states | 4 M<br>0 wait :<br>(NWAIT | states | 8 M<br>0 wait s<br>(NWAIT) | states | 12 M<br>1 wait s<br>(NWAIT) | states | 16 N<br>1 wait s<br>(NWAIT) | states | UNIT |

|                                                              |                                 |                 | TYP                                  | MAX    | TYP                       | MAX    | TYP                        | MAX    | ТҮР                         | MAX    | TYP                         | MAX    |      |

| I <sub>AM, FRAM_UNI</sub><br>(Unified memory) <sup>(3)</sup> | FRAM                            | 3 V             | 210                                  |        | 640                       |        | 1220                       |        | 1475                        |        | 1845                        |        | μA   |

| I <sub>AM, FRAM</sub> (0%) <sup>(4)(5)</sup>                 | FRAM<br>0% cache hit<br>ratio   | 3 V             | 370                                  |        | 1280                      |        | 2510                       |        | 2080                        |        | 2650                        |        | μA   |

| I <sub>AM, FRAM</sub> (50%) <sup>(4)(5)</sup>                | FRAM<br>50% cache hit<br>ratio  | 3 V             | 240                                  |        | 745                       |        | 1440                       |        | 1575                        |        | 1990                        |        | μA   |

| I <sub>AM, FRAM</sub> (66%) <sup>(4)(5)</sup>                | FRAM<br>66% cache hit<br>ratio  | 3 V             | 200                                  |        | 560                       |        | 1070                       |        | 1300                        |        | 1620                        |        | μA   |

| I <sub>AM, FRAM</sub> (75%) <sup>(4)(5)</sup>                | FRAM<br>75% cache hit<br>ratio  | 3 V             | 170                                  | 255    | 480                       |        | 890                        | 1085   | 1155                        | 1310   | 1420                        | 1620   | μA   |

| I <sub>AM, FRAM</sub> (100%) <sup>(4)(5)</sup>               | FRAM<br>100% cache hit<br>ratio | 3 V             | 110                                  |        | 235                       |        | 420                        |        | 640                         |        | 730                         |        | μA   |

| I <sub>AM, RAM</sub> <sup>(6)</sup>                          | RAM                             | 3 V             | 130                                  |        | 320                       |        | 585                        |        | 890                         |        | 1070                        |        | μA   |

| I <sub>AM, RAM only</sub> <sup>(5)(7)</sup>                  | RAM                             | 3 V             | 100                                  | 180    | 290                       |        | 555                        |        | 860                         |        | 1040                        | 1300   | μA   |

| Table 3. Active Mode Supply | Current Into V <sub>cc</sub> | Excluding External | Current for the MSP430 <sup>™(1)(2)</sup> |

|-----------------------------|------------------------------|--------------------|-------------------------------------------|

|                             |                              |                    |                                           |

$^{(1)}$  All inputs are tied to 0 V or to  $V_{\text{CC}}.$  Outputs do not source or sink any current.

<sup>(2)</sup> Characterized with program executing typical data processing.

$f_{ACLK} = 32768$  Hz,  $f_{MCLK} = f_{SMCLK} = f_{DCO}$  at specified frequency, except for 12 MHz. For 12 MHz,  $f_{DCO} = 24$  MHz and  $f_{MCLK} = f_{SMCLK} = f_{DCO} / 2$ . At MCLK frequencies above 8 MHz, the FRAM requires wait states. When wait states are required, the effective MCLK

At MCLK frequencies above 8 MHz, the FRAM requires wait states. When wait states are required, the effective MCLK frequency ( $f_{MCLK,eff}$ ) decreases. The effective MCLK frequency also depends on the cache hit ratio. SMCLK is not affected by the number of wait states or the cache hit ratio.

The following equation can be used to compute  $f_{\rm MCLK,eff}\!\!\!:$

$f_{\text{MCLK,eff}} = f_{\text{MCLK}}$  / [wait states × (1 - cache hit ratio) + 1]

For example, with 1 wait state and 75% cache hit ratio  $f_{\text{MCKL,eff}} = f_{\text{MCLK}} / [1 \times (1 - 0.75) + 1] = f_{\text{MCLK}} / 1.25$ .

<sup>(3)</sup> Represents typical program execution. Program and data reside entirely in FRAM. All execution is from FRAM.

<sup>(4)</sup> Program resides in FRAM. Data resides in SRAM. Average current dissipation varies with cache hit-to-miss ratio as specified. Cache hit ratio represents number cache accesses divided by the total number of FRAM accesses. For example, a 75% ratio implies three of every four accesses is from cache, and the remaining are FRAM accesses.

<sup>(5)</sup> See Figure 3 — each characteristic equation shown in the graph is computed using the least squares method for best linear fit using the typical data shown in Table 3.

<sup>(6)</sup> Program and data reside entirely in RAM. All execution is from RAM.

<sup>(7)</sup> Program and data reside entirely in RAM. All execution is from RAM. FRAM is off.

#### System Description

Figure 3. Typical Characteristics - Active Mode Supply Currents for MSP430

## 2.2 TI LP3982

The LP3982 device was chosen for its adjustable version with low dropout of 120 mV typical and up to 300 mA of output current. The following features were also put into consideration for this application with the low power MSP430:

- 2.5-V to 6-V input range

- 1-nA typical shutdown mode

- 90-μA typical low quiescent current

- 60-dB typical PSRR

- $37-\mu V_{RMS}$  output voltage noise

- ±2% output voltage tolerance

- Stable with capacitance Loads of 2.2 µF

- Small package sizes: 2.50 mm × 3.00 mm (WSON) and 3.00 mm × 3.00 mm (VSSOP)

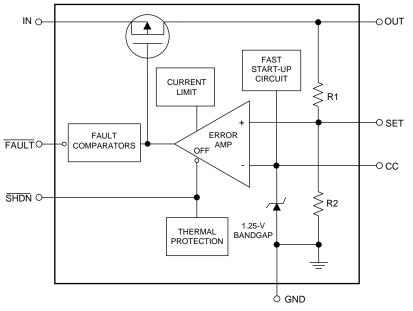

Table 4 provides a more detailed description of the operating characteristics of the LP3982, and Figure 4 shows the functional block diagram of the LP3982 to show how the LDO operates internally.

|                                           | PARAMETER           | TEST CONDITIONS                                                                                                                                                                                           | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT                  |

|-------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|-----------------------|

| V <sub>IN</sub>                           | Input voltage       | For operating temperature extremes: -40°C to 85°C                                                                                                                                                         | 2.5                |                    | 6                  | V                     |

| $\Delta V_{OUT}$ Output voltage tolerance |                     | $ \begin{array}{l} 100 \; \mu A \leq I_{OUT} \leq 300 \; mA \\ V_{\text{IN}} = V_{OUT} + 0.5 \; V^{(3)} \\ \text{SET} = \text{OUT for the ADJ Versions, } T_{\text{J}} = 25^{\circ}\text{C} \end{array} $ | -2                 |                    | 2                  | % of V <sub>OUT</sub> |

|                                           |                     | For operating temperature extremes: -40°C to 85°C                                                                                                                                                         | -3                 |                    | 3                  | (NOM)                 |

| V <sub>OUT</sub>                          | Output adjust range | ADJ version only;<br>for operating temperature extremes: -40°C to<br>85°C                                                                                                                                 | 1.25               |                    | 6                  | V                     |

- <sup>(1)</sup> All limits are verified by testing or statistical analysis.

- <sup>(2)</sup> Typical values represent the most likely parametric norm.

- <sup>(3)</sup> Condition does not apply to input voltages below 2.5 V because this is the minimum input operating voltage.

|                    | PARAMETER                         | TEST CONDITIONS                                                                                                                                                             | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT         |  |

|--------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|--------------|--|

| I <sub>out</sub>   | Maximum output current            | Average DC current rating;<br>For operating temperature extremes: -40°C<br>and 85°C                                                                                         | 300                |                    |                    | mA           |  |

|                    |                                   | $T_J = 25^{\circ}C$                                                                                                                                                         |                    | 770                |                    |              |  |

| LIMIT              | Output current limit              | For operating temperature extremes: -40°C to 85°C                                                                                                                           |                    |                    | mA                 |              |  |

| ۱ <sub>۵</sub>     |                                   | $I_{OUT} = 0 \text{ mA}, T_J = 25^{\circ}\text{C}$                                                                                                                          |                    | 90                 |                    |              |  |

|                    | Supply current                    | $I_{OUT} = 0 \text{ mA}$<br>for operating temperature extremes: $-40^{\circ}C$ to $85^{\circ}C$                                                                             |                    |                    | 270                | μΑ           |  |

|                    |                                   | I <sub>OUT</sub> = 300 mA                                                                                                                                                   |                    | 225                |                    |              |  |

|                    | Shutdown supply current           | $V_0 = 0 \text{ V}, \overline{\text{SHDN}} = \text{GND}, T_J = 25^{\circ}\text{C}$                                                                                          |                    | 0.001              | 1                  | μA           |  |

|                    | 1                                 | $I_{OUT} = 1 \text{ mA}, T_J = 25^{\circ}\text{C}$                                                                                                                          |                    | 0.4                |                    |              |  |

|                    |                                   | $I_{OUT} = 200 \text{ mA}, T_{J} = 25^{\circ}\text{C}$                                                                                                                      |                    | 80                 |                    |              |  |

| / <sub>DO</sub>    | Dropout voltage <sup>(3)(4)</sup> | $I_{OUT} = 200 \text{ mA}$<br>for operating temperature extremes: $-40^{\circ}$ C to $85^{\circ}$ C                                                                         |                    |                    | 220                | mV           |  |

|                    |                                   | I <sub>OUT</sub> = 300 mA, T <sub>J</sub> = 25°C                                                                                                                            |                    | 120                |                    |              |  |

|                    | Line regulation                   | $\begin{split} I_{\text{OUT}} &= 1 \text{ mA, } T_{\text{J}} = 25^{\circ}\text{C} \\ (V_{\text{OUT}} + 0.5 \text{ V}) \leq V_{\text{I}} \leq 6 \text{ V}^{(3)} \end{split}$ | 0.01               |                    |                    |              |  |

| ΔV <sub>OUT</sub>  |                                   | $I_{OUT} = 1 \text{ mA}$ , $(V_{OUT} + 0.5 \text{ V}) \le V_i \le 6 \text{ V}^{(3)}$ ;<br>for operating temperature extremes: $-40^{\circ}\text{C}$ to $85^{\circ}\text{C}$ | -0.1               |                    | 0.1                | %/V          |  |

|                    | Load regulation                   | 100 $\mu$ A $\leq$ I <sub>OUT</sub> $\leq$ 300 mA, T <sub>J</sub> = 25°C                                                                                                    |                    | 0.002              |                    | %/m/         |  |

|                    | Output voltage noise              | $I_{OUT} = 10 \text{ mA}, 10 \text{ Hz} \le f \le 100 \text{ kHz}, T_J = 25^{\circ}\text{C}$                                                                                |                    | 37                 |                    | $\mu V_{RM}$ |  |

| 9 <sub>n</sub>     | Output voltage noise density      | 10 Hz $\leq$ f $\leq$ 100 kHz, C <sub>OUT</sub> = 10 µF, T <sub>J</sub> = 25°C                                                                                              |                    | 190                |                    | nV/√F        |  |

|                    |                                   | $V_{\text{IH}}$ (V_{\text{OUT}} + 0.5 V) $\leq$ $V_{\text{IN}}$ $\leq$ 6 V $^{(3)}$ ; for operating temperature extremes: –40°C to 85°C                                     | 2                  |                    |                    | V            |  |

|                    | SHDN input threshold              | $V_{lL^*}(V_{OUT}$ + 0.5 V) $\leq V_{lN} \leq 6 \ V^{(3)};$ for operating temperature extremes: –40°C to 85°C                                                               |                    |                    | 0.4                | V            |  |

| SHDN               | SHDN input bias current           | $\overline{SHDN} = GND \text{ or IN}, T_J = 25^{\circ}C$                                                                                                                    |                    | 0.1                | 100                | nA           |  |

| SET                | SET input leakage                 | SET = 1.3 V, ADJ version only <sup>(5)</sup>                                                                                                                                |                    | 0.1                | 2.5                | nA           |  |

|                    |                                   | $V_{O} \ge 2.5 \text{ V}, \text{ I}_{OUT} = 200 \text{ mA}, \text{ T}_{J} = 25^{\circ}\text{C}^{(6)}$                                                                       |                    | 120                |                    |              |  |

|                    | FAULT detection voltage           | $V_{OUT} \ge 2.5 \text{ V}, I_{OUT} = 200 \text{ mA}^{(6)};$<br>for operating temperature extremes: -40°C to<br>85°C                                                        |                    |                    | 280                | mV           |  |

| V <sub>FAULT</sub> |                                   | $I_{SINK} = 2 \text{ mA}, T_J = 25^{\circ}\text{C}$                                                                                                                         |                    | 0.115              |                    |              |  |

|                    | FAULT output low voltage          | $I_{SINK} = 2 \text{ mA}$<br>for operating temperature extremes: $-40^{\circ}C$ to $85^{\circ}C$                                                                            |                    |                    | 0.25               | V            |  |

| FAULT              | FAULT off-leakage current         | FAULT = 3.6 V, SHDN = 0 V, T <sub>J</sub> = 25°C                                                                                                                            |                    | 0.1                | 100                | nA           |  |

| Γ                  | Thermal shutdown temperature      | $T_{J} = 25^{\circ}C$                                                                                                                                                       |                    | 160                |                    | °C           |  |

| T <sub>SD</sub>    | Thermal shutdown hysteresis       | $T_{J} = 25^{\circ}C$                                                                                                                                                       |                    | 10                 |                    |              |  |

|                    |                                   |                                                                                                                                                                             |                    |                    |                    |              |  |

Table 4. Operating Characteristics of LP3982 (continued)

<sup>(4)</sup> Dropout voltage is measured by reducing V<sub>IN</sub> until V<sub>OUT</sub> drops 100 mV from its nominal value at V<sub>IN</sub> - V<sub>OUT</sub> = 0.5 V. Dropout voltage does not apply to the 1.8-V version.

<sup>(5)</sup> The SET pin is not externally connected for the fixed versions.

<sup>(6)</sup> The FAULT detection voltage is specified for the input-to-output voltage differential at which the FAULT pin goes active low.

Copyright © 2016, Texas Instruments Incorporated

Figure 4. LP3982 Functional Block Diagram

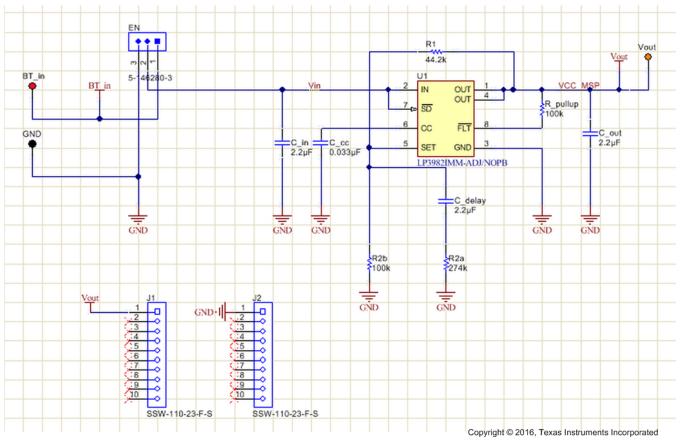

#### 3 Circuit Diagram

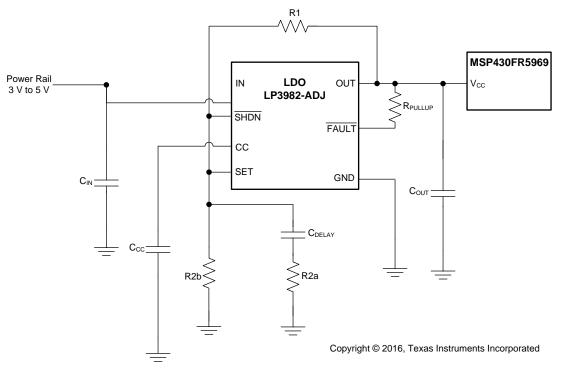

Figure 5 shows the full schematic of the circuit. The power rail or input voltage to the LDO must be equal to, or greater than, the starting output voltage of the LDO with the addition of the dropout voltage. To be more specific within this design, the desired output voltage of the LDO must start equal to or above the power-up voltage of MSP430 FRAM devices. Therefore, the minimum input to the LDO must be the start-up voltage of the MSP430 FRAM device with the addition of the dropout voltage. Numerical details are described in detail in Section 4.

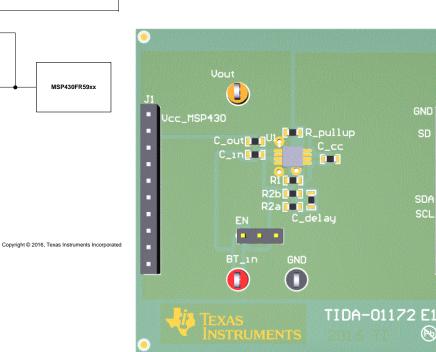

Figure 5. Full Schematic of the System

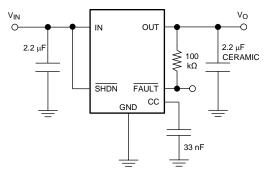

$C_{IN}$  and  $C_{OUT}$  are determined based on stability. The LP3982 is stable with a 2.2-µF ceramic output capacitor. The bypass capacitor  $C_{CC}$  is in place to reduce the output noise without slowing the transient response. The pullup resistor is in place for the FAULT pin because it is an open-drain circuit. TI recommends a 100-k $\Omega$  resistor for most applications. Figure 6 shows a typical application schematic referenced from the LP3982 data sheet with the recommended component values.

Figure 6. LP3982 Typical Application (Fixed V<sub>out</sub> Version)

Circuit Diagram

## 4 Dynamic Voltage Scaling

The TI Design uses the LP3982 adjustable output voltage to switch between the required starting voltage and the final power efficient voltage for MSP430 FRAM devices. The output voltage of the LP3982 is set with the combination of resistors in a negative feedback configuration, shown in Figure 5, and is characterized by Equation 1:

VIN

₹ 1

O VOUT

Vo = VREF

$$\left\lfloor \frac{R_1}{R_2} + \frac{R_2}{R_2} \right\rfloor$$

where

10

- R<sub>1</sub> is the resistor between OUT and and the SET pin

- R<sub>2</sub> is connected between the SET pin and GND

- V<sub>REF</sub> is set to be 1.25 V according to the LP3982 datasheet

VREF

R₁

The data sheet also suggests setting R2 to be 100 k $\Omega$  to optimize accuracy, power supply rejection, noise, and power consumption. Finally, to find out what the appropriate output needs to be, the MSP430FR5969 data sheet is referenced. The recommended operating conditions suggest the supply voltage range V<sub>cc</sub> to be at least 1.8 V minimum, and 3.6 V maximum, with the system power down level V<sub>SVSH</sub> ranging from 1.75 V to 1.85 V with 1.8 V typical. For optimal power efficiency, the MSP430 FRAM device must operate at the voltage just above the shutdown voltage. Table 5 describes the power-on characteristics of the MSP430. The power-up level V<sub>SVSH</sub> ranges from 1.77 V to 1.99 V with 1.85 V typical and the hysteresis V<sub>SVSH\_hys</sub> to be 40 mV minimum, 120 mV maximum. To ensure that the MSP430 FRAM device starts up, output voltage at the beginning must be at least over 1.99 V. Finally, to save power, the final settled value of V<sub>o</sub> must be just slightly higher than the voltage at which the MSP430 FRAM device powers down. In this design, the start-up value was chosen to be 2 V, and the operating voltage was chosen to be 1.8 V. Section 4.1 explains in detail the design process.

| Table 5. | Hysteresis | Design | Parameters <sup>(1)</sup> |

|----------|------------|--------|---------------------------|

|----------|------------|--------|---------------------------|

|                          | PARAMETER                                             | TEST CONDITIONS                             | MIN  | ТҮР  | MAX  | UNIT |

|--------------------------|-------------------------------------------------------|---------------------------------------------|------|------|------|------|

| I <sub>SVSH,LPM</sub>    | SVS <sub>H</sub> current consumption, low power modes |                                             |      | 170  | 300  | nA   |

| V <sub>SVSH-</sub>       | SVS <sub>H</sub> power-down level                     |                                             | 1.75 | 1.8  | 1.85 | V    |

| V <sub>SVSH+</sub>       | SVS <sub>H</sub> power-up level                       |                                             | 1.77 | 1.88 | 1.99 | V    |

| $V_{\text{SVSH}_hys}$    | SVS <sub>H</sub> hysteresis                           |                                             | 40   |      | 120  | mV   |

| t <sub>PD,SVSH, AM</sub> | $SVS_H$ propogation delay, active mode                | $dV_{VCC}/dt = -10 \text{ mV}/\mu \text{s}$ |      |      | 10   | μs   |

<sup>(1)</sup> Over recommended ranges of supply voltage and operating free-air temperature

(1)

#### 4.1 Application Notes

To achieve dynamic voltage scaling with a single output LDO, an RC time delay is added to the circuit in parallel with  $R_{2a}$  to effectively change the feedback resistance to the SET pin of the LDO, as shown in Figure 4. To evaluate the effects of the time delay, the basic behaviors of a capacitor must first be visited. Ideally, during start-up, there is no charge in the capacitor, and when the LDO powers up to 2 V, the capacitor acts as a short in which case the two resistors are in parallel and can be equivalently combined to form:

$$VO = VREF\left[\frac{R1}{R_{2a} || R_{2b}} + 1\right]$$

or

$$VO = VREF\left[\frac{R1}{R2a} + \frac{R1}{R2b} + 1\right]$$

(2)

Dynamic Voltage Scaling

As the capacitor begins to charge, the current through  $R_{2a}$  begins to drop, and the capacitor begins to have an effect on the circuit. This can be characterized with Equation 3:

$$V_{O} = V_{REF} \left[ \frac{R_{1}}{R_{2b}} + \frac{R_{1}}{R_{2a}} e^{-t/R_{2a} \times C_{DELAY}} + 1 \right]$$

(3)

When the capacitor is fully charged at steady state, the capacitor appears to be an open circuit, and there is no current through  $R_{2a}$ . In this case Equation 3 can be simplified to Equation 4:

$$VO = VREF \left[ \frac{R_1}{R_{2b}} + 1 \right]$$

(4)

With  $V_{REF}$  set at 1.25 V,  $R_{2b}$  set as 100 k $\Omega$  to optimize for noise and accuracy, and desired output voltage (V<sub>o</sub>) of 1.8 V, when the capacitor reaches steady state (open circuit),  $R_1$  is calculated as 44.2 k $\Omega$ . Once  $R_1$  is calculated, the start-up short circuit equation, Equation 2, can be used to calculate  $R_{2a}$ . With output voltage of 2 V during start-up according to the MSP430FR5969 data sheet,  $R_{2a}$  was calculated as 274 k $\Omega$ .

After trying out the circuit with these calculated values,  $R_{2b}$  was readjusted to 100 k $\Omega$  so that the start-up voltage is 2.355 V to ensure that the MSP430 starts up regardless of process variation and device tolerances.  $C_{\text{DELAY}}$  was calculated using Equation 5 as 2.2 µF for the time constant of 220 ms.

$\tau = R_{2b} \ \times \ C \text{DELAY}$

(5)

Dynamic Voltage Scaling

## 4.2 Test Data

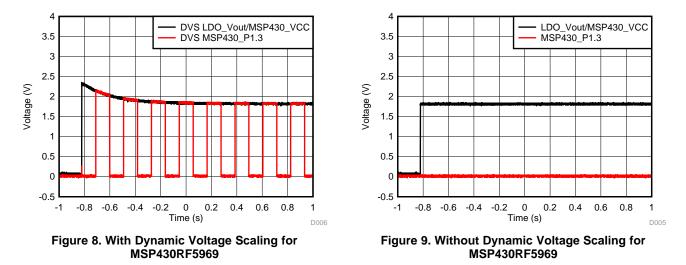

Figure 8 and Figure 9 show the importance of the dynamic voltage scaling. Figure 8 shows the MSP430 FRAM device with the dynamic voltage scaling. The red line shows the MSP430 FRAM device maintaining operation even as  $V_{CC}$ , shown with the black line, ramps down from 2.3 V to 1.8 V. The black line in Figure 9 shows the MSP430 FRAM device  $V_{CC}$  staying consistent at 1.8 V without dynamic voltage scaling. As a result, the corresponding output pin of the MSP430 FRAM device, shown with the red line in Figure 9, is not toggling, which shows that the MSP430 FRAM device is not operating. Figure 8 and Figure 9 are shown side-by-side for a direct comparison.

## 5 Design Files

## 5.1 Schematics

To download the schematics, see the design files at TIDA-01172.

Figure 10. TIDA-01172 Schematic

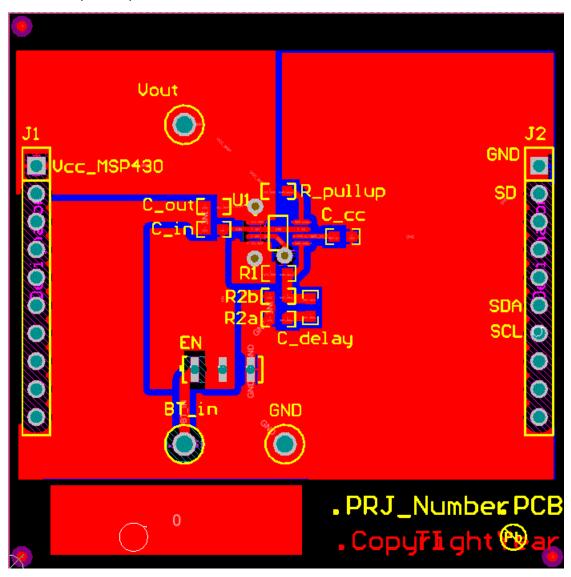

## 5.2 PCB Layout Recommendations

#### 5.2.1 Layout Guidelines

For optimal performance, place  $C_{IN}$  and  $C_{OUT}$  as close as possible to the pins of the LP3982 device. A large area ground plane is also preferred for good heat dissipation. Lastly, avoid long traces and narrow trace widths to prevent parasitic inductances.

Figure 11. PCB Layout Guidelines

.

## 5.3 Layout Prints

To download the layer plots, see the design files at TIDA-01172.

## 5.4 Gerber Files

To download the Gerber files, see the design files at TIDA-01172.

## 6 References

- 1. MSP430FR59xx Mixed-Signal Microcontrollers data sheet

- 2. LP3982 Micropower, Ultra-Low-Dropout, Low-Noise, 300-mA CMOS Regulator data sheet

## 7 About the Author

JERRY LEUNG is an Applications Engineer in the Flexible Power and LDOs group at Texas Instruments.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ('TI') reference designs are solely intended to assist designers ("Designer(s)") who are developing systems that incorporate TI products. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.

TI's provision of reference designs and any other technical, applications or design advice, quality characterization, reliability data or other information or services does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such reference designs or other items.

TI reserves the right to make corrections, enhancements, improvements and other changes to its reference designs and other items.

Designer understands and agrees that Designer remains responsible for using its independent analysis, evaluation and judgment in designing Designer's systems and products, and has full and exclusive responsibility to assure the safety of its products and compliance of its products (and of all TI products used in or for such Designer's products) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to its applications, it has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any systems that include TI products, Designer will thoroughly test such systems and the functionality of such TI products as used in such systems. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equivalent classifications outside the U.S.

Designers are authorized to use, copy and modify any individual TI reference design only in connection with the development of end products that include the TI product(s) identified in that reference design. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of the reference design or other items described above may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS AND OTHER ITEMS DESCRIBED ABOVE ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNERS AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS AS DESCRIBED IN A TI REFERENCE DESIGN OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

TI's standard terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products. Additional terms may apply to the use or sale of other types of TI products and services.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's noncompliance with the terms and provisions of this Notice.

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated