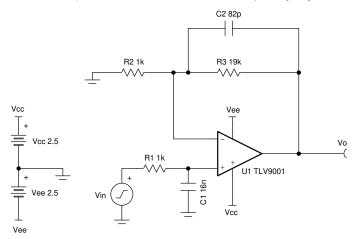

# Analog Engineer's Circuit Low-pass, filtered, non-inverting amplifier circuit

Amplifiers

### **Design Goals**

| Input             |                   | Output            |                   | BW             | Supply          |                 |

|-------------------|-------------------|-------------------|-------------------|----------------|-----------------|-----------------|

| V <sub>iMin</sub> | V <sub>iMax</sub> | V <sub>oMin</sub> | V <sub>oMax</sub> | f <sub>c</sub> | V <sub>cc</sub> | V <sub>ee</sub> |

| -0.1V             | 0.1V              | -2V               | 2V                | 10kHz          | 2.5V            | -2.5V           |

### **Design Description**

This low-pass non-inverting circuit amplifies the signal level by 20V/V (26dB) and filters the signal by setting the pole at 10kHz. Components  $R_1$  and  $C_1$  create a low-pass filter on the non-inverting pin. The frequency response of this circuit is the same as that of a passive RC filter, except that the output is amplified by the pass-band gain of the amplifier. Components  $C_2$  and  $R_3$  are used to set the cutoff frequency,  $f_c$  of the non-inverting amplifier.

## **Design Notes**

- 1. The common-mode voltage is equal to the input voltage applied to the non-inverting input of the op amp.

- 2. Using high-value resistors can degrade the phase margin of the circuit and introduce additional noise in the circuit.

- 3. Set the pole frequency created by R<sub>3</sub> / C<sub>2</sub> to be ten times higher than the pole created by R<sub>1</sub> / C<sub>1</sub> to achieve a single poll roll-off that is dominated by R<sub>1</sub> / C<sub>1</sub>. If the filter pairs R<sub>1</sub> / C<sub>1</sub> and R<sub>3</sub> / C<sub>2</sub> have the same pole frequency, the gain will be reduced by 6dB at the cutoff frequency. Also the gain decreases at a rate of -40dB/dec until the response reaches 0dB, after which the slope changes to -20dB/dec until the op amp runs out of bandwidth.

- 4. C<sub>2</sub> limits the bandwidth of the non-inverting gain stage.

- 5. Avoid placing capacitive loads directly on the output of the amplifier to minimize stability issues.

- 6. Large signal performance may be limited by slew rate. Therefore, check the maximum output swing versus frequency plot in the data sheet to minimize slew-induced distortion.

- 7. For more information on an op amp linear operating region, stability, slew-induced distortion, capacitive load drive, driving ADCs, and bandwidth, see the *Design References* section.

1

# **Design Steps**

The DC transfer function of this circuit follows:

$$V_{o} = V_{in} \times (1 + \frac{R_{3}}{R_{2}})$$

1. Calculate the gain.

Gain =

$$\frac{V_{oMax} - V_{oMin}}{V_{iMax} - V_{iMin}} = \frac{2V - (-2V)}{0.1V - (-0.1V)} = 20\frac{V}{V}$$

2. Calculate values for R<sub>2</sub> and R<sub>3</sub>.

Gain = 1 +

$$\frac{R_3}{R_2}$$

= 20  $\frac{V}{V}$   $\rightarrow$  (26dB)

Choose  $R_2 = 1k\Omega$ :

$$R_3 = (Gain - 1) \times R_2 = 19k\Omega$$

3. Calculate the component values  $R_1$  and  $C_1$  to set the cutoff frequency,  $f_c$ . Pick the value of  $R_1$  and then calculate  $C_1$  to set the location of  $f_c$ .

Choose  $R_1 = 1k\Omega$ :

$C_1 = \frac{1}{2\pi \times R_1 \times f_c} = \frac{1}{2\pi \times 1 k\Omega \times 10 kHz} = 15.92 nF \approx 16 nF \text{ (Standard Value)}$

4. Calculate  $C_2$  value to set the cutoff frequency ( $f_c$ ) of the op amp. Select the corner frequency to be at least ten times larger than  $f_c$ .

$$f_{c} = 10 \text{kHz}; 10 \times f_{c} = 100 \text{kHz}$$

$$C_2 = \frac{1}{2\pi \times R_3 \times 100 \text{kHz}} = \frac{1}{2\pi \times 19 \text{k}\Omega \times 100 \text{kHz}} = 83.77 \text{pF} \approx 82 \text{pF} \text{ (Standard Value)}$$

## **Design Simulations**

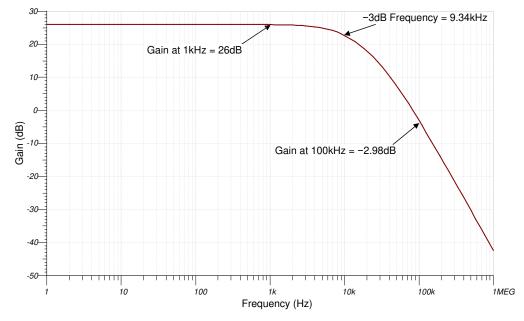

# **AC Simulation Results**

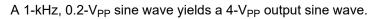

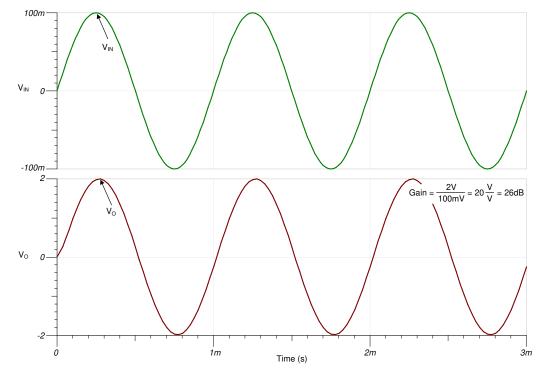

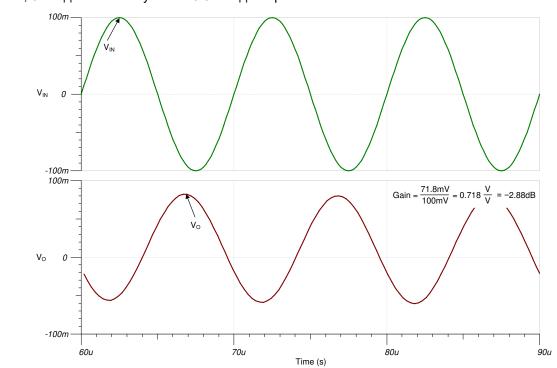

# **Transient Simulation Results**

A 100-kHz, 0.2-V<sub>PP</sub> sine wave yields a 0.071-V<sub>PP</sub> output sine wave.

## **Design References**

- 1. See Analog Engineer's Circuit Cookbooks for the comprehensive TI circuit library.

- 2. SPICE Simulation File SBOC528.

- 3. TI Precision Labs

- 4. See the AC Coupled, Single-Supply, Inverting and Non-inverting Amplifier Reference Design.

### **Design Featured Op Amp**

| TLV9001                    |              |  |  |  |

|----------------------------|--------------|--|--|--|

| V <sub>ss</sub>            | 1.8V to 5.5V |  |  |  |

| V <sub>inCM</sub>          | Rail-to-rail |  |  |  |

| V <sub>out</sub>           | Rail-to-rail |  |  |  |

| V <sub>os</sub>            | 0.4mV        |  |  |  |

| lq                         | 60µA         |  |  |  |

| ا <sub>له</sub>            | 5pA          |  |  |  |

| UGBW                       | 1MHz         |  |  |  |

| SR                         | 2V/µs        |  |  |  |

| #Channels                  | 1,2,4        |  |  |  |

| www.ti.com/product/TLV9001 |              |  |  |  |

# **Design Alternate Op Amp**

| OPA375                    |                             |  |  |  |

|---------------------------|-----------------------------|--|--|--|

| V <sub>ss</sub>           | 2.25V to 5.5V               |  |  |  |

| V <sub>inCM</sub>         | $V_{ee}$ to $V_{cc}$ – 1.2V |  |  |  |

| V <sub>out</sub>          | Rail-to-rail                |  |  |  |

| V <sub>os</sub>           | 0.15mV                      |  |  |  |

| Ιq                        | 890µA                       |  |  |  |

| I <sub>b</sub>            | 10pA                        |  |  |  |

| UGBW                      | 10MHz                       |  |  |  |

| SR                        | 4.75V/µs                    |  |  |  |

| #Channels                 | 1,2,4                       |  |  |  |

| www.ti.com/product/OPA375 |                             |  |  |  |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated