# 低 EMI 設計を 電源モジュールで簡素化

#### Michael Daimer

アナログ・フィールド・アプリケーション・エンジニア テキサス・インスツルメンツ

# スイッチング電源の設計者であれば、電磁妨害 (EMI) について耳にしたことがあるのではないでしょうか。

ますます多くのアプリケーションが、商業用販売の承認を得るためにEMI標準への準拠を必要としています。スイッチング電源は、デバイス内に電気的スイッチが存在することを意味し、そこからEMIが放射されます。

このホワイト・ペーパーでは、スイッチング電源でのEMIの発生要因と、EMI軽減のための方法や技術について説明します。 また、電源モジュール(コントローラ、ハイサイド/ローサイドFET、およびインダクタを1つのパッケージに搭載)がEMIの 低減にどのように役立つかについても示します。

# スイッチング電源での EMI の発生要因

まず、物理法則には逆らえません。マスクウェルの式によれば、交流電流は電磁場を生成します。これはすべての導電体で発生します。それらは元来いくらかの静電容量とインダクタンスを持ち、それにより発振回路を形成します。この発振回路は、特定の周波数  $(f=1/(2^*\pi^*\text{sqrt}(LC)))$  で電磁気エネルギーを空間に放射します。この回路は電磁気エネルギーの送信器として機能しますが、電磁気エネルギーを受け取る受信器としても機能します。アンテナは、送信または受信されるエネルギーが最大となるように設計されています。

しかし、必ずしもすべてのアプリケーションがアンテナとして機能する必要はなく、望ましくない副作用が起こる場合もあります。たとえば、スイッチング降圧電源は高い電圧を低い電圧に変換するよう設計されていますが、電磁波の(望ましくない)送信器としても機能し、AM帯域への干渉など、他のアプリケーションに外乱を与える場合があります。このような効果をEMIと呼びます。

機能を維持するためには、EMIの発生要因を最小限に抑えることが重要です。国際無線障害特別委員会(CISPR)では、 車載用電気アプリケーションのベンチマークであるCISPR 25や情報技術機器向けのCISPR 22などの標準を定義しています。

電源設計の放射EMIを低減するにはどうすればよいでしょうか。1つの方法は、スイッチング電源を金属で完全に遮蔽することです。しかし、ほとんどのアプリケーションでは、これはコストとスペースの関係で実現できません。より適切なアプローチは、EMIの発生要因を減らし、最適化することです。これに関して詳しく取り上げた文献は既に多くありますが、この記事の最後で2つの文献を推薦しています。

それでは、スイッチング電源でのEMIの主な発生要因と、な ぜ電源モジュールによってEMIを簡単に低減できるのかを見 ていきます。

## レイアウト内の電流ループの最小化

スイッチング電源は、その名の通りスイッチングを行います。 数百kHzから数MHzまでの周波数で、入力電圧のオン/オフを切り替えています。これにより、高速な電流遷移(dI/dt)と高速な電圧遷移(dV/dt)が生じます。交流電流および電圧は、マクスウェルの式に従って交流電磁場を発生させます。これらの電磁場は原点から放射状に広がり、その強さは距離とともに低下します。

2018

**図 1.** スイッチ・モード電源からの EMI は負荷および 1 次電源に影響を与える。

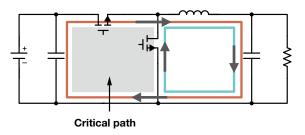

**図 2.** 入力、スイッチ、入力コンデンサの間にクリティカルな電流 ループが形成される。

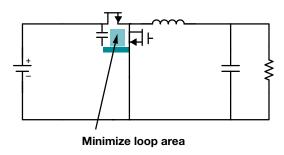

図3. ループ領域の最小化が EMI の軽減に役立つ。

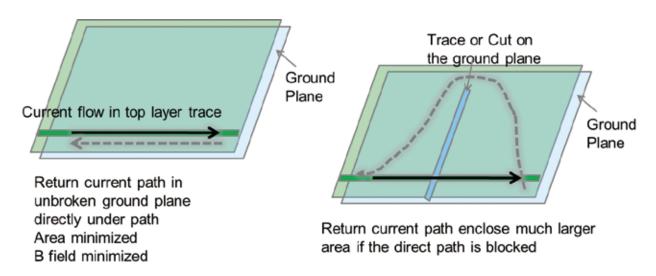

磁場および電場はアプリケーションの導電部品(アンテナのように機能するプリント基板(PCB)上の銅パターンなど)に

干渉し、ライン上に追加のノイズを発生させ、それがさらに EMIを生じます(図1を参照)。数ワットの電力が変換される という事実により、放射されるEMIの範囲が増大します。放射される電磁気エネルギーは、電流の大きさ(I) およびそれが流れるループの面積(A)に直接比例します。交流電流ループと交流電圧ループの面積を最小限に抑えれば、EMIの低減に役立ちます(図2および図3を参照)。

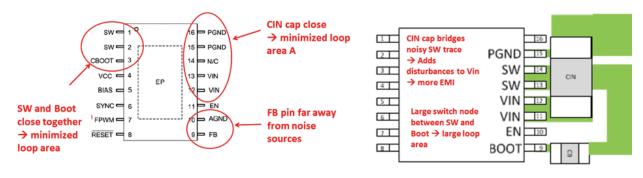

ピン配置(図4を参照)を見ると、高dI/dtのループ面積を減らして良好なレイアウトを作成できる可能性が見えてきます。たとえば、スイッチ・ノードは高電流変動(dI)と高電圧遷移(dV)の両方の要因となります。適切なピン配置では、ノイズに敏感なピンがノイズの多いピンから分離されています。スイッチ・ノードとブート・ピンは、ノイズに敏感なフィードバック・ピンからできる限り遠ざける必要があります。また、入力ピンとグランド・ピンは隣接させる必要があります。これにより、PCB上の配線および入力コンデンサの配置が容易になります。

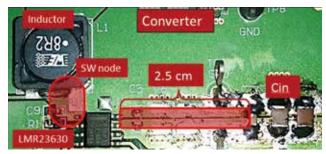

図5は、LMR23630 SIMPLE SWITCHER®コンバータの評価モジュール(EVM) に変更を加えたものです。2つの入力コンデンサが入力ピンから約2.5cm離れています。これは悪いレイアウトをシミュレートするためのものであり、電流ループ領域(図5の赤色の長方形)が、データシートで要件として規定された値よりも大きくなっています。図5の赤色の楕円形は、コンバータとインダクタの間のスイッチ・ノードを示しています。ICとインダクタの間のループ領域はできる限り小さくなっています。

**図 4.** ピン配置によるループ領域の最小化。左:最適化されたピン配置、右:ピン配置が最適化されていないため、良好なレイアウトがほとんど不可能。

**図 5.** 入力ピンと入力コンデンサの間に大きなループ領域(赤色の長方形)を持つ悪いレイアウトの例。2番目のループ領域(赤色の楕円形)はICとインダクタ間に形成。

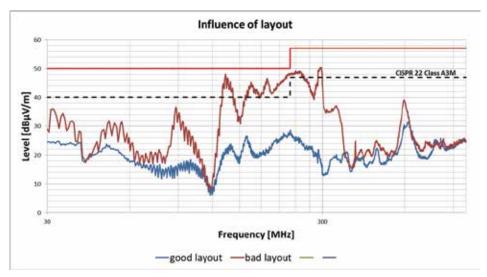

図6のグラフは、VIN、GND、入力コンデンサの間に形成されるループ領域だけが異なる場合の、LMR23630コンバータの放射EMIを示しています。良好なレイアウトでは、入力およびグランド・ピンにできる限り近づけてコンデンサが配置されます(ループ領域をできる限り小さくする)。悪いレイアウトでは、入力コンデンサが入力ピンから2.5cm離して配置され、大きなループ領域が形成されます。

図6のグラフの赤色の線は、悪いレイアウトでの放射 EMIを示しています。青色の線は、同じ EVMを使用した良好なレイアウトでの放射 EMIを示しています。1つのループ領域を変更するだけで大きな効果が得られています。コンバータ LMR23630の放射 EMI レベルを20dB  $\mu$  V/m 以上低減できます。

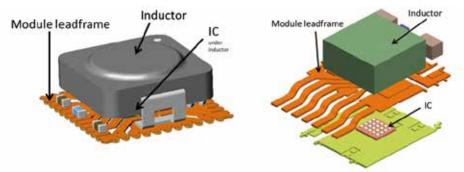

したがって、降圧コンバータまたは降圧電源モジュールの設計時には、入力コンデンサの配置は最初の考慮事項の1つとする必要があります。また、電源モジュールを使用すると、インダクタとICの間のクリティカルなループ領域が既に最適化されているという利点があります。インダクタはパッケージ内部で集積回路と接続されています(図7を参照)。この配置により、パッケージ内部のループ領域が非常に小さくなります。そのため、ノイズの多いスイッチ・ノードをプリント基板上で配線する必要がありません。

図 6. LMR23630 コンバータの入力コンデンサの配置が放射 EMI に与える影響。

図7. 異なる種類の電源モジュールの内部構成。いずれの場合も、インダクタが IC ダイの上に配置される。

電源モジュールで使用されるほとんどのインダクタは、コイルからの電磁放射を防ぐために追加の遮蔽が施されています。インダクタがリード・フレームの上に配置されることで、高い電流および電圧遷移はインダクタの非常に近くで生じ、スイッチ・ノードからの電磁場の一部が遮蔽されます(**図7**を参照)。

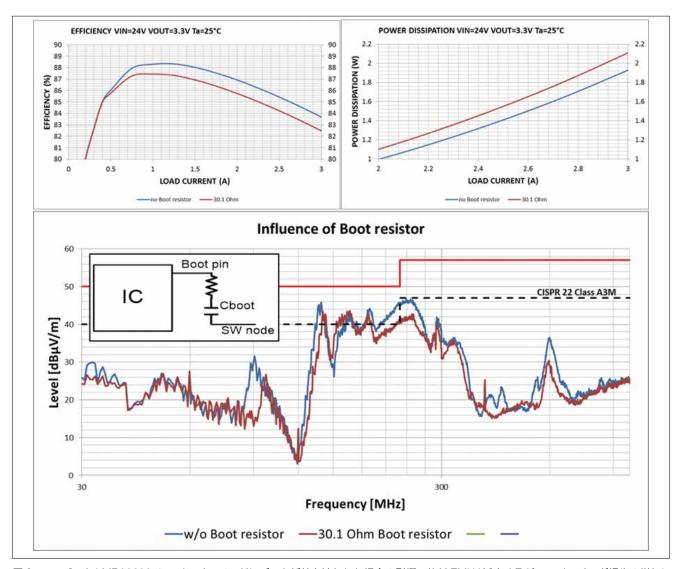

# 高速の過渡電圧および電流

高速の過渡事象はスイッチ・ノード上にリンギングを引き起こす場合があり、EMIの要因となります。一部のコンバータは、ブート・ピンへのアクセスを提供しています。ブート・コンデンサと直列に抵抗を配置すると、立ち上がり時間(dt)が増加し、EMIを低減できますが、効率は低下します。

図8に、LMR23630 EVMのEMI放射スキャンを示します。 レイアウトは入力コンデンサをピンから2.5cm離して配置する よう変更されています。これは、悪いレイアウトをシミュレー トし、ブート・コンデンサの配置が EMI性能にどのような影響を与えるかを示すためです。レイアウトを完全に変更するよりも、設計で追加のブート・コンデンサを配置する方が簡単かもしれません。設計では、必要になった場合に備えて、ブート・コンデンサの配置をあらかじめ計画しておくことをお勧めします。計画していなかった場合は、PCB上のスペースを $0\Omega$ 抵抗で短絡できます。

ブート・コンデンサと直列にブート抵抗を配置すると、EMI のスペクトルが低くなります。いくつかの周波数領域での放射は最大6dB低下します。図8は、効率に関するトレードオフも示しています。30.1Ωの抵抗で立ち上がり時間はを遅くすると、効率が1%以上低下します。電力損失に目を向けると、さらにわかりやすくなります。電力損失は全負荷(3A)に対して1.9Wから2.1Wまで増加します。この10%を超える増加は無視できず、熱に関する問題につながります。

**図 8.** コンバータ LMR23630 のスイッチ・ノードにブート抵抗を追加した場合の影響。放射 EMI は減少するが、スイッチング損失の増加により効率は低下。

同期コンバータでのスイッチ・ノード電流のリンギングdlは、スイッチ・ノード・ピンとグランド・ピンの間に小さなショットキー・ダイオードを配置して逆方向回復電流を下げることにより低減できますが、BOM(部品表)コストが上昇します。または、スイッチ・ノードとグランドの間に、追加の大きなパッケージ容量と抵抗を含むスナバ回路を追加することもできます。このスナバによってスイッチ・ノード・リンギングのエネルギーが消費されますが、これにはリンギング周波数の知識と、追加部品の適切な計算が必要になります。また、スイッチング電源の効率も低下します。

# 電流パスの寄生インダクタンスおよび容量

同期降圧コンバータでは、放射EMIとして現れるノイズの大きさがICアーキテクチャによって異なります。しかし、これをデータシートから読み取ることは困難です。EMI特性はPCBレイアウト、BOMコンポーネント、およびその他の要素によって影響を受けるため、ほとんどのデータシートにはEMIプロットが記載されていません。ときに、運がよければ、EVMのユーザー・ガイドにこの特定の設計でのEMI特性の

プロットが記載されている場合もあります。しかし、設計がEVMのレイアウトやBOMと一致していなければ、アプリケーションのEMI特性は大幅に異なる可能性があります。電源モジュールはレイアウトを単純化し、すばやく簡単な設計を可能にします。これは、いくつかの経験則だけを考慮すればよいためです。たとえば、グランド・プレーン上のパターンや切り込みは最小限に抑えます。それらが必要な場合は、電流の方向と並列になるよう設計します(図9)。

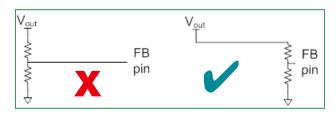

# ノイズに敏感なノードをノイズの多いノードから保護

ノイズに敏感なノードはできる限り短くし、ノイズの多いノードから離して配置します。たとえば、分圧抵抗回路からフィードバック (FB) ピンまでのパターンが長いと、アンテナとして機能し、放射された電磁外乱からのノイズを拾ってしまいます(図10)。このノイズはFBピンに注入され、出力に追加のノイズを生じるだけでなく、デバイスが不安定になる場合もあります。スイッチング降圧レギュレータのレイアウトを設計する際には、これらすべてを考慮することが課題となります。

図9. PCB上の切り込みやパターンは電流の流れに影響し、放射 EMI にも影響を与える。

| ノイズに敏感なノード | ノイズの多いノード   |

|------------|-------------|

| フィードバック・ピン | スイッチ・ノード    |

| 周波数設定      | インダクタ       |

| 補償回路       | 高dl/dtコンデンサ |

| センシング・パスなど | FET、ダイオードなど |

**表 1.** 降圧コンバータのノイズに敏感なノードとノイズの多いノードの例。

**図 10.** FB ピンの分圧抵抗は常に FB ピンにできる限り近づけて配置する。

モジュールには、ノイズに敏感なノードとノイズの多いノードの両方を最小限に抑えるという利点があるため、誤ったレイアウトを選択する可能性が低くなります。唯一の注意点は、FBピンのパターンを短く保つことです。

#### 結論

スイッチング降圧コンバータでEMIを調整する方法はいろいろあり、以下のベスト・プラクティスだけでは十分ではないかもしれません。最良の構成を見つけるには、貴重な設計時間を多く費やすことになります。電源モジュールには既にFETとインダクタの両方が含まれているため、良好なEMI性能を持つ電源設計を簡単かつ迅速に作成し完成させることができます。降圧モジュールの設計時に最も重要なポイントは、EMI性能を大きく改善する可能性のあるいくつかの外部部品の配置です。

# コンバータと電源モジュールのEMIの比較

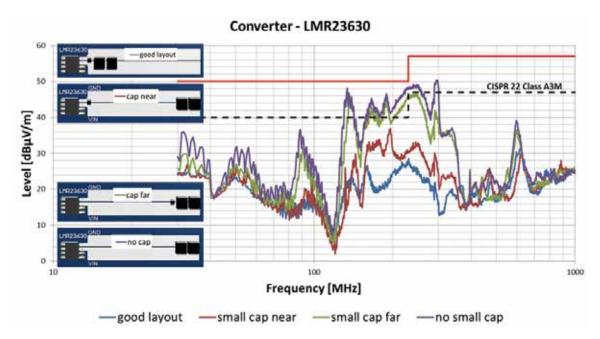

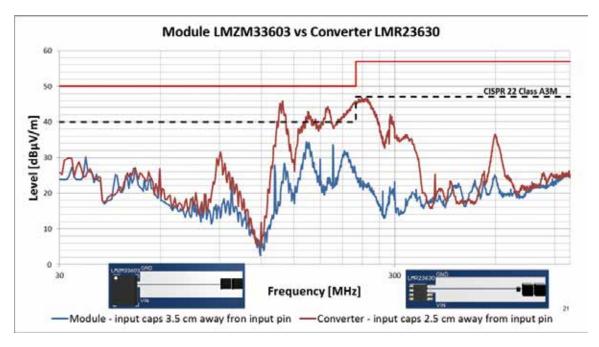

記事の前半で、スイッチング電源でのEMIの発生要因とその 低減方法について述べました。ここでは、同じ集積回路(IC) を使用するコンバータと電源モジュールの間で測定値を比較することにより、モジュールが放射EMIの低減にどのように役立つかを示します。コンバータはLMR23630、電源モジュールはLMZM33603であり、これらはともにTIのSIMPLE SWITCHER製品で、LMR23630 ICを使用しています。結果が選択した部品(コンバータまたは電源モジュール)とレイアウトのみに基づくように、BOMの部品数が同じになるよう両方のデバイスのEVMに一部変更を加えています。どちらのEVMも、良好な最適化されたレイアウトとなっています。後から、コンデンサを入力ピンから離して配置することにより、レイアウトを悪化させました。

# LMR23630コンバータの性能

図11に、異なる設計レイアウトでの4つの異なるEMIスペクトルを示しています。設計は1段階ごとに悪くなっています(図5と同様ですが、段階的に行っています)。最初の測定(good layout/青色の線)は、レイアウトに変更を加えていないEVMによるものです(すべての入力コンデンサが入力ピンの非常に近くに配置されている良いレイアウト)。2番目の測定(small cap near/赤色の線)では、2個の $4.7\mu$  Fコンデンサを入力ピンから2.5cm離して配置しています。小さな0.22 $\mu$  Fコンデンサは入力ピンに近づけたままです。3番目(small cap far/緑色の線)と4番目(no small cap/紫色の線)の測定は、それぞれ小さなコンデンサを入力ピンから2.5cm離した場合と、完全に除去した場合です。

図11から、入力コンデンサの配置が非常に重要であることがわかります。小さな入力コンデンサを入力ピンから遠ざけるか完全に除去すると、CISPR 22 Class A3Mに違反します。小さなコンデンサを入力ピンの近くに配置すると、高周波数のループ領域が最小化されます。小さなコンデンサが高周波数をフィルタリングする一方、大容量のコンデンサは低周波数ノイズをフィルタリングします。

電源モジュールでは通常、小さな入力コンデンサがパッケージ内に含まれています。レイアウトを悪化させたときの電源 モジュールの性能を見てみましょう。

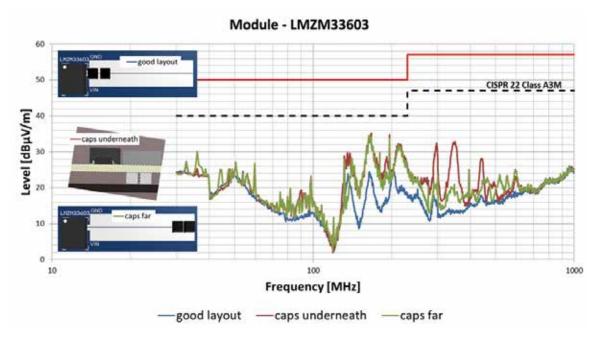

# LMZM33603電源モジュールの性能

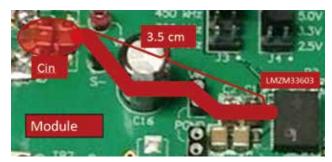

図12は電源モジュールのEVMレイアウトを示し、やはり段階的に悪化させています。青色の線は、変更を加えていないEVMでの放射EMIを示しています。赤色と緑色の線は

悪いレイアウトを示し、一方は2個の4.7μF入力コンデンサを PCBの裏側に配置しています(赤色の線)。緑色の線の方は、コンデンサが入力ピンから約3.5cm離して配置されています (図13の赤色の楕円形)。図13の赤色の太い線は、変更されたEVMと、VIN、入力コンデンサ、およびグランドの間で形成されるクリティカルなループ領域を示しています。EMI性能は悪化しますが、CISPR 22 Class A3Mの基準には違反していません。

2018

図 11. 異なる入力容量配置でのコンバータ LMR23630 の放射 EMI。

図 12. TIの LMZM33603 電源モジュールの放射 EMI 性能。

**図 13.** TI の LMZM33603 電源モジュールに対する悪いレイアウトの例。

# 電源モジュールはレイアウト設計エラーを許容

図14は、コンバータLMR23630(赤色の線)と電源モジュールLMZM33603(青色の線)を1つのグラフで比較したものです。いずれも、すべての外部入力コンデンサを入力ピンから遠ざけた悪いレイアウトの場合です。

電源モジュールLMZM33603の方がコンバータLMR23630 よりも放射EMI性能が優れていることは明らかです。いず れのレイアウトも完全ではありませんが、電源モジュールは CISPRテストに合格し、コンバータは不合格となるでしょう。

#### 結論

前に述べたとおり、スイッチング電源に対して良好なレイアウト設計を作成することは簡単ではありません。経験を積んだエンジニアであっても、入力コンデンサの不完全な配置などのエラーを簡単に犯しがちです。

電源モジュールは、設計レイアウトのエラーに対する許容度を高めます。EMI性能の基準を満たし、設計時間に関して効率性を高めることが必須である場合には、これはスイッチング電源に対する優れた選択肢となります。

EMI低減のための優れたレイアウト作成に関してさらに詳しく知りたい方には、アプリケーション・レポート "AN-2155 Layout Tips for EMI Reduction in DC/DC Converters" および "AN-643 EMI/RFI Board Design" をお勧めします。

**図 14.** コンバータ LMR23630 と電源モジュール LMZM33603 (いずれも TI 製) の EMI 性能の比較。

## S-0107

ご注意:

本資料に記載された製品・サービスにつきましては予告なしにご提供 の中止または仕様の変更をする場合がありますので、本資料に記載さ れた情報が最新のものであることをご確認の上ご注文下さいますよう お願い敬します。

TIは製品の使用用途に関する援助、お客様の製品もしくはその設計、ソフトウェアの性能、または特許侵害に対して責任を負うものではありません。また、他社の製品・サービスに関する情報を記載していても、TIがその他社製品を承認あるいは保証することにはなりません。

#### TIの設計情報およびリソースに関する重要な注意事項

Texas Instruments Incorporated ("TI")の技術、アプリケーションその他設計に関する助言、サービスまたは情報は、TI製品を組み込んだアプリケーションを開発する設計者に役立つことを目的として提供するものです。これにはリファレンス設計や、評価モジュールに関係する資料が含まれますが、これらに限られません。以下、これらを総称して「TIリソース」と呼びます。いかなる方法であっても、TIリソースのいずれかをダウンロード、アクセス、または使用した場合、お客様(個人、または会社を代表している場合にはお客様の会社)は、これらのリソースをここに記載された目的にのみ使用し、この注意事項の条項に従うことに合意したものとします。

TIによるTIリソースの提供は、TI製品に対する該当の発行済み保証事項または免責事項を拡張またはいかなる形でも変更するものではなく、これらのTIリソースを提供することによって、TIにはいかなる追加義務も責任も発生しないものとします。TIは、自社のTIリソースに訂正、拡張、改良、およびその他の変更を加える権利を留保します。

お客様は、自らのアプリケーションの設計において、ご自身が独自に分析、評価、判断を行う責任がお客様にあり、お客様のアプリケーション(および、お客様のアプリケーションに使用されるすべてのTI製品)の安全性、および該当するすべての規制、法、その他適用される要件への遵守を保証するすべての責任をお客様のみが負うことを理解し、合意するものとします。お客様は、自身のアプリケーションに関して、(1) 故障による危険な結果を予測し、(2) 障害とその結果を監視し、および、(3) 損害を引き起こす障害の可能性を減らし、適切な対策を行う目的での、安全策を開発し実装するために必要な、すべての技術を保持していることを表明するものとします。お客様は、TI製品を含むアプリケーションを使用または配布する前に、それらのアプリケーション、およびアプリケーションに使用されているTI製品の機能性を完全にテストすることに合意するものとします。TIは、特定のTIリソース用に発行されたドキュメントで明示的に記載されているもの以外のテストを実行していません。

お客様は、個別のTIリソースにつき、当該TIリソースに記載されているTI製品を含むアプリケーションの開発に関連する目的でのみ、使用、コピー、変更することが許可されています。明示的または黙示的を問わず、禁反言の法理その他どのような理由でも、他のTIの知的所有権に対するその他のライセンスは付与されません。また、TIまたは他のいかなる第三者のテクノロジまたは知的所有権についても、いかなるライセンスも付与されるものではありません。付与されないものには、TI製品またはサービスが使用される組み合わせ、機械、プロセスに関連する特許権、著作権、回路配置利用権、その他の知的所有権が含まれますが、これらに限られません。第三者の製品やサービスに関する、またはそれらを参照する情報は、そのような製品またはサービスを利用するライセンスを構成するものではなく、それらに対する関係証または推奨を意味するものでもありません。TIリソースを使用するため、第三者の特許または他の知的所有権に基づく第三者からのライセンス、もしくは、TIの特許または他の知的所有権に基づくTIからのライセンスが必要な場合があります。

TIのリソースは、それに含まれるあらゆる欠陥も含めて、「現状のまま」提供されます。TIは、TIリソースまたはその仕様に関して、明示 的か暗黙的かにかかわらず、他のいかなる保証または表明も行いません。これには、正確性または完全性、権原、続発性の障害に関する保 証、および商品性、特定目的への適合性、第三者の知的所有権の非侵害に対する黙示の保証が含まれますが、これらに限られません。

TIは、いかなる苦情に対しても、お客様への弁護または補償を行う義務はなく、行わないものとします。これには、任意の製品の組み合わせに関連する、またはそれらに基づく侵害の請求も含まれますが、これらに限られず、またその事実についてTIリソースまたは他の場所に記載されているか否かを問わないものとします。いかなる場合も、TIリソースまたはその使用に関連して、またはそれらにより発生した、実際的、直接的、特別、付随的、間接的、懲罰的、偶発的、または、結果的な損害について、そのような損害の可能性についてTIが知らされていたかどうかにかかわらず、TIは責任を負わないものとします。

お客様は、この注意事項の条件および条項に従わなかったために発生した、いかなる損害、コスト、損失、責任からも、TIおよびその代表者を完全に免責するものとします。

この注意事項はTIリソースに適用されます。特定の種類の資料、TI製品、およびサービスの使用および購入については、追加条項が適用されます。これには、半導体製品(http://www.ti.com/sc/docs/stdterms.htm)、評価モジュール、およびサンプル(http://www.ti.com/sc/docs/sampterms.htm)についてのTIの標準条項が含まれますが、これらに限られません。

Copyright © 2018, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社