SLVS072C - DECEMBER 1992 - REVISED OCTOBER 1995

#### available features **PW PACKAGE** (TOP VIEW) Fully Integrated 9-Channel SCSI **Termination** 01 TERMPWR □ 20 TERMPWR • **No External Components Required** NC 2 19 3 NC 18 ── NC Maximum Allowed Current Applied at First 4 **High-Level Step** D0 17 💷 D8 5 16 🖵 D7 D1 6-pF Typical Power-Down Output • 6 15 D2 Capacitance D3 7 14 ⊥ D6 • Wide V<sub>term</sub><sup>†</sup> (Termination Voltage) 8 13 D4 💷 D5 Operating Range, 3.5 V to 5.5 V 9 12 NC **TTL-Compatible Disable Feature** 10 11 GND I GND **Compatible With Active Negation** NC - No internal connection **Thermal Regulation**

#### description

The TL2218-285 is a current-mode 9-channel monolithic terminator specially designed for single-ended small-computer-systems-interface (SCSI) bus termination. A user-controlled disable function is provided to reduce standby power. No impedance-matching resistors or other external components are required for its operation as a complete terminator.

The device operates over a wide termination-voltage ( $V_{term}^{\dagger}$ ) range of 3.5 V to 5.5 V, offering an extra 0.5 V of operating range when compared to the minimum termination voltage of 4 V required by other integrated active terminators. The TL2218-285 functions as a current-sourcing terminator and supplies a constant output current of 23 mA into each asserted line. When a line is deasserted, the device senses the rising voltage level and begins to function as a voltage source, supplying a fixed output voltage of 2.85 V. The TL2218-285 features compatibility with active negation drivers and has a typical sink current capability of 20 mA.

The TL2218-285 is able to ensure that maximum current is applied at the first high-level step. This performance means that the device should provide a first high-level step exceeding 2 V even at a 10-MHz rate. Therefore, noise margins are improved considerably above those provided by resistive terminators.

A key difference between the TL2218-285 current-mode terminator and a Boulay terminator is that the TL2218-285 does not incorporate a low dropout regulator to set the output voltage to 2.85 V. In contrast with the Boulay termination concept, the accuracy of the 2.85 V is not critical with the current-mode method used in the TL2218-285 because this voltage does not determine the driver current. Therefore, the primary device specifications are not the same as with a voltage regulator but are more concerned with output current.

The DISABLE terminal is TTL compatible and must be taken low to shut down the outputs. The device is normally active, even when DISABLE is left floating. In the disable mode, only the device startup circuits remain active, thereby reducing the supply current to just 500 µA. Output capacitance in the shutdown mode is typically 6 pF.

The TL2218-285 has on-board thermal regulation and current limiting, thus eliminating the need for external protection circuitry. A thermal regulation circuit that is designed to provide current limiting, rather than an actual thermal shutdown, is included in the individual channels of the TL2218-285. When a system fault occurs that leads to excessive power dissipation by the terminator, the thermal regulation circuit causes a reduction in the asserted-line output current sufficient to maintain operation. This feature allows the bus to remain active during a fault condition, which permits data transfer immediately upon removal of the fault. A terminator with thermal shutdown does not allow for data transfer until sufficient cooling has occurred. Another advantage offered by the TL2218-285 is a design that does not require costly laser trimming in the manufacturing process.

The TL2218-285 is characterized for operation over the virtual junction temperature range of 0°C to 125°C.

<sup>†</sup> This symbol is not presently listed within EIA/JEDEC standards for letter symbols.

Copyright  $\ensuremath{\textcircled{O}}$  1995, Texas Instruments Incorporated

SLVS072C - DECEMBER 1992 - REVISED OCTOBER 1995

| AVAILABLE OPTIONS                                                        |                                    |                  |  |  |  |  |  |  |

|--------------------------------------------------------------------------|------------------------------------|------------------|--|--|--|--|--|--|

| Tj                                                                       | SURFACE MOUNT<br>(PW) <sup>†</sup> | CHIP FORM<br>(Y) |  |  |  |  |  |  |

| 0°C to 125°C                                                             | TL2218-285PWLE                     | TL2218-285Y      |  |  |  |  |  |  |

| <sup>†</sup> The PW package is only available left-end taped and reeled. |                                    |                  |  |  |  |  |  |  |

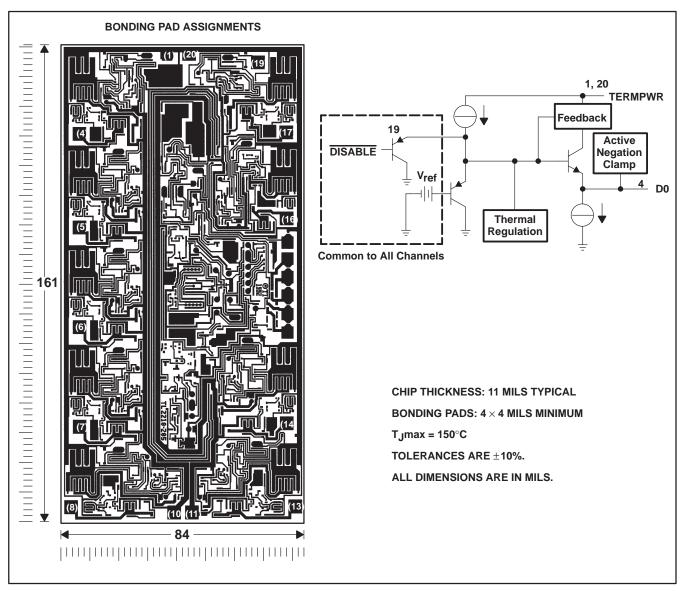

#### TL2218-285Y chip information

This chip, when properly assembled, displays characteristics similar to the TL2218-285. Thermal compression or ultrasonic bonding may be used on the doped aluminum bonding pads. The chip may be mounted with conductive epoxy or a gold-silicon preform.

SLVS072C - DECEMBER 1992 - REVISED OCTOBER 1995

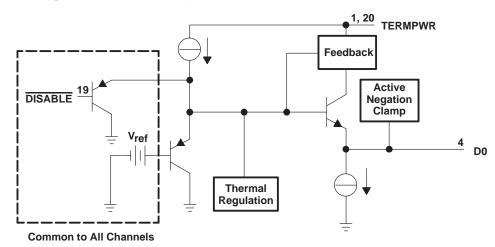

#### functional block diagram (each channel)

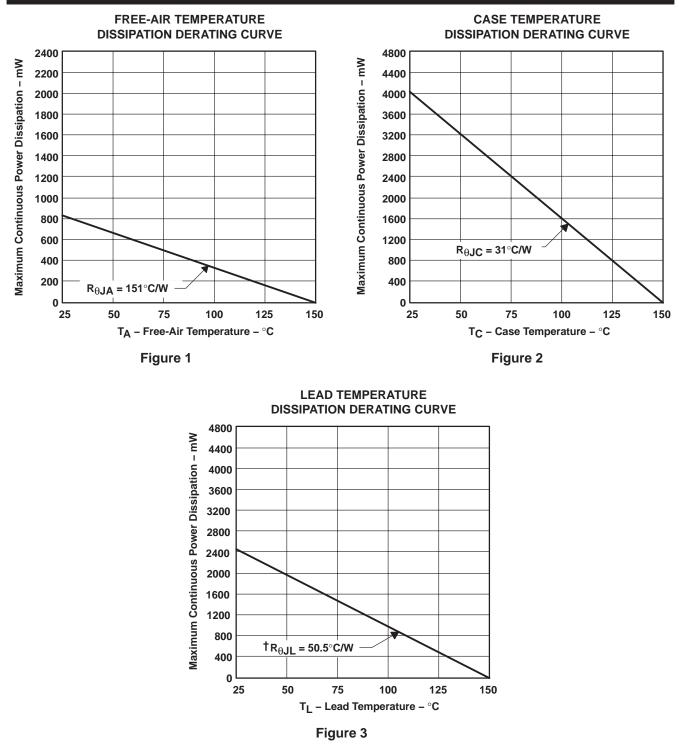

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted) (see Figures 1, 2, and 3)<sup>†</sup>

| Continuous termination voltage                               | 10 V                         |

|--------------------------------------------------------------|------------------------------|

| Continuous output voltage range                              | 0 V to 5.5 V                 |

| Continuous disable voltage range                             | 0 V to 5.5 V                 |

| Continuous total power dissipation                           | See Dissipation Rating Table |

| Operating virtual junction temperature range, T <sub>J</sub> | –55°C to 150°C               |

| Storage temperature range, T <sub>stg</sub>                  | –60°C to 150°C               |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### DISSIPATION RATING TABLE

| PACKAGE | POWER RATING<br>AT | $\textbf{T} \leq \textbf{25}^\circ \textbf{C}$ POWER RATING | DERATING FACTOR<br>ABOVE T = 25°C | T = 70°C<br>POWER RATING | T = 85°C<br>POWER RATING | T = 125°C<br>POWER RATING |

|---------|--------------------|-------------------------------------------------------------|-----------------------------------|--------------------------|--------------------------|---------------------------|

|         | TA                 | 828 mW                                                      | 6.62 mW/°C                        | 530 mW                   | 430 mW                   | 166 mW                    |

| PW      | т <sub>С</sub>     | 4032 mW                                                     | 32.2 mW/°C                        | 2583 mW                  | 2100 mW                  | 812 mW                    |

|         | τ <sub>L</sub> ‡   | 2475 mW                                                     | 19.8 mW/°C                        | 1584 mW                  | 1287 mW                  | 495 mW                    |

$R_{\theta,JL}$  is the thermal resistance between the junction and device lead. To determine the virtual junction temperature (T<sub>J</sub>) relative to the device lead temperature, the following calculations should be used: T<sub>J</sub> = P<sub>D</sub> x R<sub> $\theta,JL</sub> + T<sub>L</sub>, where P<sub>D</sub> is the internal power dissipation of the device and T<sub>L</sub> is the device lead temperature at the point of contact to the printed wiring board. R<sub><math>\theta,JL</sub> is 50.5^{\circ}C/W$ .</sub></sub>

SLVS072C - DECEMBER 1992 - REVISED OCTOBER 1995

<sup>†</sup>  $R_{\theta JL}$  is the thermal resistance between the junction and device lead. To determine the virtual junction temperature (T<sub>J</sub>) relative to the device lead temperature, the following calculations should be used:  $T_J = P_D \times R_{\theta JL} + T_L$ , where  $P_D$  is the internal power dissipation of the device, and  $T_L$  is the device lead temperature at the point of contact to the printed wiring board.  $R_{\theta JL}$  is 50.5°C/W.

SLVS072C - DECEMBER 1992 - REVISED OCTOBER 1995

#### recommended operating conditions

|                                            | MIN | MAX               | UNIT |

|--------------------------------------------|-----|-------------------|------|

| Termination voltage                        | 3.5 | 5.5               | V    |

| High-level disable input voltage, VIH      | 2   | V <sub>term</sub> | V    |

| Low-level disable input voltage, VIL       | 0   | 0.8               | V    |

| Operating virtual junction temperature, TJ | 0   | 125               | °C   |

#### electrical characteristics, V<sub>term</sub> = 4.75 V, V<sub>O</sub> = 0.5 V, T<sub>J</sub> = 25°C

| PARAMETER                           | TEST CONDITIONS             | MIN   | TYP  | MAX | UNIT |  |

|-------------------------------------|-----------------------------|-------|------|-----|------|--|

| Output high voltage                 |                             | 2.5   | 2.85 |     | V    |  |

|                                     | All data lines open         |       | 9    |     |      |  |

| TERMPWR supply current              | All data lines = 0.5 V      |       | 228  |     | mA   |  |

|                                     | DISABLE = 0 V               |       | 500  |     | μΑ   |  |

| Output current                      |                             | -20.5 | -23  | -24 | mA   |  |

| Disable issue (con Note 4)          | DISABLE = 4.75 V            |       |      | 1   | •    |  |

| Disable input current (see Note 1)  | DISABLE = 0 V               |       |      | 600 | μA   |  |

| Output leakage current              | DISABLE = 0 V               |       | 100  |     | nA   |  |

| Output capacitance, device disabled | V <sub>O</sub> = 0 V, 1 MHz |       | 6    |     | pF   |  |

| Termination sink current, total     | $V_{O} = 4 V$               |       | 20   |     | mA   |  |

NOTE 1: When DISABLE is open or high, the terminator is active.

SLVS072C - DECEMBER 1992 - REVISED OCTOBER 1995

#### THERMAL INFORMATION

The need for smaller surface-mount packages for use on compact printed-wiring boards (PWB) causes an increasingly difficult problem in the area of thermal dissipation. In order to provide the systems designer with a better approximation of the junction temperature rise in the thin-shrink small-outline package (TSSOP), the junction-to-lead thermal resistance ( $R_{\theta JL}$ ) is provided along with the more typical values of junction-to-ambient and junction-to-case thermal resistances,  $R_{\theta JA}$  and  $R_{\theta JC}$ .

$R_{\theta JL}$  is used to calculate the device junction temperature rise measured from the leads of the unit. Consequently, the junction temperature is dependent upon the board temperature at the leads,  $R_{\theta JL}$ , and the internal power dissipation of the device. The board temperature is contingent upon several variables, including device packing density, thickness, material, area, and number of interconnects. The  $R_{\theta JL}$  value depends on the number of leads connecting to the die-mount pad, the lead-frame alloy, area of the die, mount material, and mold compound. Since the power level at which the TSSOP can be used is highly dependent upon both the temperature rise of the PWB and the device itself, the systems designer can maximize this level by optimizing the circuit board. The junction temperature of the device can be calculated using the equation  $T_J = (P_D \times R_{\theta JL}) + T_L$  where  $T_J =$  junction temperature,  $P_D =$  power dissipation,  $R_{\theta JL} =$  junction-to-lead thermal resistance, and  $T_L =$  board temperature at the leads of the unit.

The values of thermal resistance for the TL2218-285 PW are as follows:

| Thermal Resistance    | <b>Typical Junction Rise</b> |

|-----------------------|------------------------------|

| $R_{	extsf{	heta}JA}$ | 151°C/W                      |

| $R_{	extsf{	heta}JC}$ | 31 °C/W                      |

| $R_{	ext{	heta}JL}$   | 50.5°C/W                     |

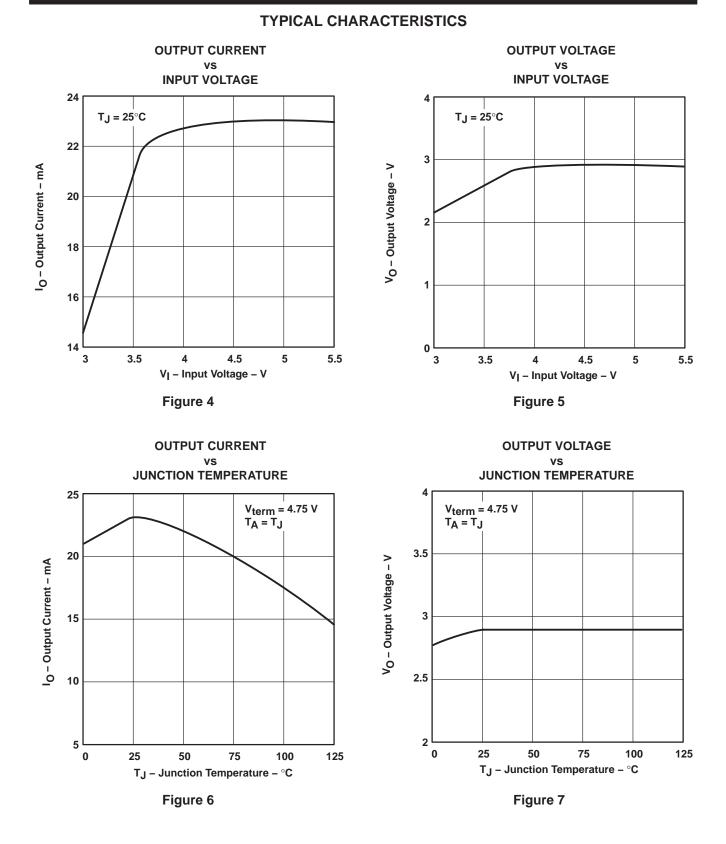

#### **TYPICAL CHARACTERISTICS**

|    |                | -                       | FIGURE |

|----|----------------|-------------------------|--------|

| IO | Output current | vs Input voltage        | 4      |

| VO | Output voltage | vs Input voltage        | 5      |

| IO | Output current | vs Junction temperature | 6      |

| VO | Output voltage | vs Junction temperature | 7      |

#### **Table of Graphs**

SLVS072C - DECEMBER 1992 - REVISED OCTOBER 1995

#### **PACKAGING INFORMATION**

| Orderable part number | Status   | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|----------|---------------|-----------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)      | (2)           |                 |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |          |               |                 |                       |      | (4)           | (5)                |              |              |

| TL2218-285PW          | Last     | Production    | TSSOP (PW)   20 | 70   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | 0 to 125     | 2218285      |

|                       | Time Buy |               | . ,.            |                       |      |               |                    |              |              |

| TL2218-285PW.A        | NRND     | Production    | TSSOP (PW)   20 | 70   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | 0 to 125     | 2218285      |

| TL2218-285PWR         | Last     | Production    | TSSOP (PW)   20 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | 0 to 125     | 2218285      |

|                       | Time Buy |               |                 |                       |      |               |                    |              |              |

| TL2218-285PWR.A       | NRND     | Production    | TSSOP (PW)   20 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | 0 to 125     | 2218285      |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

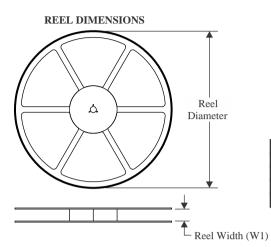

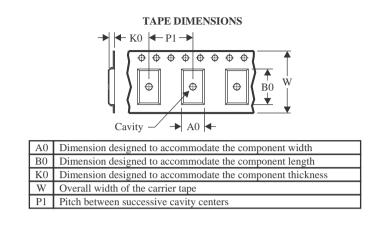

#### TAPE AND REEL INFORMATION

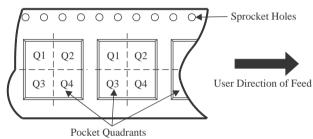

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TL2218-285PWR | TSSOP           | PW                 | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.0        | 1.4        | 8.0        | 16.0      | Q1               |

www.ti.com

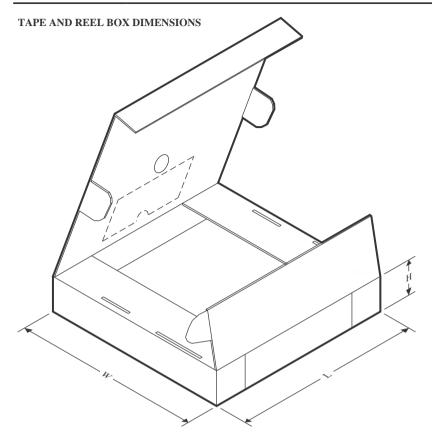

# PACKAGE MATERIALS INFORMATION

24-Jul-2025

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TL2218-285PWR | TSSOP        | PW              | 20   | 2000 | 353.0       | 353.0      | 32.0        |

#### TEXAS INSTRUMENTS

www.ti.com

24-Jul-2025

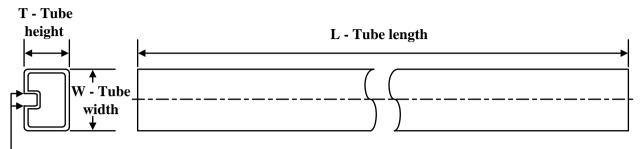

#### TUBE

### - B - Alignment groove width

\*All dimensions are nominal

| Device         | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|----------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TL2218-285PW   | PW           | TSSOP        | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TL2218-285PW.A | PW           | TSSOP        | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated