SLUS896A-AUGUST 2009-REVISED AUGUST 2009

# CURRENT MODE PWM CONTROLLER (KNOWN GOOD DIE)

### FEATURES

- -55°C to 125°C Known Good Die

- Controlled Baseline

- Optimized For Off-line and DC-to-DC Converters

- Low Start-Up Current (<1 mA)

- Automatic Feed Forward Compensation

- Pulse-by-Pulse Current Limiting

- Enhanced Load Response Characteristics

- Under-Voltage Lockout With Hysteresis

- Double Pulse Suppression

- High Current Totem Pole Output

- Internally Trimmed Bandgap Reference

- 500-kHz Operation

- Low R<sub>o</sub> Error Amp

### DESCRIPTION

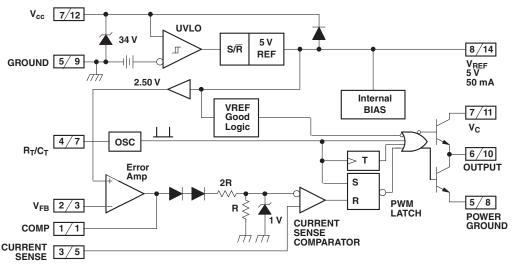

The UC1843 family of control devices provides the necessary features to implement off-line or dc-to-dc fixed frequency current mode control schemes with a minimal external parts count. Internally implemented circuits include under-voltage lockout featuring start up current less than 1 mA, a precision reference trimmed for accuracy at the error amp input, logic to insure latched operation, a PWM comparator which also provides current limit control, and a totem pole output stage designed to source or sink high peak current. The output stage, suitable for driving N-Channel MOSFETs, is low in the off state. The under-voltage lockout threshold is 8.4 V and maximum duty cycle range is around 100%.

### **BLOCK DIAGRAM**

Note 1: A/B A = DIL-8 Pin NumberB = SO-14 and CFP-14 Pin Number

#### **ORDERING INFORMATION**<sup>(1)</sup>

| T <sub>A</sub> | PACKAGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |  |

|----------------|------------------------|-----------------------|------------------|--|

| –55°C to 125°C | KGD                    | UC1843KGD1            | NA               |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

A

SLUS896A-AUGUST 2009-REVISED AUGUST 2009

www.ti.com

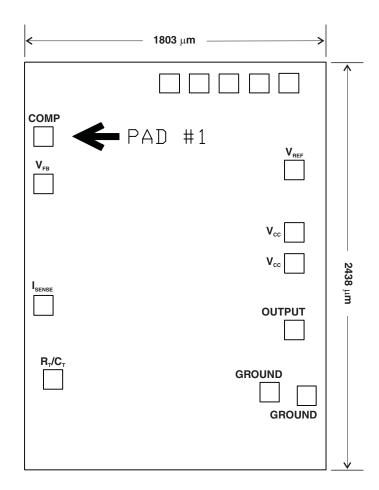

### BARE DIE INFORMATION

| DIE THICKNESS | BACKSIDE FINISH        | BACKSIDE<br>POTENTIAL | BOND PAD<br>METALLIZATION COMPOSITION |  |  |

|---------------|------------------------|-----------------------|---------------------------------------|--|--|

| 15 mils.      | Silicon with backgrind | GND                   | Al-Si-Cu (0.5%)                       |  |  |

|               | b                      | a c                   | _                                     |  |  |

# Origin

#### BOND PAD COORDINATES (in Mils)

| DESCRIPTION                    | PAD NUMBER | а     | b     | С     | d     |

|--------------------------------|------------|-------|-------|-------|-------|

| COMP                           | 1          | 78.70 | 63.40 | 82.90 | 67.60 |

| V <sub>FB</sub>                | 2          | 70.60 | 63.40 | 74.80 | 67.60 |

| I <sub>SENSE</sub>             | 3          | 39.40 | 63.40 | 43.60 | 67.60 |

| R <sub>T</sub> /C <sub>T</sub> | 4          | 18.60 | 61.20 | 22.60 | 65.60 |

| GROUND                         | 5          | 17.80 | 11.70 | 22.00 | 15.90 |

| GROUND                         | 6          | 17.40 | 3.90  | 21.80 | 8.10  |

| OUTPUT                         | 7          | 32.60 | 6.40  | 36.80 | 10.60 |

| V <sub>CC</sub>                | 8          | 47.50 | 6.40  | 51.70 | 10.60 |

| V <sub>CC</sub>                | 9          | 54.60 | 6.40  | 58.80 | 10.60 |

| V <sub>REF</sub>               | 10         | 68.70 | 6.40  | 72.90 | 10.60 |

| NC                             | TESTPAD    | 87.10 | 6.30  | 90.80 | 10.30 |

| NC                             | TESTPAD    | 87.10 | 12.60 | 90.80 | 16.60 |

| NC                             | TESTPAD    | 87.10 | 18.00 | 90.80 | 22.00 |

| NC                             | TESTPAD    | 87.10 | 24.30 | 90.80 | 28.30 |

| NC                             | TESTPAD    | 87.10 | 30.60 | 90.80 | 34.60 |

SLUS896A-AUGUST 2009-REVISED AUGUST 2009

### **ABSOLUTE MAXIMUM RATINGS**

|                                 |                         | UNIT            |  |

|---------------------------------|-------------------------|-----------------|--|

| Supply voltage                  | Low impedance source    | 30 V            |  |

|                                 | I <sub>CC</sub> < 30 mA | Self Limiting   |  |

| Output current                  | tput current            |                 |  |

| Output energy (capacitive load) |                         | 5 µJ            |  |

| Analog inputs (Pins 2, 3)       |                         | –0.3 V to 6.3 V |  |

| Error amp output sink current   |                         | 10 mA           |  |

| Storage temperature range       |                         | –65°C to 150°C  |  |

| Junction temperature range      |                         | –55°C to 150°C  |  |

### **ELECTRICAL CHARACTERISTICS**

SLUS896A-AUGUST 2009-REVISED AUGUST 2009

Unless otherwise stated, these specifications apply for  $-55^{\circ}C \le T_A \le 125^{\circ}C$ ;  $V_{CC} = 15 V^{(1)}$ ;  $R_T = 10 \text{ kW}$ ;  $C_T = 3.3 \text{ nF}$ ,  $T_A = T_J$ .

| PARAMETER              | TEST CONDITIONS                                                                                | MIN  | TYP  | MAX  | UNIT     |

|------------------------|------------------------------------------------------------------------------------------------|------|------|------|----------|

| REFERENCE SECTION      |                                                                                                | L    |      |      |          |

| Output Voltage         | $T_{\rm J} = 25^{\circ}$ C, $I_{\rm O} = 1$ mA                                                 | 4.95 | 5.00 | 5.05 | V        |

| Line Regulation        | 12 ≤ V <sub>IN</sub> ≤ 25 V                                                                    |      | 6    | 20   |          |

| Load Regulation        | $1 \le I_0 \le 20 \text{ mA}$                                                                  |      | 6    | 25   | mV       |

| Temperature Stability  | See <sup>(2)(3)</sup>                                                                          |      | 0.2  | 0.4  | mV/°C    |

| Total Output Variation | Line, load, tempature (2)                                                                      | 4.9  |      | 5.1  | V        |

| Output Noise Voltage   | 10 Hz≤ f ≤ 10 kHz, $T_J = 25^{\circ}C^{(2)}$                                                   |      | 50   |      | μV       |

| Long Term Stability    | T <sub>A</sub> = 125°C, 1000 Hrs <sup>(2)</sup>                                                |      | 5    | 25   | mV       |

| Output Short Circuit   |                                                                                                | -30  | -100 | -180 | mA       |

| OSCILLATOR SECTION     |                                                                                                |      |      | ·    |          |

| Initial Accuracy       | $T_{\rm J} = 25^{\circ} {\rm C}^{(4)}$                                                         | 47   | 52   | 57   | kHz      |

| Voltage Stability      | $12 \le V_{CC} \le 25 V$                                                                       |      | 0.2% | 1%   |          |

| Temperature Stability  | $T_{MIN} \le T_A \le T_{MAX}$ <sup>(2)</sup>                                                   |      | 5%   |      |          |

| Amplitude              | V <sub>PIN</sub> 4 peak-to-peak <sup>(2)</sup>                                                 |      | 1.7  |      | V        |

| ERROR AMP SECTION      |                                                                                                |      |      | ·    |          |

| Input Voltage          | V <sub>PIN 1</sub> = 2.5 V                                                                     | 2.45 | 2.50 | 2.55 | V        |

| Input Bias Current     |                                                                                                |      | -0.3 | -1   | μA       |

| A <sub>VOL</sub>       | $2 \le V_0 \le 4 V$                                                                            | 65   | 90   |      | dB       |

| Unity Gain Bandwidth   | $T_{\rm J} = 25^{\circ} C^{(2)}$                                                               | 0.7  | 1    |      | MHz      |

| PSRR                   | $12 \le V_{CC} \le 25 V$                                                                       | 60   | 70   |      | dB       |

| Output Sink Current    | V <sub>PIN 2</sub> = 2.7 V, V <sub>PIN 1</sub> = 1.1 V                                         | 2    | 6    |      |          |

| Output Source Current  | V <sub>PIN 2</sub> = 2.3 V, V <sub>PIN 1</sub> = 5 V                                           | -0.5 | -0.8 |      | mA       |

| V <sub>OUT</sub> High  | $V_{PIN 2}$ = 2.3 V, $R_L$ = 15 k $\Omega$ to ground                                           | 5    | 6    |      | V        |

| V <sub>OUT</sub> Low   | $V_{\text{PIN 2}} = 2.7 \text{ V}, \text{ R}_{\text{L}} = 15 \text{ k}\Omega \text{ to Pin 8}$ |      | 0.7  | 1.1  | v        |

| CURRENT SENSE SECTION  |                                                                                                |      |      | ·    |          |

| Gain                   | See <sup>(5)(6)</sup>                                                                          | 2.85 | 3    | 3.15 | V/V      |

| Maximum Input Signal   | $V_{PIN 1} = 5 V^{(5)}$                                                                        | 0.9  | 1    | 1.1  | V        |

| PSRR                   | $12 \le V_{CC} \le 25 \ V^{(2)(5)}$                                                            |      | 70   |      | dB       |

| Input Bias Current     |                                                                                                |      | -2   | -10  | μΑ       |

| Delay to Output        | $V_{PIN 3} = 0 V \text{ to } 2 V^{(2)}$                                                        |      | 150  | 300  | ns       |

| OUTPUT SECTION         |                                                                                                |      |      |      |          |

|                        | I <sub>SINK</sub> = 20 mA                                                                      |      | 0.1  | 0.4  |          |

| Output Low Level       | I <sub>SINK</sub> = 200 mA                                                                     |      | 1.5  | 2.2  | V        |

|                        | I <sub>SOURCE</sub> = 20 mA                                                                    | 13   | 13.5 |      | v        |

| Output High Level      | I <sub>SOURCE</sub> = 200 mA                                                                   |      | 13.5 |      |          |

| Rise Time              | $T_J = 25^{\circ}C, C_L = 1 \text{ nF}^{(2)}$                                                  |      | 50   | 150  | <b>F</b> |

| Fall Time              | $T_{J} = 25^{\circ}C, C_{L} = 1nF^{(2)}$                                                       |      | 50   | 150  | ns       |

Adjust  $V_{CC}$  above the start threshold before setting at 15 V. (1)

These parameters, although specified, are not 100% tested in production.

(2) (3) Temperature stability, sometimes referred to as average temperature coefficient, is described by the equation:

Temp Stability =

$$\frac{V_{REF}(max) - VREF(min)}{T_{REF}(max) - T_{REF}(min)}$$

The stability =  $\frac{1}{TJ(max) - TJ(min)} V_{REF(max)}$  and  $V_{REF(min)}$  are the maximum and minimum reference voltages measured over the appropriate temperature range. Note that the extremes in voltage do not necessarily occur at the extremes in temperature.

Output frequency equals oscillator frequency (4)

Parameter measured at trip point of latch with  $V_{PIN 2} = 0$ . (5) ).8 V

(6) Gain defined as:

$$A = \frac{\Delta V \Gamma I V T}{\Delta V P I N 3}, 0 \le V P I N 3 \le 0$$

### **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise stated, these specifications apply for  $-55^{\circ}C \le T_{A} \le 125^{\circ}C$ ;  $V_{CC} = 15$  V;  $R_{T} = 10$  kW;  $C_{T} = 3.3$  nF,  $T_{A} = T_{J}$ .

| PARAMETER                            | TEST CONDITIONS                               | MIN | TYP | MAX  | UNIT |

|--------------------------------------|-----------------------------------------------|-----|-----|------|------|

| UNDER-VOLTAGE LOCKOUT SECTION        | l l                                           |     |     |      |      |

| Start Threshold                      |                                               | 7.8 | 8.4 | 9.0  |      |

| Min. Operating Voltage After Turn On |                                               | 7.0 | 7.6 | 8.2  | V    |

| PWM SECTION                          |                                               |     |     |      |      |

| Maximum Duty Cycle                   |                                               | 95% | 97% | 100% |      |

| Minimum Duty Cycle                   |                                               |     |     | 0%   |      |

| TOTAL STANDBY CURRENT                |                                               |     |     |      |      |

| Start-Up Current                     |                                               |     | 0.5 | 1    |      |

| Operating Supply Current             | V <sub>PIN 2</sub> = V <sub>PIN 3</sub> = 0 V |     | 11  | 17   | mA   |

| V <sub>CC</sub> Zener Voltager       | I <sub>CC</sub> = 25 mA                       | 30  | 34  |      | V    |

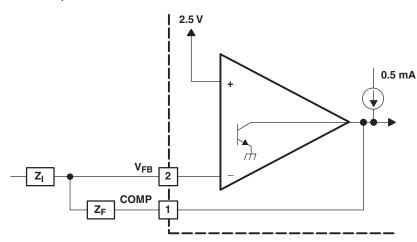

#### ERROR AMP CONFIGURATION

Error amp can source or sink up to 0.5 mA.

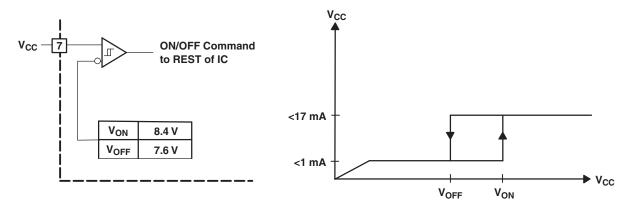

#### UNDER-VOLTAGE LOCKOUT

During under-voltage lock-out, the output drive is biased to sink minor amounts of current. Pin 6 should be shunted to ground with a bleeder resistor to prevent activating the power switch with extraneous leakage currents.

SLUS896A-AUGUST 2009-REVISED AUGUST 2009

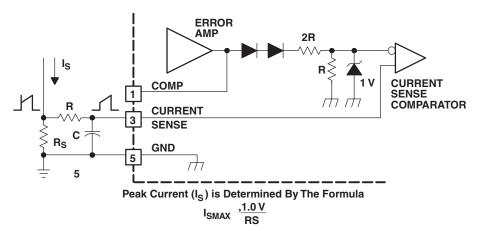

### **CURRENT SENSE CIRCUIT**

A small RC filter may be required to suppress switch transients.

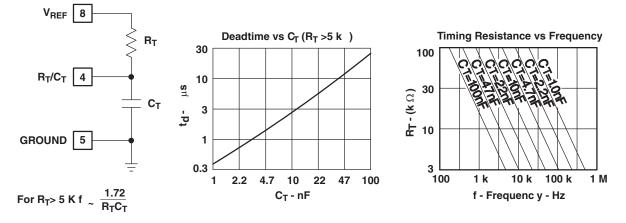

#### **OSCILLATOR SECTION**

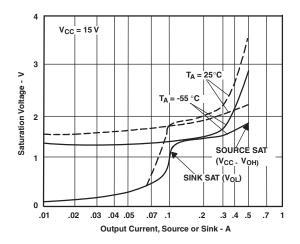

### **OUTPUT SATURATION CHARACTERISTICS**

Submit Documentation Feedback

SLUS896A-AUGUST 2009-REVISED AUGUST 2009

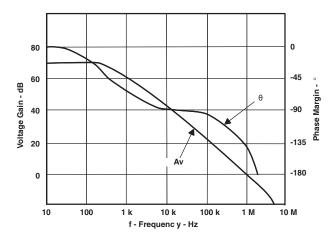

### ERROR AMPLIFIER OPEN-LOOP FREQUENCY RESPONSE

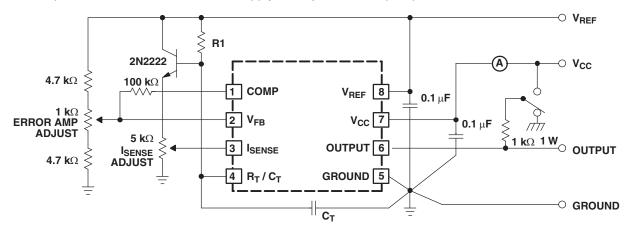

# **OPEN-LOOP LABORATORY FIXTURE**

High peak currents associated with capacitive loads necessitate careful grounding techniques. Timing and bypas capacitors should be conected close to pin 5 in a single point ground. The transistor and 5k potentiometer are used to sample the oscillator waveform and apply an adjustable ramp to pin 3.

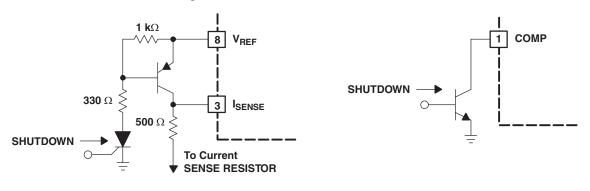

### SHUTDOWN TECHNIQUES

Shutdown of the UC1843 can be accomplished by two methods; either raise pin 3 above 1 V or pull pin 1 below a voltage two diode drops above ground. Either method causses the output of the PWM comparator to be high (refer to block diagram). The PWM latch is reset dominant so that the output will remain low until the next clock cycle after the shutdown condition at pin 1 and/or 3 is removed. In one example, an externally latched shutdown may be accomplished by adding an SCR which will be reset by cycling  $V_{CC}$  below the lower UVLO threshold. At this pint the reference turns off, allowing the SCR to reset.

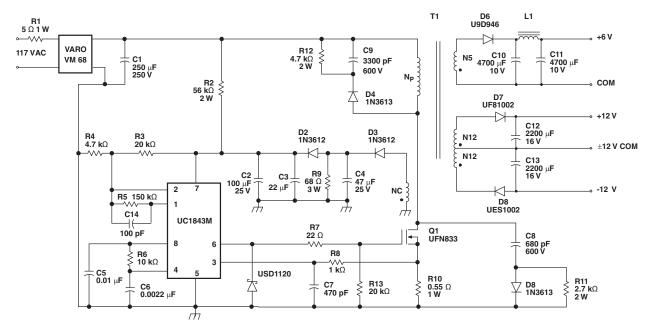

### **OFFLINE FLYBACK REGULATOR**

#### **Power Supply Specifications**

- 1. Input Voltages

- a. 5VAC to 130VA (50 Hz/60 Hz)

- 2. Line Isolation: 3750 V

- 3. Switchng Frequency: 40 kHz

- 4. Efficiency at Full Load 70%

- 5. Output Voltage:

- a. +5 V, ±5%; 1A to 4A load Ripple voltage: 50 mV P-P Max

- b. +12 V, ±3%; 0.1A to 0.3A load

Ripple voltage: 100 mV P-P Max

- c. -12 V, ±3%; 0.1A to 0.3A load Ripple voltage: 100 mV P-P Max

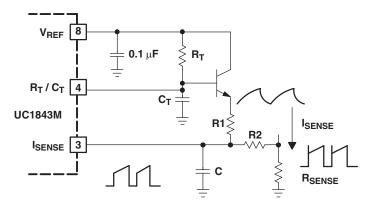

### **SLOPE COMPENSATION**

A fraction of the oscillator ramp can be resistively summed with the current sense signal to provide slope compensation for converters requiring duty cycles over 50%.

#### PACKAGING INFORMATION

| Orderable part number | Status<br>(1) | Material type (2) | Package   Pins  | Package qty   Carrier | <b>RoHS</b><br>(3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|-------------------|-----------------|-----------------------|--------------------|-------------------------------|----------------------------|--------------|---------------------|

|                       |               |                   |                 |                       |                    | (4)                           | (5)                        |              |                     |

| UC1843MKGD1           | Active        | Production        | XCEPT (KGD)   0 | 100   NOT REQUIRED    | Yes                | Call TI                       | N/A for Pkg Type           | -55 to 125   |                     |

| UC1843MKGD1.A         | Active        | Production        | XCEPT (KGD)   0 | 100   NOT REQUIRED    | Yes                | Call TI                       | N/A for Pkg Type           | -55 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF UC1843-HIREL :

Space : UC1843-SP

NOTE: Qualified Version Definitions:

• Space - Radiation tolerant, ceramic packaging and qualified for use in Space-based application

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated