**DS100RT410**

SNLS448A - JANUARY 2013-REVISED OCTOBER 2015

# DS100RT410 Low-Power 10-GbE Quad Channel Retimer

### **Features**

- Each Channel Independently Locks to 10.3125 Gbps

- Lock Operation (Typically Under 15 ms)

- Low Latency (≈300 ps)

- Adaptive Equalization up to 34-dB Boost at 5 GHz

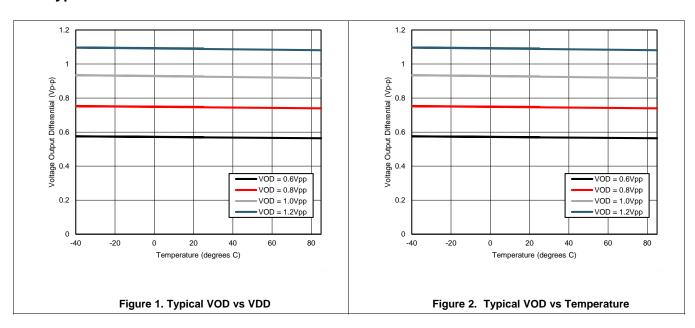

- Adjustable Transmit V<sub>OD</sub>: 600 to 1300 mVp-p

- Adjustable Transmit De-emphasis to -12 dB

- Typical Power Dissipation (EQ+CDR+DE): 150 mW/channel

- Programmable Output Polarity Inversion

- Input Signal Detection, CDR Lock Detection and Indicator

- On-chip Eye Monitor (EOM), PRBS Generator

- Single 2.5 V ±5% Power Supply

- SMBus and EEPROM Configuration Modes

- Operating Temperature Range of -40°C to 85°C

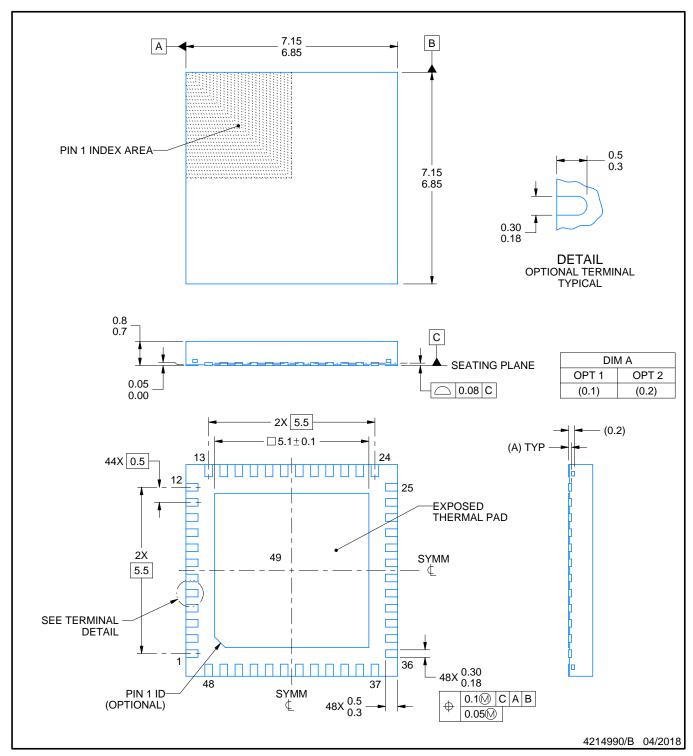

- WQFN 48-Pin, 7 mm x 7 mm Package

- Easy Pin Compatible Upgrade Between Repeater and Retimers

- DS100RT410 (EQ+CDR+DE): 10.3125 Gbps

- DS100DF410 (EQ+DFE+CDR+DE): 10.3125 Gbps

- DS110RT410 (EQ+CDR+DE): 8.5 to 11.3 Gbps

- DS110DF410 (EQ+DFE+CDR+DE): 8.5 to 11.3 Gbps

- DS125RT410 (EQ+CDR+DE): 9.8 to 12.5 Gbps

- DS125DF410 (EQ+DFE+CDR+DE): 9.8 to 12.5 Gbps

- DS100BR410 (EQ+DE): Up to 10.3125 Gbps

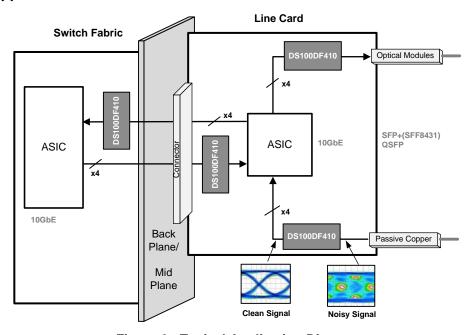

## 2 Applications

- Front Port SFF 8431 (SFP+) Optical and Direct Attach Copper

- Backplane Reach Extension, Data Retimer

- Ethernet: 10 GbE, 1 GbE

For other data rates and data transmission protocols, other pin-compatible devices in the retimer family can be used.

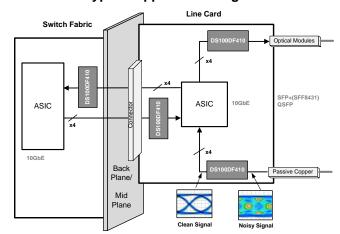

## 3 Description

The DS100RT410 is a four-channel retimer with integrated signal conditioning. Each channel can independently lock to 10.3125-Gbps data rate to support 10 GbE. The device includes a fully adaptive continuous-time linear equalizer (CTLE), clock and data recovery (CDR) and a transmit de-emphasis (DE) driver to enable data transmission over long, lossy and crosstalk-impaired highspeed serial links to achieve BER  $< 1 \times 10^{-15}$ . For channels with a high amount of crosstalk, the DS100DF410 should be used because it has self-calibrating 5-tap decisionfeedback equalizer (DFE).

The programmable settings can be applied easily using the SMBus (I2C) interface, or they can be loaded through an external EEPROM. An on-chip eye monitor and a PRBS generator allow real-time measurement of high-speed serial data for system bring-up or field tuning. Flow-through pinout and single power supply make the DS100RT410 easy to use.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| DS100RT410  | WQFN (48) | 7.00 mm × 7.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## **Typical Application Diagram**

## **Table of Contents**

| 1 | Features 1                           |    | 7.5 Programming                      | 16 |

|---|--------------------------------------|----|--------------------------------------|----|

| 2 | Applications 1                       |    | 7.6 Register Maps                    | 28 |

| 3 | Description 1                        | 8  | Application and Implementation       | 45 |

| 4 | Revision History2                    |    | 8.1 Application Information          | 45 |

| 5 | Pin Configuration and Functions3     |    | 8.2 Typical Application              | 45 |

| 6 | Specifications5                      | 9  | Power Supply Recommendations         | 47 |

| ٠ | 6.1 Absolute Maximum Ratings         | 10 | Layout                               | 47 |

|   | 6.2 ESD Ratings                      |    | 10.1 Layout Guidelines               | 47 |

|   | 6.3 Recommended Operating Conditions |    | 10.2 Layout Example                  | 47 |

|   | 6.4 Thermal Information              | 11 | Device and Documentation Support     | 49 |

|   | 6.5 Electrical Characteristics       |    | 11.1 Documentation Support           | 49 |

|   | 6.6 Typical Characteristics8         |    | 11.2 Community Resources             | 49 |

| 7 | Detailed Description9                |    | 11.3 Trademarks                      | 49 |

| • | 7.1 Overview                         |    | 11.4 Electrostatic Discharge Caution | 49 |

|   | 7.2 Functional Block Diagram 9       |    | 11.5 Glossary                        | 49 |

|   | 7.3 Feature Description              | 12 | Mechanical, Packaging, and Orderable |    |

|   | 7.4 Device Functional Modes 12       |    | Information                          | 50 |

|   |                                      |    |                                      |    |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

## Changes from Original (January 2013) to Revision A

**Page**

- Added Device Information table, ESD Ratings table, Thermal Information table, Detailed Description section,

Application and Implementation section, Power Supply Recommendations section, Layout section, Device and

Documentation Support section, and Mechanical, Packaging, and Orderable Information section

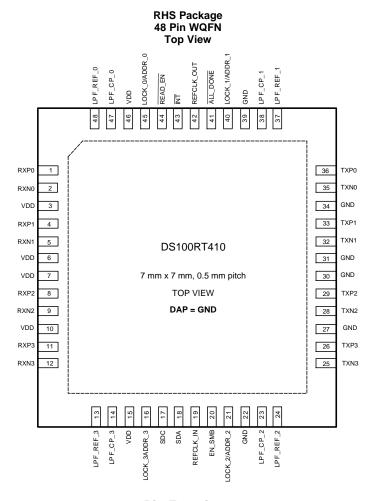

# 5 Pin Configuration and Functions

**Pin Functions**

| F            | PIN          | /O. TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                 |

|--------------|--------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME NO.     |              | VO, ITPE                | DESCRIPTION                                                                                                                                                 |

| HIGH-SPEED   | DIFFERENTIAL | 1/0                     |                                                                                                                                                             |

| RXP0<br>RXN0 | 1<br>2       | I, CML                  | Inverting and non-inverting CML-compatible differential inputs to the equalizer. Nominal differential input impedance = $100 \Omega$ . Must be AC coupled.  |

| RXP1<br>RXN1 | 4<br>5       | I, CML                  | Inverting and non-inverting CML-compatible differential inputs to the equalizer. Nominal differential input impedance = $100 \Omega$ . Must be AC coupled.  |

| RXP2<br>RXN2 | 8<br>9       | I, CML                  | Inverting and non-inverting CML-compatible differential inputs to the equalizer. Nominal differential input impedance = $100 \Omega$ . Must be AC coupled.  |

| RXP3<br>RXN3 | 11<br>12     | I, CML                  | Inverting and non-inverting CML-compatible differential inputs to the equalizer. Nominal differential input impedance = $100 \Omega$ . Must be AC coupled.  |

| TXP0<br>TXN0 | 36<br>35     | O, CML                  | Inverting and non-inverting CML-compatible differential outputs from the driver. Nominal differential output impedance = $100 \Omega$ . Must be AC coupled. |

| TXP1<br>TXN1 | 33<br>32     | O, CML                  | Inverting and non-inverting CML-compatible differential outputs from the driver. Nominal differential output impedance = $100 \Omega$ . Must be AC coupled. |

| TXP2<br>TXN2 | 29<br>28     | O, CML                  | Inverting and non-inverting CML-compatible differential outputs from the driver. Nominal differential output impedance = $100~\Omega$ . Must be AC coupled. |

| TXP3<br>TXN3 | 26<br>25     | O, CML                  | Inverting and non-inverting CML-compatible differential outputs from the driver. Nominal differential output impedance = $100~\Omega$ . Must be AC coupled. |

<sup>(1)</sup> Notes: I = Input, O = Output and 2.5-V LVCMOS pins are 2.5-V levels only.

Only SMBus pins SDA and SDC and INT pin are 3.3-V tolerant. These three pins are open-drain and require external pullup resistors.

Product Folder Links: DS100RT410

Submit Documentation Feedback

# Pin Functions (continued)

| PIN                                  |                              | 40                                  |                                                                                                                                                                                                                                                                                                                     |  |  |  |

|--------------------------------------|------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                 | NO.                          | I/O, TYPE <sup>(1)</sup>            | DESCRIPTION                                                                                                                                                                                                                                                                                                         |  |  |  |

| LOOP FILTER C                        | ONNECTION                    | PINS                                |                                                                                                                                                                                                                                                                                                                     |  |  |  |

| LPF_CP_0<br>LPF_REF_0                | 47<br>48                     | I/O, analog                         | Loop filter connection Place a 22 nF ± 10% capacitor between LPF_CP_0 and LPF_REF_0                                                                                                                                                                                                                                 |  |  |  |

| LPF_CP_1<br>LPF_REF_1                | 38<br>37                     | I/O, analog                         | Loop filter connection Place a 22 nF ± 10% capacitor between LPF_CP_1 and LPF_REF_1                                                                                                                                                                                                                                 |  |  |  |

| LPF_CP_2<br>LPF_REF_2                | 23<br>24                     | I/O, analog                         | Loop filter connection Place a 22 nF ± 10% capacitor between LPF_CP_2 and LPF_REF_2                                                                                                                                                                                                                                 |  |  |  |

| LPF_CP_3<br>LPF_REF_3                | 14<br>13                     | I/O, analog                         | Loop filter connection Place a 22 nF ± 10% capacitor between LPF_CP_3 and LPF_REF_3                                                                                                                                                                                                                                 |  |  |  |

| REFERENCE CL                         | OCK I/O                      |                                     |                                                                                                                                                                                                                                                                                                                     |  |  |  |

| REFCLK_IN                            | 19                           | I, 2.5-V analog                     | Input is 2.5 V, 25 MHz ± 100-ppm reference clock from external oscillator.  No stringent phase noise requirement                                                                                                                                                                                                    |  |  |  |

| REFCLK_OUT                           | 42                           | O, 2.5-V analog                     | Output is 2.5 V, buffered replica of reference clock input for connecting multiple DS100RT410 devices on a board                                                                                                                                                                                                    |  |  |  |

| LOCK INDICATO                        | R PINS                       |                                     |                                                                                                                                                                                                                                                                                                                     |  |  |  |

| LOCK_0<br>LOCK_1<br>LOCK_2           | 45<br>40<br>21               | O, 2.5-V<br>LVCMOS                  | Output is 2.5 V, the pin is high when CDR lock is attained on the corresponding channel.                                                                                                                                                                                                                            |  |  |  |

| LOCK_3                               | 16                           |                                     | These pins are shared with SMBus address strap input functions read at start-up.                                                                                                                                                                                                                                    |  |  |  |

| SMBus MASTER MODE PINS               |                              |                                     |                                                                                                                                                                                                                                                                                                                     |  |  |  |

| ALL_DONE                             | 41                           | O, 2.5-V<br>LVCMOS                  | Output is 2.5 V, the pin goes low to indicate that the SMBus master EEPROM read has been completed.                                                                                                                                                                                                                 |  |  |  |

| READ_EN                              | 44                           | I, 2.5-V LVCMOS                     | Input is 2.5 V, a transition from high to low starts the load from the external EEPROM. The READ_EN pin must be tied low when in SMBus slave mode                                                                                                                                                                   |  |  |  |

| INTERRUPT OUT                        | ГРИТ                         |                                     |                                                                                                                                                                                                                                                                                                                     |  |  |  |

| ĪNT                                  | 43                           | O, 3.3-V<br>LVCMOS, Open<br>Drain   | Used to signal horizontal or vertical eye opening out of tolerance, loss of signal detect, or CDR unlock External $2\text{-}k\Omega$ to $5\text{-}k\Omega$ pullup resistor is required. Pin is $3.3\text{-}V$ LVCMOS tolerant.                                                                                      |  |  |  |

| SERIAL MANAG                         | EMENT BUS                    | (SMBus) INTERFA                     | CE                                                                                                                                                                                                                                                                                                                  |  |  |  |

| ADDR_0<br>ADDR_1<br>ADDR_2<br>ADDR_3 | 45<br>40<br>21<br>16         | I, 2.5-V LVCMOS                     | Input is 2.5 V, the ADDR_[3:0] pins set the SMBus address for the retimer. These pins are strap inputs. Their state is read on power-up to set the SMBus address in SMBus control mode. High = 1-k $\Omega$ to VDD, Low = 1-k $\Omega$ to GND These pins are shared with the lock indicator functions. See Table 2. |  |  |  |

| EN_SMB                               | 20                           | I, 2.5-V analog                     | Input is 2.5 V, selects SMBus master mode or SMBus slave mode  EN_SMB = High for slave mode  EN_SMB = Float for master mode  Tie READ_EN pin low for SMBus slave mode. See Table 1.                                                                                                                                 |  |  |  |

| SDA                                  | 18                           | I/O, 3.3-V<br>LVCMOS, Open<br>Drain | Data Input and Open Drain Output External 2- $k\Omega$ to 5- $k\Omega$ pullup resistor is required. Pin is 3.3-V LVCMOS tolerant.                                                                                                                                                                                   |  |  |  |

| SDC                                  | 17                           | I/O, 3.3-V<br>LVCMOS, Open<br>Drain | Clock Input / Open Drain Clock Output External $2-k\Omega$ to $5-k\Omega$ pullup resistor is required. Pin is 3.3-V LVCMOS tolerant.                                                                                                                                                                                |  |  |  |

| POWER                                |                              |                                     |                                                                                                                                                                                                                                                                                                                     |  |  |  |

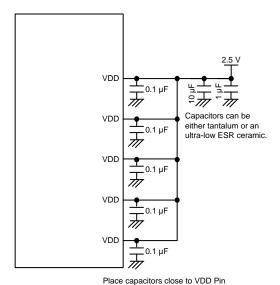

| V <sub>DD</sub>                      | 3, 6, 7,<br>10, 15, 46       | Power                               | $V_{DD} = 2.5 \text{ V} \pm 5\%$                                                                                                                                                                                                                                                                                    |  |  |  |

| GND                                  | 22, 27,<br>30, 31,<br>34, 39 | Power                               | Ground reference.                                                                                                                                                                                                                                                                                                   |  |  |  |

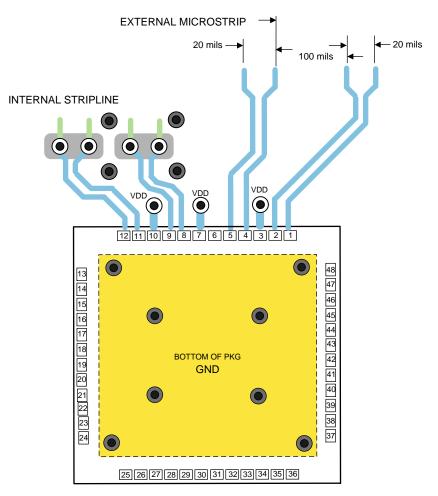

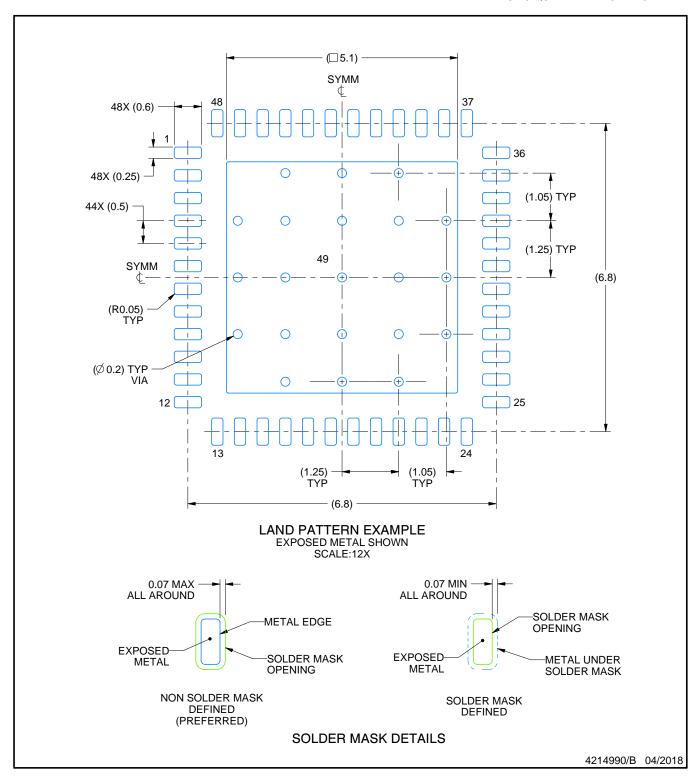

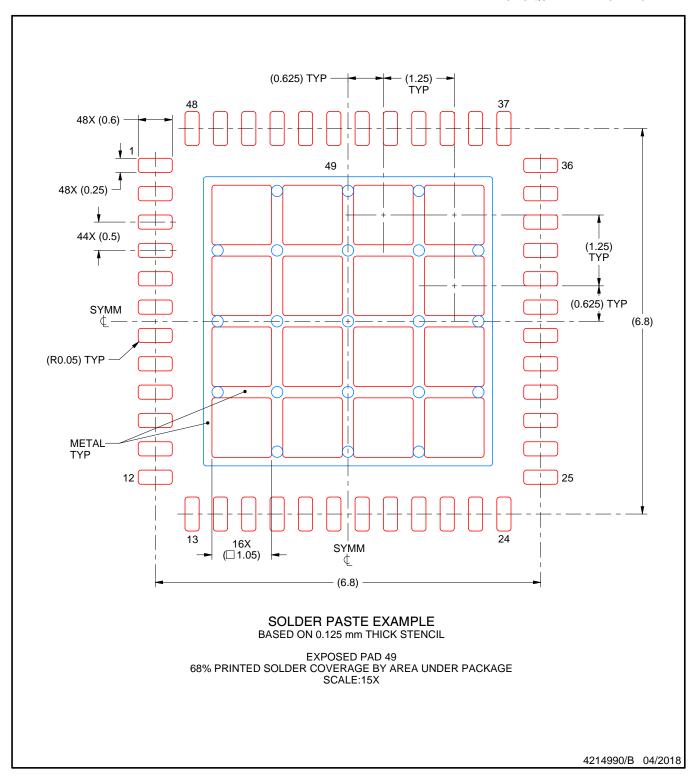

| DAP                                  | PAD                          | Power                               | Ground reference. The exposed pad at the center of the package must be connected to ground plane of the board with at least 4 vias to lower the ground impedance and improve the thermal performance of the package.                                                                                                |  |  |  |

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                        | MIN  | MAX  | UNIT |

|----------------------------------------|------|------|------|

| Supply Voltage (V <sub>DD</sub> )      | -0.5 | 2.75 | V    |

| 2.5 I/O Voltage (LVCMOS and Analog)    | -0.5 | 2.75 | V    |

| 3.3 LVCMOS I/O Voltage (SDA, SDC, INT) | -0.5 | 4.0  | V    |

| Signal Input Voltage (RXPn, RXNn)      | -0.5 | 2.75 | V    |

| Signal Output Voltage (TXPn, TXNn)     | -0.5 | 2.75 | V    |

| Junction Temperature                   |      | 150  | °C   |

| Storage Temperature, T <sub>stg</sub>  | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human Body Model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±6000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Machine Model (MM), STD - JESD22-A115-A <sup>(2)</sup>                                   | ±250  | V    |

|                    |                         | Charged Device Model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(3)</sup> | ±1250 |      |

- (1) JEDEC document JEP155 states that 6000-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V MM allows safe manufacturing with a standard ESD control process.

- (3) JEDEC document JEP157 states that 1250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                         | MIN   | NOM | MAX   | UNIT |

|-----------------------------------------|-------|-----|-------|------|

| Supply voltage (V <sub>DD</sub> to GND) | 2.375 | 2.5 | 2.625 | V    |

| Ambient temperature                     | -40   | 25  | 85    | °C   |

## 6.4 Thermal Information

See (1)

|                      |                                              | DS100RT410 |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(2)</sup>                | RHS (WQFN) | UNIT |

|                      |                                              | 48 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 29.2       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 10.2       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.3        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.1        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 6.3        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2.0        | °C/W |

<sup>(1)</sup> No airflow, 4-layer JEDEC, 9 thermal vias

<sup>(2)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics

over recommended operating supply and temperature ranges with default register settings unless otherwise specified. (1)

|                  | PARAMETER                                | TEST CONDITIONS                                                                                  | MIN  | TYP  | MAX      | UNIT              |

|------------------|------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|----------|-------------------|

| POWER            |                                          |                                                                                                  |      |      |          |                   |

| DD               | D                                        | Average power consumption (2)                                                                    |      | 660  |          | mW                |

| PD               | Power supply consumption                 | Max transient power supply current (3)                                                           |      | 500  | 610      | mA                |

|                  |                                          | 50 Hz to 100 Hz                                                                                  |      | 100  |          | mV <sub>P-P</sub> |

| NT <sub>PS</sub> | Supply noise tolerance (4)               | 100 Hz to 10 MHz                                                                                 |      | 40   |          | mV <sub>P-P</sub> |

|                  |                                          | 10 MHz to 5.0 GHz                                                                                |      | 10   |          | $mV_{P-P}$        |

| 2.5-V LVC        | MOS DC SPECIFICATIONS                    |                                                                                                  |      |      | <b>,</b> |                   |

| .,               | High level input voltage                 |                                                                                                  | 1.75 |      | $V_{DD}$ | V                 |

| $V_{IH}$         | High level (ADDR[3:0] pins)              |                                                                                                  | 2.28 |      | VDD      | V                 |

|                  | Low level input voltage                  |                                                                                                  | GND  |      | 0.7      | V                 |

| $V_{IL}$         | Low level input voltage (ADDR[3:0] pins) |                                                                                                  | GND  |      | 0.335    | V                 |

| V <sub>OH</sub>  | High level output voltage                | $I_{OH} = -3 \text{ mA}$                                                                         | 2.0  |      |          | V                 |

| V <sub>OL</sub>  | Low level output voltage                 | I <sub>OL</sub> = 3 mA                                                                           |      |      | 0.4      | V                 |

|                  | Land last and a summer                   | $V_{IN} = V_{DD}$                                                                                |      |      | 10       | μΑ                |

| liN              | Input leakage current                    | V <sub>IN</sub> = GND                                                                            | -10  |      |          | μA                |

| l <sub>IH</sub>  | Input high current (EN_SMB pin)          | $V_{IN} = V_{DD}$                                                                                |      | 55   |          | μA                |

| I <sub>IL</sub>  | Input low current (EN_SMB pin)           | V <sub>IN</sub> = GND                                                                            |      | -110 |          | μA                |

| 3.3-V LVC        | MOS DC SPECIFICATIONS (SDA, SDC          | , INT)                                                                                           |      |      |          |                   |

| V <sub>IH</sub>  | High level input voltage                 | V <sub>DD</sub> = 2.5 V                                                                          | 1.75 |      | 3.6      | V                 |

| V <sub>IL</sub>  | Low level input voltage                  | V <sub>DD</sub> = 2.5 V                                                                          | GND  |      | 0.7      | V                 |

| V <sub>OL</sub>  | Low level output voltage                 | I <sub>PULLUP</sub> = 3 mA                                                                       |      |      | 0.4      | V                 |

| I <sub>IH</sub>  | Input high current                       | V <sub>IN</sub> = 3.6 V, V <sub>DD</sub> = 2.5 V                                                 | 20   |      | 40       | μΑ                |

| I <sub>IL</sub>  | Input low current                        | V <sub>IN</sub> = GND, V <sub>DD</sub> = 2.5 V                                                   | -10  |      | 10       | μΑ                |

|                  | CMD. a ala ala mata                      | Slave Mode                                                                                       | 10   |      | 400      | kHz               |

| f <sub>SDC</sub> | SMBus clock rate                         | Master Mode <sup>(5)</sup>                                                                       |      | 400  |          | kHz               |

| DATA BIT         | RATES                                    |                                                                                                  |      |      |          |                   |

| <b>-</b>         | D., .                                    | 10.3125-Gbps Ethernet                                                                            | 10.1 |      | 10.6     | Gbps              |

| R <sub>B</sub>   | Bit rate range                           | 1.25-Gbps Ethernet                                                                               | 1.2  |      | 1.3      | Gbps              |

| SIGNAL D         | ETECT                                    |                                                                                                  | 1    |      | '        |                   |

| SDH              | Signal detect ON threshold level         | Default differential input signal level to assert signal detect, 10.3125 Gbps, PRBS-31           |      | 70   |          | mV <sub>p-p</sub> |

| SDL              | Signal detect OFF threshold level        | Default differential input signal level to de-<br>assert signal detect,<br>10.3125 Gbps, PRBS-31 |      | 10   |          | mV <sub>p-p</sub> |

Typical values represent most likely parametric norms at V<sub>DD</sub> = 2.5 V, T<sub>A</sub> = 25°C, and at the Recommended Operation Conditions at the time of product characterization.  $V_{DD} = 2.5 \text{ V}$ ,  $T_A = 25 \text{ C}$ , and at the Recommended Operation Conditions time of product characterization.  $V_{DD} = 2.5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ . All four channels active and locked. Maximum power supply current during lock acquisition. All four channels active, all four channels unlocked, all registers at default

Submit Documentation Feedback

Copyright © 2013-2015, Texas Instruments Incorporated

settings.

Allowed supply noise (mV<sub>P-P</sub> sine wave) under typical conditions.

EEPROM device used for Master mode programming must support fSDC greater than 400 kHz.

## **Electrical Characteristics (continued)**

over recommended operating supply and temperature ranges with default register settings unless otherwise specified. (1)

|                                 | PARAMETER                                        | TEST CONDITIONS                                                                                                                                                                                                                      | MIN  | TYP  | MAX | UNIT              |

|---------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-------------------|

| RECEIVER I                      | INPUTS (RXPn, RXNn)                              |                                                                                                                                                                                                                                      |      |      |     |                   |

| V <sub>TX2, min</sub>           |                                                  | 2 (5)                                                                                                                                                                                                                                |      | 600  |     | $mV_{P-P}$        |

| V <sub>TX2, max</sub>           | Minimum source transmit launch                   | See <sup>(5)</sup>                                                                                                                                                                                                                   |      | 1000 |     | $mV_{P-P}$        |

| V <sub>TX1, max</sub>           | signal level (IN, diff)                          | See <sup>(6)</sup>                                                                                                                                                                                                                   |      | 1200 |     | $mV_{P-P}$        |

| V <sub>TX0, max</sub>           |                                                  | See <sup>(7)</sup>                                                                                                                                                                                                                   |      | 1600 |     | $mV_{P-P}$        |

| L <sub>RI</sub>                 | Maximum differential input return loss -  SDD11  | 100 MHz to 6 GHz <sup>(8)</sup>                                                                                                                                                                                                      |      | -15  |     | dB                |

| Z <sub>D</sub>                  | Differential input impedance                     | 100 MHz to 6 GHz                                                                                                                                                                                                                     |      | 100  |     | Ω                 |

| Z <sub>S</sub>                  | Single-ended input impedance                     | 100 MHz to 6 GHz                                                                                                                                                                                                                     |      | 50   |     | Ω                 |

| DRIVER OU                       | TPUTS (TXPn, TXNn)                               |                                                                                                                                                                                                                                      |      |      |     |                   |

| V <sub>OD0</sub>                | Differential output voltage                      | Differential measurement with OUT+ and OUT- terminated by 50 Ω to GND, AC-Coupled, SMBus register VOD control (Register 0x2d bits 2:0) set to 0, minimum VOD De-emphasis control set to minimum (0 dB)                               | 400  |      | 675 | mV <sub>P-P</sub> |

| V <sub>OD7</sub>                | Differential output voltage                      | Differential measurement with OUT+ and OUT- terminated by 50 Ω to GND, AC-Coupled SMBus register VOD control (Register 0x2d bits 2:0) set to 7, maximum VOD De-emphasis control set to minimum (0 dB)                                | 1000 |      |     | mV <sub>P-P</sub> |

| $V_{\text{OD\_DE}}$             | De-emphasis level <sup>(9)</sup>                 | Differential measurement with OUT+ and OUT- terminated by 50 Ω to GND, AC-Coupled Set by SMBus register control to maximum de-emphasis setting Relative to the nominal 0-dB de-emphasis level set at the minimum de-emphasis setting |      | -12  |     | dB                |

|                                 | Transition time (rise and fall                   | Transition time control = Full slew rate                                                                                                                                                                                             |      | 39   |     | ps                |

| t <sub>R</sub> , t <sub>F</sub> | times) <sup>(9)</sup> (10)                       | Transition time control = Limited slew rate                                                                                                                                                                                          |      | 50   |     | ps                |

| L <sub>RO</sub>                 | Maximum differential output return loss -  SDD22 | 100 MHz to 6 GHz <sup>(8)</sup>                                                                                                                                                                                                      |      | -15  |     | dB                |

| t <sub>DP</sub>                 | Propagation delay                                | Retimed data <sup>(11)</sup>                                                                                                                                                                                                         |      | 300  |     | ps                |

| T <sub>DE</sub>                 | De-emphasis pulse duration <sup>(12)</sup>       | Measured at $V_{OD} = 1000 \text{ mV}_{P-P}$ , de-<br>emphasis setting = $-12 \text{ dB}$                                                                                                                                            |      | 75   |     | ps                |

| TJ                              | Output total jitter                              | Measured at BER = $10^{-12(13)}$                                                                                                                                                                                                     |      | 10   |     | ps                |

| T <sub>SKEW</sub>               | Intra pair skew                                  | Difference in 50% crossing between TXPn and TXNn for any output                                                                                                                                                                      |      | 3    |     | ps                |

| J.1                             | Channel-to-channel skew                          |                                                                                                                                                                                                                                      |      | 7    |     | ps                |

Differential signal amplitude at the transmitter output providing  $< 1 \times 10^{-12}$  bit error rate. Measured at 10.3125 Gbps with a PRBS-31 data pattern. Input transmission channel is 40-inch long FR-4 stripline, 4-mil trace width.

Differential signal amplitude at the transmitter output providing  $< 1 \times 10^{-12}$  bit error rate. Measured at 10.3125 Gbps with a PRBS-31 data

Product Folder Links: DS100RT410

Submit Documentation Feedback

pattern. No input transmission channel.

Measured with 10-MHz clock pattern output.

<sup>(9)</sup> Measured with clock-like {11111 00000} pattern.

(10) Slew rate is controlled by SMBus register settings.

<sup>(11)</sup> Typical at 10.3125-Gbps bit rate.

<sup>(12)</sup> De-emphasis pulse width varies with V<sub>OD</sub> and de-emphasis settings.

(13) Typical with no output de-emphasis, minimum output transmission channel.

## **Electrical Characteristics (continued)**

over recommended operating supply and temperature ranges with default register settings unless otherwise specified. (1)

|                               | PARAMETER                                                                             | TEST CONDITIONS                     | MIN     | TYP  | MAX      | UNIT |

|-------------------------------|---------------------------------------------------------------------------------------|-------------------------------------|---------|------|----------|------|

| CLOCK AND D                   | ATA RECOVERY                                                                          |                                     |         |      | <u> </u> |      |

| BW <sub>PLL</sub>             | PLL bandwidth, -3 dB                                                                  | Measured at 10.3125 Gbps            |         | 5    |          | MHz  |

| J <sub>TOL</sub>              | Input sinusoidal jitter tolerance<br>10-kHz to 250-MHz sinusoidal<br>jitter frequency | Measured at BER = 10 <sup>-15</sup> |         | 0.6  |          | UI   |

| J <sub>TRANS</sub>            | Jitter transfer sinusoidal jitter at 10-MHz jitter frequency                          | Measured at BER = 10 <sup>-15</sup> |         | -6   |          | dB   |

| T <sub>LOCK</sub>             | CDR lock time                                                                         | Measured at 10.3125 Gbps            |         | 15   |          | ms   |

| RECOMMENDE                    | ED REFERENCE CLOCK SPECS                                                              |                                     |         |      |          |      |

| REF <sub>f</sub>              | Input reference clock frequency                                                       |                                     | 24.9975 | 25   | 25.0025  | MHz  |

| REFCLK_IN <sub>PW</sub>       | Minimum REFCLK_IN Pulse Width                                                         | At REFCLK_IN pin                    |         | 4    |          | ns   |

| REFCLK_<br>OUT <sub>DCD</sub> | REFCLK_OUT duty cycle distortion                                                      | C <sub>L</sub> = 5 pF               |         | 0.55 |          | ns   |

| REF <sub>VIH</sub>            | Reference clock input min high threshold                                              |                                     |         | 1.75 |          | V    |

| REF <sub>VIL</sub>            | Reference clock input max low threshold                                               |                                     |         | 0.7  |          | V    |

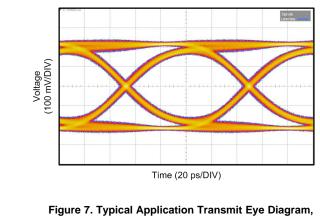

# 6.6 Typical Characteristics

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

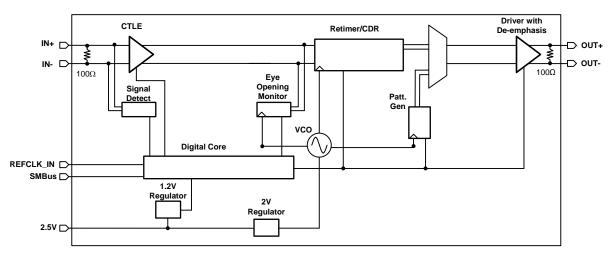

## 7 Detailed Description

#### 7.1 Overview

The DS100RT410 is a low-power 10-GbE 4-channel retimer. Each channel in the DS100RT410 operates independently. All channels include a continuous time linear equalizer (CTLE), clock and data recovery circuit (CDR) and a differential driver with programmable output voltage and de-emphasis. Each channel also has its own eye opening monitor (EOM) and configurable pseudo-random bit sequence (PRBS) pattern generator that can be used for debug purposes.

The DS100RT410 is configurable through a single SMBus port. The DS100RT410 can also act as an SMBus master to configure itself from an EEPROM.

The following sections describe the functionality of the various circuits and features within the DS100RT410.

## 7.2 Functional Block Diagram

Figure 3. DS100RT410 Data Path Block Diagram: One of Four Channels

## 7.3 Feature Description

## 7.3.1 Device Data Path Operation

The data path operation of the DS100RT410 comprises the functional sections as listed in the data path block diagram of Figure 3. The functional sections are as follows.

- Signal Detect

- CTLE

- CDR

- Differential Output Driver

#### 7.3.2 Signal Detect

The signal detect circuit monitors the energy level on the receiver inputs and powers on or off the rest of the high speed data path if a signal is detected or not. By default, each channel allows the signal detect circuit to automatically power on or off the rest of the high speed data path depending on if a signal is present. The signal detect block can be manually controlled in the SMBus channel registers. This can be useful if it is desired manually force channels to be disabled.

Copyright © 2013–2015, Texas Instruments Incorporated

## **Feature Description (continued)**

#### 7.3.3 CTLE

The CTLE in the DS125DF410 is a fully adaptive equalizer with optional limiting stage. The CTLE adapts according to a figure of merit (FOM) calculation during the lock acquisition process. Once the CDR has locked and the CTLE has been adapted, the CTLE boost level will be frozen until a manual re-adapt command is issued or until the CDR re-enters the lock acquisition state. The CTLE is typically readapted by resetting the CDR. The CTLE consists of 4 stages, with each stage having 2-bit boost control. This allows for 256 different stage-boost combinations. The CTLE adaption algorithm allows the CTLE to adapt through 32 of these stage-boost combinations. These 32 stage-boost combinations comprise the EQ Table in the channel registers; see channel registers 0x40 through 0x5F. This EQ Table can be reprogrammed to support up to 32 of the 256 stage-boost settings.

CTLE boost levels are determined by summing the boosts levels of the four stages. Different stage-boost combinations that sum to the same number will have approximately the same boost level, but will result in a different shape for the EQ transfer function (boost curve).

The fourth stage in the CTLE can be programmed through the SMBus interface to become a limiting stage rather than a linear stage.

## 7.3.4 Clock and Data Recovery

The DS100RT410 performs its clock and data recovery function by detecting the bit transitions in the incoming data stream and locking its internal VCO to the clock represented by the mean arrival times of these bit transitions. This process produces a recovered clock with jitter which is greatly reduced for jitter frequencies outside the bandwidth of the CDR phase-locked loop (PLL). This is the primary benefit of using the DS100RT410 in a system. It significantly reduces the jitter present in the data stream, in effect resetting the jitter budget for the system.

### 7.3.5 Output Driver

The output driver is capable of driving variable output voltages with variable amounts of analog de-emphasis. The output voltage and de-emphasis level can be configured by writing registers over the SMBus. The DS100RT410 cannot determine independently the appropriate output voltage or de-emphasis setting, so the user is responsible for configuring these parameters. They can be set for each channel independently.

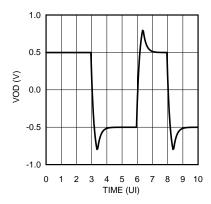

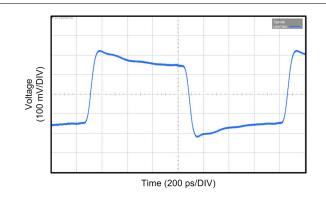

An idealized transmit waveform with analog de-emphasis applied is listed in Figure 4.

Figure 4. Idealized De-Emphasis Waveform

#### 7.3.6 CTLE Boost Setting

The CTLE is a four-stage amplifier with an adjustable, quasi-high-pass transfer function on each stage. The overall frequency response of the CTLE is set by adjusting the boost of each stage independently. Each stage of the CTLE can be set to one of four boost settings. The amount of high-frequency boost supplied by each stage generally increases with increasing boost settings.

The CTLE can also be configured to adapt automatically to provide the optimum boost level for its input signal. Automatic adaptation of the CTLE only is the default mode of operation for the DS100RT410.

## **Feature Description (continued)**

### 7.3.7 Driver Output Voltage

The differential output voltage of the DS100RT410 can be configured from a nominal setting of 600-mV peak-to-peak differential to a nominal setting of 1.3-V peak-to-peak differential, depending upon the application. The driver output voltage as set is the typical peak-to-peak differential output voltage with no de-emphasis enabled.

#### 7.3.8 Driver Output De-Emphasis

The output de-emphasis level of the DS100RT410 can be configured from a nominal setting of 0 dB to a nominal setting of –12 dB depending upon the application. Larger absolute values of the de-emphasis setting provide more pre-distortion of the output driver waveform, accentuating the high-frequency components of the output driver waveform relative to the low-frequency components. Greater values of de-emphasis can compensate for greater dispersion in the transmission media at the output of the DS100RT410. The output de-emphasis level as set is the typical value to which the output signal will settle following the de-emphasis pulse interval in dB relative to the output VOD.

#### 7.3.9 Driver Output Rise and Fall Time

In some applications, a longer rise and fall time for the output signal is desired. This can reduce electromagnetic interference (EMI) generated by fast switching waveforms. This is necessary in some applications for regulatory compliance. In others, it can reduce the crosstalk in the system.

The DS100RT410 can be configured to operate with a nominal rise/fall time corresponding to the maximum slew rate of the output drivers into the load capacitance. Alternatively, the DS100RT410 can be configured to operate with a slightly greater rise and fall time if desired. For the typical specifications on rise and fall time, see *Electrical Characteristics*.

## 7.3.10 Ref\_mode 0 Mode (Reference Clock Not Required)

The DS100RT410 can be used without using a reference clock and the input REFCLK\_IN pin can be open. When register 0x36, bits [5:4] are set to 2'b00, the device operates without using a reference clock at 10.3125-Gbps mode.

For 1-GbE applications, it is required to bypass the CDR by setting the override bit 5 of register 0x09 to 1, and set the data mux bits [7:5] to 3'b000 of register 0x1E.

#### 7.3.11 Ref mode 3 Mode (Reference Clock Required)

When using ref\_mode 3, the device uses an external 25-MHz clock. This mode of operation is set in register 0x36 bits [5:4] = 2'b11 and is the default setting. In ref\_mode 3, the external reference clock is used to aid initial phase lock, and to determine when its VCO is properly phase-locked. An external oscillator should be used to generate a 2.5-V, 25-MHz reference signal which is connected to the DS100RT410 on the reference clock input pin (pin 19). The DS100RT410 does not include a crystal oscillator circuit, so a stand-alone external oscillator is required.

The reference clock speeds up the initial phase lock acquisition. The DS100RT410 is set to phase lock to a known data rate, or a constrained set of known data rates, and the digital circuitry in the DS100RT410 preconfigures the VCO frequency. This enables the DS100RT410 phase-lock to the incoming signal very quickly.

The reference clock is used to calibrate the VCO coarse tuning. However, the reference clock is not synchronous to the data stream, and the quality of the reference clock does not affect the jitter on the output retimed data. The retimed data clock for each channel is synchronous to the VCO internal to that channel of the DS100RT410.

The phase noise of the reference clock is not critical. Any commercially-available 25-MHz oscillator can provide an acceptable reference clock. The reference clock can be daisy-chained from one retimer to another so that only one reference oscillator is required in a system.

#### 7.3.12 False Lock Detector Setting

The register 0x2F, bit 1 is set to 1 by default, which disables the false lock detector. This bit must be set to 0 to enable the false lock detector function.

## **Feature Description (continued)**

#### 7.3.13 Reference Clock In

REFCLK\_IN pin 19 is for reference clock input. A 25-MHz oscillator should be connected to pin 19. See *Electrical Characteristics* for the requirements on the 25-MHz clock. The frequency of the reference clock should always be 25 MHz no matter what data rate or mode of operation is used.

#### 7.3.14 Reference Clock Out

REFCLK\_OUT pin 42 is the reference clock output pin. The DS100RT410 drives a buffered replica of the 25-MHz reference clock input on this output pin. If there are multiple DS100RT410 in the system, the REFCLK\_OUT pin can be directly connected to the REFCLK\_IN pin of another DS100RT410 in a daisy chain connection. The other option is to connect the external 25-MHz oscillator to a clock fanout buffer to distribute the 25-MHz clock to each DS100RT410, which ensures there is a reference clock for the DS100RT410.

## 7.3.15 Daisy Chain of REFCLK\_OUT to REFCLK\_IN

When daisy chaining the device REFCLK\_OUT to the REFCLK\_IN of another device, the trace connection should be less than 1.5 inches (about 5-pF trace capacitance) and it is possible to cascade up to 9 devices. While in other systems with longer interconnecting trace or more capacitive loading, the daisy chain of multiple devices should be reduced. In a system which requires longer daisy chain, it is recommended to place an inverted gate after the sixth device. The pre-distorted duty cycle from the inverter allows longer daisy chain. A better approach is to break the long daisy chain into shorter chains, each driven by a buffer version of the clock distribution and with each chain kept to a maximum of 6 cascade devices. As an example, if there are 12 devices in the system, the daisy chain connections can be divided into two groups of 6 devices and PCB trace length for the reference clock output to input connection; each should be 1.5 inch or less.

## 7.3.16 INT

The  $\overline{\text{INT}}$  line is an open-drain, 3.3-V tolerant, LVCMOS active-low output. The  $\overline{\text{INT}}$  lines from multiple DS100RT410 devices can be wired together and connected to an external controller.

The DS100RT410 generates an interrupt when it detects a loss of signal after previously detecting the presence of a signal, or when it detects loss of lock after previously detecting phase lock. These interrupts are always enabled. In addition, the horizontal eye opening/vertical eye opening (HEO/VEO) interrupt can be enabled using SMBus control for each channel independently. This interrupt is disabled by default. The thresholds for horizontal and vertical eye opening that will trigger the interrupt can be set using the SMBus control for each channel.

If any interrupt occurs, registers in the DS100RT410 latch in information about the event that caused the interrupt. This can then be read out by the controller over the SMBus.

## 7.3.17 LOCK\_3, LOCK\_2, LOCK\_1, and LOCK\_0

Each channel of the DS100RT410 has an independent lock indication pin. These lock indication pins, LOCK\_3, LOCK\_1, and LOCK\_0, are pin 16, pin 21, pin 40, and pin 45 respectively. These pins are shared with the SMBus address strap lines. After the address values have been latched in on power-up, these lines revert to their lock indication function.

When the corresponding channel of the DS100RT410 is locked to the incoming data stream, the lock indication pin goes high. This pin can be used to drive an LED on the board, giving a visual indication of the lock status, or it can be connected to other circuitry which can interpret the lock status of the channel.

#### 7.4 Device Functional Modes

The DS100RT410 can be configured using two different methods.

- SMBus Master Configuration Mode

- SMBus Slave Configuration Mode

The configuration mode is selected by the state of the EN\_SMB pin (pin 20) when the DS100RT410 is powered-up. This pin should be either left floating or tied to the device  $V_{DD}$  through an optional 1-k $\Omega$  resistor. The effect of each of these settings is listed in Table 1.

## **Device Functional Modes (continued)**

#### **Table 1. SMBus Enable Settings**

| EN_SMB PIN<br>SETTING | CONFIGURATION MODE   | DESCRIPTION                                                        | READ_EN PIN                                                          |

|-----------------------|----------------------|--------------------------------------------------------------------|----------------------------------------------------------------------|

| Float                 | SMBus Master<br>Mode | Device reads its configuration from an external EEPROM on power-up | Pull low to initiate reading configuration data from external EEPROM |

| High (1)              | SMBus Slave Mode     | Device is configured over the SMBus by an external controller      | Tie low to enable proper address strapping on power-up               |

#### 7.4.1 SMBus Master Mode and SMBus Slave Mode

In SMBus master mode the DS100RT410 reads its initial configuration from an external EEPROM upon power-up. A description of the operation of this mode appears in the DS100DF410EVK, DS110DF410EVK, DS125DF410EVM User's Guide (SNLU126).

Some of the pins of the DS100RT410 perform the same functions in SMBus master and SMBus slave mode. Once the DS100RT410 has finished reading its initial configuration from the external EEPROM in SMBus master mode it reverts to SMBus slave mode and can be further configured by an external controller over the SMBus. Two device pins initiate reading the configuration from the external EEPROM and indicate when the configuration read is complete.

- ALL DONE

- READ EN

These pins are meant to work together. When the DS100RT410 is powered up in SMBus master mode, it reads its configuration from the external EEPROM. This is triggered when the READ\_EN pin goes low. When the DS100RT410 is finished reading its configuration from the external EEPROM, it drives its ALL\_DONE pin low. In this mode, as the name suggests, the DS100RT410 acts as an SMBus master during the time it is reading its configuration from the external EEPROM. After the DS100RT410 has finished reading its configuration from the EEPROM, it releases control of the SMBus and becomes a SMBus slave. In applications where there is more than one DS100RT410 on the same SMBus, bus contention can result if more than one DS100RT410 tries to take command of the SMBus as the SMBus master at the same time. The READ\_EN and ALL\_DONE pins prevent this bus contention.

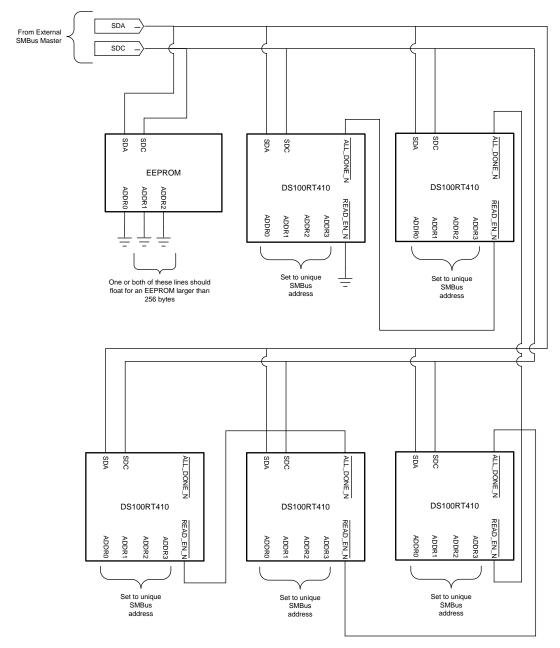

In a system where the DS100RT410 <u>devices are</u> meant to operate in SMBus master mode, the <u>READ\_EN</u> pin of one retimer should be wired to the <u>ALL\_DONE</u> pin of the next. The system should be designed so that the <u>READ\_EN</u> pin of one (and only one) of the DS100RT410 devices in the system is driven low on power-up. This DS100RT410 will take command of the SMBus on power-up and will read its initial configuration from the external EEPROM. When it is finished reading its configuration, it will set its <u>ALL\_DONE</u> pin low. This pin should be connected to the <u>READ\_EN</u> pin of another DS100RT410. When this DS100RT410 senses its <u>READ\_EN</u> pin driven low, it will take <u>command</u> of the SMBus and read its initial <u>configuration</u> from the external EEPROM, after <u>which</u> it will set its <u>ALL\_DONE</u> pin low. By connecting the <u>ALL\_DONE</u> pin of each DS100RT410 to the <u>READ\_EN</u> pin of the next DS100RT410, each DS100RT410 can read its initial configuration from the EEPROM without causing bus contention.

For SMBus slave mode, the  $\overline{READ\_EN}$  pin **must be tied low**. Do not leave the  $\overline{READ\_EN}$  pin floating or tie it high.

A connection diagram with several DS100RT410 devices along with an external EEPROM and an external SMBus master is listed in Figure 5. The SMBus master must be prevented from trying to take control of the SMBus until the DS100RT410 devices have finished reading their initial configurations from the EEPROM.

Figure 5. Connection Diagram for Multiple DS100RT410 devices in SMBus Master Mode

In SMBus master mode after the DS100RT410 has finished reading its initial configuration from the external EEPROM it reverts to SMBus slave mode. In either mode the SMBus data and clock lines, SDA and SDC, are used. Also, in either mode, the SMBus address is latched in on the address strap lines on power-up. In SMBus slave mode, if the READ\_EN pin is not tied low, the DS100RT410 will not latch in the address on its address strap lines. It will instead latch in an SMBus write address of 0x30 regardless of the state of the address strap lines. This is a test feature. Obviously a system with multiple retimers cannot operate properly if all the retimers are responding to the same SMBus address. Tie the READ\_EN pin low when operating in SMBus slave mode to avoid this condition.

The DS100RT410 reads its SMBus address upon power-up from the SMBus address lines.

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

### 7.4.2 Address Lines <ADDR [3:0]>

In either SMBus master or SMBus slave mode the DS100RT410 must be assigned an SMBus address. A unique address must be assigned to each device on the SMBus.

The SMBus address is latched into the DS100RT410 on power-up. The address is read in from the state of the <ADDR [3:0]> lines (pins 16, 21, 40, and 45 respectively) upon power-up. In either SMBus mode these address lines are input pins on power-up.

The DS100RT410 can be configured with any of 16 SMBus addresses. The SMBus addressing scheme uses the least-significant bit of the SMBus address as the Read/Write\_N address bit. When an SMBus device is addressed for writing, this bit is set to 0; for reading, to 1. Table 2 lists the write address setting for the DS100RT410 versus the values latched in on the address lines at power-up.

The address byte sent by the SMBus master over the SMBus is always 8 bits long. The least-significant bit indicates whether the address is for a write operation, in which the master will output data to the SMBus to be read by the slave, or a read operation, in which the slave will output data to the SMBus to be read by the master. if the least-significant bit is a 0, the address is for a write operation. If it is a 1, the address is for a read operation. Accordingly, SMBus addresses are sometimes referred to as seven-bit addresses. To produce the write address for the SMBus, the seven-bit address is left-shifted by one bit. To produce the read address, it is left shifted by one bit and the least-significant bit is set to 1. Table 2 lists the seven-bit addresses corresponding to each set of address line values.

When the DS100RT410 is used in SMBus slave mode, the READ EN pin must be tied low. If it is tied high or floating, the DS100RT410 will not latch in its address from the address lines on power-up. When the READ EN pin is tied high in SMBus slave mode (that is, when the EN\_SMB pin (pin 20) is tied high), the DS100RT410 will revert to an SMBus write address of 0x30. This is a test feature. If there are multiple DS100RT410 devices on the same SMBus, they will all revert to an SMBus write address of 0x30, which can cause SMBus collisions and failure to access the DS100RT410 devices over the SMBus.

Table 2. DS100RT410 SMBus Write Address Assignment

| ADDR_3 | ADDR_2 | ADDR_1 | ADDR_0 | SMBus WRITE<br>ADDRESS | SEVEN-BIT SMBus<br>ADDRESS |

|--------|--------|--------|--------|------------------------|----------------------------|

| 0      | 0      | 0      | 0      | 0x30                   | 0x18                       |

| 0      | 0      | 0      | 1      | 0x32                   | 0x19                       |

| 0      | 0      | 1      | 0      | 0x34                   | 0x1a                       |

| 0      | 0      | 1      | 1      | 0x36                   | 0x1b                       |

| 0      | 1      | 0      | 0      | 0x38                   | 0x1c                       |

| 0      | 1      | 0      | 1      | 0x3a                   | 0x1d                       |

| 0      | 1      | 1      | 0      | 0x3c                   | 0x1e                       |

| 0      | 1      | 1      | 1      | 0x3e                   | 0x1f                       |

| 1      | 0      | 0      | 0      | 0x40                   | 0x20                       |

| 1      | 0      | 0      | 1      | 0x42                   | 0x21                       |

| 1      | 0      | 1      | 0      | 0x44                   | 0x22                       |

| 1      | 0      | 1      | 1      | 0x46                   | 0x23                       |

| 1      | 1      | 0      | 0      | 0x48                   | 0x24                       |

| 1      | 1      | 0      | 1      | 0x4a                   | 0x25                       |

| 1      | 1      | 1      | 0      | 0x4c                   | 0x26                       |

| 1      | 1      | 1      | 1      | 0x4e                   | 0x27                       |

Once the DS100RT410 has latched in its SMBus address, its registers can be read and written using the two pins of the SMBus interface, serial data (SDA) and serial data clock (SDC).

#### 7.4.3 SDA and SDC

In both SMBus master and SMBus slave mode, the DS100RT410 is configured using the SMBus. The SMBus consists of two lines, the SDA or Serial Data line (pin 18) and the SDC or Serial Data Clock line (pin 17). In the DS100RT410 these pins are 3.3-V tolerant. The SDA and SDC lines are both open-drain. They require a pullup resistor to a supply voltage, which may be either 2.5 V or 3.3 V. A pullup resistor in the 2-k $\Omega$  to 5-k $\Omega$  range will provide reliable SMBus operation.

The SMBus is a standard communications bus for configuring simple systems. For a specification of the SMBus an description of its operation, see <a href="http://smbus.org/specs/">http://smbus.org/specs/</a>.

## 7.5 Programming

### 7.5.1 SMBus Strap Observation

Register 0x00, bits 7:4 and register 0x06, bits 3:0

In order to communicate with the DS100RT410 over the SMBus, it is necessary for the SMBus controller to know the address of the DS100RT410. The address strap observation bits in control/shared register 0x00 are primarily useful as a test of SMBus operation. There is no way to get the DS100RT410 to indicate what its SMBus address is unless it is already known.

In order to use the address strap observation bits of control/shared register 0x00, it is necessary first to set the diagnostic test control bits of control/shared register 0x06. This four-bit field should be written with a value of 0xa. When this value is written to bits 3:0 of control/shared register 0x06, then the value of the SMBus address straps can be read in register 0x00, bits 7:4. The value read will be the same as the value present on the ADDR3:ADDR0 lines when the DS100RT410 was powered up. For example, if a value of 0x1 is read from control/shared register 0x00, bits 7:4, then at power-up the ADDR0 line was set to 1 and the other address lines, ADDR3:ADDR1, were all set to 0. The DS100RT410 is set to an SMBus Write address of 0x32.

#### 7.5.2 Device Revision and Device ID

Register 0x01

Control/shared register 0x01 contains the device revision and device ID. The device revision listed in Table 11 is the current revision for the DS100RT410. The device ID will be different for the different devices in the retimer family. The value listed in "For the DS100RT410, Register 0x01, bits 4:0 = 0x10" is the correct value for the DS100RT410. This register is useful because it can be interrogated by software to determine the device variant and revision installed in a particular system. The software might then configure the device with appropriate settings depending upon the device variant and revision.

## 7.5.3 Control/Shared Register Reset

Register 0x04, bit 6

Register 0x04, bit 6, clears all the control/shared registers back to their factory defaults. This bit is self-clearing, so it is cleared after it is written and the control/shared registers are reset to their factory default values.

#### 7.5.4 Interrupt Channel Flag Bits

Register 0x05, bits 3:0

The operation of these bits is described in *Interrupt Status*.

#### 7.5.5 SMBus Master Mode Control Bits

Register 0x04, bits 5 and 4 and register 0x05, bits 7 and 4

Register 0x04, bit 5, can be used to reset the SMBus master mode. This bit should not be set if the DS100RT410 is in SMBus slave mode. This is an undefined condition.

When this bit is set, if the EN\_SMB pin is floating (meaning that the DS100RT410 is in SMBus master mode), then the DS100RT410 will read the contents of the external EEPROM when the READ\_EN pin is pulled low. This bit is not self-clearing, so it should be cleared after it is set.

When the DS100RT410 EN\_SMB pin is floating (meaning that the DS100RT410 is in SMBus master mode), it will read from its external EEPROM when its READ\_EN pin goes low. After the EEPROM read operation is complete, register 0x05, bit 4 will be set. Alternatively, the DS100RT410 will read from its external EEPROM when triggered by register 0x04, bit 4, as described below.

When register 0x04, bit 4, is set, the DS100RT410 reads its configuration from an external EEPROM over the SMBus immediately. When this bit is set, the DS100RT410 does not wait until the READ\_EN pin is pulled low to read from the EEPROM. This EEPROM read occurs whether the DS100RT410 is in SMBus master mode or not. If the read from the EEPROM is not successful, for example because there is no EEPROM present, then the DS100RT410 may hang up and a power-up reset may be necessary to return it to proper operation. You should only set this bit if you know that the EEPROM is present and properly configured.

If the EEPROM read has already completed, then setting register 0x04, bit 4, will not have any effect. To cause the DS100RT410 to read from the EEPROM again it is necessary to set bit 5 of register 0x04, resetting the SMBus master mode. If the DS100RT410 is not in SMBus master mode, do not set this bit. After setting this bit, it should be cleared before further SMBus operations.

After SMBus master mode has been reset, the EEPROM read may be initiated either by pulling the READ\_EN pin low or by then setting register 0x04, bit 4.

Register 0x05, bit 7, disables SMBus master mode. This prevents the DS100RT410 from trying to take command of the SMBus to read from the external EEPROM. Obviously this bit will have no effect if the EEPROM read has already taken place. It also has no effect if an EEPROM read is currently in progress. The only situations in which disabling EEPROM master mode read is valid are (1) when the DS100RT410 is in SMBus master mode, but the READ\_EN pin has not yet gone low, and (2) when register 0x04, bit 5, has been used to reset SMBus master mode but the EEPROM read operation has not yet occurred.

Do not set this bit and bit 4 of register 0x04 simultaneously. This is an undefined condition and can cause the DS100RT410 to hang up.

#### 7.5.6 Resetting Individual Channels of the Retimer

Register 0x00, bit 2, and register 0x0a, bits 3:2

Bit 2 of channel register 0x00 are used to reset all the registers for the corresponding channel to their factory default settings. This bit is self-clearing. Writing this bit will clear any register changes you have made in the DS100RT410 since it was powered-up.

To reset just the CDR state machine without resetting the register values, which will re-initiate the lock and adaptation sequence for a particular channel, use channel register 0x0a. Set bit 3 of this register to enable the reset override, then set bit 2 to force the CDR state machine into reset. These bits can be set in the same operation. When bit 2 is subsequently cleared, the CDR state machine will resume normal operation. If a signal is present at the input to the selected channel, the DS100RT410 will attempt to lock to it and will adapt its CTLE according to the currently configured adapt mode for the selected channel. The adapt mode is configured by channel register 0x31, bits 6:5.

## 7.5.7 Interrupt Status

Control/Shared Register 0x05, bits 3:0, Register 0x01, bits 4 and 0, Register 0x30, bit 4, Register 0x32, and Register 0x36, bit 6

Each channel of the DS100RT410 will generate an interrupt under several different conditions. The DS100RT410 will always generate an interrupt when it loses CDR lock or when a signal is no longer detected at its input. If the HEO/VEO interrupt is enabled by setting bit 6 of register 0x36, then the retimer will generate an interrupt when the horizontal or vertical eye opening falls below the preset values even if the retimer remains locked. When one of these interrupt conditions occurs, the retimer alerts the system controller via hardware and provides additional details via register reads over the SMBus.

First, the open-drain interrupt line  $\overline{\text{INT}}$  is pulled low. This indicates that one or more of the channels of the retimer has generated an interrupt. The interrupt lines from multiple retimers can be wire-ANDed together so that if any retimer generates an interrupt the system controller can be notified using a single interrupt input.

if the interrupt has occurred because the horizontal or vertical eye opening has dropped below the pre-set threshold, which is set in channel register 0x32, then bit 4 of register 0x30 will go high. This indicates that the source of the interrupt was the HEO or VEO.

If the interrupt has occurred because the CDR has fallen out of lock, or because the signal is no longer detected at the input, then bit 4 and/or bit 0 of register 0x01 will go high, indicating the cause of the interrupt.

In either case, the control/shared register set will indicate which channel caused the interrupt. This is read from bits 3:0 of control/shared register 0x05.

When an interrupt is detected by the controller on the interrupt input, the controller should take the following steps to determine the cause of the interrupt and clear it.

- 1. The controller detects the interrupt by detecting that the  $\overline{\text{INT}}$  line has been pulled low by one of the retimers to which it is connected.

- 2. The controller reads control/shared register 0x05 from all the DS100RT410 devices connected to the INT line. For at least one of these devices, at least one of the bits 3:0 will be set in this register.

- 3. For each device with a bit set in bits 3:0 of control/shared register 0x05, the controller determines which channel or channels produced an interrupt. Refer to Table 11 for a mapping of the bits in this bit field to the channel producing the interrupt.

- 4. When the controller detects that one of the retimers has a 1 in one of the four LSBs of this register, the controller selects the channel register set for that channel of that retimer by writing to the channel select register, 0xff, as previously described.

- 5. For each channel that generated an interrupt, the controller reads channel register 0x01. If bit 4 of this register is set, then the interrupt was caused by a loss of CDR lock. If bit 0 is set, then the interrupt was caused by a loss of signal. it is possible that both bits 0 and 4 could be set. Reading this register will clear these bits.

- 6. Optionally, for each channel that generated an interrupt, the controller reads channel register 0x30. If bit 4 of this register is set, then the interrupt was caused by HEO and/or VEO falling out of the configured range. This interrupt will only occur if bit 6 of channel register 0x36 is set, enabling the HEO/VEO interrupt. Reading register 0x30 will clear this interrupt bit.

- 7. Once the controller has determined what condition caused the interrupt, the controller can then take the appropriate action. For example, the controller might reset the CDR to cause the retimer to re-adapt to the incoming signal. If there is no longer an incoming signal (indicated by a loss of signal interrupt, bit 0 of channel register 0x01), then the controller might alert an operator or change the channel configuration. This is system dependent.

- 8. Reading the interrupt status registers will clear the interrupt. if this does not cause the interrupt input to go high, then another device on the same input has generated an interrupt. The controller can address the next device using the procedure above.

- 9. Once all the interrupt registers for all channels for <u>all DS100RT410</u> devices that generated interrupts have been read, clearing all the interrupt indications, the <u>INT</u> line should go high again. This indicates that all the existing interrupt conditions have been serviced.

The channel registers referred to above, registers 0x01, 0x30, 0x32, and 0x36, are described in the channel registers table, Table 13.

## 7.5.8 Overriding the CTLE Boost Setting

Register 0x03, Register 0x13, bit 2, and Register 0x3a

To override the CTLE boost settings, register 0x03 is used. This register contains the currently-applied CTLE boost settings. The boost values can be overridden by using the two-bit fields in this register as listed in the table.

The final stage of the CTLE has an additional control bit which sets it to a limiting mode. For some channels, this additional setting improves the bit error rate performance. This bit is bit 2 of register 0x13.