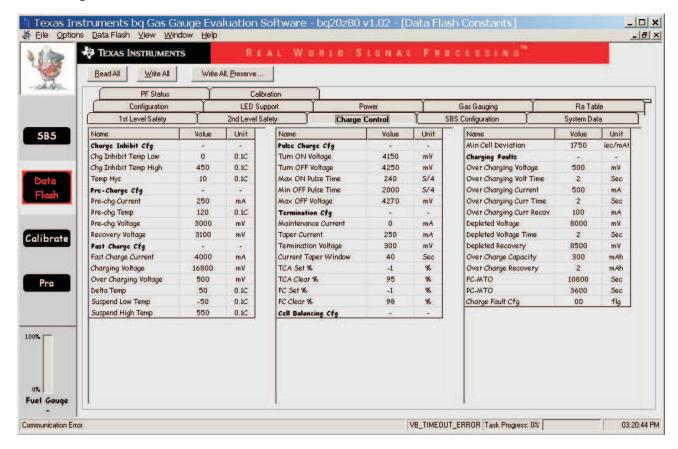

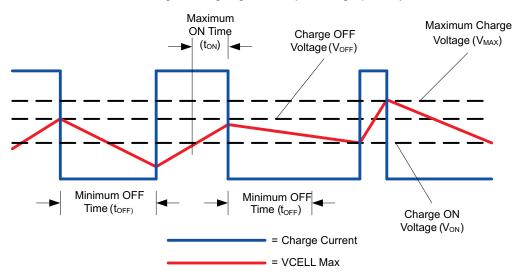

# Configuring the bq20z80 Data Flash

Battery Management

### **ABSTRACT**

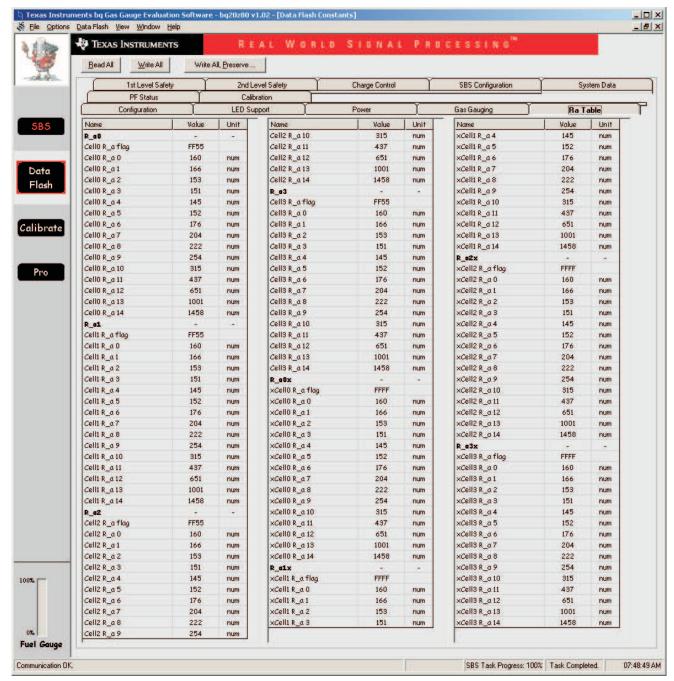

The bq20z80 has numerous data flash constants that can be used to configure the device with a variety of different options for most features. The data flash of the bq20z80 is split into sections which are described in detail within this document.

### **Contents** 1 Glossary 2 2 3 4 6 System Data 40 7 PF Status 44 8 Calibration 48 Configuration 54 10 LED Support 65 11 12 13 List of Figures Pulse Charging Voltage vs Time ..... 1 **List of Tables** AFE OC Dsg Configuration ..... 1 2 AFE OC Dsg Time Configuration ...... 3 4 AFE SC Chg Cfg Least Significant Nibble (SCCV3-SCCV0)..... 5 6 7 8

Glossary www.ti.com

# 1 Glossary

ASOC: Absolute State of Charge

Bit: This word has a different meaning than Flag. This word is used to refer to a configuration setting bit. It is primarily used in data flash settings.

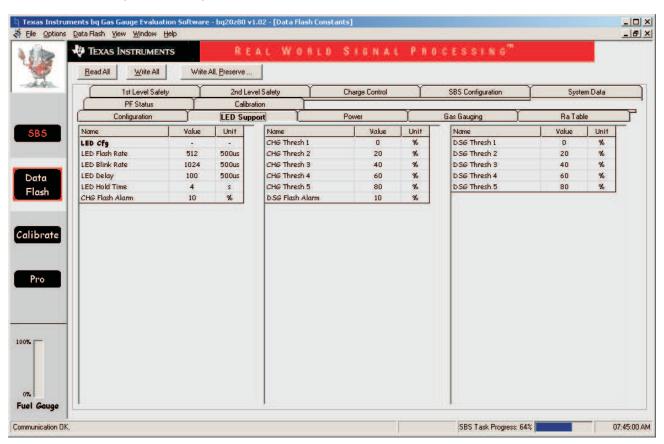

Blink, Flash and There are 3 different display modes for the LEDs in this document that need Delay: clarification.

- Blinking: When the display is said to be blinking, then the word "blinking" is

used to refer to the LED located closest to the LED used to indicate 100%

that is illuminated and "blinking" when the LED display is activated and

displaying SOC (state of charge). Only this "topmost" activated LED in the

display blinks. All other LEDs that are activated is steady state when

activated. (see LED Blink Rate)

- Flashing: When the display is said to be flashing, then the word "flashing" means all LEDs that are activated to indicate the SOC will flash with a period of (2 x LED Flash Rate).

- Delay: When the display is activate, all LEDs that are required to indicate the SOC may not illuminate at the same time. Starting from the LED that represents the lowest SOC, there can be a delay (*LED Delay*) between each LED illuminating from the LED that represents the lowest possible SOC up to the LED that represents the present SOC.

**Cell Voltage(Max)**: This represents the maximum value among all the SBS cell voltage registers.(**Cell Voltage 1** through **Cell Voltage 4**)

Cell Voltage(Min): This represents the minimum value among all the SBS cell voltage registers.(Cell Voltage 1 through Cell Voltage 4)

Cell Voltage(Any): This represents any of the possible SBS cell voltage registers.(Cell Voltage 1 through Cell Voltage 4)

[DSG] in *Battery* SBS defines the [DSG] flag in battery status as the method for determining *Status*: charging or discharging. This can be confused in many descriptions in this

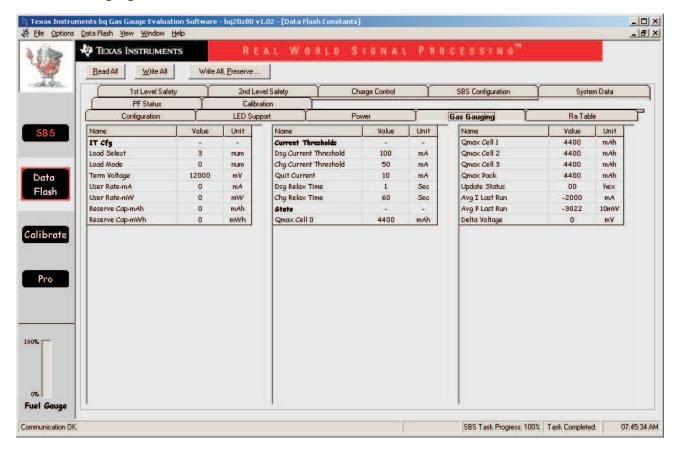

charging or discharging. This can be confused in many descriptions in this document because different functions require different methods for determining charging or discharging. The SBS description sometimes does not give enough resolution for correct part function so these functions require other data flash registers as described in their respective definitions. SBS states that if the battery is charging then [DSG] is 0, and any other time (Current less than or equal to 0), the [DSG] flag is set. The actual formula that the bq20z80 uses for setting or clearing the [DSG] flag are as follows:

[DSG] clear: [DSG]=0 if *Current* >= Chg Current Threshold

[DSG] set: [DSG]=1 if

- Current <= Dsg Current Threshold or</li>

- 2. Relaxation Mode which is defined by one of the following statements:

- A) **Current** transitioning from below (–) Quit Current to (above (–) Quit Current and below Quit Current) for Dsg Relax Time

- B) **Current** transitioning from above *Quit Current* to (below *Quit Current* and above (–) *Quit Current*) for *Chg Relax Time*

www.ti.com Glossary

FCC: Full Charge Capacity

FET opened/Closed: It is common to say FET opened or FET closed. This is used throughout this

document to mean the FET is turned off or the FET is turned on respectively.

Flag: This word is usually used to represent a read only status bit that indicates some action has occurred or is occurring. This bit usually cannot be modified by the

user.

Precharge/ZVCHG: The words Precharge and ZVCHG are interchangeable throughout the document

RCA: Remaining Capacity Alarm

RM: Remaining Capacity

RSOC: Relative state of Charge

RTA: Remaining Time Alarm

SAFE and SAFE: These words are used throughout this document to represent 2 output pins on

the bq20z80. SAFE is pin 7 on the bq20z80 and SAFE is pin 12. When this document discusses permanent failures, it normally includes a discussion of these two pins. When a permanent failure happens and its control bit is enabled, then these 2 pins are activated to either blow a fuse or to activate some hardware protection. The reason there are 2 outputs is for backwards compatibility with bq20z8X parts and to give options for an application. Both outputs are activated at the same time when enabled, but the SAFE pin is active low so it is driven low when activated while the SAFE pin is active high and is driven high when activated.

SOC: This is used as a generic meaning of State-of-Charge. It can mean RSOC, ASOC, or percentage of actual chemical capacity.

System: The word system is sometimes used in this document. It always means a host system that is consuming current from the battery pack that includes the bq20z80.

Italics: All words in this document that are in italics represent names of data flash locations exactly as they are shown in the EV software.

**Bold Italics**: All words that are bold italic represent SBS compliant registers exactly as they are shown in the EV software.

[brackets]: All words or letters in brackets represent bit/flag names exactly as they are shown in the SBS and Data Flash in the EV software.

(–): This is commonly used in this document to represent a minus sign. It is written this way to ensure that the sign is not lost in the translation of formulas in the text of this document.

1st Level Safety www.ti.com

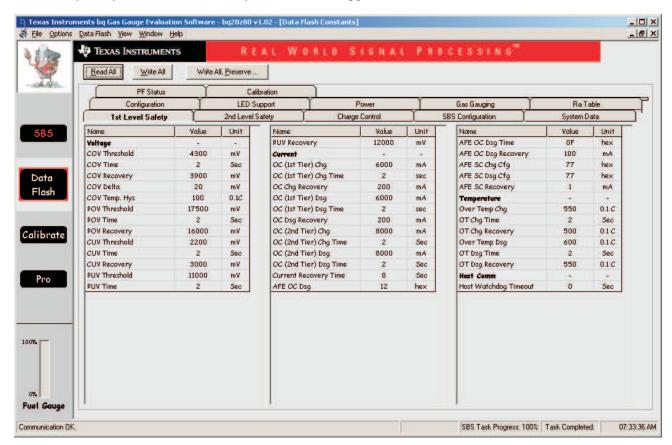

# 2 1<sup>st</sup> Level Safety

All 1<sup>st</sup> Level Safety functions are temporary. There should be no permanent failures or damage to the battery if any of the 1<sup>st</sup> Level Safety functions are triggered.

## 2.1 Voltage

### COV Threshold

When any cell voltage measured by *Cell Voltage (Any)* rises to this threshold, then the Cell Over Voltage (COV) protection process is triggered, initiating a [COV] in *Safety Alert* for *COV Time*. If the COV condition clears prior to the expiration of the *COV Time* timer, then [COV] in *Safety Alert* is cleared and no [COV] flag is set in *Safety Status*. If the COV condition does not clear, then [COV] is set in *Safety Status* and the Charge FET is opened. This fault condition causes [TCA] in *Battery Status* to be set. It also causes *Charging Current* and *Charging Voltage* to be set to 0. Setting *COV Time* to 0 completely disables this function.

**Normal Setting:** Default is 4300 mV. This cell is chemistry dependent, but 4200-4300 is the most common settings.

### COV Time

See COV Threshold. This is a buffer time allotted for a COV condition. The timer starts after [COV] is set in **Safety Alert**. When it expires, then the bq20z80 forces [COV] set in **Safety Status** and opens the Charge FET. If the condition clears prior to the expiration of the COV Time timer, then the [COV] is cleared in **Safety Alert** and the COV Time timer resets without setting [COV] in **Safety Status**. Setting COV Time to 0 completely disables COV Threshold.

Normal Setting: This is normally set to 2 seconds, but depends on the application.

www.ti.com 1st Level Safety

## COV Recovery

When a [COV] is set in **Safety Status**, it is only cleared when **ALL** cell voltages as measured by **Cell Voltage(All)** fall below this threshold.

**Normal Setting:** This defaults to 3900 mV. It must be set low enough that the hysteresis between *COV Threshold* fault and this recovery prevents oscillation of the Charge FET.

### COV Delta

The actual trigger value for *the COV Threshold* is adjusted down by this amount if *Temperature* rises above (*Over Temperature Threshold* – *COV Temp Hys*). The actual Data Flash location for *COV Threshold* is not modified, just the trigger value. It returns to normal if the temperature falls below (*Over Temperature Threshold* – *COV Temp Hys*). If this time is set to 0, then the *COV Threshold* trigger value is not modified based on the temperature.

Normal Setting: This value is normally set to 20 mV. This is application and cell chemistry dependent.

# COV Temp Hys

See COV Delta. This is the delta temperature below the Over Temperature Threshold where the COV Threshold is modified by COV Delta.

**Normal Setting:** This value is normally set to 100 in 0.1°C. This is application and cell chemistry dependent.

### POV Threshold

When the pack voltage measured by *Voltage* rises to this threshold, then the Pack Over Voltage (POV) protection process is triggered. This process starts by setting [POV] in *Safety Alert* for POV Time. If the POV condition clears prior to the expiration of the *POV Time* timer, then the [POV] is cleared in *Safety Alert* with no [POV] being set in *Safety Status*. If the POV condition does not clear, then [POV] is set in *Safety Status* and the Charge FET is opened. This fault condition causes [TCA] in *Battery Status* to be set. It also causes *Charging Current* and *Charging Voltage* to be set to 0. Setting *POV Time* to 0 completely disables this function.

**Normal Setting:** This register defaults to 17500 which is for a 4-cell pack. This is high, but it depends on the cell chemistry and the number of cells in series for an application. It is normally set to the (number of cells × 4300 mV). (i.e., 8600 mV for 2-cell applications, 12900 mV for 3-cell, and 17200 mV for 4-cell applications)

## **POV Time**

See *POV Threshold*. This is a buffer time allotted for a POV condition. The timer starts after the [POV] is set in *Safety Alert*. When it expires, then the bq20z80 forces [POV] set in *Safety Status* and opens the Charge FET. If the condition clears prior to the expiration of the *POV Time* timer, then [POV] is cleared in *Safety Alert* and the *POV Time* timer resets. Setting *POV Time* to 0 completely disables *POV Threshold*.

Normal Setting: This is normally set to 2 seconds, but depends on the application.

### POV Recovery

When [POV] is set in *Safety Status*, it is only cleared when the pack voltage measured by *Voltage* falls below this threshold.

**Normal Setting:** This defaults to 16000 mV. It must be set low enough that the hysteresis between *POV Threshold* fault and this recovery prevents oscillation of the Charge FET.

### **CUV Threshold**

When any cell voltage measured by *Cell Voltage(Any)* falls below this threshold, then the Cell Under Voltage (CUV) protection process is triggered, initiating a [CUV] flag getting set in *Safety Alert* for *CUV Time*. If the CUV condition clears prior to the expiration of the *CUV Time* timer, then [CUV] is cleared in *Safety Alert* and no [CUV] is set in *Safety Status*. If the CUV condition does not clear, then a [CUV] is set in *Safety Status* and the Discharge FET is opened. This fault condition causes [TDA] and [FD] in *Battery Status* to be set. It also causes [XDSG] in *Operation Status*. Setting *CUV Time* to 0 completely disables this function.

**Normal Setting:** Default is 2200 mV. This is cell chemistry dependent but 2200 mV-2300 mV is the most common setting.

1st Level Safety www.ti.com

### **CUV Time**

See CUV Threshold. This is a buffer time allotted for a CUV condition. The timer starts after [CUV] is set in Safety Alert. When it expires, then the bq20z80 forces [CUV] set in Safety Status and opens the Charge FET. If the condition clears prior to the expiration of the CUV Time timer, then [CUV] is cleared in Safety Alert and the CUV Time timer resets. Setting CUV Time to 0 completely disables CUV Threshold.

Normal Setting: This is normally set to 2 seconds but depends on the application.

### CUV Recovery

When [CUV] is set in Safety Status, it is only cleared when ALL cell voltages as measured by Cell **Voltage(All)** rise above this threshold.

Normal Setting: The default for this register is 3000 mV. It must be set high enough that the hysteresis between CUV Threshold fault and this recovery prevents oscillation of the Discharge FET.

### PUV Threshold

When the pack voltage measured by Voltage falls below this threshold, then the Pack Under Voltage (PUV) protection process is triggered, initiating a [PUVt] in Safety Alert for PUV Time. If the PUV condition clears prior to the expiration of the PUV Time timer, then [PUV] is cleared in Safety Alert and [PUV] are not set in Safety Status. If the PUV condition does not clear, then a [PUV] is set in Safety Status and the Discharge FET is opened. This fault condition causes [TDA] and [FD] in Battery Status to be set. It also causes [XDSG] in Operation Status. Setting PUV Time to 0 completely disables this function.

Normal Setting: This register defaults to 11000 which is for a 4-cell pack. This is very application and cell chemistry dependent. It also depends on the number of cells in series for an application. A very common setting is the (number of cells x 2750 mV). i.e., 5500 mV for 2-cell applications, 8250 mV for 3-cell, and 11000 mV for 4-cell applications)

### **PUV Time**

See PUV Threshold. This is a buffer time allotted for a PUV condition. The timer starts after [PUV] is set in Safety Alert. When it expires, then the bg20z80 forces [PUV] set in Safety Status and opens the Discharge FET. If the condition clears prior to the expiration of the PUV Time timer, then [PUV] is cleared in Safety Alert and the PUV Time timer resets. Setting PUV Time to 0 completely disables PUV Threshold.

**Normal Setting:** This is normally set to 2 seconds but depends on the application.

### PUV Recovery

When [POV] is set in **Safety Status**, it is only cleared when the pack voltage measured by **Voltage** falls below this threshold.

Normal Setting: The default for this register is 12000 mV. Set high enough that the hysteresis between PUV Threshold fault and this recovery prevents oscillation of the Discharge FET.

### 2.2 Current

There are 3 levels or tiers of current protection in the bq20z80. The first 2 levels, 1st Tier and 2nd Tier are slow responding (>1 second). The third level is a very quick responding current protection controlled directly by the bq29312A.

NOTE: IT is important that the bg29312A makes the triggering decision for any of the AFE fault conditions. This is to ensure quick response to dangerous faults. It is also designed in such a way that the AFE can act completely autonomously in the event of damage to the bq20z80 in the triggering of any AFE fault. The bq29312A cannot, however, clear the fault condition. It is cleared only by the bg20z80. The AFE data is transferred to the bg29312A on reset and (if enabled in the AFE Verification subclass) is continually monitored by the bq20z80 to ensure no corruption has occurred at any time. If corruption has occurred, the bg20z80 attempts to make corrections. If after repeated attempts (as set in the AFE Verification subclass), it cannot correct the condition, then it sets a permanent failure. If enabled in Permanent Fail Cfg, then the SAFE pin is driven high and SAFE pin is driven low on the bq20z80. (See Permanent Fail Cfg)

www.ti.com 1st Level Safety

## OC (1st Tier) Chg

When current measured by *Current* reaches up to or above this threshold during charging, then the 1<sup>st</sup> Tier Over Current in the Charge [OCC] protection process is triggered, initiating an [OCC] in *Safety Alert* for *OC* (1<sup>st</sup> *Tier*) *Chg Time* in seconds. If the 1<sup>st</sup> Tier OCC condition clears prior to the expiration of the *OC* (1<sup>st</sup> *Tier*) *Chg Time* timer, then [OCC] in *Safety Alert* is cleared and no [OCC] is set in *Safety Status*. If the 1<sup>st</sup> Tier OCC condition does not clear, then a [OCC] is set in *Safety Status* and the Charge FET is opened. This fault condition causes [TCA] in *Battery Status* to be set. It also causes *Charging Current* and *Charging Voltage* to be set to 0. Setting the *OC* (1st Tier) *Chg Time* to 0 completely disables this function.

**Normal Setting:** This register is application dependent. It should be set above the absolute maximum expected discharge current. It should be set high enough that unexpected mild charge spikes or inaccuracies do not create a false over current trigger, but low enough to force the Charge FET to open before damage occurs to the pack.

### OC (1st Tier) Chg Time

See  $OC(1^{st} \ Tier)$  Chg. This is a buffer time allotted for a  $1^{st}$  tier Over Current condition. The timer starts every time the [OCC] in **Safety Alert** is initially set. When the timer expires, then the bq20z80 forces an [OCC] in **Safety Status** and opens the Charge FET. If [OCC] in **Safety Alert** clears prior to the expiration of the  $OC(1^{st} \ Tier)$   $Chg \ Time$  timer, then [OCC] in **Safety Alert** is cleared and the  $OC(1^{st} \ Tier)$   $Chg \ Time$  timer resets. Setting the  $OC(1^{st} \ Tier)$   $Chg \ Time$  to 0 disables  $OC(1^{st} \ Tier)$   $Chg \ Time$   $Chg \ Time$  Ch

**Normal Setting:** This is normally set to 2 seconds, but depends on the application. It must be set long enough to prevent false triggering of the [OCC] in *Safety Status*, but short enough to prevent damage to the battery pack.

# OC Chg Recovery

OC Chg Recovery is one of several recovery methods used for both 1<sup>st</sup> and 2<sup>nd</sup> level Over Current in the charge direction faults. This value is used for either nonremovable packs ([NR] in Operation Cfg B =1) or for removable packs configured ([OCC] in Non-Removable Cfg). With either of these settings, Average Current must fall below this value for Current Recovery Timer in seconds to clear the [OCC] or the [OCC2] in Safety Status if either is set.

**Normal Setting:** This register is application dependent, but is normally set low enough that it prevents quick oscillation in the Charge FET. **Average Current** is used for this recovery function and falls every second that it is recomputed with **Current** at or near 0. If this recovery is set too high, then the Charge FET can oscillate with a frequency that is fast enough to cause damage to the battery pack because the **Average Current** falls below this value quickly.

# OC (1st Tier) Dsg

When current measured by *Current* falls down to or below this threshold during discharging then the 1<sup>st</sup> Tier Over Current in discharge (OCD) protection process is triggered, initiating an [OCD] in *Safety Alert* for *OC* (1<sup>st</sup> *Tier*) *Dsg Time* in seconds. If the 1<sup>st</sup> Tier OCD condition clears prior to the expiration of the *OC* (1<sup>st</sup> *Tier*) *Dsg Time* timer, then the [OCD] is cleared and no [OCD] is set. If the 1<sup>st</sup> Tier OCD condition does not clear, then a [OCD] is set in *Safety Status* and the Discharge FET is opened. This fault condition causes [XDSG] and [XDSGI] in *Operation Status* to be set. It also causes *Charging Current* to be set to 0.

**Normal Setting:** Care should be taken when interpreting discharge descriptions in this document when interpreting the direction and magnitude of the currents because they are in the negative direction. This register is application dependent. It should be set **below** the absolute maximum expected discharge current. It must be set low enough that unexpected mild discharge spikes or inaccuracies do not create a false over current trigger, but high enough to force the Discharge FET open before damage occurs to the pack.

### OC (1st Tier) Time Dsg

See  $OC(1^{st} \ Tier) \ Dsg$ . This is a buffer time allotted for a 1<sup>st</sup> tier Over Current in the discharge direction condition. The timer starts every time [OCD] in **Safety Alert** is initially set. When the timer expires, the bq20z80 forces an [OCD] Alarm in **Safety Status** and opens the Discharge FET. If [OCD] in Safety Alert clears prior to the expiration of the  $OC(1^{st} \ Tier) \ Time \ Dsg$  timer, then the [OCD] in **Safety Alert** is cleared and the  $OC(1^{st} \ Tier) \ Time \ Dsg$  timer resets. Setting the  $OC(1^{st} \ Tier) \ Time \ Dsg$  to 0 disables  $OC(1^{st} \ Tier) \ Dsg$ .

1st Level Safety www.ti.com

**Normal Setting:** This is normally set to 2 seconds, but depends on the application. It should be set long enough to prevent false triggering of the [OCD] in *Safety Status*, but short enough to prevent damage to the battery pack.

# OC Dsg Recovery

OC Dsg Recovery is one of several recovery methods used for both 1<sup>st</sup> and 2<sup>nd</sup> level Over Current in the discharge direction Faults. This value is used for either nonremovable packs ([NR] in Operation Cfg B = 1) or for removable packs configured ([OCD] in Non-Removable Cfg). With either of these settings, **Average Current** must rise **above** this value for Current Recovery Timer in seconds to clear the [OCD] or the [OCD2] in **Safety Status** if either is set.

**Normal Setting:** Care should be taken when interpreting discharge descriptions in this document when interpreting the direction and magnitude of the currents because they are in the negative direction. This register is application dependent but is normally set **high** enough that it prevents quick oscillation in the Discharge FET. **Average Current** is used for this recovery function and moves closer to 0 every second that it is recomputed with **Current** at or near 0. If this recovery is set too **low**, then the Discharge FET can oscillate with a frequency that is fast enough to cause damage to the battery pack because the **Average Current** moves **above** this value quickly.

# OC (2<sup>nd</sup> Tier) Chg

When current measured by *Current* reaches up to or above this threshold during charging then the 2<sup>nd</sup> Tier Over Current in Charge [OCC2] protection process is triggered, initiating an [OCC2] in *Safety Alert* for *OC* (2<sup>nd</sup> *Tier*) *Chg Time* in seconds. If the 2<sup>nd</sup> Tier Over Current condition clears prior to the expiration of the *OC* (2<sup>nd</sup> *Tier*) *Chg Time* timer, then [OCC2] in *Safety Alert* is cleared and no [OCC2] is set in *Safety Status*. If the 2<sup>nd</sup> Tier Over Current condition does not clear, then a [OCC2] is set in *Safety Status* and the Charge FET is opened. This fault condition causes [TCA] in *Battery Status* to be set. It also causes *Charging Current* and *Charging Voltage* to be set to 0.Normal Setting: This register is application dependent. It should be set above the *OC* (1<sup>st</sup> *Tier*) *Chg* threshold and should be set high enough that unexpected mild charge spikes or inaccuracies do not create a false over current trigger, but low enough to force the Charge FET to open before damage occurs to the pack.

**Normal Setting:** This register is application dependent. It should be set above the *OC* (1<sup>st</sup> Tier) Chg threshold and should be set high enough that unexpected mild charge spikes or inaccuracies do not create a false over current trigger, but low enough to force the Charge FET to open before damage occurs to the pack.

### OC (2<sup>nd</sup> Tier) Time Chg

See  $OC(2^{nd} \ Tier)$  Chg. This is a buffer time allotted for a  $2^{nd}$  Tier Over Current condition. The timer starts every time the [OCC2] is **Safety Alert** is initially set. When the timer expires then, the bq20z80 forces an [OCC2] in **Safety Status** and opens the Charge FET. If [OCC2] in **Safety Alert** clears prior to the expiration of the  $OC(2^{nd} \ Tier)$   $Chg \ Time$  timer, then [OCC2] in **Safety Alert** is cleared and the  $OC(2^{nd} \ Tier)$   $Chg \ Time$  timer resets. Setting the  $OC(2^{nd} \ Tier)$   $Chg \ Time$  to 0 disables  $OC(2^{nd} \ Tier)$  Chg.

**Normal Setting:** This is normally set to 2 seconds, but depends on the application. It must be set long enough to prevent false triggering of the [OCC2] in *Safety Status*, but short enough to prevent damage to the battery pack. It is common for the second level over current threshold to be disabled.

www.ti.com 1st Level Safety

## OC (2<sup>nd</sup> Tier) Dsg

When current measured by *Current* falls down to or below this threshold during discharging, then the 2<sup>nd</sup> Tier Over Current in discharge (OCD2) protection process is triggered, initiating an [OCD2] in *Safety Alert* for *OC* (2<sup>nd</sup> *Tier*) *Dsg Time* in seconds. If the 2<sup>nd</sup> Tier OCD2 condition clears prior to the expiration of the *OC* (2<sup>nd</sup> *Tier*) *Dsg Time* timer, then the [OCD2] is cleared in *Safety Alert* and no [OCD2] alarm is set in *Safety Status*. If the 2<sup>nd</sup> Tier OCD condition does not clear, then a [OCD2] is set in *Safety Status* and the Discharge FET is opened. This fault condition causes [XDSG] and [XDSGI] in *Operation Status* to be set. It also causes *Charging Current* to be set to 0.

**Normal Setting:** Care should be taken when interpreting discharge descriptions in this document when interpreting the direction and magnitude of the currents because they are in the negative direction. This register is application dependent. It should be set **below** the *OC* (1<sup>st</sup> *Tier*) *Dsg* threshold and must be set **below** the absolute maximum expected discharge current. It must be set **low** enough that unexpected mild discharge spikes or inaccuracies do not create a false over current trigger, but **high** enough to force the Discharge FET open before damage occurs to the pack.

# OC (2<sup>nd</sup> Tier) Time Dsg

See *OC* ( $2^{nd}$  *Tier*) *Dsg*. This is a buffer time allotted for a  $2^{nd}$  Tier Over Current in the discharge direction condition. The timer starts every time [OCD2] in *Safety Alert* is initially set. When the timer expires, then the bq20z80 forces an [OCD2] alarm in *Safety Status* and opens the Discharge FET. If [OCD2] in *Safety Alert* clears prior to the expiration of the *OC* ( $2^{nd}$  *Tier*) *Time Dsg* timer, then the [OCD] in *Safety Alert* is cleared and the *OC* ( $2^{nd}$  *Tier*) *Time Dsg* timer resets. Setting the *OC* ( $2^{nd}$  *Tier*) *Time Dsg* to 0 disables *OC* ( $2^{nd}$  *Tier*) *Dsg*.

**Normal Setting:** This is normally set to 2 seconds but depends on the application. It must be set long enough to prevent false triggering of the [OCD2] in *Safety Status* but short enough to prevent damage to the battery pack.

# Current Recovery Timer

The *Current Recovery Timer* is used in the recovery process of any of the over current fault conditions. After a fault condition exists, depending on if enabled, the fault condition is cleared only after *Current Recovery Timer* time in seconds with *AverageCurrent* falling below the corresponding recovery threshold in the charge direction or rising above the corresponding recovery threshold in the discharge direction. The corresponding recovery does not happen immediately after the recovery condition exits. As soon as the recovery condition exists then the *Current Recovery Timer* starts and the condition clears and the corresponding FET is enabled after the *Current Recovery Timer* expires. This timer is associated with the following Fault Conditions as described in this section:

- 1. OC (1st Tier) Dsg

- 2. OC (1st Tier) Chg

- 3. OC (2<sup>nd</sup> Tier) Dsg

- 4. OC (2<sup>nd</sup> Tier) Chg

- 5. AFE OC Dsg

- 6. AFE SC Dsg

- 7. AFE SC Cha

This Recovery method is enabled if [NR] is set in *Operation Cfg B*, or if ([NR] is cleared and the corresponding bits are set in the *Non-Removable Cfg* register:

OC (1<sup>st</sup> Tier) Dsg [OCD]

OC (1<sup>st</sup> Tier) Chg [OCC]

OC (2<sup>nd</sup> Tier) Dsg [OCD2]

OC (2<sup>nd</sup> Tier) Chg [OCC2]

AFE OC Dsg [AOCD]

AFE SC Dsg [SCD]

AFE SC Chg [SCC]

**Normal Setting:** The default for this register is 8 seconds. This is a recommended number to prevent heating up in the corresponding FET.

1st Level Safety www.ti.com

### AFE OC Dsg

See the important note about all AFE fault conditions at the beginning of the Current section.

This is the third level Over Current protection in the discharge direction. This is a last effort protection function before using the Permanent Fail Functions in the Second Level Safety Class. This register displays in HEX using the EV Software. Also note that this setting is in units of volts. It does not take into account the Sense resistor value. If the *AFE OC DSG* condition exists for *AFE OC Dsg Time* in milliseconds, then the discharge FET opens as controlled by the bq29312A. This fault condition causes [AOCD] to be set in *Safety Status* and [XDSG], [XDSGI] is set in *Operation Status*, and [TDA] is set in *Battery Status*. It also causes *Charging Current* to be set to 0. See Table 1 for settings for this register.

**Table 1. AFE OC Dsg Configuration**

| 0X00 | 0.050 V | 0x08 | 0.090 V | 0x10 | 0.130 V | 0x18 | 0.170 V |

|------|---------|------|---------|------|---------|------|---------|

| 0x01 | 0.055 V | 0x09 | 0.095 V | 0x11 | 0.135 V | 0x19 | 0.175 V |

| 0x02 | 0.060 V | 0x0a | 0.100 V | 0x12 | 0.140 V | 0x1a | 0.180 V |

| 0x03 | 0.065 V | 0x0b | 0.105 V | 0x13 | 0.145 V | 0x1b | 0.185 V |

| 0x04 | 0.070 V | 0x0c | 0.110 V | 0x14 | 0.150 V | 0x1c | 0.190 V |

| 0x05 | 0.075 V | 0x0d | 0.115 V | 0x15 | 0.155 V | 0x1d | 0.195 V |

| 0x06 | 0.080 V | 0x0e | 0.120 V | 0x16 | 0.160 V | 0x1e | 0.200 V |

| 0x07 | 0.085 V | 0x0f | 0.125 V | 0x17 | 0.165 V | 0x1f | 0.205 V |

**Normal Setting:** Note that the maximum value for this register is 0x1F. Values above 0x1F cause unpredictable results. This register is completely application specific. Its setting does not correspond to current, so a conversion using the application Sense Resistor value is required in determining the proper setting for this register. Be sure that this value is **below** the *OC* (2<sup>nd</sup> Tier) Dsg.

### AFE OC Dsq Time

This is the time after detection of an *AFE OC Dsg* fault before the Discharge FET attempts to open. This trigger function is completely controlled by the bq29312A. The setting of this register is in HEX, and it is in milliseconds (See *AFE OC Dsg*). See Table 2 for setting for this register.

**Table 2. AFE OC Dsg Time Configuration**

| 0x00 | 1 ms | 0x04 | 9 ms  | 0x08 | 17 ms | 0x0c | 25 ms |

|------|------|------|-------|------|-------|------|-------|

| 0x01 | 3 ms | 0x05 | 11 ms | 0x09 | 19 ms | 0x0d | 27 ms |

| 0x02 | 5 ms | 0x06 | 13 ms | 0x0a | 21 ms | 0x0e | 29 ms |

| 0x03 | 7 ms | 0x07 | 15 ms | 0x0b | 23 ms | 0x0f | 31 ms |

**Normal Setting:** Note that the maximum value for this register is 0x0F. Values above 0x0F cause unpredictable results. This register is completely application specific. It should be set long enough to prevent false triggering of the [AOCD] in *Safety Status*, but short enough to prevent damage to the battery pack.

# AFE OC Dsg Recovery

See the important note about all AFE fault conditions at the beginning of the Current section.

AFE OC Dsg Recovery is one of several recovery methods used for AFE OC Dsg Fault. This value is used for either nonremovable packs ([NR] in Operation Cfg B =1) or for removable packs configured ([AOCD] in Non-Removable Cfg). With either of these settings, **AverageCurrent** must rise **above** this value for Current Recovery Timer in seconds to clear the [AOCD] in **Safety Status** if it is set.

**Normal Setting:** Care should be taken when interpreting discharge descriptions in this document when interpreting the direction and magnitude of the currents because they are in the negative direction. This register is application dependent, but is normally set **high** enough that it prevents quick oscillation in the Discharge FET. If set to **low**, then the Discharge FET can oscillate with a frequency that is fast enough to still cause damage to the battery pack because the **AverageCurrent** moves **above** this value quickly.

AFE SC Chg Cfg

www.ti.com 1st Level Safety

See the **NOTE** at the beginning of the Current section for an important note about all AFE fault conditions.

This register includes 2 settings. We will refer to these as *AFE SC Chg* and *AFE SC Chg Time*. This register displays in HEX using the EV Software. The most significant nibble (bits 4-7) sets the time for the AFE short circuit in the Charge direction fault detection time (*AFE SC Chg Time*). The least significant nibble (bits 0-3) set the threshold at which the bq29312A detects a AFE short circuit fault (*AFE SC Chg*). This is an extreme condition with settings for very large voltages and very short setting times for violent faults far above any of the other fault conditions because its intended purpose is to detect a short circuit condition before damage to the battery pack can occur. Also note that this setting is in units of volts. It does not take into account the Sense resistor value. If an AFE short circuit in the Charge direction fault exists for AFE short circuit in the Charge direction fault detection time in microseconds, then the Charge FET opens as controlled by the bq29312A. This fault condition causes [SCC] to be set in *Safety Status*, and [TCA] to be set in *Battery Status*. It also causes *Charging Current* and *Charging* Voltage to be set to 0. See Table 4 for settings for this register.

# Table 3. AFE SC Chg Cfg Bit Description

| 7     | 6      | 5        | 4     | 3     | 2     | 1     | 0     |

|-------|--------|----------|-------|-------|-------|-------|-------|

| SCCT3 | SCCT2  | SCCT1    | SCCT0 | SCCV3 | SCCV2 | SCCV1 | SCCV0 |

|       | AFE SC | Chg Time |       |       | AFE S | C Chg |       |

# Table 4. AFE SC Chg Cfg Least Significant Nibble (SCCV3-SCCV0)

| 0x00 | 0.100 V | 0x04 | 0.200 V | 0x08 | 0.300 V | 0x0c | 0.400 V |

|------|---------|------|---------|------|---------|------|---------|

| 0x01 | 0.125 V | 0x05 | 0.225 V | 0x09 | 0.325 V | 0x0d | 0.425 V |

| 0x02 | 0.150 V | 0x06 | 0.250 V | 0x0a | 0.350 V | 0x0e | 0.450 V |

| 0x03 | 0.175 V | 0x07 | 0.275 V | 0x0b | 0.375 V | 0x0f | 0.475 V |

# Table 5. AFE SC Chg Cfg Most Significant Nibble (SCCT3-SCCT0)

| 0x00 | 0 µs   | 0x04 | 244 µs | 0x08 | 488 µs | 0x0c | 732 µs |

|------|--------|------|--------|------|--------|------|--------|

| 0x01 | 61 µs  | 0x05 | 305 µs | 0x09 | 549 µs | 0x0d | 793 µs |

| 0x02 | 122 µs | 0x06 | 366 µs | 0x0a | 610 µs | 0x0e | 854 µs |

| 0x03 | 183 µs | 0x07 | 427 µs | 0x0b | 671 µs | 0x0f | 915 µs |

**Normal Setting:** This register is completely application specific. Its setting does not correspond to current, so a conversion using the application Sense Resistor value is required in determining the proper setting for this register. Be sure that this value is sufficiently above *OC* (2<sup>nd</sup> *Tier*) *Chg*.

1st Level Safety www.ti.com

### AFE SC Dsg Config

See the important note about all AFE fault conditions at the beginning of the Current section.

This register includes 2 settings. Refer to these as *AFE SC Dsg* and *AFE SC Dsg Time*. This register displays in HEX using the EV Software. The most significant nibble (bits 4–7) sets the time for the AFE short circuit in the discharge direction fault detection time (*AFE SC Dsg Time*). The least significant nibble (bits 0–3) sets the threshold at which the bq29312A detects an AFE short circuit fault in the discharge direction (*AFE SC Dsg*). This is an extreme condition with settings for large voltages and short setting times for violent faults far above any of the other fault conditions because its intended purpose is to detect a short circuit condition before damage to the battery pack can occur. Also note that this setting is in units of volts. It does not take into account the Sense resistor value. If an AFE short circuit in the Charge direction fault exists for AFE short circuit in the Charge direction fault detection time in microseconds, then the Discharge FET opens as controlled by the bq29312A. This fault condition causes [SCD] to be set in *Safety Status*, [XDSG] and [XDSGI] to be set in *Operation Status*, and [TDA] to be set in *Battery Status*. See Table 7 and Table 8 for settings for this register.

# Table 6. AFE SC Dsg Cfg Bit Description

| 7     | 6      | 5        | 4     | 3     | 2     | 1      | 0     |

|-------|--------|----------|-------|-------|-------|--------|-------|

| SCDT3 | SCDT2  | SCDT1    | SCDT0 | SCDV3 | SCDV2 | SCDV1  | SCDV0 |

|       | AFE SC | Dsg Time |       |       | AFE S | SC Dsg |       |

# Table 7. AFE SC Dsg Cfg Least Significant Nibble (SCDV3-SCDV0)

| 0x00 | 0.10 V  | 0x04 | 0.20 V  | 0x08 | 0.30 V  | 0x0c | 0.40 V  |

|------|---------|------|---------|------|---------|------|---------|

| 0x01 | 0.125 V | 0x05 | 0.225 V | 0x09 | 0.325 V | 0x0d | 0.425 V |

| 0x02 | 0.150 V | 0x06 | 0.250 V | 0x0a | 0.350 V | 0x0e | 0.450 V |

| 0x03 | 0.175 V | 0x07 | 0.275 V | 0x0b | 0.375 V | 0x0f | 0.475 V |

# Table 8. AFE SC Dsg Cfg Most Significant Nibble (SCDT3-SCDT0)

| 0x00 | 0 µs   | 0x04 | 244 µs | 0x08 | 488 µs | 0x0c | 732 µs |

|------|--------|------|--------|------|--------|------|--------|

| 0x01 | 61 µs  | 0x05 | 305 µs | 0x09 | 549 µs | 0x0d | 793 µs |

| 0x02 | 122 µs | 0x06 | 366 µs | 0x0a | 610 µs | 0x0e | 854 µs |

| 0x03 | 183 µs | 0x07 | 427 µs | 0x0b | 671 µs | 0x0f | 915 µs |

**Normal Setting:** This register is completely application specific. Its setting does not correspond to current, so a conversion using the application Sense Resistor value is required to determine the proper setting for this register. Be sure that this value is **below** AFE OC Dsg.

# AFE SC Recovery

See the important note about all AFE fault conditions at the beginning of the **Current** section.

AFE SC Recovery is one of several recovery methods used for either a charge or discharge AFE short circuit fault. This value is used for either nonremovable packs ([NR] in Operation Cfg B =1) or for removable packs that this function is configured ([SCD] for discharge or [SCC] in charge in Non-Removable Cfg). With either of these settings, AverageCurrent must rise **above** this value (for discharge fault) or **below** this value (for charge fault) for Current Recovery Timer in seconds to clear the [SCD] or [SCC] in Safety Status if either is set.

**Normal Setting:** Care must be taken when interpreting discharge descriptions in this document when interpreting the direction and magnitude of the currents because they are in the negative direction. This register is application dependent, but is normally set close to 0 mA to prevent quick oscillation in the Charge/Discharge FET. If it is set to far from 0 mA, then the Charge/Discharge FET oscillates with a frequency that is fast enough to cause damage to the battery pack because the *AverageCurrent* is within this threshold value too quickly.

www.ti.com 1st Level Safety

# 2.3 Temperature

# Over Temp Chg

When the pack temperature measured by *Temperature* rises to or above this threshold while charging (*Current > Chg Current Threshold*), then the Over Temperature in charge direction (OTC) protection process is triggered and [OTC] is set in *Safety Alert* for *OT Chg Time*. If the OTC condition clears prior to the expiration of the *OT Chg Time* timer, then the [OTC] is cleared in *Safety Alert* and no [OTC] is set in *Safety Status*. If the condition does not clear, then [OTC] is set in *Safety Status* and if [OTFET] is set in *Operation Cfg B* the Charge FET is opened. If [OTFET] is not set in *Operation Cfg B*, then the Charge FET is not opened by this fault. This fault condition causes [TCA] and [OTA] in *Battery Status* to be set. It also causes *Charging Current* and *Charging Voltage* to be set to 0.

**Normal Setting:** This setting depends on the environment temperature and the battery specification. Verify the battery specification allows temperatures up to this setting while charging and verify these setting are sufficient for the application temperature. The default is 55°C which should be sufficient for most Li-lon applications.

### OT Chg Time

See *Over Temp Chg*. This is a buffer time allotted for Over Temperature in the charge direction condition. The timer starts every time the [OTC] in *Safety Alert* is initially set. When the timer expires, the bq20z80 forces an [OTC] in *Safety Status* and opens the Charge FET if enabled with [OTFET] in *Operation Cfg B*. If [OTC] in *Safety Alert* clears (fault condition clears) prior to the expiration of the *OT Chg Time* timer, then [OTC] in *Safety Alert* is cleared and the *OT Chg Time* timer resets. Setting the *OT Chg Time* to 0 disables this function.

**Normal Setting:** This is normally set to 2 seconds which should be sufficient for most applications. Temperature is normally a slow acting condition that does not need high speed triggering. It must be set long enough to prevent false triggering of the [OTC] in **Safety Status**, but short enough to prevent damage to the battery pack.

### OT Chg Recovery

OT Chg Recovery is the temperature at which the battery recovers from an OT Temp Chg fault. This is the only recovery method for an OT Temp Chg fault.

**Normal Setting:** This register is application dependent, but is normally set low enough below the fault condition temperature to prevent quick oscillation in the Charge FET if it was opened with the fault. The default is 50°C which is a 5 degree difference which is sufficient to protect against oscillation during the transition between conditions.

### Over Temp Dsg

When the pack temperature measured by *Temperature* rises to or above this threshold while discharging (*Current* <(-)(*Dsg Current Threshold*)), then the Over Temperature in discharge direction (OTD) protection process is triggered and [OTD] is set in *Safety Alert* for *OT Dsg Time*. If the OTD condition clears prior to the expiration of the *OT Dsg Time* timer, then the [OTD] is cleared in *Safety Alert* and no [OTD] is set in *Safety Status*. If the condition does not clear, then [OTD] is set in *Safety Status* and if [OTFET] is set in *Operation Cfg B* the Discharge FET is opened. If [OTFET] is not set in *Operation Cfg B* then the Discharge FET is not opened by this fault. This fault condition causes [TDA] and [OTA] in *Battery Status* to be set. It also causes *Charging Current* to be set to 0.

**Normal Setting:** This setting depends on the environment temperature and the battery specification. Verify the battery specification allows temperatures up to this setting while charging and verify these setting are sufficient for the application temperature. The default is 60°C which is sufficient for most Lilon applications. The default *Over Temp Dsg* setting is higher than the default *Over Temp Chg* because Li-lon can handle a higher temperature in the discharge direction than in the charge direction.

# OT Dsg Time

See *Over Temp Dsg.* This is a buffer time allotted for Over Temperature in the discharge direction condition. The timer starts every time the [OTD] in *Safety Alert* is initially set. When the timer expires, then the bq20z80 forces an [OTD] in *Safety Status* and opens the Discharge FET if enabled with [OTFET] in Operation Cfg B. If [OTD] in *Safety Alert* clears (fault condition clears) prior to the expiration of the *OT Dsg Time* timer, then [OTD] in *Safety Alert* is cleared and the *OT Dsg Time* timer resets. Setting the *OT Chg Time* to 0 disables this function.

1st Level Safety www.ti.com

**Normal Setting:** This is normally set to 2 seconds which is sufficient for most applications. Temperature is normally a slow acting condition that does not need high speed triggering. It should be set long enough to prevent false triggering of the [OTD] in *Safety Status*, but short enough to prevent damage to the battery pack.

### OT Dsg Recovery

OT Dsg Recovery is the temperature at which the battery recovers from an OT Temp Dsg fault. This is the only recovery method for an OT Temp Dsg fault.

**Normal Setting:** This register is application dependent, but is normally set low enough below the fault condition temperature to prevent quick oscillation in the Discharge FET if it was opened with the fault. The default is 55°C which is a 5 degrees difference which is sufficient to protect against this oscillation during the transition between conditions.

### 2.4 Host Comm

### Host Watchdog Timeout

This function is only active when the bq20z80 is in Normal Power Mode (not asleep or in shutdown mode). It is also disabled if set to 0. If there is no communication to the bq20z80 via the SMBus for Host Watchdog Timeout time in seconds, then the bq20z80 reports [HWDG] set in Safety Status and opens the Charge, Discharge, and Pre-Charge FETs if enabled. This fault causes [TCA] and [TDA] in Battery Status to be set., and [XDSG] in Operation Status to be set. It also causes Charging Current and Charging Voltage to be set to 0. It is difficult to monitor this function because any SMBus communication clears the fault condition. To monitor the function using SMBus, then the SMBus command that is used to clear the fault condition must be an SMBus read of Safety Status. The [HWDG] flag is set on this read. Then on the next read (if its within the Host Watchdog Timeout window) the [HWDG] flag is cleared. The [HWDG] flag in Safety Alert as displayed in the EV Software is not used in this algorithm, and serves no purpose.

**Normal Setting:** This is not a common function and its default setting is 0. This provides another method for turning off the FETs, and preventing charge or discharge because the corresponding FETs are turned off when the fault occurs. It is also important to note that if the *Host Watchdog Timeout* is less than the *Bus Low Time*, then the fault condition occurs prior to the *Bus Low Timeout* which normally occurs prior to going to sleep. This function is disabled when in sleep mode, and the bq20z80 detects going to sleep mode as soon as the *Bus Low Timeout* expires. So, if the *Host Watchdog Timeout* timer expires prior to detecting bus low, then it triggers this fault.

www.ti.com 2<sup>nd</sup> Level Safety

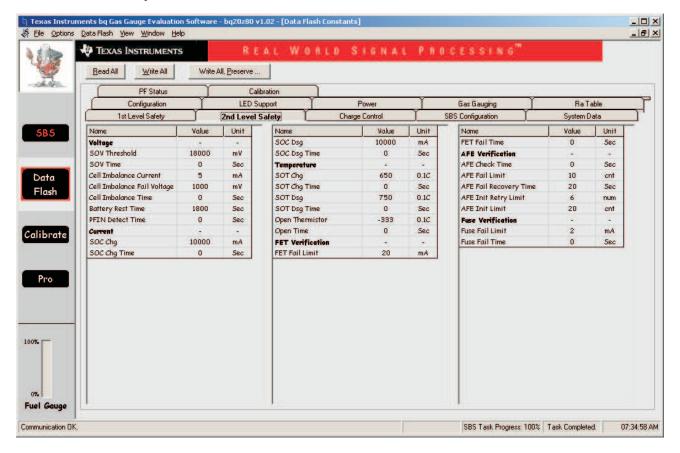

# 3 2<sup>nd</sup> Level Safety

# 3.1 Voltage

SOV Threshold

This is a final level of protection. It is permanent. When the pack voltage measured by **Voltage** rises to this threshold, then the Safety Over Voltage (SOV) protection process is triggered. This process starts by setting [SOV] in **PF Alert** for SOV Time. If the SOV condition clears prior to the expiration of the SOV Time timer, then the [SOV] is cleared in **PF Alert**, and no [SOV] is set in **PF Status**. If the SOV condition does not clear, then [SOV] is set in **PF Status**. This triggers many permanent protection features as listed here:

- 1. The Charge FET, Discharge FET, and Pre-Charge FET are all opened.

- 2. [TCA] and [TDA] in **Battery Status** is set

- 3. Charging Current and Charging Voltage is set to 0.

- 4. Data Flash Writes is disabled

- 5. if [XSOV] in Permanent Fail Cfg, then

- 0x3672 is programmed to the Fuse Flag.

- The Safety Output pins are activated which is intended to blow a fuse.

- 6. All the remaining data flash registers in the **PF Status** class are filled with backups of many of the SBS data set registers and AFE data.

**Normal Setting:** This is the last level of protection and must be set to a voltage above the POV Threshold. This is meant to be a permanent condition, and it is recommended that [XSOV] be set in *Permanent Fail Cfg* with a fuse designed into the application. There is a clear function for this condition, but it is only intended to be used during the development process.

2<sup>nd</sup> Level Safety www.ti.com

### SOV Time

See *SOV Threshold*. This is a buffer time allotted for an SOV condition. The timer starts after [SOV] is set in *PF Alert*. When it expires, then the bq20z80 forces an [SOV] in *PF Status* and opens the Charge FET Discharge FET and Pre-Charge FET if they were on. If the condition clears prior to the expiration of the *SOV Time* timer, then [SOV] is cleared in *PF Alert*, and the *SOV Time* timer resets without setting [SOV] in *PF Status*. If *SOV Time* is 0, then the *SOV Threshold* function is disabled.

**Normal Setting:** This register defaults to 0 only for the development process. This function must not be left at 0. Enabling this function in the final application is recommended. The most common values for this register are between 2–5 seconds.

### Cell Imbalance Current

This is part of the safety cell imbalance detection algorithm. There are 4 registers that go together to make up this algorithm. *Cell Imbalance Current* is the value that *Current* must be below for the entire *Battery Rest Time* before Cell Imbalance detection is enabled. The bq20z80 does not start detecting a cell imbalance for this safety algorithm until the battery *Current* has been below this *Cell Imbalance Current* for at least the *Battery Rest Time*.

**Normal Setting:** This register should be set low to ensure the battery is completely relaxed when this algorithm is enabled. This Safety algorithm if triggered is permanent, and renders the battery useless. It is imperative that all data is valid prior to activation. The default setting is 5 mA which is sufficient for most applications.

### Cell Imbalance Fail Voltage

This is part of the safety cell imbalance detection algorithm. For the purpose of this description:

**Cell Voltage H** = the highest SBS cell voltage

Cell Voltage L = the lowest SBS cell voltage

Delta Cell Voltage = Cell Voltage H - Cell Voltage L

There are 4 registers that go together to make up this algorithm. After the *Battery Rest Time* portion of the Cell Imbalance algorithm has passed the test criteria (see *Battery Rest Time* and *Cell Imbalance Current*), then if *Delta Cell Voltage* is greater than the *Cell Imbalance Fail Voltage* in millivolts, then the *Cell Imbalance Fail Voltage* protection process is triggered. This process starts by setting [CIM] in *PF Alert* for *Cell Imbalance Time*. If the cell imbalance condition clears prior to the expiration of the *Cell Imbalance Time* timer, then the [CIM] is cleared in *PF Alert* with no [CIM] being set in *PF Status*. If the cell imbalance condition does not clear, then [CIM] is set in *PF Status*. This triggers many permanent protection features as listed here:

- 1. The Charge FET, Discharge FET, and Pre-Charge FET are all opened.

- 2. [TCA] and [TDA] in Battery Status is set

- 3. Charging Current and Charging Voltage is set to 0.

- 4. Data Flash Writes is disabled

- 5. if [XCIM] in Permanent Fail Cfg then

- 0x3672 is programmed to the Fuse Flag.

- The Safety Output pins are activated which is intended to blow a fuse.

- 6. All the remaining data flash registers in the **PF Status** class are filled with backups of many of the SBS data set registers and AFE data.

**Normal Setting:** This is the last level of protection and must be set to a voltage high enough to prevent any possibility of false triggering because this application is irreversible. This is meant to be a permanent condition and it is recommended that [XCIM] be set in Permanent Fail Cfg with a fuse designed into the application. There is a clear function for this condition, but it is only intended to be used during the development process.

www.ti.com 2<sup>nd</sup> Level Safety

# Cell Imbalance Time

See Cell Imbalance Fail Voltage. This is a buffer time allotted for a cell imbalance safety condition. The timer starts after the Battery Rest Time has expired with current below the Cell Imbalance Current and Delta Cell Voltage (see Cell Imbalance Fail Voltage) is above the Cell Imbalance Fail Voltage. When the Cell Imbalance Time timer starts [CIM] is set in PF Alert. When the timer expires, then the bq20z80 forces a [CIM] in PF Status and opens the Charge FET Discharge FET and Pre-Charge FET if they were on. If the condition clears prior to the expiration of the Cell Imbalance Time timer, then [CIM] is cleared in PF Alert, and the Cell Imbalance Time timer resets without setting [CIM] in PF Status. The Cell Imbalance Fail Voltage function is disabled with Cell Imbalance Time equal to 0 or Battery Rest Time set to 0.

**Normal Setting:** This register defaults to 0. This disables the function. It is recommended that this function be enabled and the [XCIM] be enabled in *Permanent Failure Cfg* to protect against a potentially dangerous condition. *Battery Rest Time* helps prevent false triggering of this condition, so a good setting for Cell imbalance Time is 5 seconds. This gives several readings to ensure that the condition does exist.

## Battery Rest Time

See Cell Imbalance Current. Battery Rest Time is the time in seconds that the battery **Current** must be below the Cell Imbalance Current for before Cell Imbalance detection is enabled. The bq20z80 does not start detecting a cell imbalance for this safety algorithm until the battery **Current** has been below Cell Imbalance Current for at least the Battery Rest Time. The Cell Imbalance Fail Voltage function is disabled with Cell Imbalance Time equal to 0 or Battery Rest Time set to 0.

**Normal Setting:** This register should be set for a relatively long time period to ensure the battery is completely relaxed when this algorithm is enabled. This safety algorithm, if triggered, is permanent and renders the battery useless. It is imperative that all data is valid prior to activation. The default setting is 1800 seconds which is sufficient for most applications.

### PFIN Detect Time

This is a buffer time allotted for an PFIN safety condition. The timer *PFIN Detect Time* timer starts after the PFIN input pin has been set logic low by some external device (normally an external protector) which forces the [PFIN] is set in *PF Alert*. When it expires, then the bq20z80 forces an [PFIN] in *PF Status* and opens the Charge FET Discharge FET and Pre-Charge FET if they were on. If the condition clears prior to the expiration of the *PFIN Detect Time* timer, then [PFIN] is cleared in *PF Alert*, and the *PFIN Detect Time* timer resets without setting [PFIN] in *PF Status*. If *PFIN Detect Time* is 0, then this function is disabled. This fault condition triggers many permanent protection features as listed here:

- The Charge FET, Discharge FET, and Pre-Charge FET are all opened.

- 2. [TCA] and [TDA] in Battery Status is set

- 3. Charging Current and Charging Voltage is set to 0.

- 4. Data Flash Writes is disabled

- 5. if [XPFIN] in Permanent Fail Cfg then

- 0x3672 is programmed to the Fuse Flag.

- The Safety Output pins are activated which is intended to blow a fuse.

- 6. All the remaining data flash registers in the **PF Status** class are filled with backups of many of the SBS data set registers and AFE data.

**Normal Setting:** If this fault condition occurs then it is because an external device has already triggered a fault that should be nonrecoverable. This is meant to be a permanent condition, and it is recommended that [XPFIN] be set in *Permanent Fail Cfg.* If a fault occurs, and the external device sets the  $\overline{\text{PFIN}}$  input low, the fuse will blow. If the fuse does not blow, then the bq20z80 attempts to blow the fuse (SAFE pin is set high and  $\overline{\text{SAFE}}$  pin is driven low on the bq20z80). There is a clear function for this condition, but it is only intended to be used during the development process. The default for this function is 0. If the  $\overline{\text{PFIN}}$  input is not used, then this function should be disabled. It is recommended that this function be used, and that [XPFIN] be set to ensure safe operation

2<sup>nd</sup> Level Safety www.ti.com

### 3.2 Current

### SOC Chg

SOC Chg is a final level of current protection from the bq20z80. This is not related to the 3<sup>rd</sup> level (AFE) protection which is a fast acting protection. It is also intended to be permanent. When the charge current as measured by *Current* rises to or above this threshold, then the Safety Over Current in the Charge direction (SOCC) protection process is triggered. This process starts by setting [SOCC] in *PF Alert* for *SOC Chg Time*. If the SOCC condition clears prior to the expiration of the *SOC Chg Time* timer, then the [SOCC] is cleared in *PF Alert* and with no [SOCC] being set in *PF Status*. If the SOC condition does not clear, then [SOCC] is set in *PF Status*. This triggers many permanent protection features:

- 1. The Charge FET, Discharge FET, and Pre-Charge FET ware all opened.

- 2. [TCA] and [TDA] in Battery Status is set

- 3. Charging Current and Charging Voltage is set to 0.

- 4. Data Flash Writes is disabled

- 5. if [XSOCC] in Permanent Fail Cfg then

- 0x3672 is programmed to the Fuse Flag.

- The Safety Output pins is activated which is intended to blow a fuse.

- 6. All the remaining data flash registers in the **PF Status** class is filled with backups of many of the SBS data set registers and AFE data.

**Normal Setting:** This is the last level of protection and should be set to a current above  $OC(2^{nd}Tier)$  Chg. It is not necessarily required to set above AFE OC Chg which is a fast acting fault condition meant for high current spike detection. This function is meant to be a permanent condition, and it is recommended that [XSOCC] be set in *Permanent Fail Cfg* with a fuse designed into the application. There is a clear function for this condition, but it is only intended to be used during the development process.

# SOC Chg Time

See SOC Chg. This is a buffer time allotted for an SOCC condition. The timer starts after [SOCC] is set in **PF Alert**. When it expires, then the bq20z80 forces an [SOCC] in **PF Status**, and opens the Charge FET Discharge FET and Pre-Charge FET if they were on. If the condition clears prior to the expiration of the SOC Chg Time timer, then [SOCC] is cleared in **PF Alert**, and the SOC Chg Time timer resets without setting [SOCC] in **PF Status**. If SOC Chg Time is 0 then this function is disabled.

**Normal Setting:** This register defaults to 0 only for the development process. This function should not be left at 0. Enabling this function in the final application is recommended. The most common values for this register are between 2-5 seconds.

# SOC Dsg

SOC Dsg is a final level of current protection from the bq20z80. This is not related to the 3<sup>rd</sup> level (AFE) protection which is a fast acting protection. It is also intended to be permanent. When the discharge current as measured by *Current* falls **down** to or **below** a negative of this threshold ( – (SOC Dsg)), then the Safety Over Current in the discharge direction (SOCD) protection process is triggered. This process starts by setting [SOCD] in *PF Alert* for *SOC Dsg Time*. If the SOCC condition clears prior to the expiration of the *SOC Dsg Time* timer, then the [SOCD] is cleared in *PF Alert* with no [SOCC] being set in *PF Status*. If the SOC condition does not clear, then [SOCD] is set in *PF Status*. This triggers many permanent protection features:

- 1. The Charge FET, Discharge FET, and Pre-Charge FET are all opened.

- 2. [TCA] and [TDA] in Battery Status is set

- 3. Charging Current and Charging Voltage is set to 0.

- 4. Data Flash Writes is disabled

- 5. if [XSOCD] in Permanent Fail Cfg then

- 0x3672 is programmed to the Fuse Flag.

- The Safety Output pins are activated which is intended to blow a fuse.

- 6. All the remaining data flash registers in the **PF Status** class are filled with backups of many of the SBS data set registers and AFE data.

www.ti.com 2<sup>nd</sup> Level Safety

**Normal Setting:** Care must taken when interpreting discharge descriptions in this document when interpreting the direction and magnitude of the currents because they are in the negative direction. This is the last level of protection and must be set to a current below  $OC(2^{nd}Tier)$  Dsg. It is not required to set above AFE OC Dsg which is a fast acting fault condition meant for high current spike detection. This is meant to be a permanent condition and it is recommended that [XSOCD] be set in *Permanent Fail Cfg* with a fuse designed into the application. There is a clear function for this condition, but it is only intended to be used during the development process.

### SOC Dsg Time

See *SOC Dsg.* This is a buffer time allotted for an SOCD condition. The timer starts after [SOCD] is set in *PF Alert.* When it expires, then the bq20z80 forces an [SOCD] in *PF Status* and opens the Charge FET Discharge FET and Pre-Charge FET if they were on. If the condition clears prior to the expiration of the *SOC Dsg Time* timer, then [SOCD] is cleared in *PF Alert*, and the *SOC Dsg Time* timer resets without setting [SOCD] in *PF Status*. If *SOC Dsg Time* is 0, then this function is disabled.

Normal Setting: This register defaults to 0 only for the development process. This function must not be left at 0. Enabling this function in the final application is recommended. The most common values for this register are between 2–5 seconds.

# 3.3 Temperature

# SOT Chg

SOT Chg is a final level of temperature protection from the bq20z80. This fault condition is intended to be permanent. When the temperature as measured by **Temperature** rises to or above this threshold while charging ([DSG] cleared in **Battery Status**), then the Safety Over Temperature in the Charge direction (SOTC) protection process is triggered. This process starts by setting [SOTC] in **PF Alert** for SOT Chg Time. If the SOTC condition clears prior to the expiration of the SOT Chg Time timer, then the [SOTC] is cleared in **PF Alert** and with no [SOTC] being set in **PF Status**. If the SOT condition does not clear, then [SOTC] is set in **PF Status**. This triggers many permanent protection features:

- 1. The Charge FET, Discharge FET, and Pre-Charge FET ware all opened.

- 2. [TCA] and [TDA] in Battery Status is set

- 3. **Charging Current** and **Charging Voltage** is set to 0.

- 4. Data Flash Writes is disabled

- 5. if [XSOTC] in Permanent Fail Cfg then

- 0x3672 is programmed to the Fuse Flag.

- The Safety Output pins are activated which is intended to blow a fuse.

- 6. All the remaining data flash registers in the **PF Status** class is filled with backups of many of the SBS data set registers and AFE data.

**Normal Setting:** This is the last level of protection and must be set to a temperature above *Over Temp Chg.* This is meant to be a permanent condition and it is recommended that [XSOTC] be set in *Permanent Fail Cfg* with a fuse designed into the application. There is a clear function for this condition, but it is only intended to be used during the development process.

### SOT Chg Time

See *SOT Chg.* This is a buffer time allotted for a Safety Over Temperature Condition. The timer starts after [SOTC] is set in *PF Alert*. When it expires, then the bq20z80 forces an [SOTC] in *PF Status* and opens the Charge FET Discharge FET and Pre-Charge FET if they were on. If the condition clears prior to the expiration of the *SOT Chg Time* timer, then [SOTC] is cleared in *PF Alert*, and the *SOT Chg Time* timer resets without setting [SOTC] in *PF Status*. If *SOT Chg Time* is 0 then this function is disabled.

**Normal Setting:** This register defaults to 0 only for the development process. This function should not be left at 0. Enabling this function in the final application is recommended. The most common values for this register are between 2–5 seconds.

2<sup>nd</sup> Level Safety www.ti.com

### SOT Dsg

SOT Dsg is a final level of temperature protection from the bq20z80. This fault condition is intended to be permanent. When the temperature as measured by **Temperature** rises to or above this threshold while discharging ([DSG] set in **Battery Status**), then the Safety Over Temperature in the discharge direction (SOTD) protection process is triggered. This process starts by setting [SOTD] in **PF Alert** for SOT Dsg Time. If the SOTD condition clears prior to the expiration of the SOT Dsg Time timer, then the [SOTD] is cleared in **PF Alert** and with no [SOTD] being set in **PF Status**. If the SOT condition does not clear then [SOTD] is set in **PF Status**. This triggers many permanent protection features:

- 1. The Charge FET, Discharge FET, and Pre-Charge FET are all be opened.

- 2. [TCA] and [TDA] in Battery Status is set

- 3. Charging Current and Charging Voltage is set to 0.

- 4. Data Flash Writes is disabled

- 5. if [XSOTD] in Permanent Fail Cfg then

- 0x3672 is programmed to the Fuse Flag.

- The Safety Output pins are activated which is intended to blow a fuse.

- 6. All the remaining data flash registers in the **PF Status** class is filled with backups of many of the SBS data set registers and AFE data.

**Normal Setting:** This is the last level of protection and must be set to a temperature above *Over Temp Chg.* This is meant to be a permanent condition, and it is recommended that [XSOTC] be set in *Permanent Fail Cfg* with a fuse designed into the application. There is a clear function for this condition, but it is only intended to be used during the development process.

### SOT Dsg Time

See *SOT Dsg.* This is a buffer time allotted for a Safety Over Temperature Condition. The timer starts after [SOTD] is set in *PF Alert*. When it expires, then the bq20z80 forces an [SOTD] in *PF Status* and opens the Charge FET Discharge FET and Pre-Charge FET if they were on. If the condition clears prior to the expiration of the *SOT Dsg Time* timer, then [SOTD] is cleared in *PF Alert*, and the *SOT Dsg Time* timer resets without setting [SOTD] in *PF Status*. If *SOT Dsg Time* is 0 then this function is disabled.

**Normal Setting:** This register defaults to 0 only for the development process. This function must not be left at 0. Enabling this function in the final application is recommended. The most common values for this register are between 2–5 seconds.

### Open Thermistor

Setting *Open Thermistor Time* to 0 disables this function. The *Open Thermistor* register is part of a thermistor circuit fault protection algorithm in the bq20z80 that detects an open circuit in the thermistor circuit because *Temperature* reaches impossible values due to open circuit ADC readings. This fault condition is intended to be permanent. When the temperature as measured by *Temperature* falls to or below this threshold, then the Open Thermistor protection process is triggered. This process starts by setting [OTS] in *PF Alert* for *Open Thermistor Time*. If the OTS condition clears prior to the expiration of the Open Thermistor Time timer, then the [OTS] is cleared in *PF Alert* and with no [SOTS] being set in *PF Status*. If the OTS condition does not clear, then [OTS] is set in *PF Status*. This triggers many permanent protection features:

- 1. The Charge FET, Discharge FET, and Pre-Charge FET are all opened.

- 2. [TCA] and [TDA] in Battery Status is set

- 3. Charging Current and Charging Voltage is set to 0.

- 4. Data Flash Writes is disabled

- 5. if [XOTS] in Permanent Fail Cfg then

- 0x3672 is programmed to the Fuse Flag.

- The Safety Output pins are activated which is intended to blow a fuse.

- 6. All the remaining data flash registers in the **PF Status** class is filled with backups of many of the SBS data set registers and AFE data.

www.ti.com 2<sup>nd</sup> Level Safety

**Normal Setting:** This function is a good safety feature that is particularly useful in detecting thermistors that have come loose from the Gas Gauge PCB during the assembly process or if the wire of a thermistor comes lose from vibration. The value in this register does not need to be changed. This is meant to be a permanent condition, and it is recommended that [XOTS] be set in *Permanent Fail Cfg* with a fuse designed into the application. There is a clear function for this condition, but it is only intended to be used during the development process.

### Open Thermistor Time

See *Open Thermistor*. This is a buffer time allotted for an Open Thermistor Condition. The timer starts after [OTS] is set in *PF Alert*. When it expires, then the bq20z80 forces [OTS] set in *PF Status* and opens the Charge FET, Discharge FET, and Pre-Charge FET if they were on. If the condition clears prior to the expiration of the *Open Thermistor Time* timer, then [OTS] is cleared in *PF Alert*, and the *Open Thermistor Time* timer resets without setting [OTS] in *PF Status*. If *Open Thermistor Time* is 0 then the *Open Thermistor* function is disabled.

**Normal Setting:** This register defaults to 0 only for the development process. This function should not be left at 0. Enabling this function in the final application is recommended. The most common values for this register are between 2–5 seconds.

# 3.4 FET Verification

### FET Fail Limit

FET Fail Limit register is part of a FET circuit fault protection algorithm in the bq20z80 that detects potentially hazardous FET circuit damage. This fault condition is intended to be permanent, and has two possible trigger functions to help prevent confusion. The functions are listed separately.

- (A) If the Charge and Pre-Charge FET (if enabled) have been commanded to be off for any reason by either the bq20z80 or the bq29312A (any AFE fault condition) and charge current as measured by *Current* still exists which is greater than *FET Fail Limit* in milliamps, then the *FET Fail Limit* protection process is triggered. This process starts by setting [CFETF] in *PF Alert* for *FET Fail Time*. If the [CFETF] condition clears prior to the expiration of the *FET Fail Time* timer, then the [CFETF] is cleared in *PF Alert* and no [CFETF] is set in *PF Status*. If the [CFETF] condition does not clear, then [CFETF] is set in *PF Status*. This triggers many permanent protection features as listed below:

- (B) If the discharge FET has been commanded to be off for any reason by either the bq20z80 or the bq29312A (any AFE fault condition) and discharge current as measured by *Current* still exists which is less than or equal to (–) *FET Fail Limit* in milliamps, then the *FET Fail Limit* protection process is triggered. This process starts by setting [DFETF] in *PF Alert* for *FET Fail Time*. If the [DFETF] condition clears prior to the expiration of the *FET Fail Time* timer, then the [DFETF] is cleared in *PF Alert* and no [DFETF] is set in *PF Status*. If the [DFETF] condition does not clear, then [DFETF] is set in *PF Status*. This triggers many permanent protection features as listed below:

Each of the above triggers (A. and B.) cause the following permanent protection features:

- 1. The Charge FET, Discharge FET, and Pre-Charge FET are all opened.

- 2. [TCA] and [TDA] in Battery Status is set

- 3. Charging Current and Charging Voltage is set to 0.

- 4. Data Flash Writes is disabled

- 5. if A and [XCFETF] or B and [XDFETF] in Permanent Fail Cfg then

- 0x3672 is programmed to the Fuse Flag.

- The Safety Output pins is activated which is intended to blow a fuse.

- 6. All the remaining data flash registers in the **PF Status** class is filled with backups of many of the SBS data set registers and AFE data.

2<sup>nd</sup> Level Safety www.ti.com

**Normal Setting:** The Charge and Discharge FETs arguably have more stress than any other component on the gas gauge PCB. This function is an excellent safety feature to help protect against the possibility of a shorted FET that is potentially hazardous. The default value in this register must be sufficient for most applications. This is meant to be a permanent condition, and it is recommended that [XCFETF] and [XDFETF] both be set in *Permanent Fail Cfg* with a fuse designed into the application. There is a clear function for this condition, but it is only intended to be used during the development process.

### FET Fail Time

See *FET Fail Limit*. This is a buffer time allotted for the *FET Fail Limit* condition. The timer starts after either [CFETF] or [DFETF] set in *PF Alert*. When the timer expires, then the bq20z80 forces the associated flag (either [CFETF] or [DFETF]) in *PF Status* and opens the Charge FET, Discharge FET, and Pre-Charge FET if they were on. If the condition clears prior to the expiration of the *FET Fail Time* timer, then the associated flag (either [CFETF] or [DFETF]) is cleared in *PF Alert*, and the *FET Fail Time* timer resets without setting the associated flag (either [CFETF] or [DFETF]) in *PF Status*. If *FET Fail Time* is 0 then this function is disabled.

**Normal Setting:** This register defaults to 0 only for the development process. This function should not be left at 0. Enabling this function in the final application is recommended. The most common values for this register are between 2–5 seconds.

### 3.5 AFE Verification

### AFE Check Time

Every *AFE Check Time* in seconds, the bq20z80 reads all the bq29312A registers through the I<sup>2</sup>C port that is shared between the 2 parts and compares the static register read results to the AFE data in the bq20z80's Data Flash. If they do not match, then the bq20z80 attempts to repair the corruption. Then increment an internal counter (referred to in this document as AFE\_P Fail Counter) which triggers the periodic AFE\_P Fail protection process. This process starts by setting [AFE\_P] in *PF Alert*. As long as the AFE\_P Fail Counter stays below the *AFE Fail Limit* and above 0, [AFE\_P] stays set in *PF Alert*. See *AFE Recovery Time* for a recovery description. If *AFE Check Time* is set to 0, then the periodic AFE verification (AFE\_P) is completely disabled.

**Normal Setting:** Setting **AFE Check Time** to 0 only disables the AFE\_P verification function. It does not disable the AFE\_C verification function as described in *AFE Fail Limit. AFE Check Time* set to 0 is acceptable because there is still the AFE\_C verification process. If, however, AFE Check Time is used, set it above 20 seconds since the periodic test does not need to be done often to ensure the correct function.

### AFE Fail Limit

There are 2 AFE safety features that use this register. They is separated here to help prevent confusion.

- (A) The first safety feature is a continuation of AFE Check Time. If the AFE\_P Fail Counter (as described above) reaches the AFE Fail Limit then [AFE\_P] is cleared in PF Alert, and then set in PF Status. Setting AFE Fail Limit to 0 does not disable the periodic AFE verification (AFE\_P). (See AFE Check Time)

- (B) The second safety feature is not associated with *AFE Check Time*. Anytime a communication with the bq29312A is performed over the I<sup>2</sup>C bus that is not part of the periodic check described in *AFE Check Time*, then a different internal counter (referred to in this document as AFE\_C Fail Counter) increments. When the AFE\_C Fail Counter increments, the AFE\_C Fail protection process is triggered. This process starts by setting [AFE\_C] in *PF Alert*. As long as the AFE\_C Fail Counter stays below the *AFE Fail Limit* and above 0, then [AFE\_C] stays set in *PF Alert*. See *AFE Recovery Time* for a recovery description. If the AFE\_C Fail Counter reaches the *AFE Fail Limit*, then [AFE\_C] is cleared in *PF Alert*, and then set in *PF Status*. Setting *AFE Fail Limit* to 0 disables the AFE\_C Fail protection process.

Each of the above triggers (A. and B.) cause the following permanent protection features:

- 1. The Charge FET, Discharge FET, and Pre-Charge FET are all opened.

- 2. [TCA] and [TDA] in Battery Status is set

- 3. Charging Current and Charging Voltage is set to 0.

- 4. Data Flash Writes is disabled

www.ti.com 2<sup>nd</sup> Level Safety

- 5. if A. [XAFE\_P] set or if B and [XAFE\_C] set in Permanent Fail Cfg then

- 0x3672 is programmed to the Fuse Flag.

- The Safety Output pins are activated which is intended to blow a fuse.

- All the remaining data flash registers in the PF Status class is filled with backups of many of the SBS data set registers and AFE data.

**Normal Setting:** AFE Fail Limit defaults to 10. It is very important to note that setting AFE Fail Limit to 0 only disables the AFE\_C functions. AFE\_P functions are not disabled with the AFE Fail Limit set to 0. This results in [AFE\_P] flag getting set in **PF Status** on the first failure which is not recommended. The default of 10 is appropriate for most applications. This gives sufficient buffer for ESD, resets and other unknown failures that should be recoverable.

# AFE Fail Recovery Time

See AFE Check Time and AFE Fail Limit. AFE Fail Recovery Time function works independently with each of the AFE counters described above (AFE\_C Fail Counter and AFE\_P Fail Counter). While [AFE\_C] or [AFE\_P] is set in **PF\_Alert**, every AFE Fail Recover Time period in seconds AFE\_C Fail Counter and/or AFE\_P Fail Counter is decremented by 1 until each reaches 0. As soon as they are decremented back to 0, their associated flags ( [AFE\_C] or [AFE\_P]) are cleared in **PF Alert**, and the fault process is reversed.

**Normal Setting:** It is recommended that this register be set less than *AFE Check Time*, so that at least one recovery process can occur between periodic checks. *AFE Init Retry Limit*