# Application Brief High-Frequency Delay Adjustments Between Two RF Synthesizers

TEXAS INSTRUMENTS

Narala Reddy

Clock and Timing Solutions

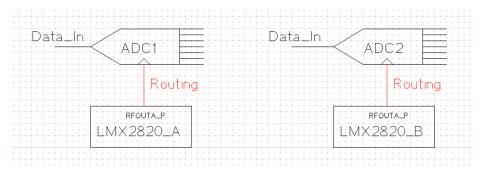

LMX2820 is RF synthesizer part, which can generate frequencies upto 22.6GHz at the output. This high frequency clock is used to clock ADC for sampling purpose. When clocking two ADCs from each of LMX2820, there could be some delay between sampling clock rising instants due to non-symmetrical routing. This non-zero delay between sampling clock rising instants can be adjusted using one of the two RF synthesizer MASH\_SEED option. This option works till the maximum frequency of 22.6GHz. As showing in figure Figure 1, Clocks generated from LMX2820\_A and LMX2820\_B to ADC1 and ADC2 respectively might have some skew between rising edges due to non-symmetrical routing. Depending on the applications, clock frequency can go as high as 20GHz. So, adjusting clock skew to zero becomes critical.

Figure 1. LMX2820 Clock Driving Two Independent ADCs

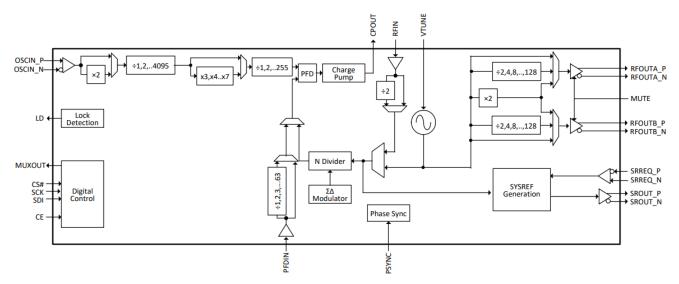

In general, PLLs are operated in fractional mode in multiple MASH orders namely first, second and third order. Functional block diagram of 2820 Synthesizer is shown in Figure 2.

Figure 2. Functional Block Diagram

1

Delta-Sigma Modulator modulates the N Divider input based on the mash order used. Higher the mash order, higher the variation in clock periods coming out of N Divider. Following table shows the period variation at the output of N Divider. Ex: 0 means divide by N, 1 means divide by N+1. Seed means MASH\_SEED(R41 and R42) and MASH\_SEED\_EN has to be made 1. Always program MASH\_SEED to be less than Denominator. Consider an example where Numerator = 9 and Denominator = 21. So, Fraction is 0.428571429.

|                                                  | 1 <sup>st</sup> Order |        |        | 2 <sup>nd</sup> Order |        | 3 <sup>rd</sup> Order |        |

|--------------------------------------------------|-----------------------|--------|--------|-----------------------|--------|-----------------------|--------|

|                                                  | Clock Edge            | 2820_A | 2820_B | 2820_A                | 2820_B | 2820_A                | 2820_B |

|                                                  | 1                     | 0      | 0      | 0                     | 0      | 0                     | 0      |

|                                                  | 2                     | 0      | 0      | 0                     | 0      | 0                     | 0      |

| Seed = 0 for<br>2820_A and 0<br>for 2820_B       | 3                     | 1      | 1      | 1                     | 1      | 1                     | 1      |

|                                                  | 4                     | 0      | 0      | 0                     | 0      | 0                     | 0      |

|                                                  | 5                     | 1      | 1      | 1                     | 1      | 1                     | 1      |

|                                                  | 6                     | 0      | 0      | 0                     | 0      | 0                     | 0      |

|                                                  | 7                     | 1      | 1      | 1                     | 1      | 1                     | 1      |

| Seed = 3 for<br>2820_A<br>Seed = 0 for<br>2820_B | 8                     | 0      | 0      | 0                     | 0      | 0                     | 0      |

|                                                  | 9                     | 1      | 0      | 1                     | 0      | 1                     | 0      |

|                                                  | 10                    | 0      | 1      | 1                     | 1      | 1                     | 1      |

|                                                  | 11                    | 0      | 0      | -1                    | 0      | 0                     | 0      |

|                                                  | 12                    | 1      | 1      | 2                     | 1      | -1                    | 1      |

|                                                  | 13                    | 0      | 0      | -1                    | 0      | 3                     | 0      |

|                                                  | 14                    | 1      | 1      | 1                     | 1      | -2                    | 1      |

|                                                  | 15                    | 0      | 0      | 1                     | 0      | 2                     | 0      |

|                                                  | 16                    | 1      | 0      | 0                     | 0      | -1                    | 0      |

|                                                  | 17                    | 0      | 1      | 0                     | 1      | 2                     | 1      |

|                                                  | 18                    | 0      | 0      | 1                     | 0      | 0                     | 0      |

|                                                  | 19                    | 1      | 1      | 0                     | 1      | 0                     | 1      |

|                                                  | 20                    | 0      | 0      | 0                     | 0      | 1                     | 0      |

|                                                  | 21                    | 1      | 1      | 2                     | 1      | 0                     | 1      |

|                                                  | 22                    |        |        | -1                    | 0      | 0                     | 0      |

|                                                  | 23                    |        |        | 1                     | 0      | 1                     | 0      |

|                                                  | 24                    |        |        | 0                     | 1      | 0                     | 1      |

|                                                  | 25                    |        |        | 1                     | 0      | 1                     | 0      |

|                                                  | 26                    |        |        | 0                     | 1      | 1                     | 1      |

|                                                  | 27                    |        |        | 1                     | 0      | -1                    | 0      |

|                                                  | 28                    |        |        | 0                     | 1      | 1                     | 1      |

## Table 1. Sequence of MASH Output

Generalized formula for the delay when channel divider is not engaged(direct VCO) is as follows:

| Order                                           | Delay in degrees of output Frequency                       |  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------|--|--|--|--|

| 1 <sup>st</sup> Order                           | ( floor(SEED/GCD(NUM,DEN)) / (DEN/<br>GCD(NUM,DEN) ) × 360 |  |  |  |  |

| 2 <sup>nd</sup> Order and 3 <sup>rd</sup> Order | (SEED/DEN × 360)                                           |  |  |  |  |

#### Table 2. Delay Formula Based on MASH Order

### Example:

- For 1<sup>st</sup> order , when MASH\_SEED =1 and NUM/DEN = 9/21, there is not clock delay change addition. If MASH\_SEED = 1 is written thrice, then delay between clocks of 2820\_A and 2820\_B is (1/7) × 360 degrees.

- 2. For 2<sup>nd</sup> order and 3<sup>rd</sup> order, when MASH\_SEED =1 and NUM/DEN =9/21, then delay between clocks of 2820\_A and 2820\_B is (1/21) × 360 degrees.

Remember that movement in Clock rising edge due to MASH\_SEED depends on previous MASH\_SEED written.

3

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated