# Implementing DDR2 PCB Layout on the TMS320C6421

Michael R. Shust, Jeff Cobb

High Speed HW Productization

#### **ABSTRACT**

This application report contains implementation instructions for the DDR2 interface contained on the TMS320C6421 digital signal processor (DSP) device. The approach to specifying interface timing for the DDR2 interface is quite different than on previous devices.

The previous approach specified device timing in terms of data sheet specifications and simulation models. The system designer was required to obtain compatible memory devices, as well as the device-specific data sheets and simulation models. This information would then be used to design the printed circuit board (PCB) using high-speed simulation to close system timing.

For the C6421 DDR2 interface, the approach is to specify compatible DDR2 devices and provide the PCB routing rule solution directly. TI has performed the simulation and system design work to ensure DDR2 interface timings are met. This document describes the required routing rules.

The C6424 EVM provides an example of a PCB layout following these routing rules that passes FCC EMI requirements. You may copy the DDR2 portion of this layout directly, but the intent is to allow enough flexibility in the routing rules to meet other PCB requirements.

#### **Contents** 1 2 **List of Figures** 1 2 3 4 5 6 **List of Tables** 1 2 3 Placement Specifications 5 5 High-Speed Bypass Capacitors ..... 7 8 9 10 11 DQS and DQ Routing Specification

TMS320C6421 www.ti.com

### 1 TMS320C6421

#### 1.1 DDR2 Interface

This section provides the timing specification for the DDR2 interface as a PCB design and manufacturing specification. The design rules constrain PCB trace length, PCB trace skew, signal integrity, cross-talk, and signal timing. These rules, when followed, result in a reliable DDR2 memory system without the need for a complex timing closure process. For more information regarding guidelines for using this DDR2 specification, *Understanding TI's PCB Routing Rule-Based DDR2 Timing Specification* (SPRAAV0).

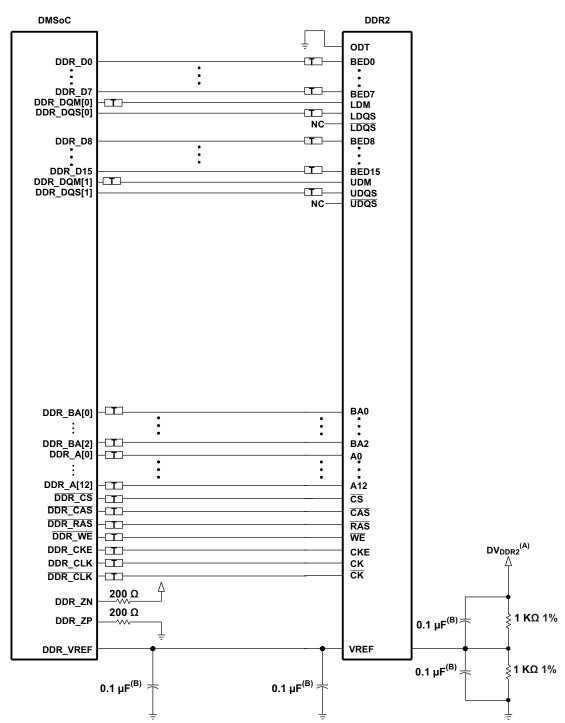

#### 1.1.1 DDR2 Interface Schematic

Table 2 shows the DDR2 interface schematic for a x16 DDR2 memory system. Pin numbers for the C6421 can be obtained from the pin description section of the *TMS320C6421 Fixed-Point Digital Signal Processor Data Manual* (SPRS346) and the DDR2 device pin numbers can be obtained from their device-specific data sheets.

# 1.2 Compatible JEDEC DDR2 Devices

Table 1 shows the parameters of the JEDEC DDR2 devices that are compatible with this interface. Generally, the DDR2 interface is compatible with x16 DDR2-400 speed grade DDR2 devices.

No. **Parameter** Min Max Unit **Notes** 1 JEDEC DDR2 Device Speed Grade DDR2-400 See Note (1) JEDEC DDR2 Device Bit Width x16 x16 Bits 3 JEDEC DDR2 Device Count 1 Device JEDEC DDR2 Device Ball Count 84 92 Balls See Note (2)

**Table 1. Compatible JEDEC DDR2 Devices**

## 1.3 PCB Stackup

The minimum stackup required for routing the C6421 is a six layer stack as shown in Table 2. Additional layers may be added to the PCB stack up to accommodate other circuity or to reduce the size of the PCB footprint.

Table 2. C6421 Minimum PCB Stack Up

| Layer | Туре   | Description                    |  |

|-------|--------|--------------------------------|--|

| 1     | Signal | Top Routing Mostly Horizontal  |  |

| 2     | Plane  | Ground                         |  |

| 3     | Plane  | Power                          |  |

| 4     | Signal | Internal Routing               |  |

| 5     | Plane  | Ground                         |  |

| 6     | Signal | Bottom Routing Mostly Vertical |  |

<sup>(1)</sup> Higher DDR2 speed grades are supported due to inherent JEDEC DDR2 backwards compatibility.

<sup>(2) 92</sup> ball devices retained for legacy support. New designs will migrate to 84 ball DDR2 devices. Electrrically the 92 and 84 ball DDR2 devices are the same.

www.ti.com TMS320C6421

NOTES:

- A. DV<sub>DDR2</sub> is the power supply for the DDR2 memory and DMSoC DDR2 interface.

- B. One of these capacitors can be eliminated if the divider and its capacitors are placed near a device VREF pin. Terminaror, if desired See terminato comments

Figure 1. C6421 16-Bit DDR2 High Level Schematic

See Note (1)

See Note (2)

See Note (3)

75

Z+5

Ω

Ω

TMS320C6421 www.ti.com

# 1.3.1 Minimizing PCB Area

The maximum placement and minimum PCB stackup uses the lowest cost PCB technology and generally results in the lowest unit cost PCB at the penalty of the largest footprint for the DDR2 interface. Customers need to evaluate the cost/benefit tradeoffs of smaller feature sizes and additional signal layers for their systems. Note that the minimum feature size and stackup may be limited by other circuitry on the PCB.

Complete stack up specifications are provided in Table 3.

No. **Parameter** Min Typ Max Unit **Notes** PCB Routing/Plane Layers 6 2 Signal Routing Layers 3 2 3 Full ground layers under DDR2 routing Region Number of ground plane cuts allowed within DDR routing region 4 0 5 Number of ground reference planes required for each DDR2 routing 6 Number of layers between DDR2 routing layer and reference ground 0 plane 7 PCB Routing Feature Size 4 Mils 8 PCB Trace Width w 4 Mils 8 18 Mils PCB BGA escape via pad size 9 PCB BGA escape via hole size 8 Mils

**Table 3. PCB Stack Up Specifications**

#### 1.3.2 Placement

10 11

12

13

DSP Device BGA pad size

DDR2 Device BGA pad size

Single Ended Impedance, Zo

Impedance Control

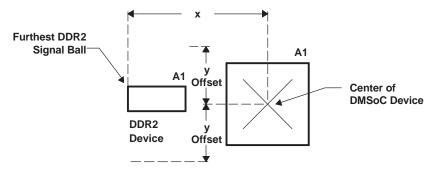

Figure 2 shows the required placement for the C6421 device as well as the DDR2 device. The dimensions for Figure 2 are defined in Table 4. The placement does not restrict the side of the PCB that the devices are mounted on. The ultimate purpose of the placement is to limit the maximum trace lengths and allow for proper routing space.

50

Z-5

Ζ

Maximum placement distances from center of DMSoC package to furthest DDR2 signal ball. Does not include distances to possible DDR2 NC outrigger balls. All dimensions in mils.

Figure 2. C6421 and DDR2 Device Placement Specification (16-bit connection)

<sup>(1)</sup> Please refer to the Flip Chip Ball Grid Array Package Reference Guide (SPRU811) for DSP device BGA pad size.

Please refer to the DDR2 device manufacturer documenation for the DDR2 device BGA pad size.

<sup>&</sup>lt;sup>(3)</sup> Z is the nominal singled ended impedance selected for the PCB specified by item 12.

www.ti.com TMS320C6421

| No. | Parameter                                             | Min | Max  | Unit | Notes               |

|-----|-------------------------------------------------------|-----|------|------|---------------------|

| 1   | X                                                     |     | 1750 | Mils | See Notes (1), (2)  |

| 2   | Υ                                                     |     | 1280 | Mils | See Notes (1), (2)  |

| 3   | Y Offset                                              |     | 700  | Mils | See Notes (1). (2), |

| 4   | DDR2 Keepout Region                                   |     |      |      | See Note (4)        |

| 5   | Clearance from non-DDR2 signal to DDR2 Keepout Region | 4   |      | w    | See Note (5)        |

<sup>(1)</sup> See Figure 2 for dimension defintions.

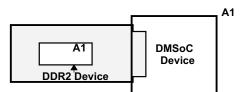

## 1.3.3 DDR2 Keep Out Region

The region of the PCB used for the DDR2 circuitry must be isolated from other signals. The DDR2 keep out region is defined for this purpose and is shown in Figure 3. The size of this region varies with the placement and DDR routing. Additional clearances required for the keep out region are shown in Table 4.

Region should encompass all DDR2 circuitry and varies depending on placement. Non-DDR2 signals should not be routed on the DDR signal layers within the DDR2 keep out region. Non-DDR2 signals may be routed in this region provided they are routed on layers separated from DDR2 signal layers by a ground layer. No breaks should be allowed in the reference ground layers in this region. In addition, the 1.8 V power plane should cover the entire keep out region.

Figure 3. Example DDR2 Keep Out Region

<sup>(2)</sup> Measurements from center of DSP device to center of DDR2 device.

<sup>(3)</sup> It is recommended that Y Offset be as small as possible.

<sup>(4)</sup> DDR2 Keepout region to encompass entire DDR2 routing area

<sup>(5)</sup> Non-DDR2 signals allowed within DDR2 keepout region provided they are separated from DDR2 routing layers by a ground plane.

TMS320C6421 www.ti.com

### 1.3.4 Bulk Bypass Capacitors

Bulk bypass capacitors are required for moderate speed bypassing of the DDR2 and other circuitry. Table 5 contains the minimum numbers and capacitance required for the bulk bypass capacitors. Note that this table only covers the bypass needs of the DSP and DDR2 interface. Additional bulk bypass capacitance may be needed for other circuitry.

**Table 5. Bulk Bypass Capacitors**

| No. | Parameter                                        | Min | Max | Unit    | Notes    |

|-----|--------------------------------------------------|-----|-----|---------|----------|

| 1   | DV <sub>DD18</sub> Bulk Bypass Capacitor Count   | 2   |     | Devices | See Note |

| 2   | DV <sub>DD18</sub> Bulk Bypass Total Capacitance | 44  |     | μF      |          |

| 3   | DDR Bulk Bypass Capacitor Count                  | 1   |     | Devices | See Note |

| 4   | DDR Bulk Bypass Total Capacitance                | 22  |     | μF      |          |

<sup>(1)</sup> These devices should be placed near the device they are bypassing, but preference should be given to the placement of the high-speed (HS) bypass caps.

## 1.3.5 High-Speed Bypass Capacitors

High-speed (HS) bypass capacitors are critical for proper DDR2 interface operation. It is particularly important to minimize the parasitic series inductance of the HS bypass cap, DSP/DDR power, and DSP/DDR ground connections. Table 6 contains the specification for the HS bypass capacitors as well as for the power connections on the PCB.

#### 1.3.6 Net Classes

Table 7 lists the clock net classes for the DDR2 interface. Table 8 lists the signal net classes, and associated clock net classes, for the signals in the DDR2 interface. These net classes are used for the termination and routing rules that follow.

Table 6. High-Speed Bypass Capacitors

| No. | Parameter                                                            | Min | Max  | Unit    | Notes        |

|-----|----------------------------------------------------------------------|-----|------|---------|--------------|

| 1   | HS Bypass Capacitor Package Size                                     |     | 0402 | 10 Mils | See Note (1) |

| 2   | Distance from HS bypass capacitor to device being bypassed           |     | 250  | Mils    |              |

| 3   | Number of connection vias for each HS bypass capacitor               | 2   |      | Vias    | See Note (2) |

| 4   | Trace length from bypass capacitor contact to connection via         | 1   | 30   | Mils    |              |

| 5   | Number of connection vias for each DDR2 device power or ground balls | 1   |      | Vias    |              |

| 6   | Trace length from DDR2 device power ball to connection via           |     | 35   | Mils    |              |

| 7   | DV <sub>DD18</sub> HS Bypass Capacitor Count                         | 8   |      | Devices | See Note (3) |

| 8   | DV <sub>DD18</sub> HS Bypass Capacitor Total Capacitance             | 0.8 |      | μF      |              |

| 9   | DDR HS Bypass Capacitor Count                                        | 8   |      | Devices | See Note (3) |

| 10  | DDR HS Bypass Capacitor Total Capacitance                            | 0.8 |      | μF      |              |

<sup>(1)</sup> LxW, 10 mil units, i.e., a 0402 is a 40x20 mil surface mount capacitor

<sup>(2)</sup> An additional HS bypass capacitor can share the connection vias only if it is mounted on the opposite side of the board.

<sup>(3)</sup> These devices should be placed as close as possible to the device being bypassed.

www.ti.com TMS320C6421

| Tahla 7   | Clock Not | Class | Definitions    |

|-----------|-----------|-------|----------------|

| I avic 1. | CIUCK NEL | Class | Dellillillolla |

| Clock Net Class | DSP Pin Names   |

|-----------------|-----------------|

| CK              | DDR_CLK/DDR_CLK |

| DQS0            | DDR_DQS0        |

| DQS1            | DDR_DQS1        |

**Table 8. Signal Net Class Definitions**

| Clock Net Class | Associated Clock Net Class | DSP Pin Names                                                                                                                                       |

|-----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR_CTRL       | CK                         | $\begin{array}{l} DDR\_BA[2:0],DDR\_A[12:0],\overline{DDR\_CS,\overline{DDR\_CAS},\overline{DDR\_RAS},\overline{DDR\_WE},} \\ DDR\_CKE \end{array}$ |

| DQ0             | DQS0                       | DDR_D[7:0], DDR_DQM0                                                                                                                                |

| DQ1             | DQS1                       | DDR_D[15:8], DDR_DQM1                                                                                                                               |

## 1.3.7 DDR2 Signal Termination

No terminations of any kind are required in order to meet signal integrity and overshoot requirements. Serial terminators are permitted, if desired, to reduce EMI risk; however, serial terminations are the only type permitted. Table 9 shows the specifications for the series terminators.

**Table 9. DDR2 Signal Terminations**

| No. | Parameter                                  | Min | Тур | Max | Unit | Notes          |

|-----|--------------------------------------------|-----|-----|-----|------|----------------|

| 1   | CK Net Class                               | 0   |     | 10  | Ω    | See Note (1)   |

| 2   | ADDR_CTRL Net Class                        | 0   | 22  | Zo  | Ω    | See Notes (1), |

| 3   | Data Byte Net Classes (DQS0-DQS1, DQ0-DQ1) | 0   | 22  | Zo  | Ω    | See Notes (1), |

Only series termination is permitted, parallel or SST specifically disallowed.

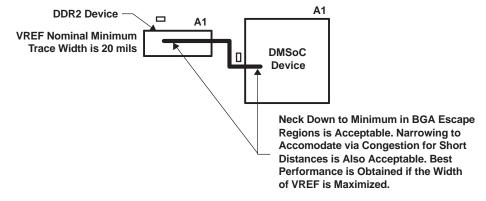

## 1.3.8 VREF Routing

VREF is used as a reference by the input buffers of the DDR2 memories as well as the C6421's. VREF is intended to be 1/2 the DDR2 power supply voltage and should be created using a resistive divider as shown in Figure 1. Other methods of creating VREF are not recommended. Figure 4 shows the layout guidelines for VREF.

Figure 4. VREF Specification 16-Bit Interface

<sup>(2)</sup> Terminator values larger than typical only recommended to address EMI issues.

<sup>(3)</sup> Termination value should be uniform across net class.

<sup>(4)</sup> When no termination is used on data lines (0 Ωs), the DDR2 device must be programmed to operate in 60% strength mode.

TMS320C6421 www.ti.com

# 1.3.9 DDR2 CK and ADDR\_CTRL Routing

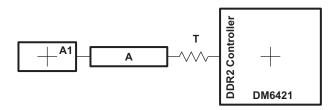

Figure 5 shows the topology of the routing for the CK and ADDR\_CTRL net classes.

Figure 5. CK and ADDR\_CTRL Routing and Topology

Table 10. CK and ADDR\_CTRL Routing Specification (1)

| No | Parameter                                                   | Min      | Тур   | Max      | Unit | N otes         |

|----|-------------------------------------------------------------|----------|-------|----------|------|----------------|

| 1  | Center to center CK-CK spacing                              |          |       | 2w       |      |                |

| 2  | Center to center CK to other DDR2 trace spacing             | 4w       |       |          |      | See Notes (2), |

| 3  | CK/ADDR_CTRL nominal trace length                           | CACLM-50 | CACLM | CACLM+50 | Mils | See Note (3)   |

| 4  | ADDR_CTRL to CK Skew Length Mismatch                        |          |       | 100      | Mils |                |

| 5  | ADDR_CTRL to ADDR_CTRL Skew Length Mismatch                 |          |       | 100      | Mils |                |

| 6  | Center to center ADDR_CTRL to other DDR2 trace spacing      | 4w       |       |          |      | See Note (2)   |

| 7  | Center to center ADDR_CTRL to other ADDR_CTRL trace spacing | 3w       |       |          |      | See Note (2)   |

<sup>(1)</sup> Series terminator, if used, should be located closest to DSP.

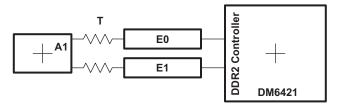

Figure 6 shows the topology and routing for the DQS and DQ net classes; the routes are point to point. Skew matching across bytes is not needed nor recommended.

Figure 6. DQS and DQ Routing and Toplogy

<sup>(2)</sup> Center to center spacing is allowed to fall to minimum (w) for up to 500 mils of routed length to accommodate BGA escape and routing congestion.

<sup>(3)</sup> CACLM is the longest Manhattan distance of the CK and ADDR\_CTRL net classes.

www.ti.com References

# Table 11. DQS and DQ Routing Specification (1)

| No. | Parameter                                        | Min         | Тур  | Max     | Unit | Notes                   |

|-----|--------------------------------------------------|-------------|------|---------|------|-------------------------|

| 1   | Center to center DQS-DQS spacing                 |             |      | 2w      |      |                         |

| 2   | DQS E Skew Length Mismatch                       |             |      | 25      | Mils |                         |

| 3   | Center to center DQS to other DDR2 trace spacing | 4w          |      |         |      | See Note (2)            |

| 4   | DQS/DQ nominal trace length                      | DQLM-<br>50 | DQLM | DQLM+50 | Mils | See Notes (1),          |

| 5   | DQ to DQS Skew Length Mismatch                   |             |      | 100     | Mils | See Note <sup>(3)</sup> |

| 6   | DQ to DQ Skew Length Mismatch                    |             |      | 100     | Mils | See Note <sup>(3)</sup> |

| 7   | Center to center DQ to other DDR2 trace spacing  | 4w          |      |         |      | See Notes (2),          |

| 8   | Center to Center DQ to other DQ trace spacing    | 3w          |      |         |      | See Note <sup>(2)</sup> |

| 9   | DQ/DQS E Skew Length Mismatch                    |             |      | 100     | Mils | See Note <sup>(3)</sup> |

<sup>(1)</sup> Series terminator, if used, should be located closest to DDR.

## 2 References

- Understanding TI's PCB Routing Rule-Based DDR2 Timing Specification (SPRAAV0)

- TMS320C6421 Fixed-Point Digital Signal Processor Data Manual (SPRS346)

- Flip Chip Ball Grid Array Package Reference Guide (SPRU811)

<sup>(2)</sup> Center to center spacing is allowed to fall to minimum (w) for up to 500 mils of routed length to accommodate BGA escape and routing congestion.

<sup>(3)</sup> There is no need and it is not recommended to skew match across data bytes, ie from DQS0 and data byte 0 to DQS1 and data byte 1.

<sup>(4)</sup> DQ's from other DQS domains are considered other DDR2 trace.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                 |                                   |

|-----------------------------|------------------------|------------------------------|-----------------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio                        | www.ti.com/audio                  |

| Data Converters             | dataconverter.ti.com   | Automotive                   | www.ti.com/automotive             |

| DLP® Products               | www.dlp.com            | Communications and Telecom   | www.ti.com/communications         |

| DSP                         | <u>dsp.ti.com</u>      | Computers and<br>Peripherals | www.ti.com/computers              |

| Clocks and Timers           | www.ti.com/clocks      | Consumer Electronics         | www.ti.com/consumer-apps          |

| Interface                   | interface.ti.com       | Energy                       | www.ti.com/energy                 |

| Logic                       | logic.ti.com           | Industrial                   | www.ti.com/industrial             |

| Power Mgmt                  | power.ti.com           | Medical                      | www.ti.com/medical                |

| Microcontrollers            | microcontroller.ti.com | Security                     | www.ti.com/security               |

| RFID                        | www.ti-rfid.com        | Space, Avionics & Defense    | www.ti.com/space-avionics-defense |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video and Imaging            | www.ti.com/video                  |

|                             |                        | Wireless                     | www.ti.com/wireless-apps          |