# OMAP5910/5912 Applications Processor Timers Reference Guide

Literature Number: SPRU891 February 2005

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                                       |                                                                            | Applications                                                                             |                                                                                                                                                                         |

|------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amplifiers                                     | amplifier.ti.com                                                           | Audio                                                                                    | www.ti.com/audio                                                                                                                                                        |

| Data Converters                                | dataconverter.ti.com                                                       | Automotive                                                                               | www.ti.com/automotive                                                                                                                                                   |

| DSP                                            | dsp.ti.com                                                                 | Broadband                                                                                | www.ti.com/broadband                                                                                                                                                    |

| Interface                                      | interface.ti.com                                                           | Digital Control                                                                          | www.ti.com/digitalcontrol                                                                                                                                               |

| Logic                                          | logic.ti.com                                                               | Military                                                                                 | www.ti.com/military                                                                                                                                                     |

| Power Mgmt                                     | power.ti.com                                                               | Optical Networking                                                                       | www.ti.com/opticalnetwork                                                                                                                                               |

| Microcontrollers                               | microcontroller.ti.com                                                     | Security                                                                                 | www.ti.com/security                                                                                                                                                     |

|                                                |                                                                            | Telephony                                                                                | www.ti.com/telephony                                                                                                                                                    |

|                                                |                                                                            | Video & Imaging                                                                          | www.ti.com/video                                                                                                                                                        |

|                                                |                                                                            | Wireless                                                                                 | www.ti.com/wireless                                                                                                                                                     |

| Data Converters DSP Interface Logic Power Mgmt | dataconverter.ti.com dsp.ti.com interface.ti.com logic.ti.com power.ti.com | Broadband Digital Control Military Optical Networking Security Telephony Video & Imaging | www.ti.com/broadband<br>www.ti.com/digitalcontrol<br>www.ti.com/military<br>www.ti.com/opticalnetwor<br>www.ti.com/security<br>www.ti.com/telephony<br>www.ti.com/video |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated

# **Preface**

# **Read This First**

# **About This Manual**

This document describes the timers present in the OMAP5910/5912 devices.

# Related Documentation From Texas Instruments

Documentation that describes the OMAP5910/5912 devices, related peripherals, and other technical collateral, is available in the OMAP5910 Product Folder on TI's website: www.ti.com/omap5910, and in the OMAP5912 Product Folder on TI's website: www.ti.com/omap5912.

# Trademarks

OMAP and the OMAP symbol are trademarks of Texas Instruments.

# **Contents**

| 1 | Introd | duction  |                                         | 12 |

|---|--------|----------|-----------------------------------------|----|

| 2 | MPU    | and DSI  | P Private Timers                        | 14 |

|   | 2.1    | Introdu  | ction to the MPU and DSP Private Timers | 14 |

|   |        | 2.1.1    | Features                                | 14 |

|   |        | 2.1.2    | Functional Block Diagram                | 14 |

|   | 2.2    | Commo    | on Architecture and Operations          | 15 |

|   |        | 2.2.1    | Clock Control                           | 15 |

|   |        | 2.2.2    | Interrupt Period                        | 16 |

|   |        | 2.2.3    | Power Management                        | 17 |

|   |        | 2.2.4    | Reset Considerations                    | 17 |

|   |        | 2.2.5    | Interrupt Support                       | 18 |

|   |        | 2.2.6    | One-Shot Mode versus Auto-Reload Mode   | 18 |

|   |        | 2.2.7    | Initialization                          | 19 |

|   |        | 2.2.8    | Common Operations                       | 20 |

|   |        | 2.2.9    | Emulation Considerations                | 21 |

|   |        | 2.2.10   | Pseudo Code Example                     | 21 |

|   | 2.3    | MPU P    | rivate Timer Registers                  | 22 |

|   | 2.4    | DSP Pi   | rivate Timer Registers                  | 23 |

| 3 | Watcl  | hdoa Tii | mers                                    | 26 |

| • | 3.1    | _        | ction                                   |    |

|   | 0.1    | 3.1.1    | Purpose                                 |    |

|   |        | 3.1.2    | Features                                |    |

|   |        | 3.1.3    | Functional Block Diagram                |    |

|   |        | 3.1.4    | Supported Modes                         |    |

|   | 3.2    |          | on Architecture and Operations          |    |

|   |        | 3.2.1    | Clock Control                           |    |

|   |        | 3.2.2    | Timeout Period                          |    |

|   |        | 3.2.3    | Power Management                        |    |

|   |        | 3.2.4    | Reset Considerations                    |    |

|   |        | 3.2.5    | Interrupt Support                       |    |

|   |        | 3.2.6    | Common Operations                       |    |

|   |        | 3.2.7    | Emulation Considerations                |    |

|   |        |          |                                         |    |

|   | 3.3   | Watcho   | dog Mode Operations                                 | . 31 |

|---|-------|----------|-----------------------------------------------------|------|

|   |       | 3.3.1    | Initialization                                      | . 31 |

|   |       | 3.3.2    | Programming the Watchdog Timer in Watchdog Mode     | . 31 |

|   |       | 3.3.3    | Pseudo Code Example                                 | . 32 |

|   | 3.4   | Housel   | keeping Mode Operations                             |      |

|   |       | 3.4.1    | Initialization                                      |      |

|   |       | 3.4.2    | Programming the Watchdog Timer in Housekeeping Mode | . 32 |

|   |       | 3.4.3    | Pseudo Code Example                                 |      |

|   | 3.5   | MPU W    | Vatchdog Timer Registers                            |      |

|   | 3.6   |          | /atchdog Timer Registers                            |      |

| 4 | 32-KI | dz OS Ti | imer                                                | . 39 |

|   | 4.1   | Introdu  | ction                                               | . 39 |

|   |       | 4.1.1    | Purpose                                             | . 39 |

|   |       | 4.1.2    | Features                                            |      |

|   |       | 4.1.3    | Functional Block Diagram                            |      |

|   | 4.2   | Commo    | on Architecture and Operations                      |      |

|   |       | 4.2.1    | Interrupt Period                                    |      |

|   |       | 4.2.2    | Clock Control                                       |      |

|   |       | 4.2.3    | Power Management                                    |      |

|   |       | 4.2.4    | Reset Considerations                                |      |

|   |       | 4.2.5    | Interrupt Support                                   |      |

|   |       | 4.2.6    | Auto-Reload Mode versus One-Shot Mode               |      |

|   |       | 4.2.7    | Initialization                                      |      |

|   |       | 4.2.8    | Common Operations                                   |      |

|   |       | 4.2.9    | Emulation Considerations                            |      |

|   |       |          | Pseudo Code Example                                 |      |

|   | 4.3   |          | z OS Timer Registers                                |      |

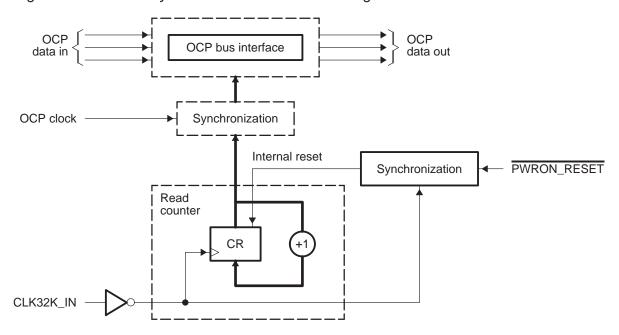

| 5 | 32-KI | dz Sync  | hronization Timer                                   | . 48 |

|   | 5.1   |          | ction                                               |      |

|   |       | 5.1.1    | Purpose                                             | . 48 |

|   |       | 5.1.2    | Features                                            | . 48 |

|   |       | 5.1.3    | Functional Block Diagram                            | . 48 |

|   | 5.2   | Commo    | on Architecture and Operations                      |      |

|   |       | 5.2.1    | Clock Control                                       |      |

|   |       | 5.2.2    | Reset Considerations                                |      |

|   |       | 5.2.3    | Common Operations                                   |      |

|   | 5.3   | -        | onization Timer Registers                           |      |

|   |       |          |                                                     |      |

| 6 | Gene | ral Purp | ose Timers                                    | 52 |

|---|------|----------|-----------------------------------------------|----|

|   | 6.1  | Introdu  | ction                                         | 52 |

|   |      | 6.1.1    | Purpose                                       | 52 |

|   |      | 6.1.2    | Features                                      | 52 |

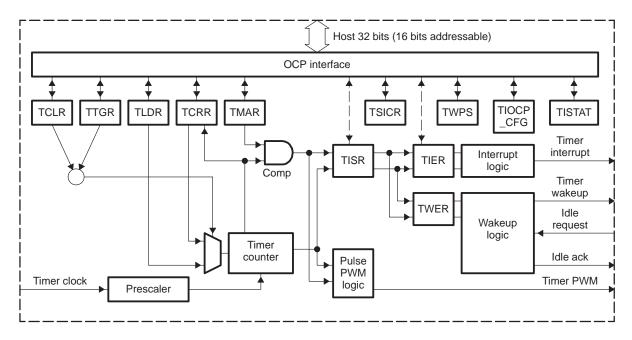

|   |      | 6.1.3    | Functional Block Diagram                      | 53 |

|   |      | 6.1.4    | Supported Modes                               | 53 |

|   | 6.2  | Commo    | on Architecture and Operations                | 54 |

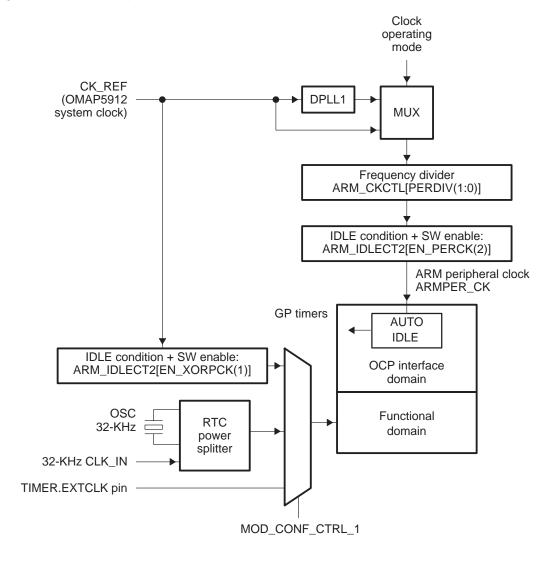

|   |      | 6.2.1    | Clock Control                                 | 54 |

|   |      | 6.2.2    | Timeout Period                                | 55 |

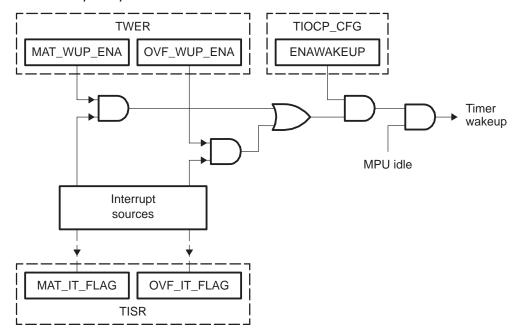

|   |      | 6.2.3    | Power Management                              | 56 |

|   |      | 6.2.4    | Register Write Mode: Posted versus Non-Posted | 58 |

|   |      | 6.2.5    | Reset Considerations                          | 59 |

|   |      | 6.2.6    | Interrupt Support                             | 60 |

|   |      | 6.2.7    | Initialization                                | 61 |

|   |      | 6.2.8    | Common Operations                             | 62 |

|   |      | 6.2.9    | Emulation Considerations                      | 63 |

|   |      | 6.2.10   | Pseudo Code Example                           | 64 |

|   | 6.3  | Compa    | re Mode Operations                            | 65 |

|   |      | 6.3.1    | Pseudo Code Example                           | 66 |

|   | 6.4  | Pulse-V  | Vidth Modulation                              | 67 |

|   |      | 6.4.1    | PWM Output Signal                             |    |

|   | 6.5  | GP Tim   | ner Registers                                 | 69 |

# **Figures**

| 1  | OMAP5912 Timers                                             | 13 |

|----|-------------------------------------------------------------|----|

| 2  | MPU/DSP Private Timer Block Diagram                         |    |

| 3  | Clock Input to MPU/DSP Private Timers                       | 15 |

| 4  | Watchdog Timer Block Diagram                                |    |

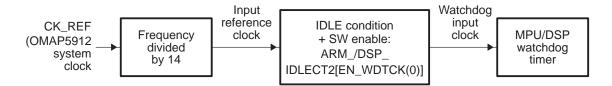

| 5  | Clock Input to Watchdog Timers                              | 28 |

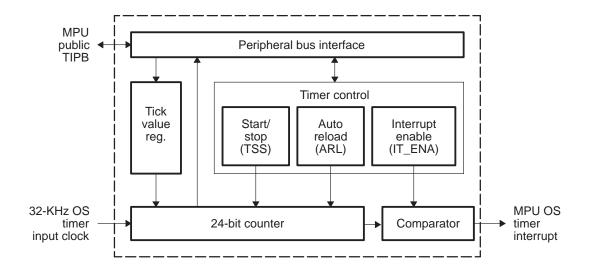

| 6  | 32-KHz OS Timer Block Diagram                               | 40 |

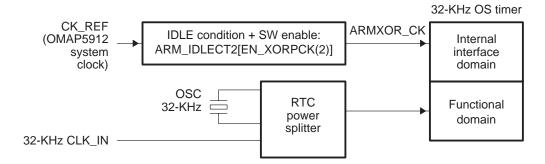

| 7  | Clock Input to 32-KHz OS Timers                             | 41 |

| 8  | 32-KHz Synchronization TImer Block Diagram                  | 48 |

| 9  | Clock Input to the 32-KHz Synchronization Timers            | 49 |

| 10 | GP Timer Block Diagram                                      | 53 |

| 11 | Clock Input for GP Timers                                   |    |

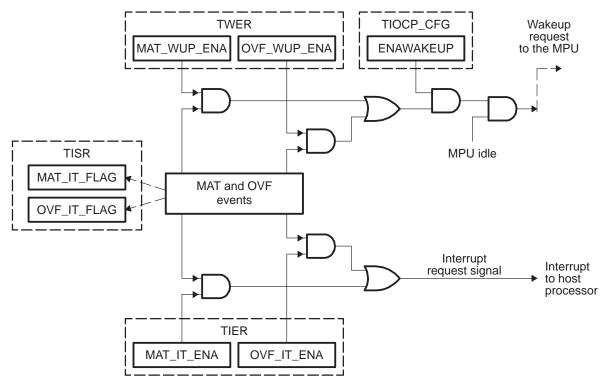

| 12 | Wakeup Request Generation                                   | 57 |

| 13 | GP Timer Interrupt Architecture                             | 60 |

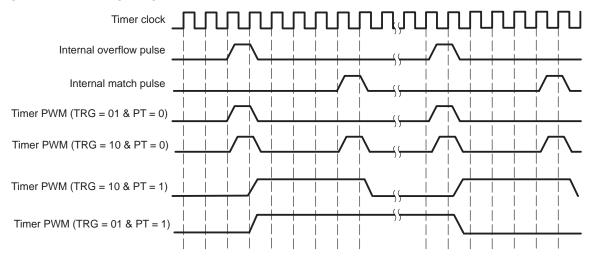

| 14 | Timing Diagram of Pulse-Width Modulation With SCPWM Bit = 0 | 68 |

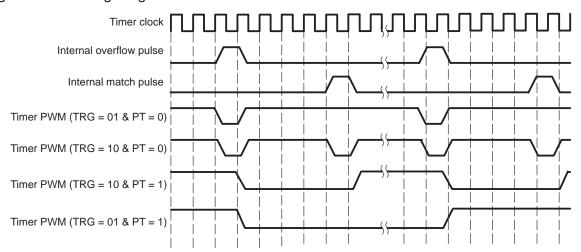

| 15 | Timing Diagram of Pulse-Width Modulation With SCPWM Bit = 1 | 68 |

# **Tables**

| 1  | Prescaler Value and Clock Divisor for MPU/DSP Private Timer     | 16 |

|----|-----------------------------------------------------------------|----|

| 2  | Example of MPU Private Timer Interrupt Periods                  | 17 |

| 3  | MPU/DSP Private Timer Interrupt Number                          | 18 |

| 4  | Register Base Addresses of MPU Private Timers                   | 22 |

| 5  | MPU Private Timer Registers                                     |    |

| 6  | MPU Control Timer Register (MPU_CNTL_TIMER)                     | 22 |

| 7  | MPU Load Timer Register Value (MPU_LOAD_TIMER)                  | 23 |

| 8  | MPU Read Timer Register Value (MPU_READ_TIMER)                  | 23 |

| 9  | Base Addresses of DSP Private Timer Registers                   | 23 |

| 10 | DSP Private Timer Registers                                     | 24 |

| 11 | DSP Control Timer Register (DSP_CNTL_TIMER)                     | 24 |

| 12 | DSP Load Timer Register Low (DSP_LOAD_TIMER_LO)                 | 25 |

| 13 | DSP Load Timer Register High (DSP_LOAD_TIMER_HI)                | 25 |

| 14 | DSP Read Timer Register Low (DSP_READ_TIMER_LO)                 | 25 |

| 15 | DSP Read Timer Register High (DSP_READ_TIMER_HI)                | 25 |

| 16 | Watchdog Timer Characteristics                                  | 29 |

| 17 | MPU Watchdog Timer Registers                                    | 34 |

| 18 | MPU Watchdog Control Timer Register (MPU_WDT_CNTL_TIMER)        | 34 |

| 19 | MPU Watchdog Load Timer Register (MPU_WDT_LOAD_TIMER)           | 35 |

| 20 | MPU Watchdog Read Timer Register (MPU_WDT_READ_TIMER)           | 35 |

| 21 | MPU Watchdog Timer Mode Register (MPU_WDT_TIMER_MODE)           | 36 |

| 22 | DSP Watchdog Timer Registers                                    | 36 |

| 23 | DSP Watchdog Control Timer Register (DSP_WDT_CNTL_TIMER)        | 37 |

| 24 | DSP Watchdog Load Timer Register (DSP_WDT_LOAD_TIMER)           | 37 |

| 25 | DSP Watchdog Read Timer Register (DSP_WDT_READ_TIMER)           | 38 |

| 26 | DSP Watchdog Timer Mode Register (DSP_WDT_TIMER_MODE)           | 38 |

| 27 | Timer Interrupt Period According to TVR Value                   | 40 |

| 28 | OS Timer Registers                                              | 46 |

| 29 | OS Timer Register Access Timing Constraints                     | 46 |

| 30 | OS Timer Control Register (OS_TIMER_CNTL)                       | 47 |

| 31 | OS Timer Tick Value Register (OS_TIMER_TICK_VAL)                | 47 |

| 32 | OS Timer Tick Counter Register (OS_TIMER_TICK_CNTR)             | 47 |

| 33 | Synchronization Timer Registers                                 |    |

| 34 | Synchronization Timer Identification Register (32K_SYN_CNT_REV) |    |

| 35 | Synchronization Timer Read Counter Register (32K_SYN_CNT_CR)    |    |

| 36 | Function Domain Clock for the GP Timer                          |    |

|    |                                                                 |    |

| 37 | Clock Divisor Values                                                | 55 |

|----|---------------------------------------------------------------------|----|

| 38 | TLDR Value and Corresponding Timeout Period (where PS = 1)          | 56 |

| 39 | GP Timer Interrupt Lines                                            | 61 |

| 40 | OMAP5912 ZDY Package: Pin Mux Configuration for the PWM Output Pins | 69 |

| 41 | OMAP5912 ZZG Package: Pin Mux Configuration for the PWM Output Pins |    |

| 42 | GP Timer Register Base Address                                      | 69 |

| 43 | GP Timer Registers                                                  |    |

| 44 | Timer Identification Register (GPTMR_TIDR)                          | 70 |

| 45 | Timer OCP Configuration Register (GPTMR_TIOCP_CFG)                  | 71 |

| 46 | Timer System Status Register (GPTMR_TISTAT)                         |    |

| 47 | Timer Status Register (GPTMR_TISR)                                  | 72 |

| 48 | Timer Interrupt Enable Register (GPTMR_TIER)                        | 73 |

| 49 | Timer Wakeup Enable Register (GPTMR_TWER)                           | 73 |

| 50 | Timer Control Register (GPTMR_TCLR)                                 | 74 |

| 51 | Timer Counter Register (GPTMR_TCRR)                                 | 75 |

| 52 | Timer Load Register (GPTMR_TLDR)                                    | 75 |

| 53 | Timer Trigger Register (GPTMR_TTGR)                                 | 75 |

| 54 | Timer Write Pending Status Register (GPTMR_TWPS)                    | 75 |

| 55 | Timer Match Register (GPTMR_TMAR)                                   | 76 |

| 56 | Timer Synchronization Interface Control Register (GPTMR_TSICR)      | 76 |

This page is intentionally left blank.

# **Timers**

Both the OMAP5912 and OMAP5910 application processors have three MPU private timers, three DSP private timers, one MPU watchdog timer, one DSP watchdog timer, and one 32-KHz operating system (OS) timer. The OMAP5912 processor also has one reserved 32-KHz watchdog timer, one 32-KHz synchronization timer, and eight general-purpose (GP) timers.

The MPU and DSP private timers are used for general housekeeping functions inside OMAP5910/5912.

The watchdog timers reset or generate an interrupt to MPU or DSP when they reach timeout. They can be used to detect user programs stuck in an infinite loop, loss of program control, or a runaway condition. In addition, they have general housekeeping capabilities.

The 32-KHz OS timer is able to generate periodical interrupts to the OS. This is used to keep track of the current time to control the operation of the device drivers, and also for OS scheduling purposes. If the OMAP chip is in deep sleep mode, it can also be used to wake up the system.

Using the reserved 32-KHz watchdog timer is not supported. It needs to be disabled upon reset.

The 32-KHz synchronization timer is a simple counter which can be used by the 32-KHz input clock to enable synchronization between devices, but only when the OMAP5912 is used in conjunction with another component (e.g., a modem) having the same clock input.

Each GP timer has the housekeeping capability. In addition, its internal compare logic allows interrupt events on the programmable counter matching value. If it is clocked by the 32-KHz input, it can be used to wake up the chip from deep sleep. GP timers 1, 2, and 3 can also be configured to provide a programmable pulse-width modulation (PWM) output on the dedicated output pin.

# 1 Introduction

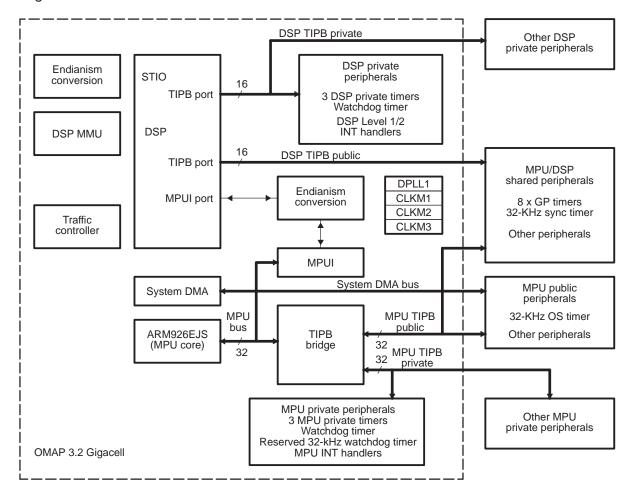

Figure 1 shows all the timers in the OMAP5912. The diagram also applies to the OMAP5910, except that OMAP5910 does not have the reserved 32-KHz watchdog timer, the synchronization timer, or the GP timers.

There are three MPU private timers and an MPU watchdog timer. These are MPU private peripherals and only accessed by the MPU via the MPU private peripheral bus.

There are three DSP private timers and a DSP watchdog timer. These are DSP private peripherals and are accessed by the DSP via the DSP private peripheral bus.

Eight general-purpose (GP) timers and a 32-KHz synchronization timer are MPU and DSP shared peripherals. They are accessed by both processors via the MPU and DSP public peripheral buses.

The 32-KHz operating system (OS) timer is an MPU public peripheral. It is accessed by the MPU via the MPU public peripheral bus and the system DMA via the system DMA bus.

The system clock (12 MHz, 13 MHz, or 19.2 MHz) is turned off in deep sleep mode, but the 32-KHz clock remains active. As it is active, the 32-KHz OS timer can be used to wake up the chip from deep sleep. If a GP timer is configured to be clocked by the 32-KHz signal, it can also wake up the chip from deep sleep. The MPU watchdog timer also has the wakeup capability, as it resets both the MPU and DSP upon timeout. The DSP watchdog timer only resets the DSP when its counter expires.

Figure 1. OMAP5912 Timers

# 2 MPU and DSP Private Timers

This section presents the purpose and features of the MPU and DSP private timers in the OMAP5912. This information also applies to the OMAP5910.

There are three MPU private timers and three DSP private timers inside the OMAP5912 that are typically used for general housekeeping functions.

# 2.1 Introduction to the MPU and DSP Private Timers

## 2.1.1 Features

The features of the MPU/DSP private timers are as follows:

- ☐ 32-bit down count

- ☐ Interrupt to MPU/DSP when the timer expires

- Programmable timer period

- ☐ Auto-reload mode and one-shot mode

- On-the-fly read capability

# 2.1.2 Functional Block Diagram

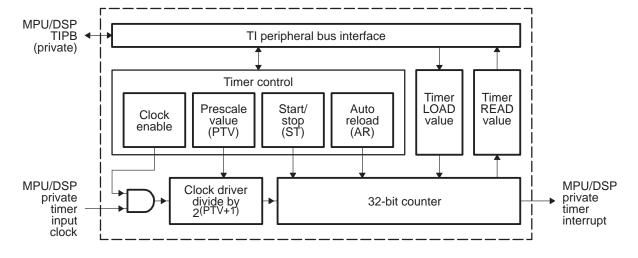

Figure 2 shows the MPU/DSP private timer block diagram. The functionality of the MPU and DSP private timers is identical except that the MPU timers interface to the 32-bit MPU private peripheral bus, and the DSP timers interface to the 16-bit DSP private peripheral bus.

Figure 2. MPU/DSP Private Timer Block Diagram

# 2.2 Common Architecture and Operations

#### 2.2.1 Clock Control

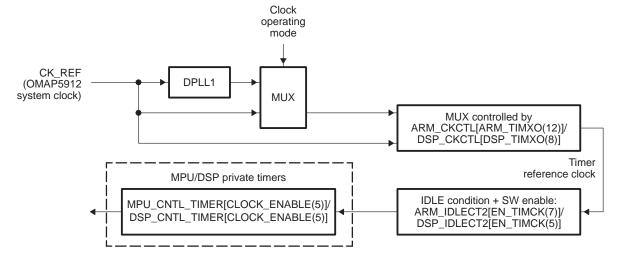

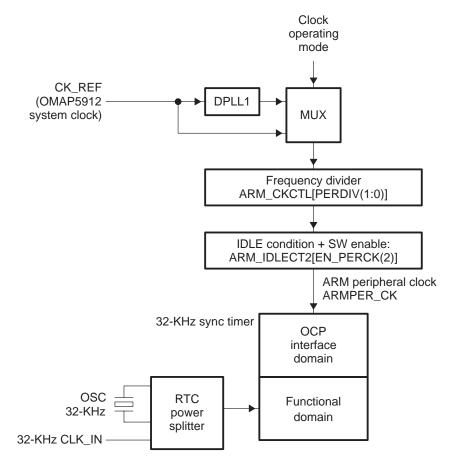

Figure 3 shows the clocking for the MPU and DSP private timers.

CK\_REF is the 12-, 13- or 19.2-MHz OMAP system clock (12-, 13- or 19.2-MHz oscillator, or from external clock input).

Figure 3. Clock Input to MPU/DSP Private Timers

# 2.2.1.1 Configuration of the Input Reference Clock

The timer reference clock for the MPU/DSP private timer module is controlled by the OMAP5912 clock generation and reset module. By configuring the ARM\_/DSP\_TIMXO bit in the ARM\_/DSP\_CKCTL register of the clock module, you can select from two possible clock sources:

- 1) ARM\_/DSP\_TIMXO = 0: Select the OMAP5912 system clock as the timer reference clock for the MPU/DSP private timers.

- 2) ARM\_/DSP\_TIMXO = 1: Select the output from the DPLL1 module as the timer reference clock for the MPU/DSP private timers.

The default selection is the output from DPLL1. When operating from DPLL1, the private timer should be stopped before programming a change to the DPLL1 frequency divisor. For detailed information on programming DPLL1, see the Clock Generation and Reset Management section in the *OMAP5912 Multimedia Processor OMAP 3.2 Subsystem Reference Guide* (SPRU749).

The timer reference clocks can be stopped or activated by configuring the EN\_TIMCK bit in the ARM\_/DSP\_IDLECT2 register.

- ☐ EN\_TIMCK = 0: The timer reference clock is stopped.

- ☐ EN\_TIMCK = 1: The timer reference clock is activated and can be stopped by configuring the IDLTIM\_ARM/\_DSP bit in the ARM\_/DSP\_IDLECTL1 register.

- IDLTIM\_ARM/\_DSP = 0: The timer reference clock remains active when the MPU/DSP enters the idle mode.

- IDLTIM\_ARM/\_DSP = 1: The timer reference clock is stopped in conjunction with the MPU/DSP clock when the MPU/DSP enters the idle mode.

# 2.2.1.2 Input Clock Enable

The MPU/DSP private timer reference clock can be disabled with the CLOCK\_ENABLE bit in the MPU\_/DSP\_CNTL\_TIMER register.

# 2.2.2 Interrupt Period

The MPU/DSP private timer generates an interrupt to the MPU/DSP when the counter passes 0. The interrupt period is defined by:

- ☐ The frequency of the timer reference clock for the MPU/DSP private timer (see section 2.2.1).

- ☐ The value of the prescaler bit field (PTV) in the MPU\_/DSP\_CNTL\_TIMER register. The input reference clock to the timer is divided by 2<sup>(PTV+1)</sup>. The PTV value is in the range from 0 to 7. Table 1 lists some valid PTV values and the corresponding clock divisor.

- ☐ The values of the load registers: MPU\_LOAD\_TIMER and DSP\_LOAD\_TIMER\_HI/\_LO.

Table 1. Prescaler Value and Clock Divisor for MPU/DSP Private Timer

| PTV Bit Field in MPU/DSP Private Timer<br>Control Register | Input Clock Divisor |

|------------------------------------------------------------|---------------------|

| PTV, (PTV = 07)                                            | 2(PTV+1)            |

| 000                                                        | 2                   |

| 111                                                        | 256                 |

The following equations are used to determine the timer interrupt period.

For the MPU private timer:

```

\label{eq:total_total_total_total} $$ T_{MPU\_Timeout} = T_{MPU\_ref\ clk} \times (< MPU\_LOAD\_TIMER> + 1) \times 2^{(PTV+1)} $$

```

## For the DSP private timer:

```

\label{eq:topp_top} \footnotesize \texttt{TDSP Timeout} = \texttt{TDSP ref clk} \ \times \ ( < \texttt{DSP\_LOAD\_TIMER\_HI}, \ \texttt{LO} > +1 ) \ \times \ 2 \ ( \texttt{PTV} + 1 )

```

where T<sub>MPU\_ref\_clk</sub> and T<sub>DSP\_ref\_clk</sub> are the periods of the input reference clocks for the MPU and DSP private timers.

Based on these equations, Table 2 calculates examples for various MPU private timer interrupt periods for a hypothetical input reference clock frequency of 100 MHz ( $T_{MPU\ ref\ clk} = 10\ ns$ ).

Table 2. Example of MPU Private Timer Interrupt Periods

| MPU_LOAD_TIMER              | PTV = 000 | PTV = 111                 |

|-----------------------------|-----------|---------------------------|

| 0x0 (granularity)           | 20 ns†    | 2.56 μs                   |

| 0xFFFF FFFF<br>(max period) | 85.9 s    | 10995 s (3 hr 3 min 15 s) |

<sup>&</sup>lt;sup>†</sup> Although the timer can be programmed to generate 20ns periodical interrupts, this is not recommended, as the TIPB bus and the ARM interrupt handling mechanism are not fast enough to handle those interrupts.

# 2.2.3 Power Management

Before the MPU/DSP subsystem can enter any of the low power states, the MPU/DSP timer reference clock must be stopped in the following two ways:

- ☐ Set the EN\_TIMCK bit in the MPU\_/DSP\_IDLECT2 register to 0 to force the clock to stop.

- □ Leave the EN\_TIMCK bit in the MPU\_/DSP\_IDLECT2 register as 1, but stop all the MPU/DSP private timers by configuring the ST bit in the MPU\_/DSP\_CNTL\_TIMER register and set the IDLTIM\_ARM/\_DSP bit to 1. Setting the IDLTIM\_ARM/\_DSP bit to 1 causes the input reference clock to be stopped in conjunction with MPU/DSP clock when the idle mode is entered.

For details on OMAP5912 power management, see the *OMAP5912 Multimedia Processor Power Management Reference Guide* (SPRU753).

#### 2.2.4 Reset Considerations

Upon reset, the MPU/DSP timer module is in the following state:

- ☐ The input reference clock is from DPLL1 (ARM\_CKCTL[ARM\_TIMXO]/DSP\_CKCTL[DSP\_TIMXO] = 1).

- The input reference clock is stopped (EN\_TIMCK bit is 0 in the ARM\_/DSP\_IDLECT2 register).

The input clock is not enabled inside timer module (CLOCK\_ENABLE bit is 0 in the MPU\_/DSP\_CNTL\_TIMER register).

The timer is in one-shot mode.

The timer is stopped (ST bit is 0 in the MPU\_/DSP\_CNTL\_TIMER)

# 2.2.5 Interrupt Support

An interrupt is generated to the MPU/DSP when an MPU/DSP private timer decrements to 0. Table 3 shows the interrupt number used by each MPU/DSP private timer.

Table 3. MPU/DSP Private Timer Interrupt Number

register).

| Timer               | Interrupt Number          |

|---------------------|---------------------------|

| MPU private timer 1 | MPU level 1 interrupt #26 |

| MPU private timer 2 | MPU level 1 interrupt #30 |

| MPU private timer 3 | MPU level 1 interrupt #16 |

| DSP private timer 1 | DSP level 1 interrupt #23 |

| DSP private timer 2 | DSP level 1 interrupt #22 |

| DSP private timer 3 | DSP level 1 interrupt #8  |

All interrupts are falling edge sensitive.

For details about OMAP5912 interrupt handling, see the *OMAP5912 Multimedia Processor Interrupts Reference Guide* (SPRU757).

## 2.2.6 One-Shot Mode versus Auto-Reload Mode

An MPU/DSP private timer works in one-shot mode if the AR(1) bit in the MPU\_/DSP\_CNTL\_TIMER register is 0. In this mode, when the timer counter expires an interrupt is generated and the timer is stopped. The ST(0) bit is automatically reset by the internal logic.

The MPU/DSP private timer works in auto-reload mode if the AR(1) bit is 1. In this mode, when the timer counter expires an interrupt is generated and the new count value is loaded from the MPU\_LOAD\_TIMER register or the DSP\_LOAD\_TIMER\_HI/\_LO register. The timer continues counting down from the new loaded count value.

#### 2.2.7 Initialization

The following procedure is an example of MPU/DSP private timer initialization.

- 1) Configure the timer input reference clock.

- a) Program the ARM\_/DSP\_TIMXO bit in the ARM\_/DSP\_CKCTL register to select the reference for the timer clock (1: DPLL1 is selected; 0: OMAP5912 system clock is selected). If DPLL1 is selected, the DPLL1 needs to be programmed.

- b) Set the EN\_TIM bit in the ARM\_/DSP\_IDLECT2 register to activate the timer reference clock.

- 2) Configure the interrupt controller module. For the MPU private timer:

- a) Enable the MPU global interrupt.

- b) Program the corresponding level 1 interrupt priority\_level (ILR) register for the timer interrupt being used. For the MPU private timers 1, 2, and 3, it is ILR26, ILR30, and ILR16 respectively.

- i) Program the PRIORITY field to set the interrupt priority (0 highest; 31 lowest).

- ii) Set the SENS\_LEVEL bit to 0 as falling edge sensitive.

- iii) Set the FIQ bit to 1 to set the interrupt as a FIQ.

- c) Prepare the FIQ ISR and place its address to the appropriate entry of the interrupt vector (entry 7 in the vector).

- d) Prepare the timer ISR.

- e) Enable the specific timer interrupt by clearing the corresponding bit in the MPU interrupt level 1 mask register.

- 3) Configure the interrupt controller module. For the DSP private timer:

- a) Enable the DSP global interrupt.

- b) Prepare the timer ISR and put its address in the appropriate entry of the interrupt vector (based on the interrupt number being used).

- c) Enable the specific timer interrupt by clearing the corresponding bit in the DSP interrupt level 1 mask register.

# 2.2.8 Common Operations

# 2.2.8.1 Start/Stop an MPU/DSP Private Timer

Setting the ST bit in the MPU\_/DSP\_CNTL\_TIMER register starts the MPU/DSP private timer. At start, the timer loads the values in the MPU\_LOAD\_TIMER register or the DSP\_LOAD\_TIMER\_HI and DSP\_LOAD\_TIMER\_LO registers into the counter.

Clearing the ST bit stops the MPU/DSP private timer. When stopped, the timer keeps the current value.

#### Note:

Only the ST and EN\_TIMCLK bits in the MPU\_/DSP\_CNTL\_TIMER register can be written while the timer is running.

Undefined results occur if following configurations are changed while the timer is running:

- Prescaler (PTV) and auto-reload (AR) bits in the MPU\_/DSP\_CNTL\_TIM-ER register

- DSP\_LOAD\_TIMER\_HI/\_LO registers

#### 2.2.8.2 Read Timer Count Value

The timer value can be read from the MPU\_/DSP\_READ\_TIMER register either on-the-fly or after the timer is stopped.

For the MPU, the MPU\_READ\_TIMER is a 32-bit register and can be read directly.

However, the DSP peripheral bus only has a width of 16 bits. To correctly read the value of the DSP private timers, the upper 16 bits must be read prior to the lower 16 bits. When the upper read occurs, the lower 16 bits are simultaneously stored in a temporary register. The contents of this temporary register are provided by an access to the lower 16 bits.

#### 2.2.9 Emulation Considerations

The FREE bit in the MPU\_/DSP\_CNTL\_TIMER register defines the behavior of the MPU/DSP private timer when the debugger halts its parent processor.

- FREE = 1: Keep running while the debugger halts its processor.

- FREE = 0: Stop the timer while the debugger halts its processor (even if the ST bit in the timer control register is set).

# 2.2.10 Pseudo Code Example

The pseudo code below shows how to use an MPU/DSP private timer.

- 1) Initialization.

- 2) Program the timer to the desired interrupt period and mode.

- a) Program the MPU\_/DSP\_LOAD\_TIMER register to set the load value.

- b) Program the PTV field in the MPU\_/DSP\_CNTL\_TIMER register to set the clock divider value (PTV = 0 ... 7).

- c) Program the AR bit in the MPU\_/DSP\_CNTL\_TIMER register. (1: auto-reload mode; 0: one-shot mode)

- d) Program the FREE bit in the MPU\_/DSP\_CNTL\_TIMER register. (1: run free during emulation stop; 0: stop during emulation stop)

- e) Load the desired counter value to the MPU\_LOAD\_TIMER register or DSP\_LOAD\_TIMER\_HI/\_LO register.

- f) Set the CLOCK\_ENABLE bit in the MPU\_/DSP\_CNTL\_TIMER register to enable the input clock.

- 3) Start the timer by setting the ST bit in the MPU\_CNTL\_TIMER register and wait until an interrupt happens.

- 4) When an interrupt happens, control jumps depending on the timer:

- a) For the MPU private timer, control jumps to the FIQ ISR, which should:

- i) Read the interrupt level 1 source register for FIQ to get the interrupt number, which should be the timer interrupt number.

- ii) Call the timer ISR to process the interrupt.

- iii) Set the NEW\_FIQ\_ARG bit in the interrupt level 1 control register to acknowledge the interrupt, which will allow new FIQ generation.

- b) For the DSP private timer, control jumps the timer ISR in which the interrupt is processed.

# 2.3 MPU Private Timer Registers

Table 4 lists the register base addresses of the MPU private timers. Table 5 lists the registers. All the registers are 32 bits. Table 6 through Table 8 are the descriptions for each register.

Table 4. Register Base Addresses of MPU Private Timers

| MPU Private Timer | MPU Byte Address |

|-------------------|------------------|

| Timer 1           | 0xFFFE: C500     |

| Timer 2           | 0xFFFE: C600     |

| Timer 3           | 0xFFFE: C700     |

Table 5. MPU Private Timer Registers

| MPU Byte Base Address = 0xFFFE C500, 0xFFFE C600, 0xFFFE C700 |                   |     |      |  |

|---------------------------------------------------------------|-------------------|-----|------|--|

| Name Description R/W Offset                                   |                   |     |      |  |

| MPU_CNTL_TIMER                                                | MPU control timer | R/W | 0x00 |  |

| MPU_LOAD_TIMER                                                | MPU load timer    | W   | 0x04 |  |

| MPU_READ_TIMER                                                | MPU read timer    | R   | 80x0 |  |

Table 6. MPU Control Timer Register (MPU\_CNTL\_TIMER)

| Bit  | Name         | Function                                                                                    | R/W | Reset     |

|------|--------------|---------------------------------------------------------------------------------------------|-----|-----------|

| 31:7 | RESERVED     | Reserved.                                                                                   |     | 0x0000000 |

| 6    | FREE         | Defines the behavior of the MPU private timer when the debugger halts its parent processor. | R/W | 0         |

|      |              | 0: Stop counting even if ST =1.                                                             |     |           |

|      |              | 1: Keep counting if ST=1.                                                                   |     |           |

| 5    | CLOCK_ENABLE | Enable input reference clock to the MPU private timer module 0: Disable. 1: Enable.         | R/W | 0         |

| 4:2  | PTV          | Prescale timer input reference clock Clock divisor = $2^{(PTV+1)}$                          | R/W | 000       |

Table 6. MPU Control Timer Register (MPU\_CNTL\_TIMER) (Continued)

|     | MPU Byte Base Address = 0xFFFE C500, 0xFFFE C600, 0xFFFE C700, Byte Offset = 0x00 |                                                                                               |     |       |  |

|-----|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----|-------|--|

| Bit | Name                                                                              | Function                                                                                      | R/W | Reset |  |

| 1   | AR                                                                                | 0: One-shot mode.<br>1: Auto-reload mode.                                                     | R/W | 0     |  |

| 0   | ST                                                                                | <ul><li>0: Stop timer value decrement.</li><li>1: Start timer value decrement.</li></ul>      | R/W | 0     |  |

|     |                                                                                   | In one-shot mode (AR = $0$ ), this bit is cleared automatically when the timer value expires. |     |       |  |

Table 7. MPU Load Timer Register Value (MPU\_LOAD\_TIMER)

|      | MPU Byte Base Address = 0xFFFE C500, 0xFFFE C600, 0xFFFE C700, Byte Offset = 0x04 |                                                                |     |           |  |  |

|------|-----------------------------------------------------------------------------------|----------------------------------------------------------------|-----|-----------|--|--|

| Bit  | Name                                                                              | Function                                                       | R/W | Reset     |  |  |

| 31:0 | MPU_LOAD_TIMER                                                                    | This value is loaded when the timer expires or when it starts. | W   | Undefined |  |  |

Table 8. MPU Read Timer Register Value (MPU\_READ\_TIMER)

|      | MPU Byte Base Address = 0xFFFE C500, 0xFFFE C600, 0xFFFE C700, Byte Offset = 0x08 |                     |     |           |  |

|------|-----------------------------------------------------------------------------------|---------------------|-----|-----------|--|

| Bit  | Name                                                                              | Function            | R/W | Reset     |  |

| 31:0 | MPU_READ_TIMER                                                                    | Value of the timer. | R   | Undefined |  |

# 2.4 DSP Private Timer Registers

Table 9 lists the register base addresses of the DSP private timers. Table 10 lists the registers. Table 11 through Table 15 are the descriptions for each register.

All the registers are 16 bits except the DSP\_CNTL\_TIMER register, which is 32 bits.

Table 9. Base Addresses of DSP Private Timer Registers

| DSP Private Timer | DSP Word Address (I/O Space) |

|-------------------|------------------------------|

| Timer 1           | 0x2800                       |

| Timer 2           | 0x2C00                       |

| Timer 3           | 0x3000                       |

Table 10. DSP Private Timer Registers

| Name              | Description                   | R/W | DSP Word<br>Offset |

|-------------------|-------------------------------|-----|--------------------|

| DSP_CNTL_TIMER    | DSP control timer             | R/W | 0x00               |

| DSP_LOAD_TIMER_LO | DSP load timer value, 1/2 LSW | W   | 0x03               |

| DSP_LOAD_TIMER_HI | DSP load timer value, 1/2 MSW | W   | 0x02               |

| DSP_READ_TIMER_LO | DSP read timer value, 1/2 LSW | R   | 0x05               |

| DSP_READ_TIMER_HI | DSP read timer value, 1/2 MSW | R   | 0x04               |

Table 11. DSP Control Timer Register (DSP\_CNTL\_TIMER)

|      | DSP Word Base Address = 0x2800, 0x2C00, 0x3000, Word Offset = 0x00 |                                                                                             |     |       |

|------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-------|

| Bit  | Name                                                               | Function                                                                                    | R/W | Reset |

| 15:7 | RESERVED                                                           | Reserved.                                                                                   |     | 0x000 |

| 6    | FREE                                                               | Defines the behavior of the DSP private timer when the debugger halts its parent processor. | R/W | 0     |

|      |                                                                    | 0: Stop counting even if ST =1.                                                             |     |       |

|      |                                                                    | 1: Keep counting if ST=1.                                                                   |     |       |

| 5    | CLOCK_ENABLE                                                       | Enables input reference clock to the DSP OS timer module                                    | R/W | 0     |

|      |                                                                    | 0: Disable.                                                                                 |     |       |

|      |                                                                    | 1: Enable.                                                                                  |     |       |

| 4:2  | PTV                                                                | Prescale timer input reference clock                                                        | R/W | 000   |

|      |                                                                    | Clock divisor = $2^{(PTV+1)}$                                                               |     |       |

| 1    | AR                                                                 | 0: One-shot mode.                                                                           | R/W | 0     |

|      |                                                                    | 1: Auto-reload mode.                                                                        |     |       |

| 0    | ST                                                                 | 0: Stop timer value decrement.                                                              | R/W | 0     |

|      |                                                                    | 1: Start timer value decrement.                                                             |     |       |

|      |                                                                    | In one-shot mode (AR = $0$ ), this bit is cleared automatically when the timer expires.     |     |       |

Table 12. DSP Load Timer Register Low (DSP\_LOAD\_TIMER\_LO)

|      | DSP Word Base Address = 0x2800, 0x2C00, 0x3000, Word Offset = 0x03 |                                                                |     |           |  |  |

|------|--------------------------------------------------------------------|----------------------------------------------------------------|-----|-----------|--|--|

| Bit  | Name                                                               | Function                                                       | R/W | Reset     |  |  |

| 15:0 | DSP_LOAD_TIMER_LO                                                  | This value is loaded when the timer expires or when it starts. | W   | Undefined |  |  |

Table 13. DSP Load Timer Register High (DSP\_LOAD\_TIMER\_HI)

|      | DSP Word Base Address = 0x2800, 0x2C00, 0x3000, Word Offset = 0x02 |                                                                |     |           |  |  |

|------|--------------------------------------------------------------------|----------------------------------------------------------------|-----|-----------|--|--|

| Bit  | Name                                                               | Function                                                       | R/W | Reset     |  |  |

| 15:0 | DSP_LOAD_TIMER_HI                                                  | This value is loaded when the timer expires or when it starts. | W   | Undefined |  |  |

Table 14. DSP Read Timer Register Low (DSP\_READ\_TIMER\_LO)

|      | DSP Word Base Address = 0x2800, 0x2C00, 0x3000, Word Offset = 0x05 |                                                                                                                                                                     |     |           |  |

|------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|--|

| Bit  | Name                                                               | Function                                                                                                                                                            | R/W | Reset     |  |

| 15:0 | DSP_READ_TIMER_LO                                                  | Value of the timer bits (15:0): To read a correct value for DSP private timer, the upper 16 bits (from DSP_READ_TIMER_HI) must read prior to reading this register. | R   | Undefined |  |

Table 15. DSP Read Timer Register High (DSP\_READ\_TIMER\_HI)

|      | DSP Word Base Address = 0x2800, 0x2C00, 0x3000, Word Offset = 0x04 |                                                                                                                                                                 |     |           |  |

|------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|--|

| Bit  | Name                                                               | Function                                                                                                                                                        | R/W | Reset     |  |

| 15:0 | DSP_READ_TIMER_HI                                                  | Value of the timer bits (31:16): To read correct value for DSP private timer, this register must be read first, followed by lower 16 bits of DSP_READ_TIMER_LO. | R   | Undefined |  |

# 3 Watchdog Timers

# 3.1 Introduction

There are three watchdog timers inside the OMAP5912: one MPU watchdog timer, one DSP watchdog timer, and one reserved 32-KHz watchdog timer.

Using the 32-KHz watchdog is not supported. Upon system reset, it needs to be disabled before it expires (in approximately 19s) via the following procedure:

```

(*(volatile int*)0xFFFEB048) = 0xAAAA;

// wait until the write operation is completed

while ( ((*(volatile int *)0xFFFEB034) & 0x10) == 0x10 );

(*(volatile int*)0xFFFEB048) = 0x5555;

// wait until the write operation is completed

while ( ((*(volatile int *)0xFFFEB034) & 0x10) == 0x10 );

```

This section presents the purpose and features of the MPU and DSP watchdog timers in the OMAP5912. All the information also applies to the OMAP5910.

# 3.1.1 Purpose

There are two useful watchdog timers inside the OMAP5912. One is in the MPU subsystem (controlled by the MPU), and the other is in the DSP subsystem (controlled by the DSP). Each watchdog timer can be configured either as a watchdog timer or a housekeeping timer.

When the timer is configured as a watchdog timer, the software must periodically write to the count register before the counter expires. If the counter expires, the MPU watchdog timer resets the OMAP3.2 gigacell except the DPLL1, while the DSP watchdog timer resets the DSP only. The watchdog timers can be used to detect user programs that are stuck in an infinite loop, have a loss of program control, or are in a runaway condition.

When used as a housekeeping timer, it is 16-bit counter configurable either to auto-reload mode or one-shot mode with on-the-fly read capability. It generates an interrupt to the MPU/DSP when the count expires.

#### 3.1.2 Features

The following are features of the MPU/DSP watchdog timers:

- ☐ 16 bit count down

- Possesses on-the-fly read capability

- ☐ Fixed low input clock frequency (system\_clock/14)

- Programmable reset or interrupt period

- ☐ If configured as a watchdog timer, the MPU watchdog timer resets both the MPU and DSP when the counter passes 0, while the DSP watchdog timer resets the DSP only

- ☐ If configured as a housekeeping timer:

- Supports both auto-reload and one-shot mode

- Generates an interrupt to MPU/DSP when counter passes 0

# 3.1.3 Functional Block Diagram

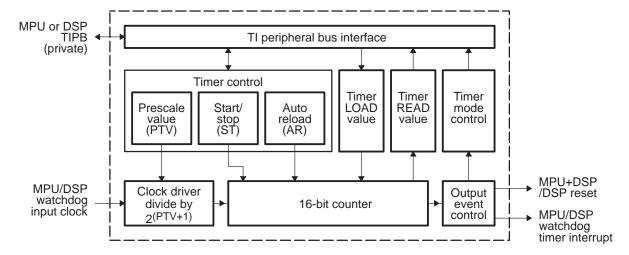

Both watchdog timers have identical functionality, except that the MPU timer interfaces to the 32-bit MPU private peripheral bus, and the DSP timer interfaces to the 16-bit DSP private peripheral bus.

Figure 4. Watchdog Timer Block Diagram

# 3.1.4 Supported Modes

A watchdog timer can be configured as either a watchdog timer or a housekeeping timer.

Both the MPU and DSP watchdog timers are configured for watchdog mode after reset. For specific watchdog mode information, see section 3.3.

Both MPU and DSP watchdog timers can also be configured to work as 16-bit housekeeping timers, supporting both auto-reload and one-shot mode with on-the-fly read capability. For specific housekeeping mode information, see section 3.4.

# 3.2 Common Architecture and Operations

# 3.2.1 Clock Control

Figure 5 shows the clocking for the MPU and DSP watchdog timers.

CK\_REF is the 12-, 13- or 19.2-MHz system clock (12-, 13- or 19.2-MHz oscillator, or from external clock input).

Figure 5. Clock Input to Watchdog Timers

#### 3.2.1.1 Configuration of the Input Reference Clock for Watchdog Timers

The input reference clocks for the watchdog timer modules are derived from OMAP5912 system clock, divided by 14. For example, if the system clock is 12 MHz, the watchdog input reference clock will be about 0.86 MHz.

If the MPU/DSP watchdog timer is configured for watchdog mode, the input reference clock is always active, regardless of the EN\_WDTCK bit value in the MPU\_/DSP\_IDLECT2 register.

If the watchdog timer is configured for housekeeping mode, the input clock can be stopped or activated by configuring the EN\_WDTCK bit in the MPU\_/DSP\_IDLECT2 register.

- ☐ EN\_WDTCK = 0: The input reference clock is stopped.

- EN\_WDTCK = 1: The input reference clock is activated and can be stopped by configuring the IDLWDT\_ARM/\_DSP bit in the ARM\_/DSP\_IDLECTL1 register.

- IDLWDT\_ARM/\_DSP = 0: The input reference clock remains active when the MPU/DSP enters the idle mode.

- IDLWDT\_ARM/\_DSP = 1: The input reference clock is stopped in conjunction with the MPU/DSP clock when the MPU/DSP enters the idle mode.

#### 3.2.2 Timeout Period

The timeout period of an MPU/DSP watchdog timer is defined by:

- ☐ The frequency of the input reference clock, which is the OMAP system clock frequency divided by 14.

- ☐ The value of the prescaler bit field (PTV) in the MPU\_/DSP\_WDT\_CNTL register. The input clock frequency is further divided by 2<sup>(PTV+1)</sup>. When the watchdog timer is in watchdog mode, the PTV value is fixed to 7. When the watchdog is configured as a housekeeping timer, PTV is in the range 0 to 7.

- ☐ The value of the load register, MPU\_/DSP\_WDT\_LOAD.

The following equation is used to determine the timeout period.

$$T_{WDT\ Timeout} = T_{WDT\ ref\ clk}\ \times\ (< MPU_/DSP_WDT_LOAD > +1)\ \times\ 2^{(PTV+1)}$$

where T<sub>WDT</sub> ref clk is the input reference clock period of the watchdog timer.

Table 16 shows the characteristics of the watchdog timer for different MPU\_/DSP\_WDT\_LOAD values.

Table 16. Watchdog Timer Characteristics

| OMAP System<br>Clock | WDT_ref_clk | MPU_/DSP_WDT_LOAD | T <sub>WDT_Timeout</sub> (PTV=7) |

|----------------------|-------------|-------------------|----------------------------------|

| 12 MHz               | 1167 ns     | 0x0001            | 597.34 μs                        |

| 12 MHz               | 1167 ns     | 0xFFFF            | 19.57 s                          |

# 3.2.3 Power Management

Before the MPU/DSP subsystem enters any of the low power states, the corresponding input reference clock to the watchdog timer must be stopped, as it implies that the watchdog timer must be configured for housekeeping mode.

There are two ways to stop the input reference clock when the MPU/DSP watchdog timer is in housekeeping mode:

| Set the EN_WDTCK bit in the MPU_/DSP_IDLECT2 register to 0 to force |

|---------------------------------------------------------------------|

| the clock to stop.                                                  |

□ Set the EN\_WDTCK bit in the MPU\_/DSP\_IDLECT2 register to 1, but stop the MPU/DSP watchdog timer by setting the ST bit in the MPU\_/DSP\_WDT\_CNTL register, and program the IDLWDT\_ARM/ \_DSP bit to 1. This causes the input reference clock to be stopped automatically in conjunction with the MPU/DSP clock when the idle mode is entered.

For details on OMAP5912 power management, see the *OMAP5912 Multimedia Processor Power Management Reference Guide* (SPRU753).

# 3.2.4 Reset Considerations

Both the MPU and DSP watchdog timers are configured for watchdog mode after powerup. The default value of the MPU\_/DSP\_WDT\_LOAD register is 0xFFFF.

When the MPU watchdog expires, it resets the OMAP3.2 gigacell, except for the DPLL1. When the DSP watchdog expires, it resets only the DSP.

If the OMAP system clock is 12 MHz, the reset occurs in approximately 19 seconds upon powerup, unless the default setting is changed.

# 3.2.5 Interrupt Support

If the watchdog is configured as a housekeeping timer, the timer can be configured to generate an interrupt when the counter expires.

MPU watchdog timer uses MPU level 1 interrupt #27. DSP watchdog timer uses DSP level 1 interrupt #13. Both interrupts are falling edge sensitive.

For details about OMAP5912 interrupt handling, see the *OMAP5912 Multimedia Processor Interrupts Reference Guide* (SPRU757).

# 3.2.6 Common Operations

#### 3.2.6.1 Read Timer Values

The timer values can be read from the respective MPU or DSP read timer register (MPU\_/DSP\_WDT\_READ) either on-the-fly or after the timer is stopped.

#### 3.2.7 Emulation Considerations

The FREE bit in the MPU\_/DSP\_WDT\_CNTL\_TIMER register defines the MPU/DSP watchdog behavior in housekeeping mode when the debugger halts its parent processor.

FREE = 1: Keep running while the debugger halts its processor.

FREE = 0: Stop the timer while the debugger halts its processor, even if the ST bit in the timer control register is set.

If the MPU/DSP watchdog timer is configured for watchdog mode, it keeps counting until it expires, regardless of this bit.

# 3.3 Watchdog Mode Operations

#### 3.3.1 Initialization

On power up, the MPU/DSP watchdog timer defaults to watchdog mode.

When the timer is in housekeeping mode, it can be switched back to watchdog mode by setting the WATCHDOG bit in the MPU\_/DSP\_WDT\_TIMER\_MODE register. In this case, the value loaded into MPU\_/DSP\_WDT\_LOAD register is set to the maximum value (0xFFFF), as on power up.

#### Note:

In watchdog mode, the MPU\_/DSP\_WDT\_CNTL register must not be used. The watchdog timer cannot be stopped by clearing the ST bit. The prescale (PTV) value is fixed to 7 regardless of the PTV field value. Auto-reload and one-shot do not apply because, if the counter expires, the processor is reset and the watchdog registers are reinitialized.

# 3.3.2 Programming the Watchdog Timer in Watchdog Mode

When used as a watchdog timer, it is the responsibility of the software to periodically write to the MPU\_/DSP\_WDT\_LOAD register before the counter expires. The newly loaded value must be different from the previous value, otherwise the write will not be taken into account. Due to internal sequencing, three timer clock periods must pass before a new value can be written into the register. If the OMAP system clock (CLK\_REF) is 12 MHz, the duration of three timer clock periods is approximately 3.5  $\mu s$ .

# 3.3.3 Pseudo Code Example

The following procedure shows how to use the watchdog timer in watchdog mode.

- Arrange a routine which is executed periodically before the WDT expires.

For example, this routine can be launched by the MPU/DSP private timers or GP timers.

- If the watchdog timer is in housekeeping mode, start the watchdog timer by setting the WATCHDOG bit in the MPU\_/DSP\_WDT\_TIMER\_MODE register.

- 3) Wait until an interrupt occurs before the watchdog times out. Inside the ISR, reload the MPU\_/DSP\_WDT\_LOAD register with a different value from the current one.

# 3.4 Housekeeping Mode Operations

# 3.4.1 Initialization

On power up, the MPU/DSP watchdog timer defaults to watchdog mode. By writing a predefined sequence to the WATCHDOG\_DIS field of the MPU\_/DSP\_WDT\_TIMER\_MODE register, the timer can be switched to housekeeping mode. A sequence decode is initialized when 0xF5 is written. Once in this state, if the next write is different from 0xA0, the state machine causes a reset as if the watchdog timer has timed out. The watchdog timer cannot be disabled by simply clearing the WATCHDOG bit in the MPU\_/DSP\_WDT\_TIMER\_MODE register.

# 3.4.2 Programming the Watchdog Timer in Housekeeping Mode

The timer in housekeeping mode is started by setting the ST bit in the control timer register (MPU\_/DSP\_WDT\_CNTL) to 1. It is stopped by resetting this bit to 0. When the timer is stopped, the timer counter keeps the current value.

If the AR bit in the MPU\_/DSP\_WDT\_CNTL\_TIMER register is 0, the timer decrements from the loaded value down to 0 and then stops. If the AR bit is 1, the timer continues. A new value from the MPU\_/DSP\_WDT\_LOAD register is loaded into the timer counter when it expires.

# Note:

Only the ST bit in the MPU\_/DSP\_WDT\_CNTL register can be written while the timer is running. Undefined results occur if the PTV or AR bits in the MPU\_/DSP\_WDT\_CNTL register are written. Undefined results occur if the MPU\_/DSP\_WDT\_LOAD register is written while the timer is running.

# 3.4.3 Pseudo Code Example

The following procedure shows how to switch a watchdog timer into housekeeping mode and how to use the timer.

- 1) Switch the timer to housekeeping mode, if necessary:

- a) Write 0xF5 to the MPU\_/DSP\_WDT\_TIMER\_MODE register.

- b) Write 0xA0 to the MPU\_/DSP\_WDT\_TIMER\_MODE register.

- Enable the watchdog timer input clock by setting the EN\_WDTCK bit in the ARM\_/DSP\_IDLECT2 register.

- 3) Configure the timer:

- a) Program the MPU\_/DSP\_WDT\_LOAD\_TIMER register to the desired load value.

- b) Program the PTV field in the MPU\_/DSP\_WDT\_CNTL\_TIMER register to set the clock divider value (PTV = 0 ... 7).

- c) Program the AR bit in the MPU\_/DSP\_WDT\_CNTL\_TIMER register.(1: auto-reload mode; 0: one-shot mode)

- d) Program the FREE bit in the MPU\_/DSP\_WDT\_CNTL\_TIMER register. (1: run free during emulation stop; 0: stop during emulation stop)

- 4) Configure the MPU interrupt controller module for the MPU watchdog timer:

- a) Enable the MPU global interrupt.

- b) Program the corresponding level 1 interrupt priority\_level (ILR) register for the timer interrupt being used. (For the MPU watchdog timer, ILR27.)

- i) Program the PRIORITY field to set the interrupt priority (0 highest; 31 lowest).

- ii) Set the SENS\_LEVEL bit to 0 as falling edge sensitive.

- iii) Set the FIQ bit to 1 to set the interrupt as a FIQ.

- c) Prepare the FIQ ISR and place its address the appropriate entry of the interrupt vector (entry 7 in the vector).

- d) Prepare the watchdog timer ISR.

- e) Enable the specific timer interrupt by clearing the corresponding bit in the MPU level 1 interrupt mask register.

- 5) Configure the DSP interrupt controller module for DSP watchdog timer:

- a) Enable the DSP global interrupt.

- b) Prepare the watchdog timer ISR and put its address in entry 13 of the interrupt vector.

- Enable the timer interrupt by clearing the corresponding bit the in the DSP level 1 interrupt mask register.

# 6) When the interrupt occurs:

- a) For the MPU watchdog timer, control jumps to the FIQ ISR, which will:

- i) Read the level 1 interrupt source register for FIQ to get the interrupt number (which should be interrupt #27).

- ii) Call the timer ISR to process the interrupt.

- iii) Set the NEW\_FIQ\_ARG bit in the interrupt level 1 control register to acknowledge the interrupt.

- b) For the DSP watchdog timer, control jumps to the watchdog timer ISR in which the interrupt is processed.

# 3.5 MPU Watchdog Timer Registers

Table 17 lists the MPU watchdog timer registers. All the registers are 16 bits. The base (byte) address is 0xFFFE C800. Table 18 through Table 21 provide the descriptions for each register.

Table 17. MPU Watchdog Timer Registers

| Name               | Description                   | R/W | MPU (Byte) Address |

|--------------------|-------------------------------|-----|--------------------|

| MPU_WDT_CNTL_TIMER | MPU watchdog control timer    | R/W | 0xFFFE C800        |

| MPU_WDT_LOAD_TIMER | MPU watchdog load timer       | W   | 0xFFFE C804        |

| MPU_WDT_READ_TIMER | MPU watchdog read timer value | R   | 0xFFFE C804        |

| MPU_WDT_TIMER_MODE | MPU watchdog timer mode       | R/W | 0xFFFE C808        |

Table 18. MPU Watchdog Control Timer Register (MPU\_WDT\_CNTL\_TIMER)

| MPU Byte Address = 0xFFFE C800, Byte Offset 0x00 |          |                                                                                                                                                                     |     |                |

|--------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|

| Bits                                             | Name     | Description                                                                                                                                                         | R/W | Reset<br>Value |

| 15-12                                            | RESERVED | Reserved.                                                                                                                                                           | R/W |                |

| 11-9                                             | PTV      | Prescale clock timer value Clock divisor = 2 <sup>(PTV+1)</sup> if the timer is in house-keeping mode. Clock divisor is fixed 256 if the timer is in watchdog mode. | R/W | 0              |

| 8                                                | AR       | Auto-reload/One-shot timer when in housekeeping mode.                                                                                                               | R/W | 0              |

|                                                  |          | 0: One-shot timer.                                                                                                                                                  |     |                |

|                                                  |          | 1: Auto-reload timer.                                                                                                                                               |     |                |

Table 18. MPU Watchdog Control Timer Register (MPU\_WDT\_CNTL\_TIMER) (Continued)

| Bits | Name     | Description                                                                                                          | R/W | Reset<br>Value |

|------|----------|----------------------------------------------------------------------------------------------------------------------|-----|----------------|

| 7    | ST       | Start/Stop timer when in housekeeping mode                                                                           | R/W | 0              |

|      |          | 0: Stop the timer.                                                                                                   |     |                |

|      |          | 1: Start the timer.                                                                                                  |     |                |

| 6-2  | RESERVED | Reserved.                                                                                                            |     |                |

| 1    | FREE     | It defines the behavior of the MPU watchdog timer in housekeeping mode when the debugger halts its parent processor. | R/W | 1              |

|      |          | 0: Stop counting even if ST =1.                                                                                      |     |                |

|      |          | 1: Keep counting if ST=1.                                                                                            |     |                |

|      |          | The MPU watchdog timer keeps counting in watchdog mode, regardless of this bit value.                                |     |                |

| 0    | RESERVED | Reserved.                                                                                                            |     |                |

Table 19. MPU Watchdog Load Timer Register (MPU\_WDT\_LOAD\_TIMER)

| MPU Byte Base Address = 0xFFFE C800, Offset = 0x04 |                        |                                                                                   |     |                |

|----------------------------------------------------|------------------------|-----------------------------------------------------------------------------------|-----|----------------|

| Bit                                                | Name                   | Description                                                                       | R/W | Reset<br>Value |

| 15-0                                               | MPU_WDT_<br>LOAD_TIMER | Housekeeping mode: This value is loaded when the timer expires or when it starts. | W   | 0xFFFF         |

|                                                    |                        | Watchdog mode: Reload the timer with this value.                                  |     |                |

Table 20. MPU Watchdog Read Timer Register (MPU\_WDT\_READ\_TIMER)

| MPU Byte Base Address = 0xFFFE C800, Offset = 0x04 |                        |                      |     |                |

|----------------------------------------------------|------------------------|----------------------|-----|----------------|

| Bit                                                | Name                   | Description          | R/W | Reset<br>Value |

| 15-0                                               | MPU_WDT_<br>READ_TIMER | Current timer value. | R   | 0xFFFF         |

Table 21. MPU Watchdog Timer Mode Register (MPU\_WDT\_TIMER\_MODE)

| MPU Byte Base Address = 0xFFFE C800, Offset = 0x08 |              |                                                                                                                                  |     |                |

|----------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------|-----|----------------|

| Bit                                                | Name         | Description                                                                                                                      | R/W | Reset<br>Value |

| 15                                                 | WATCHDOG     | Write access                                                                                                                     | W   | 1              |

|                                                    |              | 1: Switch the timer mode back to watchdog mode.                                                                                  |     |                |

|                                                    |              | 0: No effect.                                                                                                                    |     |                |

| 14-8                                               | RESERVED     | Reserved.                                                                                                                        |     |                |

| 7-0                                                | WATCHDOG_DIS | Write access only                                                                                                                | W   | 0              |

|                                                    |              | Writing a predefined sequence (0xF5, followed by 0xA0) in this field switches the timer from watchdog mode to housekeeping mode. |     |                |

|                                                    |              | After receiving 0xF5, if the second write access is different from 0xA0, the MPU and DSP cores are reset.                        |     |                |

# 3.6 DSP Watchdog Timer Registers

Table 22 shows the DSP watchdog timer registers. All of the registers are I/O space mapped. Table 23 through Table 26 describe the register bits.

Table 22. DSP Watchdog Timer Registers

| Register Name      | Description                   | R/W | DSP (Word) Address<br>(I/O Space) |

|--------------------|-------------------------------|-----|-----------------------------------|

| DSP_WDT_CNTL_TIMER | DSP watchdog control timer    | R/W | 0x3400                            |

| DSP_WDT_LOAD_TIMER | DSP watchdog load timer       | W   | 0x3402                            |

| DSP_WDT_READ_TIMER | DSP watchdog read timer value | R   | 0x3402                            |

| DSP_WDT_TIMER_MODE | DSP watchdog timer mode       | R/W | 0x3404                            |

Table 23. DSP Watchdog Control Timer Register (DSP\_WDT\_CNTL\_TIMER)

|       | DSP Word Base Address = 0x3400, Word Offset = 0x00 |                                                                                                                             |     |                |  |  |

|-------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|----------------|--|--|

| Bit   | Name                                               | Description                                                                                                                 | R/W | Reset<br>Value |  |  |

| 15-12 | Reserved                                           | Reserved.                                                                                                                   |     |                |  |  |

| 11-9  | PTV                                                | Prescale clock timer value Clock divisor = $2^{(PTV+1)}$ in housekeeping mode. Clock divisor is fixed 256 in watchdog mode. | R/W | 0              |  |  |