SBAA335-January 2019

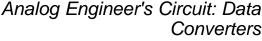

# Programmable voltage output with sense connections circuit

Garrett Satterfield

### **Design Goals**

**TRUMENTS**

| DAC Output<br>Voltage | Output Voltage V <sub>LOAD</sub> | Minimum Load<br>Resistance R <sub>LOAD</sub> | Maximum Line<br>Resistance<br>Compensation | Error      |

|-----------------------|----------------------------------|----------------------------------------------|--------------------------------------------|------------|

| 0V-5V                 | 0V-10V                           | 1kΩ                                          | +25% of R <sub>LOAD</sub>                  | <0.25% FSR |

### **Design Description**

The programmable voltage output with sense connections circuit provides a precise voltage across a load, compensating for parasitic series resistance. The amplifier A1 uses feedback from the high-side and lowside of the attached load to accurately regulate the voltage between V<sub>SENSE+</sub> and V<sub>SENSE+</sub>. The digital-toanalog converter (DAC) output and discrete resistors set the voltage across the load. This circuit is used in applications where additional line resistance may be present and must be compensated for by increasing the output voltage to deliver the correct voltage to the load. Common end equipment that use this circuit include PLC Analog Output Modules, Memory and Semiconductor Test Equipment, Spectroscopy, and Data Acquisition (DAQ) Cards.

### **Design Notes**

- 1. Select a DAC with low total unadjusted error (TUE) and with the required resolution for the application. A DAC with integrated reference, like the DAC80501 device, can be used to minimize components and solution size.

- 2. Choose a high-voltage amplifier, with rail-to-rail output to ensure sufficient output swing to drive the load and line resistance. The amplifier should have low offset voltage and offset voltage drift so it does not significantly contribute to output error.

- 3. Resistor mismatch directly contributes to gain error at the output. Use resistors with 0.05% tolerance or better and low thermal drift.

- 4. For correct compensation of additional line resistance the ratio of R2:R4 must match the ratio of R3:R1 as closely as possible.

- 5. The amplifier supply voltage is chosen based on the required output voltage, additional line resistance, and amplifier output swing at maximum load current.

- 6. To reduce error at zero-scale a negative voltage can be supplied to the amplifier.

### **Design Steps**

1. The transfer function for  $V_{OUT}$  based on DAC voltage and resistor values is:

$$V_{LOAD} = \frac{R3}{R1} \cdot V_{DAC} \ ; \ \frac{R3}{R1} = \frac{R4}{R2}$$

2. A 50-k $\Omega$  resistance is chosen for R3. A relatively large value should be selected to reduce the current in the feedback paths. R1 is then calculated:

$$R1 = \frac{V_{DAC,FS}}{V_{LOAD,FS}} \cdot R3 = \frac{5V}{10V} \cdot 50 \,k\Omega = 25 \,k\Omega$$

- 3. R4 and R2 are chosen equal to R3 and R1, respectively.

- Calculate the maximum load current based on the minium load resistance and full scale V<sub>LOAD</sub>. The

maximum load current impacts the amplifier output voltage swing and the additional line resistance the

circuit can compensate.

$$I_{LOAD,max} = \frac{\dot{V_{LOAD,FS}}}{R_{LOAD,min}} = \frac{10V}{1k\Omega} = 10mA$$

5. The required  $V_{CC}$  voltage is calculated to drive 25% additional load resistance and still maintain voltage regulation across  $R_{LOAD}$ .  $V_{O,rail}$  is the approximate amplifier output swing from V+ at a 10-mA load current.

$$V_{CC,min} = V_{O,rail} + 0.25 \cdot R_{LOAD,min} \cdot I_{LOAD,max} + V_{LOAD,FS} = 500 \text{mV} + 250 \Omega \cdot 10 \text{mA} + 10 \text{V} = 13 \text{V}$$

6. The output error can be approximated based on the DAC TUE, amplifier offset voltage, resistor tolerance, and reference initial accuracy using root sum square (RSS) analysis.

Output TUE(%FSR) =

$$\sqrt{\text{TUE}_{DAC}^2 + \left(\frac{V_{OS}}{\text{FSR}} \cdot 100\right)^2 + 4 \cdot \text{R}^2_{\text{Tol}} + \text{Accuracy}_{Ref}^2} = \sqrt{0.1^2 + \left(\frac{100 \mu V}{5 V} \cdot 100\right)^2 + 4 \cdot 0.05^2 + 0.1^2} = 0.173\%$$

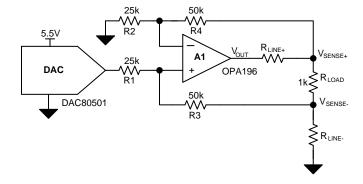

# **DC Transfer Characteristic**

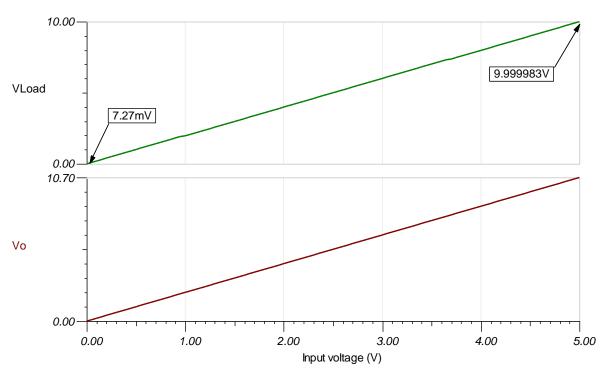

# **Small-Signal Step Response**

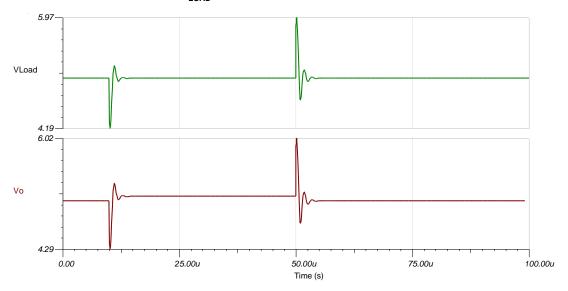

# Load Transient 10-k $\Omega$ to 5-k $\Omega$ $R_{\text{\tiny LOAD}}$

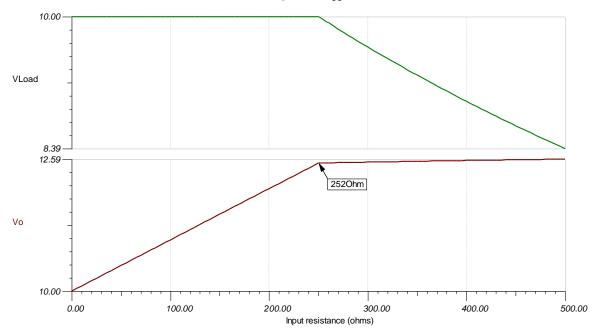

# Maximum Additional Line Resistance at Amplifier $V_{cc}$ = 13V

#### www.ti.com

### **Devices**

| Device   | Key Features                                                                                           | Link                               | Other Possible Devices   |

|----------|--------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------|

| DACs     |                                                                                                        |                                    |                          |

| DAC80501 | 16-bit resolution, 1-LSB INL, single-channel, voltage output DAC with 5ppm/°C internal reference       | http://www.ti.com/product/DAC80501 | http://www.ti.com/pdacs  |

| DAC81416 | 16-bit resolution, 1-LSB INL, 16-channel ±20-V high-voltage output DAC with 5ppm/°C internal reference | http://www.ti.com/product/DAC81416 | http://www.ti.com/pdacs  |

| DAC80508 | 16-bit resolution, 1-LSB INL, octal-channel, voltage output DAC with 5ppm/°C internal reference        | http://www.ti.com/product/DAC80508 | http://www.ti.com/pdacs  |

| Op Amps  |                                                                                                        |                                    |                          |

| OPA196   | Low-offset (100µV), Low-drift, rail-to-rail I/O, 2.25-V to 36-V supply                                 | http://www.ti.com/product/OPA196   | http://www.ti.com/opamps |

| TLV170   | Cost-sensitive, rail-to-rail output, 2.7-V to 36-V supply                                              | http://www.ti.com/product/TLV170   | http://www.ti.com/opamps |

| OPA192   | Precision, ultra-low offset (5µV) and drift, rail-to-rail I/O, 4.5-V to 36-V supply                    | http://www.ti.com/product/OPA192   | http://www.ti.com/opamps |

## Links to Key Files

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

Download source files for Programmable Voltage Output with Sense Connections – http://www.ti.com/lit/zip/sbac228.

For direct support from TI Engineers use the E2E community: e2e.ti.com.

### Other Links

Learn more about how to design with precision DACs in our *Precision DAC Learning Center*.

Learn more about TI's precision DAC portfolio and find additional technical resources: http://www.ti.com/data-converters/dac-circuit/precision/overview.html.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated