TI Designs: TIDEP-0067

# 66AK2Gx DSP + ARM Processor Power Solution Reference Design

# **TI Designs**

This TI Design is a power reference platform based on the K2G Multicore DSP + ARM® System-on-Chip (SoC) and companion TPS65911x power management integrated circuit (PMIC). This power solution design also includes the first stage buck converters to support a 12-V input and the DDR termination regulator for DDR3L memory. The reference design is tested and includes hardware reference (EVM), software (Processor SDK) and test data.

#### **Design Resources**

Tool Folder Containing Design Files TIDEP0067 66AK2G12 Product Folder TPS65911 Product Folder **TPS54620** Product Folder **TPS54429** Product Folder K2G General Purpose **EVM Tool Folder** K2G 1GHz GP EVM **EVM Tool Folder** Processor SDK for K2G **Download Software**

ASK Our E2E Experts

#### **Features**

- TPS54620 and TPS54429: The First Stage Buck Converters to Convert a 12-V input to 3.3-V and 5-V Outputs.

- TPS65911x Companion PMIC Supporting Power Sequencing and Power Supplies Required for the SoC and DDR3L Memory.

- The TPS65911x Offers an Integrated Real-Time Clock (RTC) for Time-Critical Applications.

- LP2996A DDR3L Termination Regulator.

# **Applications**

- Automotive Audio Amplifiers

- Home Audio

- · Professional Audio

- Power Protection

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

Introduction www.ti.com

#### 1 Introduction

This TI Design is a power reference platform based on the K2G Multicore DSP + Arm® System-on-Chip (SoC) and companion TPS65911x power management integrated circuit (PMIC). This power solution design also includes the first stage buck converters to support a 12 V input and the DDR termination regulator for DDR3L memory. The reference design is tested and includes hardware reference (EVM), software (Processor SDK) and test data.

### 2 K2G GP EVM Power Solution Block Diagram

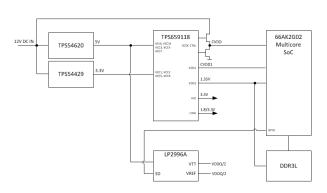

The first stage buck converter devices TPS54620 and TPS54429 convert the 12-V DC input of the EVM to 5 V and 3.3 V respectively. The 5-V output from the TPS54620 provides the inputs to TPS65911x and LP2996A. The 3.3-V output form TPS54429 provides the input to TPS65911x, and 3.3-V peripheral devices on the EVM. TPS65911x provides all power supplies required for the 66K2Gx Multicore SoC, except for the 3.3-V I/O power supply.

Figure 1 shows the block diagram of the power solution on the K2G GP EVM.

Figure 1. K2G General Purpose EVM Power Solution Block Diagram

www.ti.com K2G EVM Overview

#### 3 K2G EVM Overview

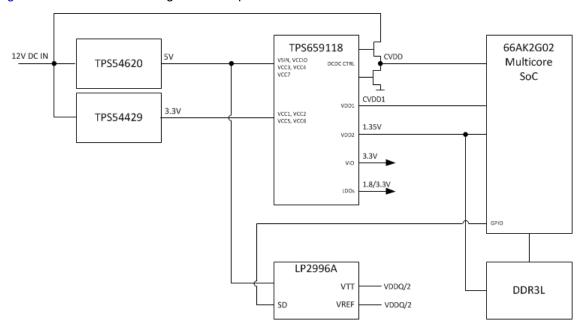

The K2G GP EVM is intended to exercise the key interfaces on the K2G device. The K2G GP EVM includes the following features:

- Memory

- 2 GB of DDR3L with ECC (32-bit data + 4-bit ECC)

- 512 Mbit of QSPI Flash

- 2 Gbit of NAND Flash

- 128 Mbit of SPI Flash

- 128 kByte of 12C EEPROM for Boot support from 12 C

- 16 GByte eMMC

- Micro-SD Card slot (32 GB micro-SD card included)

- Connectivity

- Gbit Ethernet: RGMII through Micrel KSZ9031 PHY RJ45 jack

- USB 2.0 x 2: Micro A/B connector, Host connector

- PCIe Gen 2: Single lane card slot (root complex only)

- COM8 connector for use with WiLink 8 modules

- Display

- 4.3" Touch LCD display (sold seperately)

- HDMI Tx

- Audio

- AIC3106 stereo code

- 3.5 mm stereo jack x2 supports stereo analog input and output

- All McASP signals routed to audio expansion connector

- General Purpose Serial

- SPI and 12C ports not already used for memory, or control are routed to serial expansion connector

- UART through RS232 chip and DB9 connector, UART over USB

- Automotive

- MLB supported through expansion connector

- DCAN supported through transceivers, DB9 connectors

- Emulation

- Onboard XDS200 through mini-USB connector

- MIPI-60 header for external emulators

- TRACE is supported with some caveats (resistor-muxed with display signals)

- Power

- Provided through TPS65911x PMIC factory-programmed with K2G power-up sequence

- 3 step-down DC–DC converters

- 8 LDOs

- 12C and enable signals

- Board Management Controller

- Mainly intended for automated testing; not intended for end-products

- May control boot modes, power-up, and more

- Character display for system status

- Clocking

- K2G is unique among K2 devices because the K2G generates most clocks internally, including audio frequency clocks. DDR, USB, Ethernet, and more. Clocks may be generated internally. This is the default mode on the EVM.

K2G EVM Overview www.ti.com

A CDCM6209 is also included and generates SYSCLK, DDR ref clock, USB clcok, and PCIe clock.

Figure 2 shows the K2G general purpose EVM.

Figure 2. K2G General Purpose EVM

www.ti.com Software

#### 4 Software

Software for the K2G EVM is available by downloading the Processor SDK.

#### 5 K2G EVM

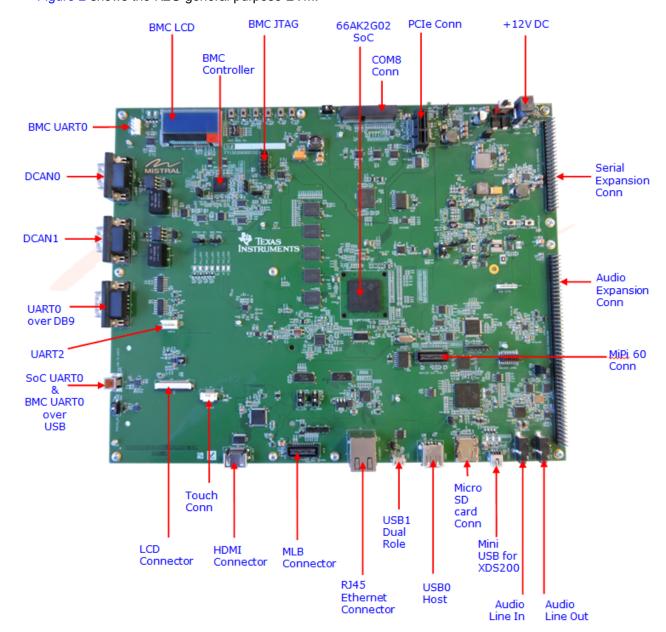

The 66AK2Gx SoC supports the following features:

- Processor Cores and Memory

- ARM Cortex A15 up to 1000 MHz

- 32 KB L1D, 32 KB L1P, 512 KB, L2 cache

- C66x DSP up to 1000 MHz

- 32 KB L1D, 32 KB L1P, 1 MB L2

- ECC on all memory

- Industrial and Control Peripherals

- 2 Industrial Communication Subsystems enable cut through, real-time and low latency industrial Ethernet protocols

- Programmable real-time I/O enables versatile field bus and control interfaces

- · Security and Crypto

- Standard secure boot with customer programmable OTP keys

- Crypto

- Package

- 21 x 21 mm, 0.8-mm pitch BGA 625 pins

K2G EVM www.ti.com

Figure 3 shows the 66AK2G12 diagram.

Copyright © 2016, Texas Instruments Incorporated

Figure 3. 66AK2G12 Diagram

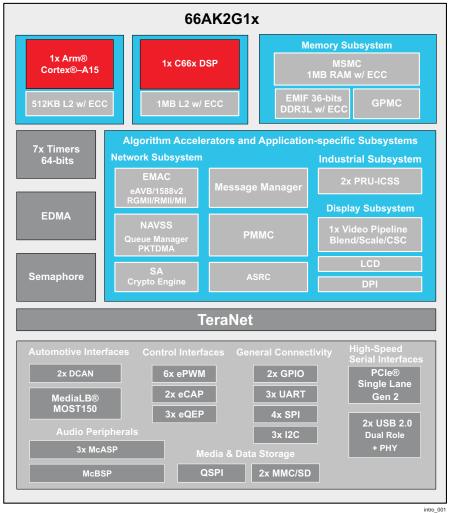

# 6 TPS65911x Power Management Integrated Circuit (PMIC)

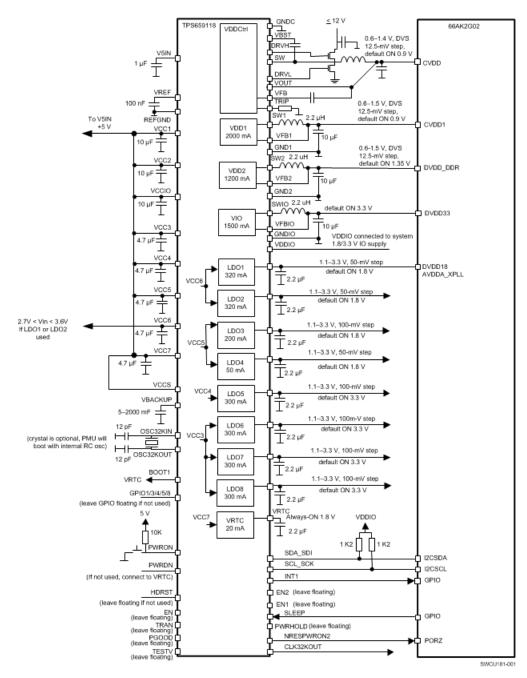

The TPS65911x is an integrated power management IC configured to operate with the 66AK2Gx SoC, combining three switch-mode buck converters, one switch-mode buck controller, and 8 linear regulators into a single BGA package. The PMIC handles power-supply sequencing and reset conditions, provides GPIO outputs for enabling external regulators or switches, and accepts i2c instructions from the processor for features such as voltage scaling and interrupt masking of various event or fault notifications. The TPS659118 is optimized to power a 66AK2G02 system, utilizing a one-time-programmable (OTP) memory configured with boot voltages, power sequencing, and other default conditions. The TPS65911A is optimized to power a 66AK2G12 system. The PMIC and processor must be connected correctly in order to meet the defined voltage, current, and sequencing requirements of the processor. A detailed lock diagram of the power management solution for the 66AK2Gx using the TPS65911x is shown in Figure 4. The TPS659118 User's Guide to Power 66AK2G02 (SWCU176) describes these connections, as well as the OTP settings defined within the PMIC. The TPS65911A User's Guide to Power 66AK2G12 (SWCU176)

Figure 4. TPS659118 PMIC with 66AK2G02

www.ti.com Test Data

# 7 Test Data

# 7.1 Power-Up Sequence Specification

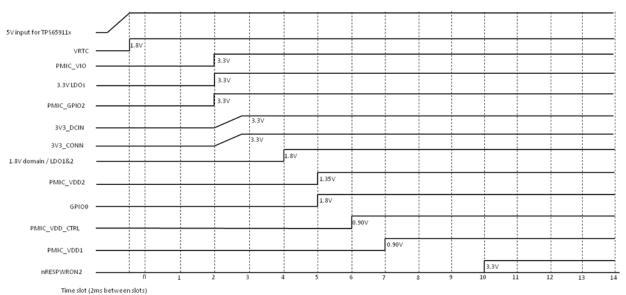

Figure 5 shows the TPS65911x power-up sequencing timing.

Figure 5. TPS65911x Power Sequencing

Test Data www.ti.com

# 7.2 Power-Up Sequence Waveforms

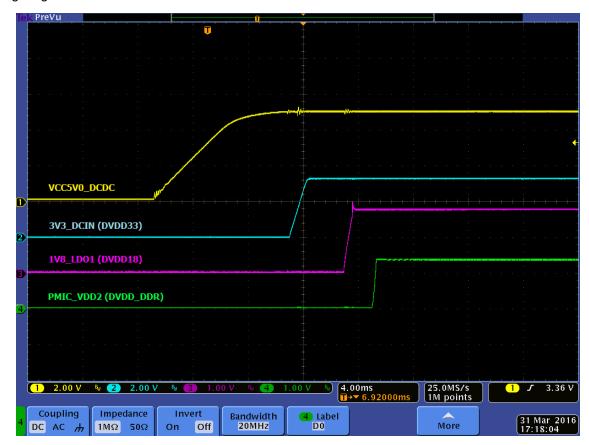

The following waveforms demonstrate the power-on of the TPS65911x as required by the 66AK2Gx.

Figure 6 shows the power-on sequence for each of the output voltage rails and nRESPWRON2 signal respectively. The 3.3 V, 1.8 V, 1.35 V, CVDD, and CVDD1 rails turn sequentially and the nRESPWRON2 signal goes *HIGH* after all rails are *ON*.

Figure 6. Power-On Sequence for the TPS65911x

Table 1 lists the delay time for the 3.3 V, 1.8 V, and 1.35 V processor power supplies.

Table 1. Delay Time for the 3.3 V, 1.8 V, and 1.35 V Processor Power Supplies

| PLOT   | EXPECTED TIMING | ACTUAL TIMING |

|--------|-----------------|---------------|

| 1 to 2 | N/A             | 10.0 ms       |

| 2 to 3 | 4.0 ms          | 4.0 ms        |

| 2 to 4 | 6.0 ms          | 6.0 ms        |

| 3 to 4 | 2.o ms          | 2.0 ms        |

www.ti.com Test Data

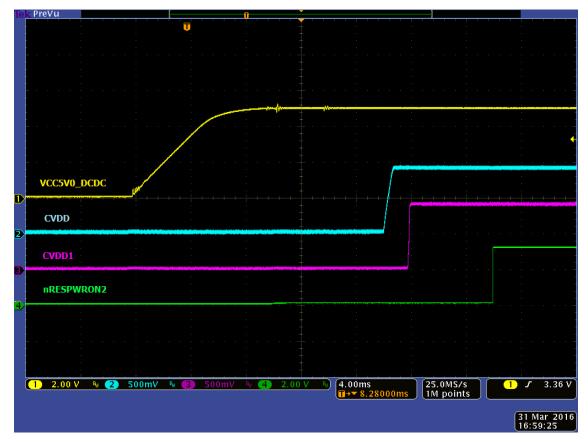

Figure 7 shows the power-on sequence for the TPS65911x with nRESPWRON2.

Figure 7. Power-On Sequence for the TPS65911x With nRESPWRON2

Table 2 lists the delay time for the CVDD and CVDD1 processor power supplies and power on reset (POR) signal.

Table 2. Delay Time for the CVDD and CVDD1 Processor Power Supplies and Power On Reset (POR) Signal

| PLOT   | EXPECTED TIMING | ACTUAL TIMING |

|--------|-----------------|---------------|

| 1 to 2 | N/A             | 18.4 ms       |

| 2 to 3 | 2.0 ms          | 2.0 ms        |

| 2 to 4 | 8 ms            | 8.0 ms        |

| 3 to 4 | 6 ms            | 6 ms          |

Design Files www.ti.com

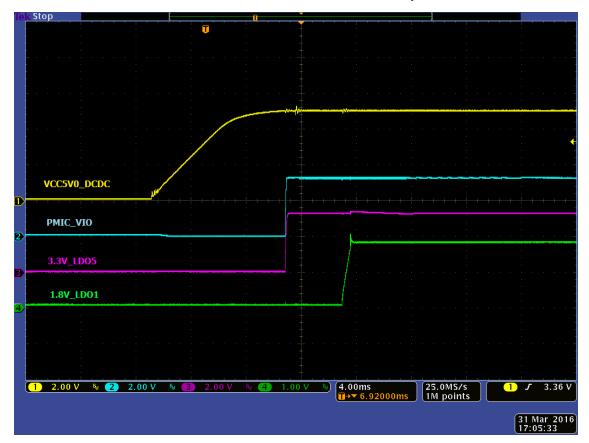

Figure 8 shows the 3.3 V VIO buck converter, 3.3 V LDO5 and 1.8 V LDO1 of the TPS65911x. The 3.3 V PMIC\_VIO buck converter and the 3.3 V\_LDO turn *ON* simultaneously.

Figure 8. Power-On Sequence for the TPS65911x Voltage Rails

# 8 Design Files

To download the design files for TIDEP0067, see the design files at http://www.ti.com/tool/TIDEP0067.

# 8.1 Trademarks

Arm is a registered trademark of ARM Limited.

www.ti.com Revision History

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (May 2016) to A Revision |                                                                              | Page |   |

|------------------------------------------------|------------------------------------------------------------------------------|------|---|

| •                                              | Added 66AK2G12 Product Folder                                                |      | 1 |

| •                                              | Added link to EVMK2GX Tool Folder (1GHz K2G GP EVM)                          | ′    | 1 |

| •                                              | Changed "at 600 MHz" to "up to 1000 MHz" for both Cortex-A15 and C66x cores. | {    | 5 |

| •                                              | Changed 66AK2G02 block diagram to 66AK2G12 block diagram                     | (    | ô |

| •                                              | Added distinction between TPS659118 and TPS65911A                            | 7    | 7 |

|                                                |                                                                              |      |   |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ("TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated