# TI Designs: TIDA-01379 Transient Load Generator Reference Design

# 🦉 Texas Instruments

# Description

This reference design permits to generate fast load transient signals required for the evaluation of converter stability. The board includes three separable load transient generators that are either regulated or not regulated and are able to support different load configurations. The loads can be referenced to ground or floating.

#### Resources

TIDA-01379 CSD17304Q3 CSD25404Q3 CSD18534Q5A OPA365 Design Folder Product Folder Product Folder Product Folder Product Folder

ASK Our E2E Experts

## Features

- Fast Transients

- Floating and GND-Referenced Loads

- Regulated

- Isolated

#### Applications

Power Supply Testing

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

Power supplies are present in all electronic devices where they power the needed supply rails. These rails need to be maintained at a certain level under the specified operating conditions, including load transient events. A load transient event happens when the load current changes suddenly from one level to another. The response of a converter to such changes permits to assess its stability.

The TIDA-01379 design board includes three different circuits that are used to perform load transient measurements for different load configurations. These circuits provide faster rise and fall times than commercial transient generators at a lower cost.

# 1.1 Key System Specifications

| PARAMETER                   | SPECIFICATIONS |

|-----------------------------|----------------|

| Load current                | ≥ 500 mA       |

| Rise and fall time          | < 1 µs         |

| Maximum load output voltage | 20 V           |

#### **Table 1. Key System Specifications**

# 2 System Overview

# 2.1 Block Diagram

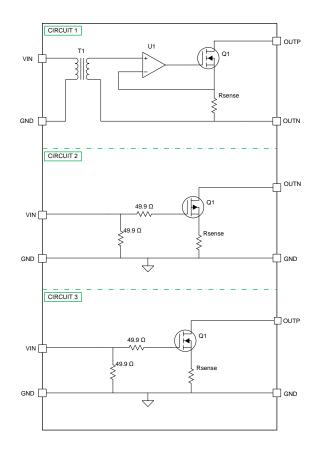

Figure 1. TIDA-01379 Block Diagram

System Overview

www.ti.com

# 2.2 Highlighted Products

#### 2.2.1 CSD17304Q3

The CSD17304Q3 device is a 30-V, N-channel, NexFET™ power MOSFET with the following features:

- Optimized for 5-V gate drive

- Ultra-low Q<sub>g</sub> and Q<sub>gd</sub>

- Low thermal resistance

- Avalanche rated

- Pb-free terminal plating

For further details, see the CSD17304Q3 product page.

#### 2.2.2 CSD25404Q3

The CSD25404Q3 device is a -20-V, P-channel, NexFET power MOSFET with the following features:

- Ultra-low  $Q_{\alpha}$  and  $Q_{\alpha d}$

- Low thermal resistance

- Low R<sub>DS(on)</sub>

- · Halogen free

- RoHS compliant

For further details, see the CSD25404Q3 product page.

# 2.2.3 CSD18534Q5A

The CSD18534Q5A device is a 60-V, N-channel NexFET power MOSFET with the following features:

- Ultra-low Q<sub>q</sub> and Q<sub>qd</sub>

- Low thermal resistance

- Avalanche rated

- Logic level

- Pb-free terminal plating

For further details, see the CSD18534Q5A product page.

#### 2.2.4 OPA365

The OPA365 device is a rail-to-rail input and output operational amplifier with a gain bandwidth of 50 MHz. This amplifier has a slew rate of 25 V/ $\mu$ s and can settle to 0.01% in 0.3  $\mu$ s.

The OPA365 has the following features:

- Gain bandwidth: 50 MHz

- Zerø-crossover distortion topology:

- Excellent THD+N: 0.0004%

- CMRR: 100 dB (minimum)

- Rail-to-rail input and output

- Input 100 mV beyond supply rail

- Low noise: 4.5 nV/√Hz at 100 kHz

- Slew rate: 25 V/µs

- Fast settling: 0.3 µs to 0.01%

- Precision:

- Low offset: 100 µV

- Low input bias current: 0.2 pA

Transient Load Generator Reference Design

• 2.2- to 5.5-V operation

For further details, see the OPA365 product page.

# 2.3 System Design Theory

The following sections present three ways to generate fast transient signals for converter stability tests. These designs provide transient signals with a rise and fall time of less than 1  $\mu$ s for load steps from 0 to 500 mA with a limited bill of materials.

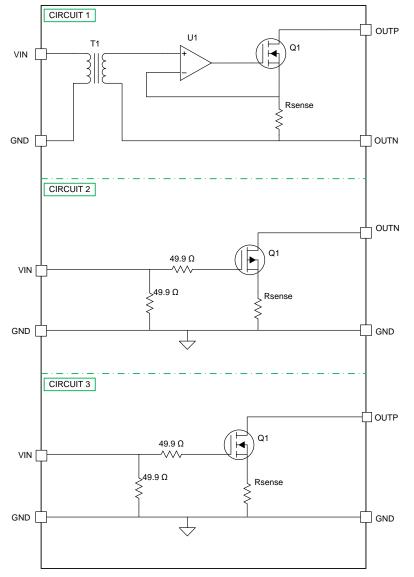

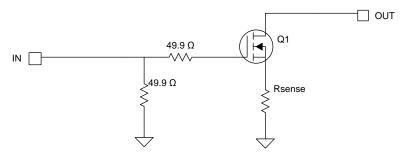

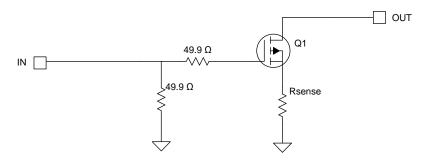

#### 2.3.1 Open-Loop Load Transient Generator

Figure 2 and Figure 3 are open-loop load transient generators for ground-referenced positive or negative outputs. These generators are mainly composed of the following:

- An NMOS transistor for positive outputs

- A PMOS transistor for negative outputs

- A sense resistor to measure the load current

The transistors Q1 and Q2 are operated in their linear regions as variable resistors. The adjustment of the gate voltage permits to control the value of the resistance between drain and source, thereby setting the load current. A pulse waveform with the right levels must be applied on the IN pin to get the required load step. A pulse signal with a low duty cycle must be used to optimize the power dissipation on the transistor and the sense resistor and to avoid overheating of the board. Because this simple transient generator is always stable, it is recommended to use it for the first stability assessment of a converter when it is unknown if the converter is stable or not.

Figure 2. Open-Loop Load Transient Generator for Positive Outputs

Figure 3. Open-Loop Load Transient Generator for Negative Outputs

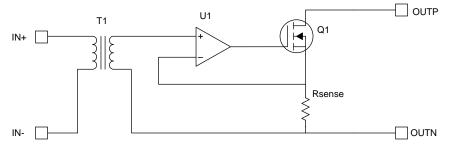

#### 2.3.2 Regulated Load Transient Generator

The circuits presented in Section 2.3.1 are unregulated, and the user needs to estimate and set the gate voltage input that is needed for each required load steps. To avoid this manual tuning, the regulated load transient generator on Figure 4 is used. It is composed of mainly the following:

- An NMOS transistor

- · An operational amplifier that is driving the gate of the transistor

- A transformer for galvanic isolation

- A sense resistor to measure the load current step

The gate of the transistor is driven by the amplifier and the feedback loop is between the transistor's source and the negative input of the amplifier. The transient load that is applied to the device under test (DUT) is then proportional to the sense resistor value and the amplifier input voltage. In this TI Design,  $R_{SENSE} = 1 \Omega$ , which means that this design has a 1:1 equivalence between the control input voltage and the load step value.

A 1:1 transformer is added to isolate the input from the signal generator and to give the possibility to apply a transient to ground-referenced DUTs as well as floating DUTs. Adding this transformer creates overshoots and undershoots on the input signal applied to the non-inverting input of the amplifier. These are damped with the addition of a resistor (10 k $\Omega$ ) across the transformer's secondary, which leads to some power loss.

To avoid that the transformer enters into saturation and a distortion of the input signal, 50% duty cycle pulse signals with symmetrical positive and negative levels must be used as input.

To select the amplifier, consider the following parameters to meet requirements in Table 1:

- Bandwidth  $f_{3dB} > 0.35/tr$ , with tr being the rise time of the input signal

- Slew rate that must be high enough to support the maximum rate of change of the amplifier's output

- Supply voltage range that shall permit to reach the expected amplifier's output voltage for the required maximum load

- Amplifier's output load capability

Consider the following parameters when selecting the transformer:

- Input level that must allow to transmit the input signal without distortion

- Frequency range of operation and volt-microsecond rating. There must be enough time between the rising and falling edges of the pulse input signal to see the complete converter response.

Figure 4. Closed-Loop Load Transient Generator

# 3 Hardware, Testing Requirements, and Test Results

# 3.1 Hardware

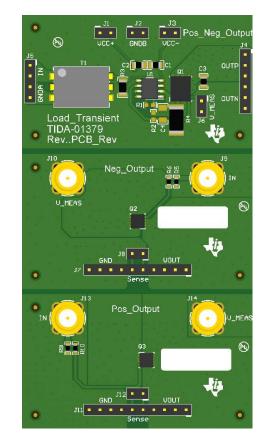

The TIDA-01379 design board is composed of three different load transient generators that can be split up and used separately.

#### 3.1.1 Connectors, Jumpers, and Test Points

Table 2, Table 3, and Table 4 give an overview of the connector and jumper connections of the evaluation board.

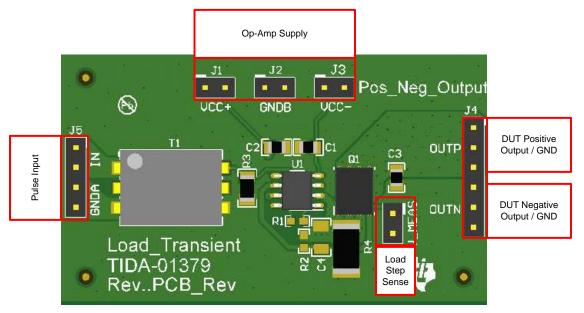

|    | CONNECTOR              | SIGNAL | PIN     | DESCRIPTION                             |

|----|------------------------|--------|---------|-----------------------------------------|

| J1 | Positive power supply  | VCC+   | 1, 2    | Positive power supply                   |

| J2 | Ground                 | GNDB   | 1, 2    | Secondary ground or DUT negative output |

| J3 | Negative power supply  | VCC-   | 1, 2    | Negative power supply                   |

| J4 | DUT output voltage     | OUTP   | 1, 2, 3 | DUT positive output                     |

|    |                        | OUTN   | 4, 5, 6 | DUT negative output                     |

| J5 | Input                  | VIN    | 1, 2    | Signal generator input                  |

|    |                        | GNDA   | 3, 4    | Primary ground                          |

| J6 | Load transient voltage | V_MEAS | 1       | Load transient voltage                  |

|    |                        | GNDB   | 2       | Secondary ground or DUT negative output |

#### Table 2. Connector Overview Circuit 1 (1)

<sup>(1)</sup> Circuit 1 corresponds to the top part of the board with the title "Pos\_Neg\_Output"

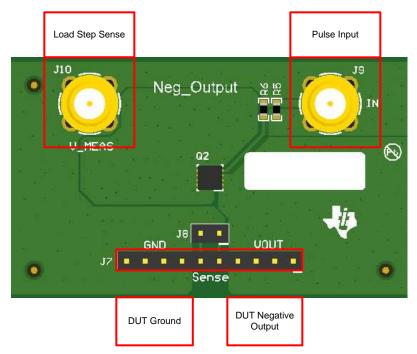

#### Table 3. Connector Overview Circuit 2 (1)

|     | CONNECTOR                | SIGNAL | PIN            | DESCRIPTION            |

|-----|--------------------------|--------|----------------|------------------------|

| J7  | DUT output voltage       | VOUT   | 1, 2, 3, 4     | Negative output        |

|     |                          | S-     | 5              | Negative output sense  |

|     |                          | GND    | 6, 7, 8, 9, 10 | Ground                 |

| J8  | DUT output voltage sense | S-     | 1              | Negative output sense  |

|     |                          | GND    | 2              | Ground                 |

| J9  | Gate drive input         | VIN    | —              | Signal generator input |

| J10 | Load transient voltage   | V_MEAS | —              | Load transient voltage |

<sup>(1)</sup> Circuit 2 corresponds to the middle part of the board with the title "Neg\_Output"

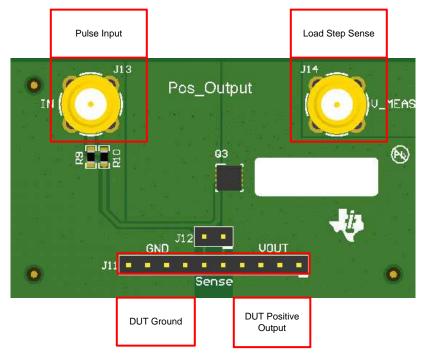

# Table 4. Connector Overview Circuit 3 <sup>(1)</sup>

|     | CONNECTOR                | SIGNAL | PIN            | DESCRIPTION            |

|-----|--------------------------|--------|----------------|------------------------|

| J11 | DUT output voltage       | VOUT   | 1, 2, 3, 4     | Positive output        |

|     |                          | S+     | 5              | Positive output sense  |

|     |                          | GND    | 6, 7, 8, 9, 10 | Ground                 |

| J12 | DUT output voltage sense | S+     | 1              | Positive output sense  |

|     |                          | GND    | 2              | Ground                 |

| J13 | Gate drive input         | VIN    | —              | Signal generator input |

| J14 | Load transient voltage   | V_MEAS | —              | Load transient voltage |

<sup>(1)</sup> Circuit 3 corresponds to the bottom part of the board with the title "Pos\_Output"

#### 3.2 Testing and Results

The three different circuits are used to evaluate the load transient response of the TPS65632 device. The TPS65632 is a triple-output ( $V_{POS}$ ,  $V_{NEG}$ , and AVDD) power supply used to drive AMOLED displays.

#### 3.2.1 Test Setup

To evaluate the different circuits, a signal generator, an oscilloscope, and a power supply are required.

#### 3.2.2 Test Results

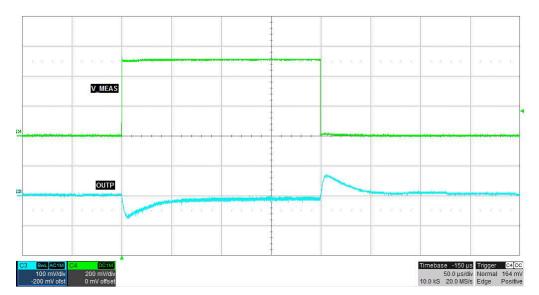

#### 3.2.2.1 Positive Output

The circuit in Figure 2 is used to evaluate the transient response of the VPOS boost converter. The load is connected between VPOS and GND as shown in Figure 5. Figure 6 shows that the converter is stable when a 500-mA load step with a rise and fall time of less than 250 ns is applied to it.

Figure 5. Board 3 Connection

Figure 6. Transient Response—Load Between VPOS and GND

# 3.2.2.2 Negative Output

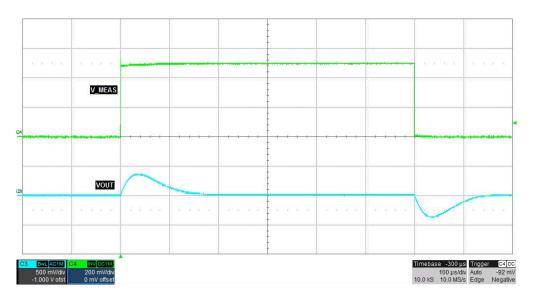

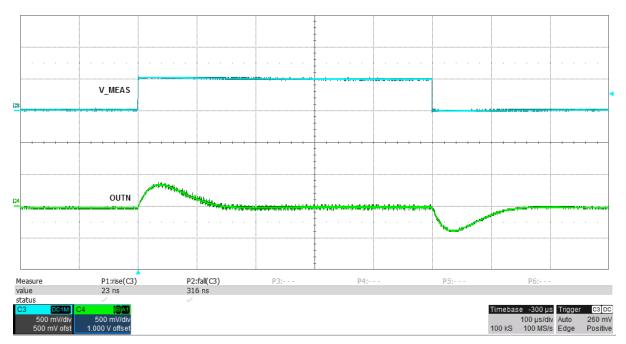

The circuit in Figure 3 is used to test the transient response of the VNEG inverting buck-boost converter as shown in Figure 7. The load transient signal has an amplitude of 500 mA and a rise and fall time of less than 250 ns.

Figure 7. Board 2 Connection

Figure 8. Transient Response—Load Between VNEG and GND

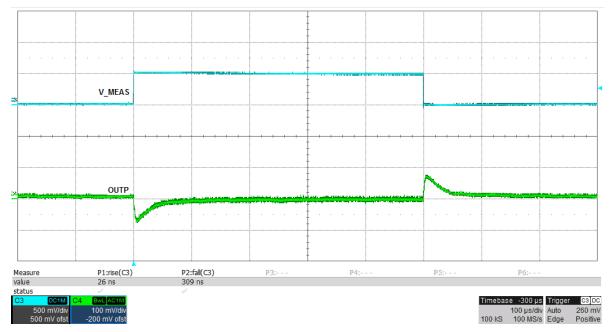

#### 3.2.2.3 Positive and Negative Outputs

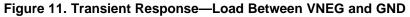

The circuit in Figure 4 permits to generate a load transient signal for ground referenced loads as well as floating loads. It is used to test the stability of the TPS65632 converters when a 500-mA load step is applied between VPOS and GND, between VNEG and GND, and between VPOS and VNEG. Figure 9 shows how to connect the different loads. Figure 10, Figure 11, and Figure 12 show that the 500-mA load step has different rise and fall times values of 25 ns and 320 ns, respectively.

Figure 9. Board 1 Connection

Figure 10. Transient Response—Load Between VPOS and GND

Figure 12. Transient Response—Load Between VPOS and VNEG

# 4 Design Files

# 4.1 Schematics

To download the schematics, see the design files at TIDA-01379.

# 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01379.

# 4.3 Layout Prints

To download the layer plots, see the design files at TIDA-01379.

# 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01379.

# 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01379.

# 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01379.

# 5 Related Documentation

- 1. Texas Instruments, *TPS65632 Triple-Output AMOLED Display Power Supply*, TPS65632 Datasheet (SLVSCY2)

- Texas Instruments, AN-1733 Load Transient Testing Simplified, SNOA507 Application Report (SNOA507)

# 5.1 Trademarks

TIDUCQ4-October 2017

Submit Documentation Feedback

NexFET is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated