# TI Designs: TIDA-01495 480-W, Thin-Profile (< 17-mm), 94% Efficiency, Fast Transient Response AC/DC SMPS Reference Design

# Texas Instruments

#### Description

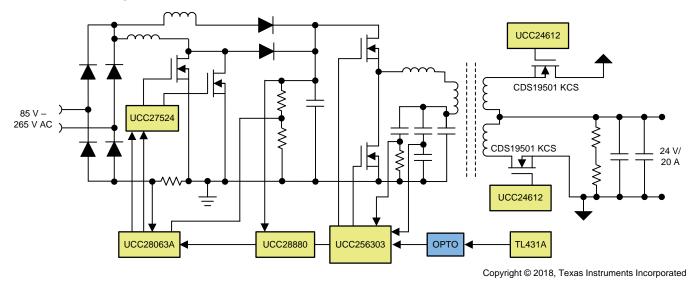

This low profile, fast transient response AC/DC SMPS reference design consists of a front-end, two-phase interleaved transition mode (TM) power factor correction (PFC) based on the UCC28063A, which minimizes the PFC inductor dimensions and reduces electromagnetic interference (EMI) filter requirements. The UCC256303 hybrid hysteretic control LLC controller controls the HB-LLC isolated DC/DC stage and ensures a fast transient response, which results in a reduced PFC bulk and output capacitor dimension. Phase shedding in the PFC stage and the advance burst mode optimization feature in the LLC stage help to obtain high efficiency at a 5% load (230-V AC). The UCC24612 multimode synchronous rectifier controller establishes a proportional gate drive, which reduces the conduction losses in the output rectifier of the LLC stage, to achieve this high-efficiency design.

#### Resources

| TIDA-01495  | Design Folder  |

|-------------|----------------|

| UCC28063A   | Product Folder |

| UCC256303   | Product Folder |

| UCC24612    | Product Folder |

| CSD19501KCS | Product Folder |

| TL431A      | Product Folder |

| UCC28880    | Product Folder |

| UCC27524    | Product Folder |

|             |                |

#### Features

- Thin Profile (Less Than 17-mm Height) for Use in Space-Constrained Applications With PCB Form Factor of 185 mm × 110 mm

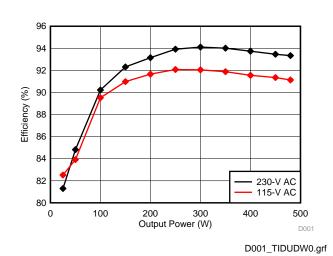

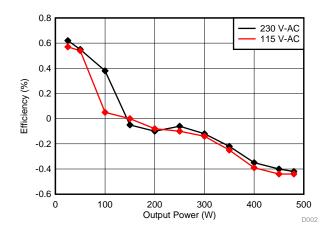

- Full Load Efficiency of Greater Than 93.3% (230-V AC) and Greater Than 91.1% (115-V AC) With Peak Efficiency of 94.1% (230-V AC) and 92% (115-V AC) Meets 80+ Platinum Standard

- Phase-Shedding Feature in PFC Stage and Advanced Burst Mode Feature in LLC Stage Enable High Efficiency at Light Load Conditions Greater Than 84% (230-V AC) and Greater Than 82% (115-V AC) at 5% Load

- ZCS Avoidance Feature and OVP Sensing Feature in LLC Controller Improves Robustness and Protects Systems From Overcurrent, Short Circuit, and Overvoltage to Ensure Safety

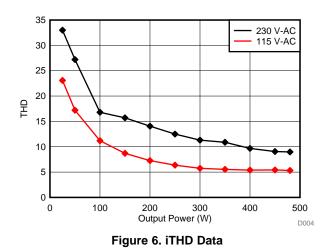

- High Power Factor Greater Than 0.99 and Meets PFC Regulations and Current THD per IEC 61000-3-2 Class A

- Designed to Meet EN55011 Class B Conducted Emissions Standard

#### Applications

- Industrial AC/DC

- Consumer AC/DC

- DIN Rail Power Supply

- Medical Power Supply

- Battery Chargers

480-W, Thin-Profile (< 17-mm), 94% Efficiency, Fast Transient Response AC/DC SMPS Reference Design

Copyright © 2018, Texas Instruments Incorporated

#### System Description

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

This reference design is a thin-profile, 480-W, high-efficiency AC/DC power supply for use in spaceconstrained, high-power-density applications. The design consists of a two-phase-interleaved, critical conduction mode (CrCM) PFC converter, which operates from an input voltage range of 85-V to 265-V AC<sub>RMS</sub> and generates a 390-V DC bus. The second stage comprises an isolated half-bridge (HB) LLC stage, which generates a 24-V, 20-A nominal output. This design demonstrates high-efficiency operation in a small form factor (185 x 110 x 17 mm) and delivers a continuous 480 W of power over the entire input operating voltage range from 85-V to 265-V AC. The design shows an efficiency greater than 93% for 230-V AC nominal operation and 91% for 115-V AC nominal operation.

The UCC28063A PFC integrated circuit (IC) controls the interleaved CrCM PFC stage. Interleaved critical conduction mode (CrCM) and continuous conduction mode (CCM) are the two popular topologies for PFC applications with greater than 300-W output power. CrCM PFC has the advantage of minimizing the turnon losses on the PFC MOSFET and eliminates the reverse recovery on the boost diode to reduce losses. CrCM PFC also has a much smaller inductor value than the CCM PFC. The reduced boost inductor value helps to develop the low-profile magnetics necessary for meeting the thin-profile requirement in the design. By interleaving two CrCM power stages, the effective input ripple current is reduced and helps to minimize the EMI filter requirement. The HB-LLC power stage is controlled through the stage of the art UCC256303 resonant controller which implements current mode control for increased control bandwidth. This increased control bandwidth reduces the PFC bulk and output capacitors required to suppress the AC ripple on the output. To achieve high efficiency, the output of the LLC stage uses synchronous rectification based on the UCC24612 device and the CSD19501KCS MOSFET.

The design has low standby power of < 400 mW and meets ENERGY STAR rating requirements as well as 2013 EU eco-design directive ErP Lot 6. The EMI filter is designed to meet EN55011 class-B conducted emission levels. The design is fully tested and validated for various parameters such as regulation, efficiency, EMI signature, output ripple, start-up, and switching stresses. Overall, the design meets the key challenges of industrial power supplies to provide safe and reliable power with all protections built-in, while delivering high performance with low power consumption and low bill-of-material (BOM) cost.

# 1.1 Key System Specifications

| PARAMETER                                   | SYMBOL                       | TEST CONDITIONS                                                          | MIN      | NOM   | MAX  | UNIT |

|---------------------------------------------|------------------------------|--------------------------------------------------------------------------|----------|-------|------|------|

| INPUT CONDITIONS                            |                              | · · · · · · · · · · · · · · · · · · ·                                    | I        | I     | I.   |      |

| Input voltage                               | V <sub>INAC</sub>            |                                                                          | 85       | 230   | 265  | V AC |

| Frequency                                   | f <sub>LINE</sub>            |                                                                          | 47       | 50    | 63   | Hz   |

| No load power                               | PSB                          |                                                                          |          | 400   |      | mW   |

| OUTPUT CONDITIONS                           |                              |                                                                          |          |       |      |      |

| Output voltage                              |                              |                                                                          |          | 24    |      | V    |

| Output current                              |                              |                                                                          |          | 20    |      | А    |

| Line regulation                             |                              | Both current and voltage                                                 |          |       | 0.5% |      |

| Load regulation                             |                              | Both current and voltage                                                 |          |       | 1%   |      |

| Output voltage ripple                       |                              | Peak to peak                                                             |          | 200   |      | mV   |

| Output power (nominal)                      | Po                           |                                                                          |          |       | 480  | W    |

| SYSTEM CHARACTER                            | ISTICS                       |                                                                          | <u>i</u> |       |      |      |

| Efficiency                                  | Н                            | $V_{IN} = 230$ -V AC <sub>RMS</sub> and full load at 24-V output         |          | 93.5% |      |      |

|                                             | п                            | V <sub>IN</sub> = 115 AC <sub>RMS</sub> and 230-W load<br>at 24-V output |          | 91.4% |      |      |

| Destautions                                 | Output<br>overcurrent        |                                                                          |          | 25    |      | А    |

| Protections                                 | Output<br>overvoltage        |                                                                          |          | 30    |      | V    |

| Operating ambient                           | Open frame                   | -10                                                                      | 25       |       | 55   | С    |

|                                             | Power line<br>harmonics      | As per EN55011 / EN55022 Class B                                         |          |       |      |      |

| Standards and norms                         | Conducted emissions          | EN55022 Class B                                                          |          |       |      |      |

|                                             | EFT                          | As per IEC-61000-4-4                                                     |          |       |      |      |

|                                             | Surge                        | As per IEC-61000-4-5                                                     |          |       |      |      |

| Board form factor (FR4 material, two-layer) | Length × breadth<br>× height | 180 mm × 110 mm × 17 mm                                                  |          |       |      | mm   |

# Table 1. Key System Specifications

3

System Overview

www.ti.com

#### 2 System Overview

#### 2.1 Block Diagram

Figure 1. TIDA-01495 Block Diagram

# 2.2 Highlighted Products

#### 2.2.1 UCC28063A

The UCC28063A is a two-phase, naturally-interleaved, transient-mode power factor correction (PFC) controller for implementing a high-efficiency, low-component-count, front-end AC/DC PFC stage. The two-phase interleaved power stage reduces the filter requirements for input current ripple electromagnetic interference (EMI).

The natural interleaving technique of the UCC28063A ensures that both phases operate at high efficiency while synchronized to the same switching frequency. The integrated brownout and dropout handling feature, the inrush-safe current limiting feature combined with the overvoltage protection, and the overcurrent protection feature increase the robustness of the PFC stage.

#### 2.2.2 UCC256303

Series resonant converters like LLC are one of the most widely used topologies for implementing mediumto-high power isolated DC/DC power stages in consumer and industrial power supplies. LLC resonant converters are quite popular due to their ability to achieve soft-switching (ZVS turnon) for high-voltage MOSFETs, thereby improving the overall efficiency of a system.

The UCC256303 has a unique, hybrid hysteretic control that provides excellent line and load transient response, minimizing the requirement for output filter capacitors. The wide frequency range of the device can be used to reduce the PFC bulk capacitor required to meet the holdup time requirement in the industrial power supplies. With the integrated high-voltage gate drive, X-Cap discharge function, and additional output overvoltage protection, the UCC256303 reduces the amount of external discreet components required to implement a high-efficiency industrial power supply.

#### 2.2.3 UCC24612-2

The UCC24612-2 is a multi-mode synchronous rectifier controller for active clamp flyback and LLC applications. Along with its 4-A sink and 1-A source capability, this device has a proportional gate drive, which helps when using this synchronous rectifier in LLC applications where the system can operate far above the resonant frequency. The adaptive off-time feature adds robustness to the synchronous rectifier by preventing false triggering.

### 2.2.4 CSD19501KCS

The CSD19501KCS is an 80-V NexFET<sup>TM</sup> power MOSFET, with 5.5-m $\Omega$  resistance and 38-nC gate charge. In this reference design, the CSD19501KCS is used as the synchronous field-effect transistor (FET) to lower the losses in the output stage of the LLC converter.

### 2.3 System Design Theory

This reference design provides a universal AC mains-powered, 480-W nominal output at 24 V and 20 A. This design comprises a front-end AC/DC PFC power stage followed by an isolated DC/DC LLC power stage.

### 2.3.1 PFC Regulator Stage Design

For high power levels such as 500 W, either the single-phase CCM PFC or interleaved CrCM PFC is the preferred topology for implementing PFC. Interleaved CrCM PFC offers certain advantages at these power levels because it ensures valley switching for the PFC MOSFET and ZCS turnoff diode, which reduces the losses in the PFC stage. Cheaper diodes can be used because the PFC diode does not have a hard turnoff. CrCM PFC requires a smaller PFC inductor. By interleaving two CrCM power stages, the overall input ripple current is also reduced. Alternatively, CCM PFC requires a larger inductor and is not very effective in low-profile designs.

This reference design uses the UCC28063A-based interleaved CrCM PFC. The following subsections detail the design process and component selection.

#### 2.3.1.1 Design Parameters

| SYMBOL                | PARAMETER                  | MIN | TYP   | MAX | UNIT |

|-----------------------|----------------------------|-----|-------|-----|------|

| INPUT                 | -                          |     |       |     |      |

| V <sub>IN</sub>       | Input voltage              | 85  |       | 265 | V AC |

| f <sub>LINE</sub>     | Input frequency            | 47  |       | 63  | Hz   |

| OUTPUT                | · ·                        |     |       |     |      |

| V <sub>OUT</sub>      | Output voltage             |     | 397   |     | V DC |

| P <sub>OUT(nom)</sub> | Output power               |     |       | 500 | W    |

|                       | Line regulation            |     |       | 5%  |      |

|                       | Load regulation            |     |       | 5%  |      |

| PF                    | Targeted power factor      |     | 0.99  |     |      |

| η                     | Targeted efficiency        |     | 97.3% |     |      |

| iTHD                  | Targeted input current THD |     | 5%    |     |      |

Table 2. Design Parameters for PFC Power Stage Design

### 2.3.1.2 Input Current Calculations

The input fuse, bridge rectifier, and input capacitor are selected based on the input current calculations. First, determine the maximum average output current,  $I_{OUT(max)}$ :

$$I_{OUT(max)} = \frac{P_{OUT(max)}}{V_{OUT(max)}}$$

(1)

$$I_{OUT(max)} = \frac{500}{390} = 1.28 \text{ A}$$

(2)

Calculate the maximum input root mean square (RMS) for the line current, I<sub>INrms(max)</sub>, using the parameters from the *Key System Specifications* and the initial assumptions of the efficiency and power factor:

$$I_{\text{INrms}(\text{max})} = \frac{P_{\text{OUT}(\text{max})}}{\eta \times V_{\text{IN}(\text{min})} \times \text{PF}}$$

(3)

**EXAS** *TRUMENTS*

www.ti.com

(6)

System Overview

$$I_{\rm INrms(max)} = \frac{500}{0.94 \times 85 \times 0.99} = 6.32 \text{ A}$$

(4)

#### 2.3.1.3 **Boost Inductor**

Calculate the boost inductor using the minimum input voltage and the minimum desired frequency of operation. First calculate the duty cycle, DUTY<sub>(max)</sub>, at the peak of the minimum input voltage:

$$DUTY_{(max)} = \frac{\left(V_{OUT(nom)} - V_{INrms(min)} \times \sqrt{2}\right)}{V_{OUT(nom)}}$$

(5)

$$DUTY_{(max)} = \frac{390 - (1.414 \times 85)}{390} = 0.691$$

(6)

Equation 7 calculates the boost inductor value.

$$L1 = L2 = \frac{\left(\eta \times \left(V_{INrms(min)}\right)^{2} \times DUTY_{(max)}\right)}{\left(P_{OUT(max)} \times F_{MIN}\right)}$$

(7)

$$L1 = L2 = \frac{0.95 \times 85^{2} \times 0.69}{500 \times 50000} = 195 \ \mu H$$

(8)

The actual value of the boost inductor used is 210 µH. Calculate the required saturation current for the boost inductor is calculated using Equation 9 for the minimum input voltage and under the assumption that both phases equally share the load.

$$I_{L(max)} = \left(\sqrt{2} \times \frac{P_{OUT(max)}}{V_{INrms(min)}}\right) = 8.3 \text{ A}$$

(9)

#### 2.3.1.4 **Output Capacitor**

For this application, choose the output capacitor such that the output ripple is kept below 25 V<sub>PK-PK</sub>. Equation 10 calculates the output capacitor.

$$C_{OUT} \ge 2 \times P_{OUT(max)} \times \frac{1}{V_{OUT} \times 4 \times \pi \times F_{LINE} \times V_{PFCRipple}}$$

(10)

$$C_{OUT} \ge 2 \times 500 \times \frac{1}{100} = 182.4 \text{ JmE}$$

$$C_{OUT} \ge 2 \times 500 \times \frac{1}{390 \times 4 \times \pi \times 47 \times 25} = 182.4 \,\mu\text{F}$$

(11)

In this reference design, two low-profile 100-µF capacitors are connected in parallel to form the PFC bulk capacitor.

#### 2.3.1.5 Current Sense Resistor

6

The current sense resistor detects the sum of the inductor currents through both phases. The overcurrent protection limit in UCC28063A is 200 mV. The required value of the current sense resistor is calculated for the lowest input voltage and a 25% overload condition. Estimate the peak current first (Equation 12) before calculating the current sense resistor:

$$I_{\text{PEAK}_{\text{CS}}} = \frac{2 \times \sqrt{2} \times P_{\text{OUT}(\text{max})} \times 1.25}{\eta \times V_{\text{INrms}(\text{min})}}$$

(12)

$$I_{\text{PEAK}_{\text{CS}}} = \frac{2 \times \sqrt{2} \times 500 \times 1.25}{0.95 \times 85} = 21 \text{ A}$$

(13)

This result gives the value of the current sense resistor as:

$$\operatorname{Rcs} = \frac{200 \,\mathrm{mV}}{21 \,\mathrm{A}} \cong 9 \,\mathrm{m}\Omega \tag{14}$$

This reference design uses two  $18 \text{-m}\Omega$  resistors in parallel.

### 2.3.1.6 PFC MOSFET

Equation 15 calculates the RMS current through the PFC MOSFET.

$$IDS_{rms} = \left(\frac{I_{PEAK_{CS}}}{2}\right) \times \sqrt{\frac{\frac{1}{6} - \left(4\sqrt{2} \times V_{INrms(min)}\right)}{9\pi \times V_{OUT_{PFC}}}}$$

$$IDS_{rms} = 3.715 \text{ A}$$

(15)

Select a MOSFET with a low figure of merit for this application. To maintain the overall height of the design to less than 17 mm, the PFC stage has been designed to switch at high frequency. The key MOSFET specifications that are important for minimizing losses in this design are:

- Low R<sub>DSon</sub>, for reducing the conduction losses in the MOSFET

- Low Q<sub>G</sub>, for fast turnoff

#### 2.3.1.7 PFC Diode

Equation 17 calculates the RMS current through the boost diode.

$$ID_{rms} = \left(\frac{I_{PEAK_{CS}}}{2}\right) \times \sqrt{\frac{\left(4\sqrt{2} \times V_{INrms(min)}\right)}{9\pi \times V_{OUT_{PFC}}}} = 2.26 \text{ A}$$

(17)

#### 2.3.1.8 Brownout Protection Configuration

The brownout voltage in UCC28063A can be set through the potential divider on the VINAC pin. In this reference design, the brownout voltage is set to 70 V with a hysteresis of 12 V. The following equations determine the value of the resistors in the potential divider network.  $R_A$  refers to the top three resistors in the potential divider (Equation 18) and  $R_B$  refers to the bottom resistor in the potential divider (Equation 18).

$$R_{A} = 12 \times \frac{1.414}{I_{BOHYS}} = \frac{17}{2 \times 10^{-6}} = 8.5 \text{ M}\Omega$$

(18)

Three resistors of 2.87 M $\Omega$  are connected in series to form R<sub>A</sub>, with the bottom resistor using Equation 19.

$$R_{\rm B} = \frac{1.4 \times R_{\rm A}}{70\sqrt{2} - 1.414} = 123.5 \,\rm K \tag{19}$$

A standard value of 123 k is chosen for RB.

#### 2.3.1.9 Control Loop Compensation

This design uses a type-2 compensator for the voltage loop compensation. Resistor R67 and capacitors C63 and C65 form the compensator. Start with a value of 7.5 K for R67. Place a zero close to 10 Hz to give a phase boost close to the gain crossover frequency. This zero is formed by R67 and C63.

$$C63 = \frac{1}{2\pi \times 10 \times 7500} = 2.12 \,\mu\text{F}$$

(20)

Choose a 2.2-µF capacitor for the C63 capacitor.

Place a pole at a frequency much lower than the lowest switching frequency, around 20 KHz, to attenuate the switching noise. This pole is formed by R67 and C65.

$$C65 = \frac{1}{2\pi \times 20000 \times 7500} = 1.06 \text{ nF}$$

(21)

Choose a 1-nF capacitor for C65.

7

# 2.3.1.10 Programming VOUT and HVSEN

System Overview

The VOUT pin sets the output voltage regulation point. To minimize the no-load losses, use high-value resistances to construct this potential divider network. Use three 3.01-M $\Omega$  resistors to form the top resistor (R<sub>c</sub>) in the potential divider. Calculate the bottom resistor (R<sub>D</sub>) using Equation 22.

$$R_{D} = V_{REF} \times \frac{R_{C}}{V_{OUT(nom)} - V_{REF}} = \frac{6 \times 9 \times 10^{6}}{390 - 6} = 140.6 \text{ k}\Omega$$

(22)

Use a value of 142 k $\Omega$  for  $R_{\scriptscriptstyle D}$

This reference design uses the HVSEN pin to set the fail-safe output overvoltage protection (OVP). Three 3.01-M $\Omega$  resistors form the top resistor (R<sub>E</sub>) in the potential divider. Calculate the bottom resistor (R<sub>F</sub>) using Equation 23.

$$\mathsf{R}_{\mathsf{F}} = \frac{4.87 \times \mathsf{R}_{\mathsf{E}}}{\mathsf{V}_{\mathsf{OUT}(\mathsf{pk})} - 4.87} = \frac{4.87 \times 9 \times 10^6}{450 - 4.87} = 98.46 \text{ k}\Omega$$

Use a value of 97.6 k $\Omega$  for  $R_{\scriptscriptstyle F}.$

# 2.3.2 LLC Converter Stage Design

Increased demands for high-power-density power supplies have resulted in the increase in switching frequency of the converters designed. While component sizes tend to decrease with an increase in the switching frequency, device switching losses (which are proportional to frequency) have significantly increased contributing to resulting in significant efficiency loss. Resonant converters use soft-switching techniques to alleviate switching loss problems and attain high efficiencies. Further, soft-switching helps attain low losses during light load conditions, very-low device stress, and reduced EMI.

The LLC resonant converter is based on the series resonant converter (SRC). By utilizing the transformer magnetizing inductor, zero-voltage switching can be achieved over a wide range of input voltage and load. As a result of multiple resonances, zero-voltage switching can be maintained even when the switching frequency is higher or lower than the resonant frequency.

In this design, the LLC converter operates at a high nominal switching frequency of around 180 kHz. This allows to minimize the dimension of the LLC transformer to meet the low profile requirements. The converter achieves the best efficiency when operated close to its resonant frequency at a nominal input voltage. As the switching frequency is lowered, the voltage gain is significantly increased. This allows the converter to maintain regulation when the input voltage falls low. These features make the converter ideally suited to operate from the output of a high-voltage boost PFC pre-regulator, allowing it to hold up through brief periods of AC line-voltage dropout.

With its hybrid hysteretic control and ZCS avoidance feature, the UCC256303 LLC controller enables safe operation of the LLC power stage while minimizing the dimension of the output capacitors. In addition, the controller delivers complete system protection functions including overcurrent, undervoltage lockout (UVLO), and overvoltage protection (OVP).

Table 3 lists the design parameters for the LLC power stage design.

480-W, Thin-Profile (< 17-mm), 94% Efficiency, Fast Transient Response

AC/DC SMPS Reference Design

| SYMBOL              | PARAMETER                   | MIN | TYP   | MAX | UNIT |

|---------------------|-----------------------------|-----|-------|-----|------|

| INPUT               |                             |     |       |     |      |

| V <sub>INDC</sub>   | Input voltage               | 250 | 397   | 410 | V DC |

| OUTPUT              |                             |     |       |     |      |

| V <sub>OUT</sub>    | Output voltage              |     | 24    |     | V DC |

| P <sub>OUT</sub>    | Max output power            |     | 480   |     | W    |

| f <sub>SW_nom</sub> | Nominal switching frequency |     | 180   |     | kHz  |

|                     | Line regulation             |     | 1     |     | %    |

|                     | Load regulation             |     | 1     |     | %    |

| η                   | Targeted efficiency         |     | 0.965 |     |      |

### Table 3. Design Parameters for LLC Power Stage Design

(23)

#### 2.3.2.1 Determine LLC Transformer Turns Ratio N

The LLC tank is designed to have a nominal gain,  $M_g$ , of 1 at the resonant frequency. Use Equation 24 to estimate the required turns ratio.

$$n = M_g \times \frac{\frac{V_{DCIN(nom)}}{2}}{V_O + V_F} : M_g = 1$$

where

- M<sub>a</sub> is the voltage gain,

- V<sub>DCIN(nom)</sub> is the nominal PFC output,

- V<sub>o</sub> is the output voltage,

- V<sub>F</sub> is the voltage drop across the synchronous rectifier.

From the specifications, the nominal values for input voltage and output voltage are 390 V and 24 V, respectively. Assuming an average drop of 100 mV on the synchronous rectifier, the turns-ratio can be calculated as:

$$n = 1 \times \left(\frac{390}{24 + 0.1}\right) = 8.07$$

(25)

The transformer turns ratio is set to 8.

#### 2.3.2.2 Determine M<sub>g min</sub> and M<sub>g max</sub>

Determine  $M_{q min}$  and  $M_{q max}$  using Equation 26 and Equation 27, respectively.

$$M_{g_{min}} = n \times \frac{(V_{O} + V_{F})}{\frac{V_{DCIN(max)}}{2}}$$

$$M_{g_{min}} = 8.0 \times \left(\frac{24.1 V}{\frac{410 V}{2}}\right) = 0.94$$

$$M_{g_{max}} = n \times \left(\frac{V_{0(nom)} + V_{F}}{\frac{V_{DCIN(min)}}{2}}\right)$$

$$M_{g_{max}} = 8.0 \times \left(\frac{24.1 V}{310 V}\right) = 1.285$$

$\left( \frac{2}{2} \right)$

(27)

9

The dimensioned  $M_{g_max}$  is increased to 1.1 times the required value to have some margin =  $M_{g_max}$  = 1.1 × 1.28543  $\approx$  1.426.

#### 2.3.2.3 Determine Equivalent Load Resistance (R<sub>e</sub>) of Resonant Network

Equation 28 calculates the equivalent load resistance at nominal and peak load under nominal output voltage and peak output voltage.

$$R_{e} = \frac{8 \times n^{2}}{\pi^{2}} \times \left(\frac{V_{O_{nom}}}{I_{O_{nom}}}\right)$$

$$R_{e_{nom}} = \frac{8 \times 8^{2}}{\pi^{2}} \times \left(\frac{24}{20}\right) = 62.31\Omega$$

(29)

TIDUDW0–February 2018 Submit Documentation Feedback 480-W, Thin-Profile (< 17-mm), 94% Efficiency, Fast Transient Response AC/DC SMPS Reference Design

Copyright © 2018, Texas Instruments Incorporated

(24)

(26)

#### System Overview

#### 2.3.2.4 Select Lm and Lr ratio (Ln) and Qe

Set the resonance point for the LLC converter close to 180 kHz to minimize the dimension of the LLC transformer set. The operating point of the LLC power stage is close to this frequency during a full load condition. Choose a value of Lr = 15  $\mu$ H and Cr = 66 nF to calculate the value of the resonant frequency as follows:

$$Fr = \frac{1}{2 \times \pi \times \sqrt{(Lr \times Cr)}} = 176 \text{ kHz}$$

(30)

The magnetizing inductance to resonant inductance ratio is chosen as 6:10.5 to develop a sufficient Q while simultaneously minimizing the magnetizing current in the LLC transformer. A planar core has been used to realize the LLC transformer. The required leakage inductance is provided through an additional shim inductor.

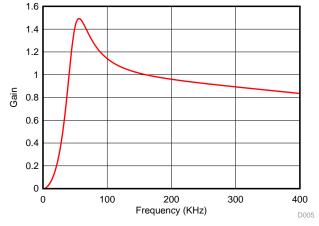

Figure 2 shows the Q curves for this design at full load conditions.

Figure 2. Q Curve at Full Load and Nominal Output Voltage

#### 2.3.2.5 Determine Primary-Side Currents

Use Equation 31 to calculate the primary-side RMS load current (I<sub>pri</sub>) at a full load condition:

$$I_{\text{pri}} = \frac{\pi}{2\sqrt{2}} \times \left(\frac{I_{\text{O}(\text{nom})}}{n}\right)$$

$$I_{\text{pri}} = 1.11 \times \left(\frac{20}{8.0}\right) = 2.775 \text{ A}$$

(32)

As calculated in Equation 33, the RMS magnetizing current ( $I_m$ ) at  $f_{SW_{min}} = 100$  kHz is:

$$I_{m} = \left(\frac{2\sqrt{2}}{\pi}\right) \times \left(n \times \frac{V_{O(nom)} + V_{f}}{2 \times \pi \times f_{SW}_{min} \times L_{M}}\right)$$

(33)

$$I_{m} = \left(\frac{2\sqrt{2}}{\pi}\right) \times \left(\frac{8.0 \times 24}{2 \times \pi \times 100 \text{ kHz} \times 150 \text{ }\mu\text{H}}\right) = 1.84 \text{ A}$$

(34)

Equation 35 calculates the resonant circuit current  $(I_r)$ :

$$I_{\rm r} = \sqrt{I_{\rm m}^2 + I_{\rm pri}^2}$$

(35)

$$I_{\rm r} = \sqrt{2.775^2 + 1.84^2} = 3.373 \text{ A}$$

(36)

This value is also equal to the transformer primary winding current at  $f_{SW\_min}$ .

10

(37)

(38)

11

#### 2.3.2.6 Determine Secondary-Side Currents

The secondary-side RMS currents can be calculated from the average load current. Assuming the LLC power stage is operating close to its second resonant frequency, the RMS current through each rectifier in the secondary-side push-pull output is calculated in Equation 37:

$$I_{\text{sec}\_\text{rms}} = I_{\text{sec}} \times \frac{\pi}{4} = 15.7 \text{ A}$$

where,

• I<sub>sec</sub> is the full-load, secondary-side output current (equal to 20 A).

#### 2.3.2.7 Primary Side MOSFETs

Consider each MOSFET to have an input voltage equal to its maximum applied voltage. A MOSFET with a maximum drain source voltage greater than 500 V is feasible for this design. The turnon losses can be neglected for an LLC power stage working in ZVS. Choose the MOSFET based on the values for  $R_{DSon}$  and  $C_{OSS}$ . Optimizing the  $C_{OSS}$  helps to minimize the dead time required for achieving ZVS, thereby minimizing the duty cycle loss. This reference design uses the STP24N60M2 MOSFET. The adaptive dead-time optimization feature of the UCC256303 helps to maximize the duty cycle, which improves the efficiency.

#### 2.3.2.8 Secondary-Side Synchronous MOSFETs

Equation 38 calculates the synchronous rectifier maximum voltage rating.

$$V_{\text{DSmax sec}} = 1.2 \times 2 \times V_{O(\text{nom})} = 57.6 \text{ V}$$

The current rating of the MOSFET is determined as I<sub>sec Mrms</sub> = 15.7 A.

This reference design uses TI's CSD19501KCS with its low  $R_{DSon}$  (< 5.5 m $\Omega$ ) and  $Q_g$  (< 38 nC). The very-low  $R_{DSon}$  of the device helps to reduces the overall loss in the synchronous rectifier.

#### 2.3.2.9 Soft Start—UCC256303

The UCC256303 is configured to provide a maximum 400-ms soft-start period. During start-up the softstart capacitor charges using the internal 25-µA current source. The UCC256303 exits soft start when the closed-loop control takes over or when the voltage on the soft-start capacitor reaches 7 V. Select the value of the soft-start capacitor using Equation 39.

$$C_{SS} = C31 = 400 \text{ mS} \times \frac{25 \,\mu\text{A}}{7 \,\text{V}} = 1.5 \,\mu\text{F}$$

(39)

#### 2.3.2.10 Current Sense Circuit (ISNS Pin)—UCC256303

The overcurrent limit OCP3 is set to trigger at 1.2 times the peak overload capability of the system.

$$V_{\text{ISNSFulload}} = \frac{\text{OCP3}}{1.2} = \frac{0.6}{1.2} = 0.5 \text{ V}$$

(40)

The current sense ratio is then calculated as:

$$K_{\rm ISNS} = \frac{V_{\rm ISNSFullload}}{\left(\frac{P_{\rm OUT(max)}}{\eta}\right) \times \left(\frac{1}{V_{\rm DCIN(nom)}}\right)} = \frac{0.5}{(500) \times \left(\frac{1}{390}\right)} = 0.39 \ \Omega \tag{41}$$

Select the current sense capacitor  $C_{ISNS} = C39 = 150 \text{ pF}$ . Equation 42 calculates the current sense resistor  $R_{ISNS}$ .

$$R_{ISNS} = R14 = K_{ISNS} \times \frac{C_r}{C_{ISNS}} = 0.39 \times \frac{66 \times 10^{-9}}{150 \times 10^{-12}} = 171 \Omega$$

(42)

Use a 169- $\Omega$  resistor for R14.

#### 2.3.2.11 Overvoltage Protection (BW Pin)—UCC256303

The BW pin senses the output voltage through the bias winding mounted on the LLC transformer. This pin can be used to provide an additional OVP in the system. In this reference design, the bias winding has the same number of turns as the secondary winding. When the OVP voltage is set to 32 V, the bias winding voltage will be 32 V. After implementing this setting, the BW pin potential divider is configured in such a way that it acknowledges the 4 V at the 32-V output.

Select  $R_{BWLOWER} = R18 = 10 \text{ k}\Omega$ . Equation 43 then calculates the  $R_{BWUPPER}$  as follows.

$$R_{BWUPPER} = R20 = R18 \times \frac{32 V - 4 V}{4 V} = 70 k$$

(43)

Use a 69.8-k $\Omega$  resistor for R18.

# 3 Hardware, Testing Requirements, and Test Results

# 3.1 Requirement for Testing

# 3.1.1 Test Conditions

- Input conditions:

- $\,$  V\_{\rm IN}\!\!: 85-V to 265-V AC

- IIN: Current limit to 8 A

- Output conditions:

- V<sub>OUT</sub>: 24 V

- I<sub>OUT</sub>: 0 A to 20 A

# 3.1.2 Required Equipment

- Isolated AC source

- Single-phase power analyzer

- Digital oscilloscope

- Multimeters

- Electronic load

- 12-V DC fan

### 3.1.3 Procedure

- 1. Turn on the 12-V DC fan and set the current to obtain approximately 200 LFM airflow on the board.

- 2. Connect the input terminals (connector J3) of the reference board to the AC power source.

- 3. Connect the output terminals (connector J2) to the electronic load, maintaining correct polarity.

- 4. Set a minimum load of approximately 50 mA.

- Gradually increase the input voltage from 0 V to turn on a voltage of 85-V AC. As the voltage across the PFC bulk capacitor crosses 90 V, the LLC section begins working and supplies the auxiliary power to the PFC controller. At this point, the PFC starts and boosts the PFC stage output voltage to 390-V DC.

- 6. Observe the start-up conditions for smooth switching waveforms.

- 7. Apply a load and perform tests to determine the efficiency, obtain regulation data, and observe steadystate operating conditions.

# 3.2 Test Results

# 3.2.1 Efficiency, Regulation, PF, and iTHD

This section shows the efficiency, power factor, regulation, and iTHD results at 115-V AC and 230-V AC input. Table 4 gives the test data.

| P <sub>OUT</sub> (W) | EFFICIENCY (%)<br>AT 115-V AC | EFFICIENCY (%)<br>AT 230-V AC | PF AT<br>115-V AC | PF AT<br>230-V AC | iTHD (%) AT<br>115-V AC | iTHD (%) AT<br>230-V AC | % REGULATION<br>AT 115-V AC | % REGULATION<br>AT 230-V AC |

|----------------------|-------------------------------|-------------------------------|-------------------|-------------------|-------------------------|-------------------------|-----------------------------|-----------------------------|

| 25                   | 82.51507128                   | 81.29950053                   | 0.9481            | 0.7               | 23.09                   | 33                      | 0.57                        | 0.62                        |

| 50                   | 83.9242486                    | 84.81680385                   | 0.9727            | 0.866             | 17.2                    | 27.2                    | 0.54                        | 0.55                        |

| 100                  | 89.52061765                   | 90.22170067                   | 0.9884            | 0.964             | 11.19                   | 16.8                    | 0.05                        | 0.38                        |

| 150                  | 90.97905138                   | 92.31231215                   | 0.992             | 0.9755            | 8.7                     | 15.7                    | 0                           | -0.05                       |

| 200                  | 91.65701754                   | 93.15128193                   | 0.995             | 0.981             | 7.27                    | 14.06                   | -0.08                       | -0.1                        |

| 250                  | 92.07668415                   | 93.92470822                   | 0.996             | 0.985             | 6.37                    | 12.5                    | -0.1                        | -0.06                       |

| 300                  | 92.04876775                   | 94.11389092                   | 0.997             | 0.988             | 5.75                    | 11.3                    | -0.14                       | -0.12                       |

| 350                  | 91.87753864                   | 94.01469237                   | 0.997             | 0.9899            | 5.53                    | 10.88                   | -0.25                       | -0.22                       |

| 400                  | 91.55421377                   | 93.74407263                   | 0.997             | 0.991             | 5.39                    | 9.67                    | -0.39                       | -0.35                       |

| 450                  | 91.35421377                   | 93.45708653                   | 0.998             | 0.992             | 5.42                    | 9.06                    | -0.44                       | -0.4                        |

| 480                  | 91.12785237                   | 93.34447384                   | 0.998             | 0.992             | 5.31                    | 8.97                    | -0.44                       | -0.42                       |

# Table 4. Test Results for 115-V AC and 230-V AC Input

1 0.95 0.9 0.85 Н 0.8 0.75 0.7 230-V AC 115-V AC 0.65 0.6 0 100 200 300 400 500 Output Power (W) D003

Figure 5. Power Factor Data

TIDUDW0-February 2018 Submit Documentation Feedback

Hardware, Testing Requirements, and Test Results

### 3.2.2 Inrush Current Limiting at Start-Up

Figure 7 shows the inrush current at start-up. The inrush current is limited through an active inrush limiter circuit in series with the bulk capacitor.

Figure 7. Inrush Current Limiting at Start-Up

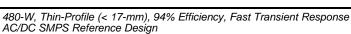

### 3.2.3 PFC Start-Up Waveform

Figure 8 shows the full-load start-up waveform. The input current reaches the steady-state value in the first few cycles.

Figure 8. Full Load Start-Up Waveform at 230-V AC Input

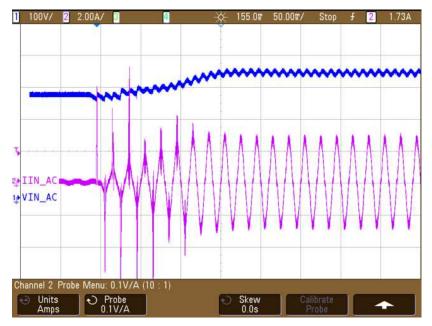

#### 3.2.4 Load Transient Response

Figure 9 shows the load transient response of the system when the 24-V output load current step changes from 20% to 100% with a slew rate of 500 mA/ $\mu$ s.

Figure 9. Load Transient Response

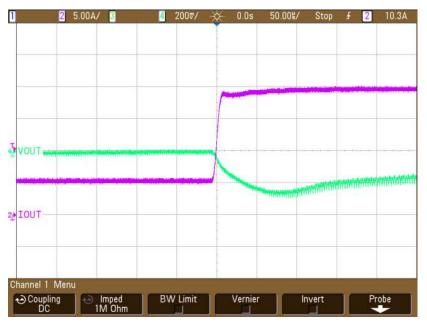

### 3.2.5 Output Voltage Ripple

Figure 10 shows the output voltage ripple at the 24-V output at full load.

Figure 10. Output Voltage Ripple at Full Load

Hardware, Testing Requirements, and Test Results

#### www.ti.com

### 3.2.6 PFC Working Waveforms

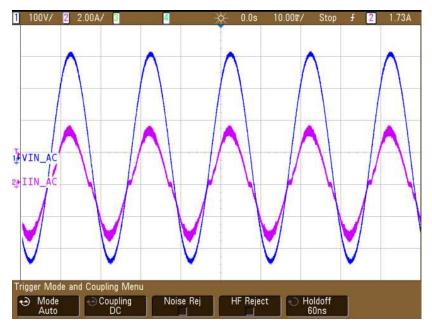

This subsection shows the PFC input and switching waveforms. Figure 11 shows the input voltage and input current at a 230-V AC input and full-load output.

Figure 11. PFC Input Voltage and Current Waveform

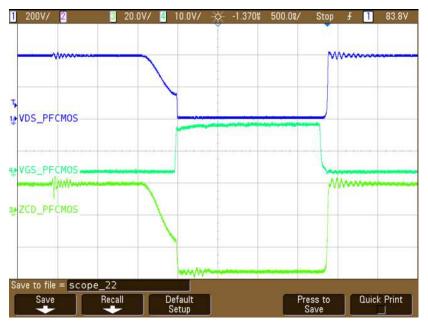

Figure 12 shows the PFC switching waveform for phase 1. The MOSFET drain source voltage, gate source voltage, and the ZCD winding voltage has been captured. Note how the PFC MOSFET turns at the valley point, thus ensuring the lowest turnon loss.

Figure 12. PFC MOSFET Switching Waveform

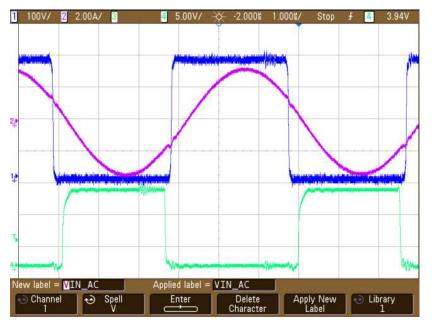

#### 3.2.7 LLC Working Waveform

Figure 13 shows the LLC switching waveforms. The primary high-voltage MOSFET drain source voltage, gate source voltage, and the resonant tank current have been captured.

Figure 13. LLC Stage MOSFET Switching Waveform

### 3.2.8 Synchronous Rectifier Waveform

This subsection shows the UCC24612 synchronous rectifiers drive output along with the current through the synchronous rectifier MOSFET. When the current begins to flow through the body diode of the synchronous MOSFET, the synchronous rectifier turns on the channel within 170 ns; Figure 14 shows this result.

Figure 14. Synchronous Rectifier Working Waveform

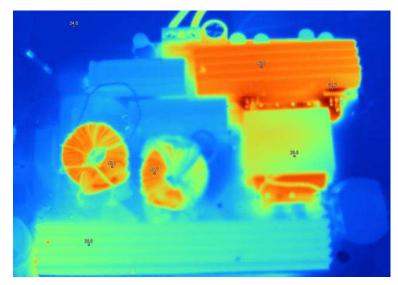

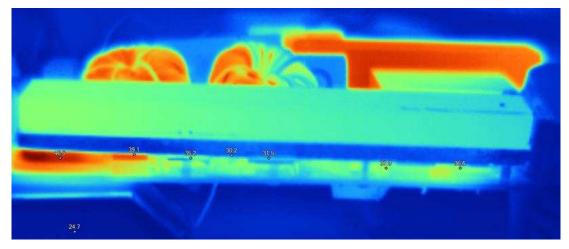

#### 3.2.9 Full-Load Thermal Image

Figure 15 and Figure 16 show the full-load thermal image at a 230-V AC input. The thermal image was recorded after running the board for 20 minutes. This thermal image was recorded using forced air cooling with a 200-LFM airflow.

Figure 15. Thermal Image Captured at 230-V AC Input and Full Load Output (Top View)

Figure 16. Thermal Image Captured at 230-V AC Input and Full Load Output (Side View)

Table 5 lists the temperatures at different points on the board.

| COMPONENT                 | TEMPERATURE    |

|---------------------------|----------------|

| Diode bridge              | 46.8°C         |

| PFC MOSFET                | 39.1°C, 35.2°C |

| PFC diode                 | 31.5°C, 30.2°C |

| PFC inductor              | 48.1°C, 46.7°C |

| LLC MOSFET                | 46.2°C, 46.4°C |

| LLC synchronous rectifier | 56.9°C, 52.5°C |

| LLC transformer           | 38.8°C         |

| Table 5. Temperature of Various Components |

|--------------------------------------------|

| on Board                                   |

480-W, Thin-Profile (< 17-mm), 94% Efficiency, Fast Transient Response AC/DC SMPS Reference Design

Design Files

#### 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01495.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01495.

### 4.3 PCB Layout Recommendations

Refer to the UCC256303, UCC28063A, and UCC24612-2 data sheets for detailed layout recommendations.

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01495.

### 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01495.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01495.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01495.

#### 5 Trademarks

E2E, NexFET are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 6 About the Author

**RAMKUMAR S** is a systems engineer at Texas Instruments, where he is responsible for developing reference design solutions for the industrial segment. Ramkumar brings his diverse experience in analog and digital power supplies design to this role. Ramkumar earned his master of technology (M.Tech) from the Indian Institute of Technology in Delhi.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated